# Fast role swap power architecture

## **TEXAS INSTRUMENTS**

Jacob Ontiveros PSIL/PI/Applications Texas Instruments

## The first official USB Type-C<sup>™</sup> and USB PD 2.0 specification set the path for an initial wave of products that can perform data functions outside of transferring USB data and increased power capabilities up to 100W. This capability merged functions that were once in separate products.

The USB PD 3.0 specification promises even more functionality, including smarter devices that allow system information to pass back and forth. Fast Role Swap (FRS) is great new feature of USB PD 3.0, where a device that is providing power can quickly change its power role to become a power consumer in order to maintain a constant data connection. FRS helps prevent any data loss that may occur when power is unexpectedly removed from a device.

Despite a defined detection method and standard USB PD messaging, designing devices to handle the dynamic changes in power is still a challenge. In this white paper, I will describe a FRS dongle design that is capable of the handling these new challenges, as well as some lessons learned from previous designs.

#### The design

A dongle can take full advantage of USB PD 3.0 FRS because it can operate both as a sink or source and maintain its functionality. A dongle can take many forms, including converting USB Type-C to legacy connectors (such as USB Type-A, DisplayPort<sup>™</sup> or High-Definition Multimedia Interface [HDMI]) or expanding to additional USB Type-C ports. The dongle must be able to provide power to the host it connects to, so there will be some power input coming either from a USB Type-C charging

Figure 1. Dongle and host.

port or a barrel jack-style connector. **Figure 1** shows a basic diagram of how a dongle connects with a USB Type-C host.

At a very high level, the design seems fairly simple – until you add some real functions. I recently purchased a USB Type-C and USB PD notebook with two full-featured USB Type-C ports that support USB, DisplayPort and USB PD charging.

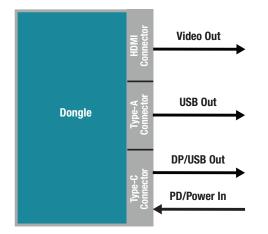

Figure 2. Dongle features.

Many of the devices I plug into my notebook still use legacy connectors, so a typical dongle should support USB Type-A and HDMI. Support for an additional USB Type-C and USB PD port would enable interfacing with newer devices such as a USB Type-C DisplayPort monitor. **Figure 2** shows the features of the dongle design.

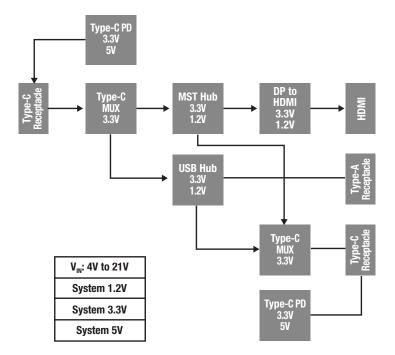

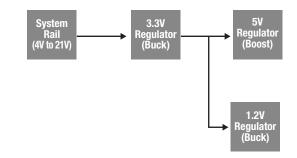

Implementing these features requires certain integrated circuits (ICs); you can see the need for two USB PD controllers (one per USB Type-C port), USB Type-C multiplexers, a USB hub, a DisplayPort hub and a DisplayPort-to-HDMI converter. Keeping these ICs powered during FRS and maintaining functionality is the toughest challenge. You'll need three voltage rails (5V, 3.3V and 1.2V) with a power architecture capable of generating these voltages from 4V to 21V. The design should also be able to handle the voltage transitions that occur during FRS to ensure that the design can provide the necessary rails. **Figure 3** shows the data-path architecture for the dongle with the respective power rails.

With well-defined data-path features, let's move onto the USB PD source features. USB PD 3.0 defines power rules for advertising source capabilities, where a 60W power adapter must be able to support 5V, 9V, 15V and 20V at 3A. A variable voltage supply achieves this in a standard adapter, but a dongle design is slightly more complicated because the USB PD power coming in on the charging port could range from 4V to 21V.

Figure 3. Dongle data-path architecture.

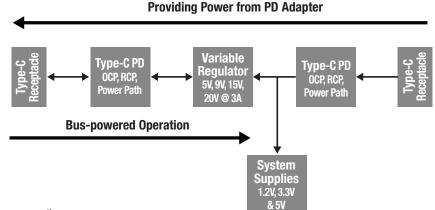

Figure 4. Dock/dongle power path.

Power-path control is essential to protecting the dongle and system from reverse and overcurrent conditions that may occur during FRS. The power coming into and out of the dongle must be controlled in order to prevent damage to 5V-only systems. These are some of the key features to look for in a USB PD controller where the controller is monitoring the USB PD contracts and system power to create seamless power handling. **Figure 4** shows the power path.

#### **Power-path architecture**

Before diving into the power-path architecture, you'll need to see what source and sink capabilities the design supports, along with the preferred data and power role and preferred mode of operation for DisplayPort Alternate Mode. With this information, you can determine what type of power you need in each mode of operation. Table 1 below shows the source and sink capabilities of the design. The host port is intended to provide power when the charging port is connected and consume power when it bus powered. The charging port is the main power source for the design, so it will sink the maximum power available up to 20V at 5A. When operating in bus-powered mode the design can still provide 5V at 900mA to power up a USB device.

Table 2 below summarizes the data capabilities

of the host and charging port. The host port is the main connection to the notebook and will data sink, where the charging port will function as a data source that can interface to other devices.

| USB Type-C receptacle | Source capabilities    | Sink capabilities              |

|-----------------------|------------------------|--------------------------------|

| USB Type-C host port  | 5V, 9V, 15V, 20V at 3A | 5V at 3A                       |

| Charging port         | 5V at 900mA            | 5V, 9V, 15V and 20V at 3A (5A) |

Table 1. USB Type-C port source/sink capabilities.

| USB Type-C receptacle | DisplayPort support        | Preferred data/power role         |

|-----------------------|----------------------------|-----------------------------------|

| USB Type-C host port  | UFP_D pin assignment C/D/E | Upstream-facing port (UFP)/source |

| Charging port         | DFP_D pin assignment C/E   | Downstream-facing port (DFP)/sink |

Table 2. USB Type-C port data/power roles.

| Port       | Voltage and current     | Power |

|------------|-------------------------|-------|

| HDMI       | 5V at 100mA             | 0.5W  |

| USB Type-A | 5V at 900mA             | 4.5W  |

| USB Type-C | 5V at 1.3A (with VCONN) | 6.5W  |

| Total      | 5V at 2.3A              | 11.5W |

Table 3. Connector power allocation.

Now, let's look at the power budget for the design. The HDMI, USB Type-A and USB Type-C connectors will require a certain amount of power to operate, and you must allot some power to the ICs on the dongle. The dongle will have 15W of power (5V at 3A) for bus-powered operation and 11.5W to provide power to the connectors. This leaves 3.5W of power for the dongle ICs and power loss.

**Table 3** summarizes the power allocated to theeach connector. The system bulk capacitanceshould be able to handle any power spikes thatmay occur.

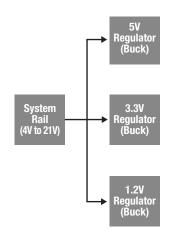

When putting together your system power supplies, you'll need to consider a few details in order to handle the power from  $V_{BUS}$ , which could range from 4V to 21V. Putting all of the converters in parallel enables each regulator to generate their voltage from the system power rail. There are issues when operating in the corner cases that could cause high in-rush currents during startup.

Figure 5. Parallel regulator architecture.

For my first implementation, I modified a fully certified USB PD 2.0 device that uses a parallel regulator architecture. During initial testing, the design would not consistently handle a FRS event. It turns out that some of the regulators were marginally stable when the system power fell from 20V to 5V, with a constant 3A load causing some supplies to collapse. When operating with V<sub>BUS</sub> at 4V, the 5V regulator supporting a 100% duty cycle would cause intermittent USB enumeration on the USB Type-A port that it powers. **Figure 5** shows the initial parallel architecture.

These design challenges necessitate a different approach to help reduce costs and make the design of the regulators simple. To ensure operation when  $V_{BUS}$  is at 4V, I used a wide-input-voltage 5A buck converter to generate the 3.3V rail and to feed the rest of the system supplies. A boost converter generated the 5V supply and a buck converter generated the 1.2V supply from the 3.3V rail. Starting the regulators up in a staggered fashion helps minimize the amount of in-rush current during initial power-up. **Figure 6** shows the final regulator architecture.

Figure 6. Staggered regulator architecture.

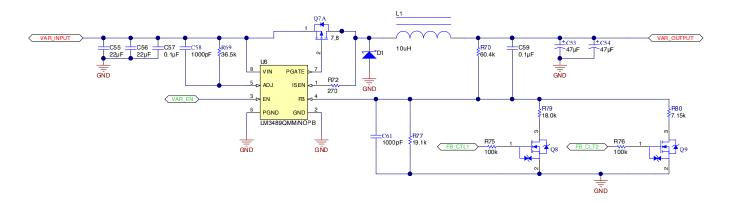

Figure 7. Variable regulator design.

With the board's power supplies in order, let's move to the USB PD source portion of the design. The variable voltage regulator that generates the 5V, 9V, 15V and 20V can be relatively simple. One of the features required on the design was to support "true constant on-time" so that the regulator could act as a simple pass-through device when a 20V USB PD adapter connects to the charging port. A simple P-channel FET hysteric controller fits the design needs perfectly. This type of topology guarantees stability over a wide operating range, with the input voltage ranging from 5V to 20V, the output voltage ranging from 5V, 9V, 15V and 20V, and the supporting current up to 3A. Changing the regulator feedback resistors varies the output voltage from the hysteretic controller. The USB PD controller dynamically sets the general-purpose input/output (GPIO) needed to output the appropriate voltage on the regulator. Figure 7 shows the variable regulator circuit.

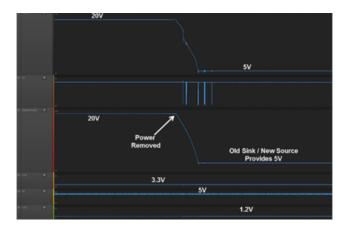

The final consideration to take into account is  $V_{BUS}$ and the system power during FRS. The state of  $V_{BUS}$ is the state of the system power in the dongle. This is where having a staggered voltage architecture works well, since it is optimized for the conditions seen during FRS and will keep the system supplies "alive." With higher loading, holding up the system power rail long enough for FRS to complete becomes a matter of physics. This is where capacitance is added to the system power rail. Making a few assumptions, you can use **Equation 1** to estimate how much capacitance will keep the system voltage valid if 20V falls to 5V with a  $\sim$ 3A initial load within 10ms. My design ended up using six 100µF capacitors to keep the system power rail alive.

$$V_C = V_0 e^{-t/RC} \rightarrow C = \frac{-t}{R \cdot \ln\left(\frac{V_C}{V_0}\right)} \rightarrow C = \frac{-.010s}{6\Omega \cdot \ln\left(\frac{5V}{20V}\right)} = \sim 600 \mu F$$

(1)

**Figure 8** shows an entire FRS event. The power from the dongle is removed and the configuration channel signaling for FRS occurs. As the voltage falls on  $V_{BUS}$ , there is a dip down to 4.2V, which recovers to 5V once the old sink/new source has fully supplied  $V_{BUS}$ . The dongle supplies are constantly on and maintain the data connection during power loss.

Figure 8. System supplies during FRS.

### Conclusion

USB PD 3.0 FRS enables a smooth and consistent user experience even during power losses. This design process is expandable to other types of products, such as external storage with multiple hard-drive bays that charge a notebook over a USB Type-C connector. FRS can help prevent the loss of data when power is removed from the storage device or even during a power outage.

**Important Notice:** The products and services of Texas Instruments Incorporated and its subsidiaries described herein are sold subject to TI's standard terms and conditions of sale. Customers are advised to obtain the most current and complete information about TI products and services before placing orders. TI assumes no liability for applications assistance, customer's applications or product designs, software performance, or infringement of patents. The publication of information regarding any other company's products or services does not constitute TI's approval, warranty or endorsement thereof.

The platform bar, is a trademark of Texas Instruments. All other trademarks are the property of their respective owners.

#### IMPORTANT NOTICE FOR TI DESIGN INFORMATION AND RESOURCES

Texas Instruments Incorporated ('TI") technical, application or other design advice, services or information, including, but not limited to, reference designs and materials relating to evaluation modules, (collectively, "TI Resources") are intended to assist designers who are developing applications that incorporate TI products; by downloading, accessing or using any particular TI Resource in any way, you (individually or, if you are acting on behalf of a company, your company) agree to use it solely for this purpose and subject to the terms of this Notice.

TI's provision of TI Resources does not expand or otherwise alter TI's applicable published warranties or warranty disclaimers for TI products, and no additional obligations or liabilities arise from TI providing such TI Resources. TI reserves the right to make corrections, enhancements, improvements and other changes to its TI Resources.

You understand and agree that you remain responsible for using your independent analysis, evaluation and judgment in designing your applications and that you have full and exclusive responsibility to assure the safety of your applications and compliance of your applications (and of all TI products used in or for your applications) with all applicable regulations, laws and other applicable requirements. You represent that, with respect to your applications, you have all the necessary expertise to create and implement safeguards that (1) anticipate dangerous consequences of failures, (2) monitor failures and their consequences, and (3) lessen the likelihood of failures that might cause harm and take appropriate actions. You agree that prior to using or distributing any applications. TI has not conducted any testing other than that specifically described in the published documentation for a particular TI Resource.

You are authorized to use, copy and modify any individual TI Resource only in connection with the development of applications that include the TI product(s) identified in such TI Resource. NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT OF TI OR ANY THIRD PARTY IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information regarding or referencing third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of TI Resources may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

TI RESOURCES ARE PROVIDED "AS IS" AND WITH ALL FAULTS. TI DISCLAIMS ALL OTHER WARRANTIES OR REPRESENTATIONS, EXPRESS OR IMPLIED, REGARDING TI RESOURCES OR USE THEREOF, INCLUDING BUT NOT LIMITED TO ACCURACY OR COMPLETENESS, TITLE, ANY EPIDEMIC FAILURE WARRANTY AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY YOU AGAINST ANY CLAIM, INCLUDING BUT NOT LIMITED TO ANY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON ANY COMBINATION OF PRODUCTS EVEN IF DESCRIBED IN TI RESOURCES OR OTHERWISE. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, DIRECT, SPECIAL, COLLATERAL, INDIRECT, PUNITIVE, INCIDENTAL, CONSEQUENTIAL OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF TI RESOURCES OR USE THEREOF, AND REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

You agree to fully indemnify TI and its representatives against any damages, costs, losses, and/or liabilities arising out of your noncompliance with the terms and provisions of this Notice.

This Notice applies to TI Resources. Additional terms apply to the use and purchase of certain types of materials, TI products and services. These include; without limitation, TI's standard terms for semiconductor products <a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation modules, and samples (<a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2018, Texas Instruments Incorporated