## PCM1738におけるDSDフィルタの特性と出力レベル

### 概要

このアプリケーション・ノートは、DVD-Audio、DSD両フォーマットに対応可能な高性能ステレオDAC、PCM1738におけるDSDフィルタの特性に関して記述しています。

周知の通り、PCM信号とDSD信号ではそのフォーマット 原理から信号フルスケール・レベルに差異があり、DSD信号 はPCM信号より6dB出力レベルが低くなっています。

PCM1738においては、4種類のDSDフィルタが内蔵され

ており、シリアル・レジスタ制御によりDSDフィルタの選択が可能で、DSD信号の基準出力レベルを同時に選択することができます。

### DSDモードとDSDフィルタ選択レジスタ

PCM1738のDSDモードとDSDフィルタの選択は第1図に示すレジスタ制御によって行うことができます。

#### DSD MODE CONFIGURATION AND FUNCTION CONTROLS

Configuration for DSD Interface mode:

- DFTH = 1 (Register 20)

- DME = 1 (Register 18)

Table V shows the register mapping available in DSD Mode

| REGISTER | B15 | B14 | B13 | B12 | B11 | B10 | B9 | B8 | B7  | B6   | B5   | B4                  | В3   | B2   | B1                 | B0  |

|----------|-----|-----|-----|-----|-----|-----|----|----|-----|------|------|---------------------|------|------|--------------------|-----|

| 16       | W/R | 0   | 0   | 1   | 0   | 0   | 0  | 0  | _   | _    | _    | _                   | _    | _    | _                  | -   |

| 17       | W/R | 0   | 0   | 1   | 0   | 0   | 0  | 1  | _   | _    | _    | _                   | -    | _    | _                  | -   |

| 18       | W/R | 0   | 0   | 1   | 0   | 0   | 1  | 0  | _   | _    | _    | _                   | DMF1 | DMF0 | DME <sup>(1)</sup> | -   |

| 19       | W/R | 0   | 0   | 1   | 0   | 0   | 1  | 1  | _   | _    | _    | OPE                 | CLKD | CLKE | _                  | -   |

| 20       | W/R | 0   | 0   | 1   | 0   | 1   | 0  | 0  | RSV | SRST | MRST | DFTH <sup>(1)</sup> | RSV  | RSV  | OS1                | OS0 |

| 21       | R   | 0   | 0   | 1   | 0   | 1   | 0  | 1  | RSV | RSV  | RSV  | RSV                 | RSV  | RSV  | -                  | -   |

|          |     |     |     |     |     |     |    |    |     |      |      |                     |      |      |                    |     |

NOTE: (1) This bit is required selection for the external Digital Filter mode. (2) "-" = function disabled.

TABLE V. Register Mapping in DSD Mode.

### DMF[1:0] Analog FIR Performance Selection

These bits are available for Read/Write

Default Value: 00

| DMF[1:0] | Analog FIR Performance Select |

|----------|-------------------------------|

| 00       | DSD Filter 1                  |

| 01       | DSD Filter 2                  |

| 10       | DSD Filter 3                  |

| 11       | DSD Filter 4                  |

Plots for the Analog FIR filter responses are shown in the Typical Perfomance Curves of this data sheet.

### DSDフィルタ特性

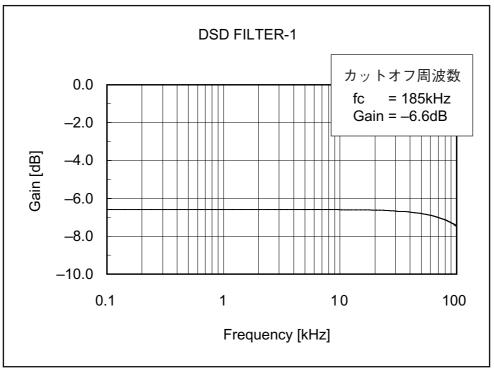

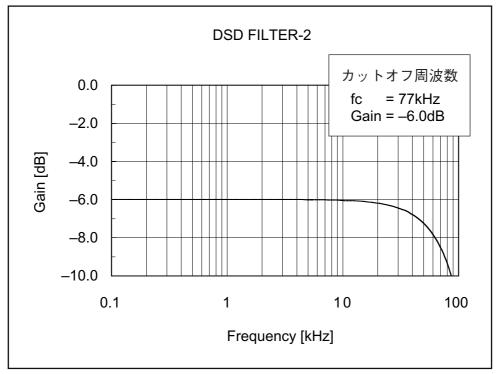

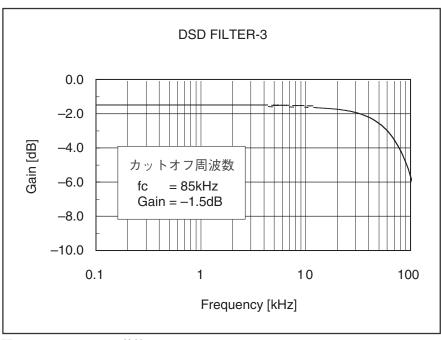

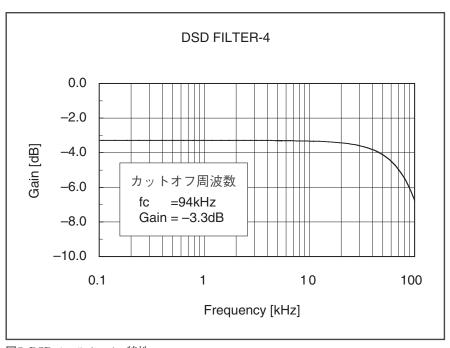

PCM1738の4種類のDSDフィルタ特性を第2図~第5図に示します。ここでは、PCM信号を基準(0dB)としたレベルで示しています。

PCM1738のデータシートでは4種類の各フィルタ特性をそれぞれの正規化レベルで示していますので合わせて参照ください

**図2.** DSDフィルター1 特性

**図3.** DSDフィルター2 特性

図4. DSDフィルター3 特性

**図5.** DSDフィルター4 特性

### PCM信号とのレベル差

第2図~第5図に示した通り、各DSDフィルタはPCM信号を基準とした場合、-1.5dBから-6dB低いレベルにあります。このレベル差補正は外部アナログ回路または、PCM信号に対するデジタル・アッテネータのアットネート量をDSDフィルタのゲインに合わせる手法で行う事も可能です。

最も簡単な方法では、-1.5dB程度のレベルが許容できるのであれば、PCM1738においてDSDフィルタ-3を選択することにより実現することが可能です。但し、各DSDフィルタの周波数特性は異なりますので、実アプリケーション設計におては選択DSDフィルタの周波数特性を考慮した設計を行って下さい。

(PCM1738)

# ご注意

日本テキサス・インスツルメンツ株式会社(以下TIJといいます)及びTexas Instruments Incorporated(TIJの親会社、以下TIJおよびTexas Instruments Incorporatedを総称してTIといいます)は、その製品及びサービスを任意に修正し、改善、改良、その他の変更をし、もしくは製品の製造中止またはサービスの提供を中止する権利を留保します。従いまして、お客様は、発注される前に、関連する最新の情報を取得して頂き、その情報が現在有効かつ完全なものであるかどうかご確認下さい。全ての製品は、お客様とTIとの間に取引契約が締結されている場合は、当該契約条件に基づき、また当該取引契約が締結されていない場合は、ご注文の受諾の際に提示されるTIの標準契約約款に従って販売されます。

TIは、そのハードウェア製品が、TIの標準保証条件に従い販売時の仕様に対応した性能を有していること、またはお客様とTIとの間で合意された保証条件に従い合意された仕様に対応した性能を有していることを保証します。検査およびその他の品質管理技法は、TIが当該保証を支援するのに必要とみなす範囲で行なわれております。各デバイスの全てのパラメーターに関する固有の検査は、政府がそれ等の実行を義務づけている場合を除き、必ずしも行なわれておりません。

TIは、製品のアプリケーションに関する支援もしくはお客様の製品の設計について責任を負うことはありません。TI製部品を使用しているお客様の製品及びそのアプリケーションについての責任はお客様にあります。TI製部品を使用したお客様の製品及びアプリケーションについて想定されうる危険を最小のものとするため、適切な設計上および操作上の安全対策は、必ずお客様にてお取り下さい。

TIは、TIの製品もしくはサービスが使用されている組み合せ、機械装置、もしくは方法に関連しているTIの特許権、著作権、回路

配置利用権、その他のTIの知的財産権に基づいて何らかのライセンスを許諾するということは明示的にも黙示的にも保証も表明もしておりません。TIが第三者の製品もしくはサービスについて情報を提供することは、TIが当該製品もしくはサービスを使用することについてライセンスを与えるとか、保証もしくは是認するということを意味しません。そのような情報を使用するには第三者の特許その他の知的財産権に基づき当該第三者からライセンスを得なければならない場合もあり、またTIの特許その他の知的財産権に基づきTIからライセンスを得て頂かなければならない場合もあります。

TIのデータ・ブックもしくはデータ・シートの中にある情報を複製することは、その情報に一切の変更を加えること無く、且つその情報と結び付られた全ての保証、条件、制限及び通知と共に複製がなされる限りにおいて許されるものとします。当該情報に変更を加えて複製することは不公正で誤認を生じさせる行為です。TIは、そのような変更された情報や複製については何の義務も責任も負いません。

TIの製品もしくはサービスについてTIにより示された数値、特性、 条件その他のパラメーターと異なる、あるいは、それを超えてなされた 説明で当該TI製品もしくはサービスを再販売することは、当該TI製 品もしくはサービスに対する全ての明示的保証、及び何らかの黙示 的保証を無効にし、且つ不公正で誤認を生じさせる行為です。TIは、 そのような説明については何の義務も責任もありません。

なお、日本テキサス・インスツルメンツ株式会社半導体集積回路製品販売用標準契約約款もご覧下さい。

http://www.tij.co.jp/jsc/docs/stdterms.htm

Copyright © 2006, Texas Instruments Incorporated 日本語版 日本テキサス・インスツルメンツ株式会社

### 弊社半導体製品の取り扱い・保管について

半導体製品は、取り扱い、保管・輸送環境、基板実装条件によっては、お客様での実装前後に破壊/劣化、または故障を起こすことがあります。

弊社半導体製品のお取り扱い、ご使用にあたっては下記の点 を遵守して下さい。

### 1. 静電気

- 素手で半導体製品単体を触らないこと。どうしても触る必要がある場合は、リストストラップ等で人体からアースをとり、導電性手袋等をして取り扱うこと。

- 弊社出荷梱包単位(外装から取り出された内装及び個装) 又は製品単品で取り扱いを行う場合は、接地された導 電性のテーブル上で(導電性マットにアースをとったも の等)、アースをした作業者が行うこと。また、コンテナ等も、導電性のものを使うこと。

- マウンタやはんだ付け設備等、半導体の実装に関わる 全ての装置類は、静電気の帯電を防止する措置を施す こと。

- 前記のリストストラップ・導電性手袋・テーブル表面 及び実装装置類の接地等の静電気帯電防止措置は、常 に管理されその機能が確認されていること。

### 2. 温·湿度環境

■ 温度:0~40℃、相対湿度:40~85%で保管・輸送 及び取り扱いを行うこと。(但し、結露しないこと。) ● 直射日光があたる状態で保管・輸送しないこと。

### 3. 防湿梱包

● 防湿梱包品は、開封後は個別推奨保管環境及び期間に 従い基板実装すること。

### 4. 機械的衝撃

● 梱包品(外装、内装、個装)及び製品単品を落下させたり、 衝撃を与えないこと。

### 5. 熱衝撃

● はんだ付け時は、最低限260°C以上の高温状態に、10 秒以上さらさないこと。(個別推奨条件がある時はそれ に従うこと。)

### 6. 汚染

- はんだ付け性を損なう、又はアルミ配線腐食の原因となるような汚染物質(硫黄、塩素等ハロゲン)のある環境で保管・輸送しないこと。

- はんだ付け後は十分にフラックスの洗浄を行うこと。 (不純物含有率が一定以下に保証された無洗浄タイプのフラックスは除く。)

以上