Application Report JAJA085

# アンプとビット: データ・コンバータ用アンプ選択の手引き

Bruce Carter, Patrick Rowland Jim Karki, Perry Miller

High Performance Linear Products

## 概

このアプリケーション・レポートでは、汎用アンプとアナ ログ-デジタル・コンバータのインターフェイスをとる際に 考慮すべき様々な事柄について説明します。帯域幅、分解 能、アナログADC入力駆動、電源といった検討事項を、アン プとADC両方の観点から論じます。

#### 目 次

| 1.                | はじょ             | かに                 | 3   |  |  |  |

|-------------------|-----------------|--------------------|-----|--|--|--|

| 2.                | バッフ             | ファリングの重要性          | 3   |  |  |  |

| 3.                | 帯域幅             | <u></u>            | 4   |  |  |  |

|                   | 3.1             | 帰還理論               |     |  |  |  |

|                   | 3.2             | 閉ループ帯域幅            | 5   |  |  |  |

|                   |                 | 3.2.1 非反転閉ループ帯域幅   | 5   |  |  |  |

|                   |                 | 3.2.2 反転閉ループ帯域幅    | 6   |  |  |  |

|                   | 3.3             | ゲイン帯域幅の安全域         | 7   |  |  |  |

|                   | 3.4             | ゲイン帯域幅の、電源電圧への依存性  | 8   |  |  |  |

| 4.                | スルー             | -・レート              | 8   |  |  |  |

| 5.                | ノイス             | ぐとビット              | 9   |  |  |  |

|                   | 5.1             | グラフから読み取るノイズ       | 9   |  |  |  |

|                   | 5.2             | nV または 仕様から読み取るノイズ | 9   |  |  |  |

|                   | 5.3             | 全高調波歪み (THD) + ノイズ | .10 |  |  |  |

|                   | 5.4             | 信号 - ノイズ比 (SNR)    | .10 |  |  |  |

|                   | 5.5             | SINAD              | .11 |  |  |  |

|                   | 5.6             | 有効ビット数 (ENOB)      | .11 |  |  |  |

|                   | 5.7             | ADCのビット            | .12 |  |  |  |

|                   | 5.8             | ADC入力              | .13 |  |  |  |

|                   | 5.9             | 駆動電流               | .14 |  |  |  |

|                   | 5.10            | 再びスルー・レートについて      | .14 |  |  |  |

|                   | 5.11            | セトリング時間            | .15 |  |  |  |

|                   | 5.12            | 信号バイアス             | .15 |  |  |  |

|                   | 5.13            | 入力オフセット            | .16 |  |  |  |

| 6.                | 電源.             |                    |     |  |  |  |

|                   | 6.1             | 電源プレーンとグランド・プレーン   | .16 |  |  |  |

|                   | 6.2             | 入力/出力電圧範囲          | .16 |  |  |  |

| 7.                | 要約.             |                    | .17 |  |  |  |

| 8.                | 参照文             | て献                 | .17 |  |  |  |

| 付録A: 設計例 携帯電話の基地局 |                 |                    |     |  |  |  |

|                   | Αľ              | OCに関する検討事項         | .18 |  |  |  |

|                   | GSM信号処理のADC要件18 |                    |     |  |  |  |

この資料は、Texas Instruments Incorporated (TI) が英文で記述した資料を、皆様のご理解の一助として頂くために日本テキサス・インスツルメンツ (日本TI) が英文から和文へ翻訳して作成したものです。 資料によっては正規英語版資料の更新に対応していないものがあります。 日本TIによる和文資料は、あくまでもTI正規英語版をご理解頂くための補助的参考資料としてご使用下さい。

製品のご検討およびご採用にあたりましては必ず正規英語版の最新資料を

Tおよび日本TIは、正規英語版にて更新の情報を提供しているにもかかわらず、更新以前の情報に基づいて発生した問題や障害等につきましては如 何なる責任も負いません。

SLOA035B 翻訳版

最新の英語版資料

http://www-s.ti.com/sc/techlit/sloa035.pdf

| M     |                                       |    |

|-------|---------------------------------------|----|

| 図 1.  | アンプとADC                               |    |

| 図 2.  | オペアンプの開ループのボード線図                      | .4 |

| 図 3.  | 閉ループのボード線図                            | .4 |

| 図 4.  | 非反転ゲイン段                               | .5 |

| 図 5.  | ループの切れた非反転段                           | .5 |

| 図 6.  | 反転ゲイン段                                |    |

| 図 7.  | 反転段の部品がゲインに与える影響                      |    |

| 図 8.  | 安全域による帯域幅の制限                          |    |

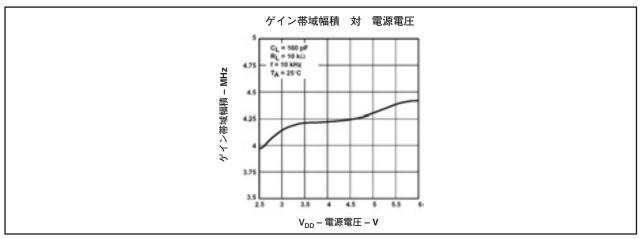

| 図 9.  | 標準的なゲイン帯域幅積のグラフ (TLV2460)             |    |

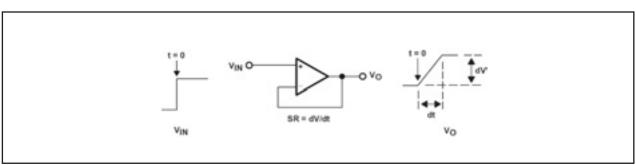

| 図 10. | スルー・レート                               |    |

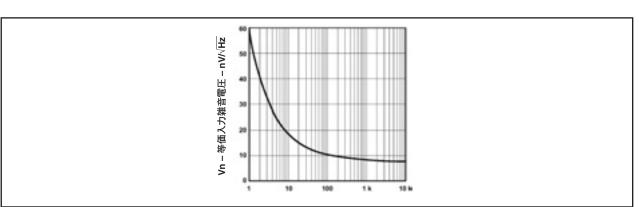

| 図 11. | 標準的なオペアンプのノイズ特性                       |    |

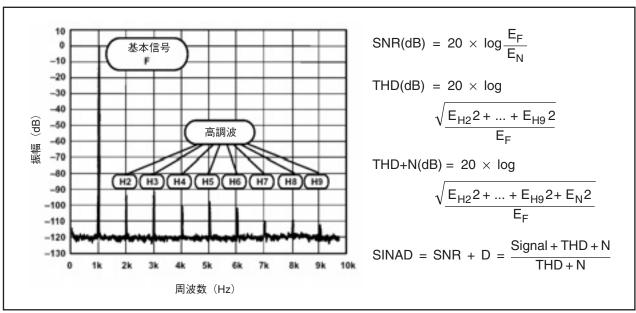

|       | SNRとTHDのビジュアル表現1                      |    |

| 図 13. |                                       |    |

|       | アンプ - ADC間のインターフェイス1                  |    |

| 図 15. | 基地局アプリケーションの例1                        |    |

|       | ADCへの完全差動入力1                          |    |

| 図 17. | 回路の簡素化1                               |    |

| 図 18. |                                       |    |

|       | · · · · · · · · · · · · · · · · · · · |    |

|       | 入力オフセット電圧 (V <sub>IO</sub> )1         |    |

| 図 21. | バッファ・オペアンプの設計例2                       | 20 |

|       |                                       |    |

| 表     |                                       |    |

| 表 1.  | 安全域 vs ゲイン誤差                          | .7 |

| 表 2.  | SNR vs コンバータのビット1                     | 0  |

| 表 3.  | オペアンプ要件1                              | 9  |

## 1. はじめに

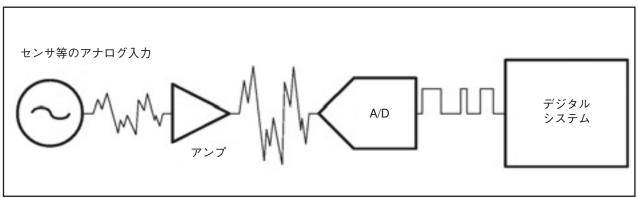

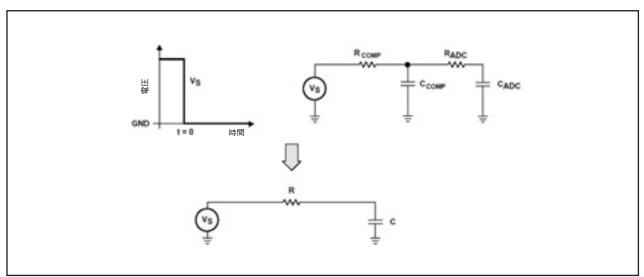

このアプリケーション・レポートでは、オペアンプとアナログ・デジタル・コンバータ (ADC)のインターフェイスをとる際に考慮すべき様々な事柄について説明します。説明の大部分は低速のアプリケーションに関するものですが、高速インターフェイス関係の構成要素も提示されます。付録Aでは、性能制約が極度に重要となるタイプのアプリケーション - 携帯電話の基地局中で、オペアンプとADC間のインターフェイスを定義するのに必要な基準のいくつかについて説明します。図1に、アンプとADC間のインターフェイスを示します。

入力をADCヘインターフェイスするプロセスには、次に 挙げるプロセスのいくつか、またはすべてが含まれる可能性 があります。

- 増幅/減衰 入力信号レベルのスケーリングを行い、ADC の入力回路に必要なレベルに合わせます。

- DCオフセット/レベルシフト 固定オフセットで入力信号 のDCレベルを上下に動かして、ADCの動作範囲に合わせます。

- フィルタリング 入力信号から不要な信号成分を除去し、 関心の対象となる帯域幅のみをADCに提供します。

幸いなことに、オペアンプはこれらの機能すべてに非常に適しています。単体のオペアンプに複数の機能を実行させることはよくあります。アプリケーションというのは、ある意味ではどれもが特殊ケースです。入力源をADCに示すためのオペアンプ・インターフェイスを決定するに先立って、データ・コンバータ、入力信号、電源等のシステム要件の特性を理解しておくことは設計者の責務です。例えば、温度センサでは直流の電流または電圧を出力するため、信号のDC特性がきわめて重要になります。一方、RFアプリケーションではAC結合が可能であるため、オペアンプのDC特性は無視できます。

### 2. バッファリングの重要性

ADCでオペアンプ・インターフェイスを使用する利点のひとつでありながら見落とされがちなのが、バッファリングです。

大半のADCの入力電圧範囲は、信号源からかかる電圧範囲と完全には一致しません。電圧源出力がADCに合う場合はほとんどないのです。このような場合には、オペアンプ・インターフェイスを取り除きたくなるでしょう。ただしその場合でも設計者は、入力信号とコンバータの間にバッファ・オペアンプを置くことを検討しようと思うかもしれません。その理由は様々ですが、最もよくあるものは次のとおりです。

- インピーダンス整合のため: 信号源は必ずしも低インピーダンスではありません。ADCの入力は信号源に大きな負荷をかけ、影響を与える可能性があります。ユニティ・ゲインのオペアンプ・バッファでは入力インピーダンスが非常に高く、したがって信号源に負荷をかけることはありません。その上、出力インピーダンスは低いため、ADCの入力を駆動するのに非常に適しています。

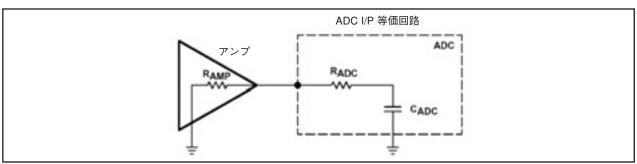

- 容量性負荷の影響を減らすため: 大部分のタイプのADCでは、抵抗負荷と同様に容量性負荷が入力にかかります。このために、通常抵抗1つとキャパシタ1つからなる外部補償回路が必要になります。TIでは、この回路を仕様で指定することがよくあります。この推奨に従うことは大切ですが、そうすると信号源に容量性負荷がかかることになります。信号源は抵抗でキャパシタから切り離されますが、この抵抗はたいてい低い値です。オペアンプ・インターフェイスの低出力インピーダンスでならば、通常はこの回路を問題なく駆動できます。

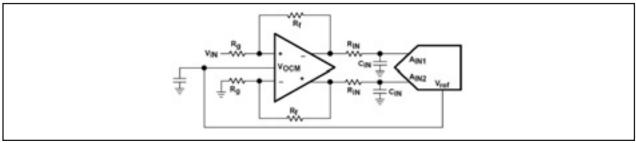

- シングル・エンド信号から差動信号への変換のため: 上記 のような理由でオペアンプが必要になることがないとしても、新しいADCの多くでは差動入力をサポートしています。一方、入力源の大半はシングル・エンドです。したがって、この変換を行うためにどうしてもオペアンプ・インターフェイスが必要になります。この変換はシングル・エンドのオペアンプでも可能ですが、完全差動オペアンプを使用した方が容易に実行できます。

図 1. アンプとADC

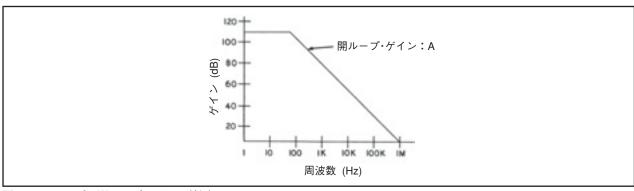

図2. オペアンプの開ループのボード線図

## 3. 帯域幅

帯域幅のシステム要件を満たすADCを選ぶことは、最優先事項です。電力 (power) やインターフェイスといった他の検討事項も出てきますが、ADCの帯域幅さえ決まればアンプはそれに合わせて選択できます。各アプリケーションではエイリアシングを回避するためにナイキスト周波数を測定し、関心の対象となる最高周波数の2倍を超える周波数でサンプリングを行います。重要な要因がナイキスト制限値だけであれば、本論をここで終えることもできるのですが。

残念なことに「帯域幅はどのくらいあれば十分なのか?」 という疑問は、もっとずっと複雑です。

オペアンプの帯域幅に関する考察はどれも、開ループ応答のボード線図(ボード・プロット)から始まります。この線図はどのオペアンプのデータシートにも記載されており、図2のプロットのような形をしています。

ボード線図とは、オペアンプの「周波数 vs. ゲイン」の関係を表したプロットです。軸は両方とも対数軸で、ゲインがデシベル (dB) 単位でプロットされます。次に示す、ボード線図に関するいくつかのポイントを理解するだけで、あらゆる補償型電圧帰還オペアンプのパフォーマンスを見積もることができます。

- DC(0Hz)~低い周波数での開ループ·ゲイン(A)。水平な (= 周波数に対してゲインが一定値である)線で表されます。

- 内部補償によるブレークポイント。このポイントで、それまで周波数に対して一定値だったオペアンプの応答が、

周波数1ディケードあたり20dBのロールオフ(減衰傾度)を伴う領域に変化します。

周波数のロールオフが、ボード線図上のユニティ・ゲイン (0dB) のラインに達するポイント。ここがアンプの帯域幅 とみなされます。

特性曲線でトランジスタの動作点を定義するのと同じように、ボード線図ではオペアンプの正当な動作点を定義します。オペアンプは、開ループ・ゲイン曲線の左側と下側ならばどの領域でも動作可能です。ただし、曲線に近い領域でオペアンプを動作させると、予期しない結果が生じる可能性があります。この結果は反転ゲイン構成と非反転ゲイン構成では全く異なるものになるので、以降のセクションで詳しく論じることにします。

#### 3.1 帰還理論

オペアンプは、閉ループ構成で帰還をかけることによって動作します。したがって、帰還方式の一般的な公式をオペアンプにも適用することができます。

$$\frac{V_O}{V_I} = \frac{A}{1 + A\beta} \tag{1}$$

この式では、次に示す重要な項を定義します。

- 量A(開ループ·ゲイン)

- 量 AB (ループ·ゲイン)

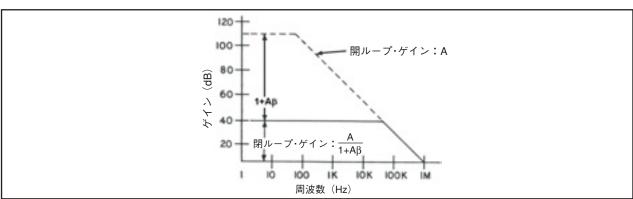

図3にこれらの図解を示します。

図3. 閉ループのボード線図

閉ループ・ゲインは、開ループ・ゲインAを1+Aβで除算して修正したものです。対数が用いられているため、除算は2つの量の減算によって行えます。したがって図3では、内部補償によるブレークポイントまでの低周波数領域の閉ループ・ゲインは110dBマイナス70dB、つまり40dBとなります。

ゲインを犠牲にすると、帯域幅は増加します。ゲイン110dBでの帯域幅は、内部補償周波数のブレークポイント(図2と図3の100Hz付近)で一定値の(水平な)ゲイン・ラインと交差していますが、ゲイン40dBでの帯域幅は50kHz付近で交差しています。このようなゲインの減少と帯域幅の増加は一次関数の関係にあり、ゲイン帯域幅積(GBP)として知られています。

電圧帰還(VFB)アンプを使用する場合の小信号帯域幅について考える際には、GBPの仕様が関わってきます。VFBアンプは使用されているゲインに依存するため、関心の対象となる信号をゲインで増幅した場合の周波数は、アンプのGBPよりも低い値でなければなりません。

#### 3.2 閉ループ帯域幅

ここで、非反転アンプ段と反転アンプ段の両方で、動作ゲイン (actual gain) が閉ループ・ゲインと開ループ・ゲイン 両方の関数になっていることに注意する必要があります。多くの場合、開ループ・ゲインからの寄与は無視できる程度のものであるため、設計者はこの事実になじみが薄いかもしれません。この事実が意味することについて、以降のセクションで説明します。

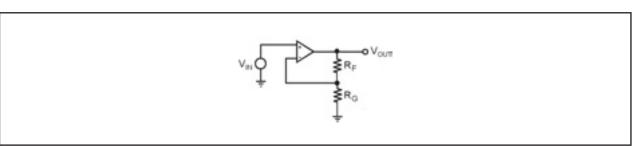

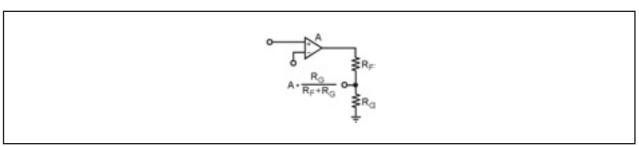

#### 3.2.1 非反転閉ループ帯域幅

次の式で、非反転オペアンプのゲイン段の正確なゲインを 計算できます。

$$\frac{V_O}{V_I} = \frac{A}{1 + \frac{A \bullet R_G}{R_G + R_F}}$$

A >> 所要の閉ループ·ゲインの場合

$$\frac{V_O}{V_I} = 1 + \frac{R_F}{R_G} \tag{2}$$

ここで:

RGはゲイン抵抗

R<sub>F</sub>は帰還抵抗

$$R_{G}$$

$R_G + R_F$  という量は、入力に返される出力電圧の比率です。 (分圧の法則より)

式(2)では非反転閉ループ・ゲインを定義しています。閉ループ・ゲインがオペアンプの開ループ・ゲイン曲線と交差する点は、閉ループ帯域幅です。したがって、ゲイン帯域幅積(GBP)は下記に等しくなります。

設計者にはおそらく、  $\frac{V_O}{V_I} = 1 + \frac{R_F}{R_G}$  という式の方がずっとなじみがあるでしょう。しかし、これは開ループ・ゲインを無限とした場合の概算値であることを覚えておく必要があります。

図 4. 非反転ゲイン段

図 5. ループの切れた非反転段

図 6. 反転ゲイン段

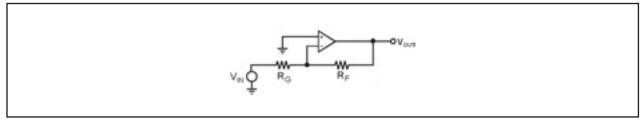

#### 3.2.2 反転閉ループ帯域幅

前のセクションで導き出されたゲイン帯域幅積が真に当てはまるのは、非反転ゲイン段のみです。反転オペアンプ・ゲイン段の正確なゲインを計算するには、次の式を用います。

$$\frac{V_O}{V_I} = \frac{\frac{-A \bullet R_F}{R_G + R_F}}{1 + \frac{A \bullet R_G}{R_G + R_F}}$$

A >>所要の閉ループ·ゲインの場合

$$\frac{V_O}{V_I} = -\frac{R_F}{R_G} \tag{5}$$

おそらく設計者には、二番目の式の方がずっとなじみがあるでしょう。この式と帰還式(1)の一般式を比較すると、 反転ゲイン段の開ループ・ゲインは下記に等しくなります。

$$\frac{-\mathsf{A} \bullet \mathsf{R}_{\mathsf{F}}}{\mathsf{R}_{\mathsf{G}} + \mathsf{R}_{\mathsf{F}}} \tag{6}$$

これは、反転ゲイン段のゲイン帯域幅積に対し、反転構成が使用される場合、開ループ・ゲインは帰還抵抗 $R_F$ とゲイン抵抗 $R_G$ の影響を受けることを意味します。図7に示すのは、帯域幅への影響です。

$R_G = R_F$ となるユニティ·ゲイン段では、ゲインが2分の1減ります。

この影響は、開ループのボード線図上で視覚的に計算できます。まず減ったゲインに対応する水平な直線を、補償のブレークポイントとなる周波数まで引きます。次に、元からある開ループのプロットに平行な斜めの線を引き、0dB軸まで伸ばします。これで、反転ゲイン抵抗付きのオペアンプ段に合わせてゲイン・プロットが調整されました。

これは別の表現をすると、ゲイン1の反転アンプでは、ゲイン2の非反転アンプと同様に出力信号の半分が返されるということです。

したがって、インターフェイスの速度が第一に要求される 高速アプリケーションでは、非反転構成を使用する必要があ ります。第一に要求されるのが同相信号の除去、ノイズ、高 調波歪みである場合は、反転構成を使用してください。

図7. 反転段の部品がゲインに与える影響

図8. 安全域による帯域幅の制限

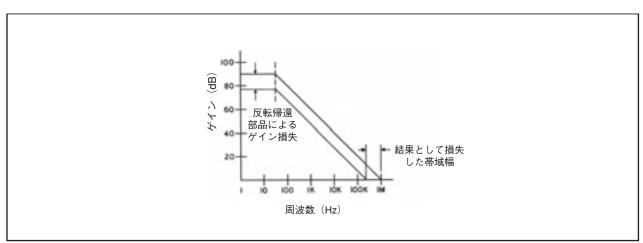

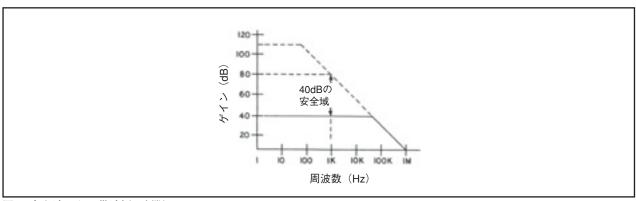

### 3.3 ゲイン帯域幅の安全域

アンプのGBPのマージンにある程度余裕を持たせておく のは、設計実践の上で好ましいことです。

40dBの余裕があれば十分な安全域として機能し、オペアンプの開ループ特性に起因する誤差を、確実に最小限にできます。

図8に示す1MHzのオペアンプのボード線図を見ると、40dB(×100)のゲインが必要な場合、使用できる周波数は最大1kHzにしかなりません。比較的低速のシステムでも高速オペアンプが必要となる可能性があるのは、このような理由にもよります。

安全域を40dBとしたのは、反転ゲイン構成と非反転ゲイン構成両方で、閉ループ・ゲインの計算に開ループ・ゲイン(A)への依存性があるためです(式2と式5を参照)。閉ループ・ゲインと開ループ・ゲイン間の差が40dBの場合、反転ゲイン誤差と非反転ゲイン誤差は0.01%程度です。安全域が20dBに減ると、ゲイン誤差は2%程度になります。2%はゲイン誤差としては相当大きいため、回避する必要があります。

より高い精度が必要な場合は、安全域を増やす必要があります。これは、高いゲイン帯域幅積を持つオペアンプを低いゲインで利用すれば可能です。精度がノイズよりも重要度の高い検討事項である場合は、複数のオペアンプを低ゲインで動作させる方が、単体のオペアンプを高ゲインで

動作させるよりも効果的です。安全域が増加すると、精度 も劇的に上がります。安全域が60dBの場合、 ゲイン誤差は 0.0001%程度です。表1に、反転段と非反転段のゲイン精度 に対する、安全域の効果を示します。

上の表の数字は、式(2)と式(5)から得られたものです。 どの安全域でも、非反転段のゲイン誤差の方が低くなって います。

開ループの依存性に関する問題はもうひとつあります。 図8を見ると、閉ループ・ゲインに関連する周波数依存性が わずかにあるのが分かります。1kHzでの安全係数は40dBで すが、100Hzでは安全域が60dBにまで増加しています。つ まり、ゲインがわずかに変化しています。

ほとんどの設計者は、オペアンプのゲイン回路に開ループが与える効果に気付いていません。高ゲイン帯域幅積のオペアンプを利用して、低ゲインで設計することに慣れているためです。オペアンプの開ループ・ゲインによって生成される誤差は、閉ループ・ゲインを定義するのに使用される抵抗の精度よりもずっと少なくなっています。このことは特殊相対性理論の場合に少し似ています。特殊相対性理論の本当に奇妙な効果は、光速に非常に近い速度で動いている場合にしか現れません。閉ループ・ゲインに関する開ループ・ゲインの本当に奇妙な効果も、安全域の値を低くして動作させない限りは現れないのです。

| 安全域 (dB) | 反転段<br>ゲイン誤差 (%) | 非反転段<br>ゲイン誤差 (%) |  |

|----------|------------------|-------------------|--|

| 0        | 66.6             | 50                |  |

| 10       | 16.7             | 9.09              |  |

| 20       | 1.96             | 0.99              |  |

| 30       | 0.2              | 0.0999            |  |

| 40       | 0.02             | 0.01              |  |

| 50       | 0.002            | 0.001             |  |

| 60       | 0.0002           | 0.0001            |  |

| 70       | 0.00002          | 0.00001           |  |

| 80       | 0.000002         | 0.000001          |  |

表 1. 安全域 vs ゲイン誤差

図 9. 標準的なゲイン帯域幅積のグラフ (TLV2460)

# 3.4 ゲイン帯域幅の、電源電圧への依 存性

オペアンプで使用される電源電圧はGBPにも影響します。 例えば図9では、TLV2460の $V_{\rm DD}$ 範囲全体でのGBPの差分 (delta) が400kHzであることが示されています。

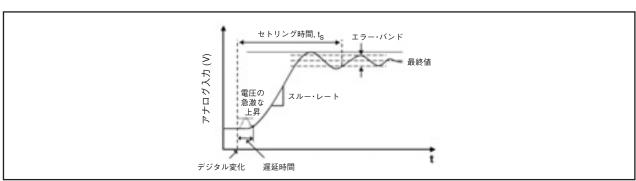

#### 4. スルー・レート

大信号帯域幅に関連して関心の対象となる仕様が、スルー・レート (SR) です。スルー・レートは、信号レベルが大きい (オペアンプの電圧範囲の限界に近い)、または信号の性質が正弦波以外 (方形波、パルス、三角波、ノコギリ波、ランプ波など) である場合に重要となります。これらの波形には、オペアンプの帯域幅を超える可能性のある高調波成分が含まれています。

スルー・レートは、「入力でのステップ変化によって起こる出力電圧の変化の割合」と定義され、V/μsまたはV/nsという単位で表されます。オペアンプの仕様として指定されるスルー・レートは、そのオペアンプが通過させる最大のSRであり、通常はゲイン1とともに指定されます。図10は、SRを視覚的に表したものです。

SR不足で歪みが生じないように信号をアンプで通過させるには、アンプのSRが信号SRの最大値と同じか、それ以上でなければなりません。サイン波のSRは、サイン波がゼロと交差する時に最大になります。次の式は、このスルー・レートを定義したものです。

$$SR = 2\pi fV \tag{7}$$

ここで、

f = 信号の周波数

V=信号のピーク電圧

SRは、SR+およびSR-と表されることがあります。SR+は「立ち上がり(positive transition)のスルー・レート(slew rate)」の略、SR-は「立ち下がり (negative transition)のスルー・レート」の略です。多くのアプリケーションでは、SR+とSR-が同じ大きさになる場合に最高のパフォーマンスが得られます。

ほとんどのオペアンプでSRを制御する主な要因となるのは、オペアンプをユニティ・ゲイン安定にするために追加される内部補償キャパシタです。ただし、すべてのオペアンプが補償キャパシタを備えているわけではないことを覚えておく必要があります。内部補償キャパシタのないオペアンプでは、SRは内部オペアンプの寄生容量によって決まります。通常、非補償型の(noncompensated)オペアンプでは、不完全補償型の(decompensated)オペアンプよりも高速のSRを示します。また、不完全補償型のオペアンプでは、完全補償型の(fully compensated)オペアンプよりも高速のスルー・レートを示します。非補償型または不完全補償型のオペアンプを使う場合、設計者は外付け部品で回路の安定性を確実にする必要があります。

図 10. スルー・レート

## 5. ノイズとビット

予想がつくことですが、ノイズはバッファ・オペアンプと ADCを結合したパフォーマンスを劣化させます。このセク ションでは、その劣化について説明します。

ノイズを表現する方法は、オペアンプのデータシートに よって異なります。残念なことに、これらのノイズ仕様は 重複することもあります。

- 1つは、帯域幅の関数としてノイズ仕様を指定します。ホワイト・ノイズ (白色雑音) 特性をnV単位または $\mu V/\sqrt{Hz}$ 単位で表し、どちらも一定の値となります。

- もう1つは、グラフを使ってノイズ仕様を指定します。上 記の方法では、グラフの中で一定値であるホワイト・ノイ ズ部の仕様しか指定できず、低い周波数 – グラフの中で、 周波数の逆数 (1/f) に比例してノイズが急速に増加するピン ク・ノイズ部では無効になります。図11に、オペアンプの ノイズのグラフを示します。

- 最後は、これらを結合し、全高調波歪み (THD) + ノイズ の仕様で表します。

ノイズを指定する最適な方法を決定するのは設計者の責任です。一般的に、帯域幅が広い場合は上記の最初の方法がベストでしょう。独立したTHDの仕様の記載がないとしても、THD+ノイズで表現すればおそらくノイズの方が優勢になります。帯域幅が狭い場合にはノイズからの寄与が大幅に少なくなるため、THD+Nでの仕様も有効になると思われます。

#### 5.1 グラフから読み取るノイズ

設計者はなるべく、関心対象の帯域幅と重複する1/fノイズ特性を持たないオペアンプを選択する必要があります。

図11を見ると、周波数の値が100Hzより高い領域では、ノイズが周波数に対して比較的一定ですが、100Hzより低い領域ではノイズが急激に(指数関数的に)増加しています。ノイズが検討事項である場合は、100Hzより低い周波数でこのオペアンプを使うことはできません。AC結合されてい

るアプリケーションは多いので、ノイズのブレークポイントが関心対象の周波数範囲より低い領域にあるオペアンプを選択することは可能です。

## 5.2 nVまたはμV/√Hz仕様から読み取る ノイズ

オペアンプのノイズ仕様はデータシートに記載されています。ノイズ仕様の数値は通常、nV /\Hz単位で表されます。

関心対象の帯域幅より低い1/fノイズ部を持つオペアンプを選択していれば、ノイズ総量をノイズ仕様から計算することができます。設計者は、システムの帯域幅を知っている必要があります。この帯域幅とは、「オペアンプの通す最高周波数」から「オペアンプの通す最低周波数」を引いた値のことです。

ここで、低い周波数領域でのノイズのブレークポイントが 10Hz、ノイズ仕様が8nV/√Hz、そして使用される周波数範 囲が20Hz~20kHzのオペアンプがあると仮定してください。

- まず、ノイズのブレークポイントとなる10Hzは関心対象の周波数範囲の下限よりも低いため、帯域幅内の周波数全体が一定値のノイズ仕様8nV/√Hzであると仮定できます。

- 次に、ルートヘルツ部を計算します。√20000-20 = 141.35

- 上の結果にノイズ仕様をかけます。 8×141.35 = 1.131μV

これが「等価入力ノイズ(EIN)」です。出力ノイズは、入力ノイズにゲインをかけたものと等価になります。ADCと結合するのは、もちろん出力ノイズです。

システム中のノイズ源は、オペアンプのノイズだけでは ない可能性があります。他のノイズ源としては、フィルタ リング、オフセット、信号処理等を行う前段から入ってく るノイズがあります。各ノイズ源は、根二乗和の法則に 従って次のように加算されます。

$$E_{rms} = \sqrt{e_{1rms}^2 + e_{2rms}^2 + ... e_{nrms}^2}$$

(8)

計算の前に、ノイズ源と思われるすべての要素からの寄 与を考慮に入れてください。

図 11. 標準的なオペアンプのノイズ特性

#### 5.3 全高調波歪み (THD) + ノイズ

「全高調波歪み+ノイズ(雑音歪み率)」、略してTHD+Nというオペアンプ・パラメータは、「ノイズ電圧のRMS値+基本信号に対する高調波成分電圧のRMS値の、出力での基本信号電圧のRMS値に対する比率」と定義され、dBcまたは%単位で表されます。

dBcとは、単独のdB同様によく使われる、可変の基準をもつ相対的な言葉です。つまり、ある搬送波(carrier)レベルを基準とするdBという意味です。例えば「-50dBcより小さいスプリアス信号」とは、ある特定の搬送波レベルよりも、少なくとも50dB小さいスプリアス信号ということになります。(また、所要の信号よりも50dB小さいという意味でもあります)

THD+Nでは、出力信号の周波数内容を入力の周波数内容と比較します。入力信号が純粋なサイン波である場合は、出力信号も純粋なサイン波になるのが理想的ですが、オペアンプ内部の非線形性とノイズ源のために、出力が純粋になることはありません。

言い換えればTHD+Nとは、「基本周波数に対する、他のすべての周波数成分の比率」です。

$$THD + N =$$

$\left[ \frac{\sum 高調波電圧 + ノイズ電圧}{基本信号} \right] \times 100\%$  (9)

通常、THDを低くするには、オペアンプを推奨動作条件 以下で動作させる必要があります。

残念なことに、THDがこのようにノイズと結合した場合に設計者に残される選択肢は、nVまたは $\mu V/\sqrt{Hz}$ 仕様から THD+N仕様に換算されたノイズを加算することしかない可能性があります。

幸いこの2つの仕様は無相関であるため、根二乗和法に従って次のように加算されます。

$$E_{rms} = \sqrt{e_{1rms}^2 + e_{2rms}^2 + ... e_{nrms}^2}$$

(10)

#### 5.4 信号 - ノイズ比(SNR)

このセクションのタイトルが、そのままこの仕様の説明になっています。この仕様には、ADC側からと同様に、インターフェイスのオペアンプ側からも取り組むことが可能であり、2つのパフォーマンスは一致します。実際には、ADCのパフォーマンスを制限しないように、オペアンプの信号-ノイズ比はADCの信号-ノイズ比よりもずっと良好でなければなりません。

現在のノイズ・レベルが分かっていると仮定すると、ノイズ・レベルで信号レベルを割った値が信号-ノイズ比になります。両方ともdB単位で表せば、信号レベルからノイズ・レベルを引くだけで信号-ノイズ比の値が得られます。

ADCの信号-ノイズ比は次のように、コンバータのビットに関しても決定できます。

SNR dB =

$$6.02 \times n - 1.76$$

(11)

または

$$n = \frac{SNR \, dB + 1.76}{6.02} \tag{12}$$

式(12)は、アプリケーションに必要なコンバータのビット数の概算です。これは正弦波信号のみに有効であり、またコンバータでは積分非直線性誤差(INL)が0、微分非直線性誤差(DNL)が0であることを前提としています。データ・コンバータのビット vs. SNRの数値を得るために、次のようにシンプルな表を作ります。

| ビット数 (n) | SNR (dB) |  |

|----------|----------|--|

| 4        | 22.32    |  |

| 8        | 46.4     |  |

| 10       | 58.44    |  |

| 12       | 70.48    |  |

| 14       | 82.52    |  |

| 16       | 94.56    |  |

| 18       | 106.6    |  |

| 20       | 118.64   |  |

| 22       | 130.68   |  |

| 24       | 142.72   |  |

表 2. SNR vs コンバータのビット

#### 5.5 SINAD

全高調波歪み+ノイズ (THD+N) 仕様が分かれば、それを 利用してSINADを計算できます。以下、順を追って簡単に SINADを紹介します。

SINADは、信号の質を表すために用いられる性能指数です。基本的にはオーディオ信号中の、ノイズと高調波が原因で発生する歪みの基準です。SINADの数式の一般式は次のとおりです。

SINAD =

$$\frac{\sum (全周波数成分)}{\sum (全周波数成分 - 基本成分)}$$

(13)

変調された信号のSINADを計算するには、まず基本信号を除去します。次に、この基本信号を除去した後のパワー・スペクトルのRMS値に対する、残ったパワー・スペクトルのRMS値をデシベル単位にします。信号の全要素に対する、ノイズ+高調波歪みの比がSINADです。

SINADは、次のように定義されることもあります。

SINAD = SNR + D =

$$\frac{\text{信号 + THD + N}}{\text{THD + N}}$$

(14)

SINAD (Signal to Noise And Distortion (信号 対 ノイズおよび歪み))という名前はこれに由来します。

注:これらの数値はスカラーであり、dB単位ではありません。

要約すると — SNRとは、基本信号のエネルギーと、ノイズ中のエネルギーの比率です。全高調波歪み (THD) は、高調波のエネルギーと基本信号のエネルギー間の同様の比率です。

#### 5.6 有効ビット数 (ENOB)

どのコンバータも、一定のビット数を持っています。前出の表2には通常のビット数を示してあります。コンバータのパフォーマンスを低下させる限界はコンバータ自体にもありますが、これらについては次のセクションで説明します。バッファ・オペアンプのSNRとTHDは、ADCの変換システムのパフォーマンスを低下させ、システムのデータ処理要素に提供できる、有効な情報ビット数を減らします。

SINADでは高調波とノイズ・エネルギーを考慮するので、 有効ビット数 (effective number of bits, ENOB) を導き出す 真のSNRを作り出します。ENOBの定義は次のとおりです。

ENOB =

$$\frac{[(SINAD dB) - 1.76]}{6.02}$$

(15)

データ・コンバータの仕様では、SNR+DかTHD+NのどちらかをdB単位で記載しています。これにより、この式が使いやすくなります。これに対してアンプの仕様では通常、SNR+DかTHD+NをdBではなくパーセントで指定します。同じ式を利用するには、数学的な操作をいくらか加える必要があります。

パーセントをdBに変換する方法は簡単です。例えば、次の手順はTHD+N%をTHD+NdBに変換するためのものですが、SNR+DまたはSINADをパーセントからdBに変換する場合にも同じ手順が使えます。

$$\frac{\text{THD} + \text{N}\%}{100} = \text{THD} + \text{N}$$

(16)

その後、次のようにします。

$$20 \log (THD + N) = (THD + N) dB \tag{17}$$

図 12. SNRとTHDのビジュアル表現

これらをひとつの数式にまとめると、

$$20\log_{10}\left(\frac{\text{THD} + \text{N}\%}{100}\right) = (\text{THD} + \text{N}) \text{ dB}$$

(18)

上のようになりますが、途中にスカラ数の手順を入れると役に立つことがよくあります。数式(16)もまたスカラ数で記述されるからです。この式をdB単位で使うには、次のことを覚えておいてください。

$log B^A = A \times log B$ したがって、 式 (14) をdB単位で表すと次のようになります。

SINAD

$$dB = SNR + D dB = (THD + N dB)^{-1}$$

=  $- (THD + N) dB$  (19)

パーセントとdBの間で変換を行う方法を利用すると、アンプとADC間で適切なSINAD仕様の整合をとる作業が簡単になります。 理想的には、同じSINADを持つアンプとADCを選択するとシグナル・チェーンの全潜在能力を引き出すことが可能になります。 実際にはADCよりもわずかに高いSINADを持つアンプを選べば、そのアンプを使ってもシステム性能が低下しなくなることが確実になります。

例えばTLV1572 ADCのSNR+Dは通常58dBですが、これは 9.35ビットのENOBに相当します。TLV2770のようなアンプは、このADCを駆動するのに最適の選択です。TLV2770は、入力信号に大きなゲインを与えるために、十分すぎるほどのGBP (通常5.1MH) を持っています。また、TLV2770のデータシートの後ろに記載されたTHD+Nのグラフは、電源電圧が比較的高いことと信号ゲインが高いことを除いては、ほとんどすべての場合にTLV1572のパフォーマンスと整合が取れます。

#### 5.7 ADCのビット

$V_{CC}$ レベルによって異なるADC仕様のひとつが、最下位 ビット (LSB) のサイズです。このことは、次の式で明らか

$$1LSB = \frac{Vfullscale}{2^{N} - 1}$$

(20)

になります。

ここで、n=ADCの分解能です。

12ビット (ENOB) ADCの場合、フルスケール範囲が5Vから3Vに下がると、1LSBのサイズが1.22mVから732 $\mu$ Vに減る結果になります。 $V_{CC}$ 範囲が2.7~5.5VであるTLV1572 (10 ビット) のようなADCの場合は、LSBサイズの範囲が5.37mV~2.64mVになる結果となります。ここで特に注意すべきなのは、システムを低い電圧に移動させる場合に、システムの寄生成分の影響を受けやすくなるポイントまでLSBが低下しないということです。

ADCは完璧な部品ではありません。その精度に影響する 誤差もあります。これらの誤差は最下位ビットに影響を与 え、最終的なシステム精度に対する制限として働くことに なります。

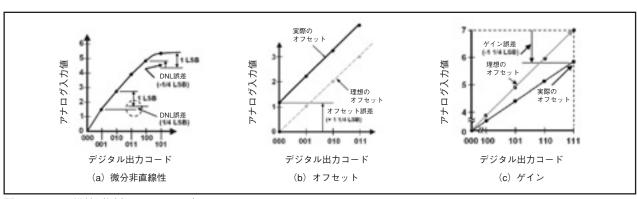

これらの誤差は次の3つのタイプに分けられます。

- 微分非直線性誤差。入力電圧のステップ·サイズと出力 コードの各変化が一致しない。(図13(a))

- オフセット誤差。入力電圧がすべて理想値より上か下の 固定値になっているために、出力コードに変化が生じて いる。(図13(b))

- ゲイン誤差。デジタル・コードを発生させる電圧変化が、 理想のゲイン/出力コード関数より下か上になっている。 累積誤差である。(図13(c))

ADCのデータシートでは通常これらの誤差原因を加算し、総計として表現します。この仕様を「ADCの積分非直線性 (INL)」と呼びます。これらの誤差原因とそこから予想される影響を理解することは、設計者の責務です。データ・コンバータではINLが0ビットであることが理想的ですが、実際にはデータ・コンバータがENOBにまで性能低下する以前に、INLが1/2ビット程度の大きさを持つ可能性があります。1/2ビットより大きいINLが許容されるのは、誤差の原因がAC結合システムにおけるオフセットである場合だけです。最下位ビットを捨てることでINL誤差が除去できるように、設計者は当初予定していたよりもビット数の多いADCを指定する必要があるかもしれません。

変換周波数が増加するにつれて、ENOBは減少していきます。その理由は明らかです - 変換は可能な限り短いセトリング時間で行う必要がありますが、セトリング時間が短くなるほど入力電圧の値は予測しにくくなるためです。

図 13. ADCの誤差原因(Error Sources)

図 14. アンプ - ADC間のインターフェイス

#### 5.8 ADC入力

図14は、ADCの入力を駆動するオペアンプの例です。設計者にはおそらく、ADCの入力が単極のローパス・フィルタであることが分かるでしょう。高速のデータ・コンバータは、 $500\Omega$ ~ $1M\Omega$ という広範囲な $R_{ADC}$ や、1~5pFの入力容量を持つ可能性があります。回路の帯域幅は主にこれらの要素によって決まります。図14は必ずしも、この容量が切り離されていることを示しているわけではありません -  $R_{ADC}$ とともに与えられるものであり、したがってその場合はバッファ・オペアンプの出力に現れます。不都合なことに、容量はたとえ値が小さくてもバッファ・オペアンプ段に不安定性を生じさせるおそれがあるため、切り離しと補償が必須になります。

高性能ADCの多くは、差動入力を備えています。この場合、各入力の入力特性はシングル·エンド入力の特性と同様になります。

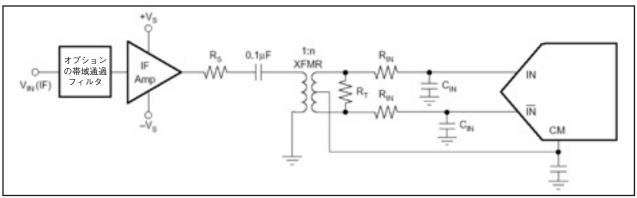

図15に示すようなトランスと結合させる方法の代わりに、 完全差動オペアンプを使うこともできます。

図16のような完全差動インターフェイスには、次のよう に重要な特色がいくつかあります。

- この例ではシングル·エンドの入力電圧V<sub>IN</sub>が、完全差動 オペアンプによって差動出力に変換されています。

- ・ 完全差動オペアンプの同相動作点  $(V_{OCM})$  は、ADCの $V_{ref}$  出力によって設定されます。設計者は、データ・コンバータの $V_{ref}$ 出力を過負荷にしないように特に注意する必要があります。 $V_{ref}$ 出力が大きな負荷を駆動するように設計されていない可能性があるためです。上記の例ではまた、 $V_{ref}$ 出力がキャパシタでバイパスされています。データ・コンバータは、 $V_{ref}$ 出力と $V_{ref}$ 出力を備えることがありますが、これらはオペアンプ・バッファを使用してシングル・エンドに変換できます。

図 15. 基地局アプリケーションの例

図 16. ADCへの完全差動入力

• 各入力に付けた $R_{\rm IN}$ と $C_{\rm IN}$ から構成される、ローパス・フィルタの回路があります。関心対象の帯域幅の振幅に影響を与えずに高周波干渉を取り除く単極ローパス・フィルタを作るために、値を選択します。単極フィルタは-3dBポイントの前で振幅を大幅にロールオフ(減衰)させるため、-3dBポイントをサンプル周波数の $2\sim5$ 倍の位置までずらします。このようにすると、関心の対象となる帯域幅の振幅のロールオフ(減衰)を無視できます。 $R_{\rm IN}$ はまた、オペアンプの出力を容量性負荷から切り離す働きもします。そうしないと、容量性負荷のためにオペアンプの出力が不安定になります。 $R_{\rm IN}$ は通常、2つの抵抗間で終端値を分割して、ADCの入力を $50\Omega$ で終端処理するために選択されます。

#### 5.9 駆動電流

アンプからの駆動電流も、ADCのアナログ入力を駆動する際の考慮事項のひとつです。ADCの通常の入力抵抗には、500Ω~1MΩ超という大変な幅があります。RFの設計者はdBm単位でRFレベルを扱うのに慣れています。入力抵抗が500のデータ・コンバータに必要な入力電力(input power)は1dBmの範囲内になりますが、それが設計者の意図でない場合には、ADCに前述のRCローパス・フィルタが付加された上に、ADCでオペアンプ出力をロードすることもできます。簡単にいうと、オペアンプ出力上の直列抵抗とADC入力を使って分圧器を形成するということです。

ここで設計者が直面するのが、直列抵抗の許容誤差、およびADC入力抵抗の絶対値の不確定性によって、精度の損失が発生するという問題です。

この問題の対処法は2つあります。ひとつはRCローパス・フィルタを完全に削除し、潜在的な高周波干渉とADCの入力容量を受け入れるというものです。この2つはオペアンプを不安定にするおそれがあるため、明らかに望ましくない方

法です。

もうひとつは、自動較正のテクニックを使ってこれらの 許容誤差を補償するというものです。ADC変換範囲の上限 と下限での変換の数ビットを犠牲にします。これは入力信 号がAC結合され、DC精度は重要な問題にならないことを 前提とします。

#### 5.10 再びスルー・レートについて

ADCの入力そのもの、および補償ローパス・フィルタとともに使用するADCを扱う場合には、RC時定数に関連する立ち上がり時間が問題になります。これらの問題は「スルー・レート」のセクションで述べたように、スルー・レートの制限という形で現れます。ただし本論では、スルー・レートに影響するオペアンプ以外の部品 -- 補償ローパス・フィルタと、ADC入力について述べます。キャパシタは駆動電圧で充電されるため、スルー・レートはキャパシタの影響を受けます。

この充電時間は次の式で計算されます。

$$V(t) = V_O e^{-(t/RC)}$$

(21)

ここで、

V。はキャパシタの電圧Vの定常状態です。

$t=-\infty$ から t=0までの間、電圧源  $(V_s)$  が安定していると 仮定すれば、 $V_o=V_s$ であると判断できます。 簡単に説明すると、DC定常状態では、キャパシタは開回路と同じように 動作するため、 $V_s$ と同じ電圧になります。

解析をさらにシンプルなものにするために、ここで $V_s$ が 既知の電圧からグラウンドに切り替わると仮定します。2つ の分圧式を解いて、簡素なRC回路をひとつ作ります。

図 17. 回路の簡素化

直感的に分かることですが、電流が最大になるのはt=0の場合、つまり電位が切り替わる瞬間です。一方、電圧は時間とともに指数関数的に下がります。そこで、アンプでの処理が必要な電流のおよその最大値は、次の式で計算できます。

$$I = \frac{V(t)}{R}$$

22%,  $t = 0$  (22)

例えば、入力RC回路を持たないADC製品であるTLV1544を使用した場合、概略値は $R = 1k\Omega$ およびC = 55pFとなります。次に、ADC上の入力抵抗が与えられるので、時定数 $\tau$ を計算できます。TLV1544への最大入力電圧が3Vであれば、アンプが処理する必要があるのは約3 mAになります。

#### 5.11 セトリング時間

入力抵抗が高い場合は、負荷特性はADCの入力容量が支配的になります。ADCの入力容量からオペアンプの出力を切り離すために前述のローパス・フィルタは必須ですが、容量性負荷がオペアンプの出力上にオーバーシュートを発生させるため、ADC入力でセトリング時間に関わる問題が起こります。

図18は、オペアンプ/ADCインターフェイスの複雑な性質を示しています。次のような、注意すべき点がいくつかあります。

• ADCの出力段の動作が原因で、電圧レベルが急激に上がる(グリッチする)可能性があります。適切なデカプリング技法を用いれば、この影響を減らすことができます。

- インターフェイス全体のスルー・レートは、アナログ電圧 をどれだけ短時間でサンプリングできるかに影響します。

- キャパシタの動作によりある程度のリンギングが発生し、 エラー・バンド (エラー帯域) が作りだされます。リンギン グは減衰定数を持つため、電圧は安定してゆきます。

スルー・レートによる電圧変化が終わり、遷移が安定し、 グリッチがおさまるのを待てば、新しくサンプリングを始 められるようになります。

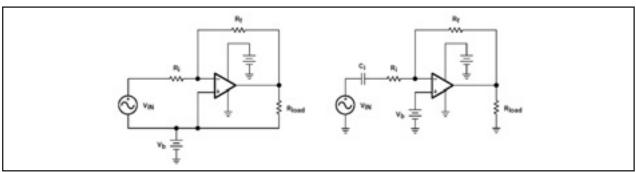

#### 5.12 信号バイアス

入力波形に対して適切な信号バイアスを用いることも、ADCのアナログ入力に関する重要な考慮事項のひとつです。アナログ入力の範囲は、ADCの種類によって違ってきます。

例えば、TLV1572はシングル・エンドのアナログ入力を持ち、電源レールより0.3V超える電圧範囲を持ちます。また、TLV1562では、TLV1572と同様なシングル・エンド入力を持ちますが、異なるモードとして、差動入力(約2Vpp)で動作させることもできます。 さらにTLC320AD50のようなタイプのコンバータでは、完全差動入力の構造が用いられています。アナログ入力電圧範囲がどのようであるかを理解すれば、設計者は入力信号の増幅やバイアスを正しく行い、ADCのダイナミック・レンジを最大限に利用することができます。

アナログ入力信号に適切にバイアスをかけるための回路はたくさんあります。図19には、1998年のTIアナログセミナーで検証された、バイアス回路が2つ示されています。どちらの回路でも、単一電源アンプの電源レール中間でAC入力信号にバイアスをかけます。

図 18. セトリング時間の限界

図 19. 入力信号バイアス回路

図19の左側の回路は、明らかに使えません。電源と負荷の両方がグラウンド以外の電位を基準とするのは、おそらく不可能であるからです。図の右側の回路では、電位 $V_b$ はカップリング・キャパシタ $C_{i,}$ により、 $V_{IN}$ から切り離されますが、負荷 $R_{load}$ 上に現れます。

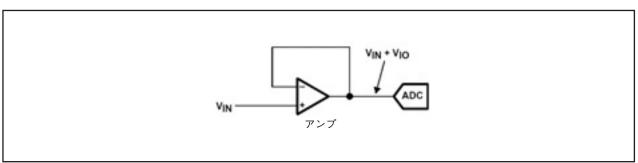

#### 5.13 入力オフセット

入力オフセット電圧  $(V_{IO})$  も、アンプ選択の際に考慮すべきパラメータです。単純なバイアシング用やバッファリング用のアプリケーションでさえ、アンプにはDC誤差が発生します。DC誤差はアンプの入力に伴う電圧差によって発生するもので、データシート上では $V_{IO}$ で示されます。

アンプに関するもうひとつの重要な入力誤差は、入力バイアス電流 $I_{\rm IB}$ です。入力バイアス電流は、アンプの入力信号が比較的小さい電流で表されている場合には、重大な誤差になるおそれがあります。例えばある種のセンサを使った場合に、そうなる可能性があります。たいていの場合、入力バイアス電流よりもDC誤差 $V_{\rm IO}$ の方が容易に視覚化できますが、入力電流の誤差も、アプリケーションでの分解能誤差に多大な影響を与える可能性があります。一般的には、データ・コンバータ上のILSBのサイズを基準として、この両方の誤差を合わせたサイズを常に0.5LSBより低くしておくとよいでしょう。

## 6. 雷源

当然のことながら、設計で使用するデバイスはボード上で使用される電圧に耐えて、その電圧で動作できなければなりません。その点は明白ですが、それほど明白でないために調査が必要な点もあります。電源プレーンとグラウンド・プレーン、入力/出力電圧範囲、ADC上の1LSBのサイズなどです。

#### 6.1 電源プレーンとグランド・プレーン

1つのボードには、アナログ用とデジタル用のグランド・プレーンが1つずつあるのが理想的です。こうすると、アンプのような高感度アナログ回路を、デジタル回路に付き物

のスイッチング・ノイズから隔離しやすくなるためです。アナログ電源とグランド・プレーンを別々に用意できない場合には、電源変動除去比 (PSRR) の仕様を見れば、電源ノイズが原因で発生する可能性のある問題を特定できます。TLV2450のように新しいアンプ製品の場合、データシートの後ろにPSRR vs 周波数のグラフが記載されていることが多いのですが、設計者が電源レール上に生じているノイズの周波数特性を理解している場合にはこのグラフが役に立ちます。

#### 6.2 入力/出力電圧範囲

どの $V_{CC}$ を選択しても影響を受ける可能性のある要素としてはもうひとつ、アンプの入力/出力電圧範囲があります。比較的最近まで、大部分のアンプでは正・負の電源電圧の限界までスイングできるような入力/出力を持っていませんでした。たとえば、TLC2272ではレール・ツー・レール出力(RRO)を提供していますが、レール・ツー・レール入力(RRI)は提供しておらず、TLC2272では入力の正電源電圧に1.5Vのヘッドルームを持ちます。したがって、電源電圧が10Vの場合、TLC2272の入力範囲はGND~8.5Vとなります。同様に $V_{CC}$ が5Vの場合にも、TLC2272には1.5Vのヘッドルームがあり、入力範囲はGND~3.5Vとなります。

アンプが発展した結果、レール・ツー・レール入力および出力(RRIO)式のアンプという革新的な製品が出現しました。TLV2462もそのひとつです。RRIOアンプでは、信号が正・負の電源電圧の限界までスイング可能であり、したがって入力または出力のヘッドルームがなくなります。このことは、低電圧アプリケーションでは特に重要です。低電圧アプリケーションでは、設計者が使える入力/出力範囲が狭くなるからです。ただし、RRIを使うとコストが高くなります。また現時点では、レール・ツー・レール入力段を構築するとクロスオーバ歪みが取り込まれます。歪みの影響を受けやすいアプリケーションで特殊なアンプを使おうとする場合、設計者はオペアンプのベンダに相談したりデータシートを見たりして、適合性を判断する必要があります。

図 20. 入力オフセット電圧(V<sub>IO</sub>)

## 7. 要約

本論では、オペアンプでADCのインターフェイスをとる 場合に考慮すべき様々な問題について簡潔に述べています。 これらのことを念頭においておけば、多くの選択肢にも 迷うことなく、ADCに対するインターフェイスとして申し 分なく動作し、かつシステム性能を最適化するような部品 を容易に見つけることができるはずです。

(簡略版チェックリスト)

- 帯域幅 アンプのGBP vs ADCの速度

- 分解能 アンプのSINAD vs ADCのENOB

- アナログ入力 τ および駆動電流、入力信号 vs ADCのア ナログ入力範囲

- 電源 アンプのPSRR、アンプのI/O電圧範囲、ADCの LSB

## 8. 参照文献

- Electric Circuit Analysis Second Edition, by Johnson, Johnson, and Hilburn Copyright 1992, Prentice Hall, Englewood Cliffs NJ

- DSP/Analog Technologies 1998 Seminar Series, by Texas Instruments Incorporated Copyright 1998

- 3. Op Amps for Everyone, Ron Mancini, Editor, Texas Instruments SLOD006, Copyright 2000

- 4. Intuitive Operational Amplifier, Thomas M. Frederickson, McGraw Hill, Copyright 1988

## 付録A: 設計例 -- 携帯電話の基地局

#### ADCに関する検討事項

携帯電話基地局の設計のパフォーマンスについて考察する場合は必ず、中間周波数 (IF) の帯域幅をデジタル化するために使用されるデータ・コンバータのパフォーマンスに重点を置く必要があります。

基地局のRF性能がどのようなものになるかは、正しいデータ・コンバータを選択するかどうかでだいたい決まります。したがってデータ・コンバータの選択は、設計者がオペアンプのインターフェイスの設計を始めるずっと前に行われるのが普通です。設計者は、オペアンプのインターフェイスがシステム性能全体の制限要因として機能するようなことが絶対ないようにしなければなりません。

通信ADCでは、DC非直線性のパフォーマンスは計測ADC の場合ほど重要にはなりません。信号に帯域制限があるためです。ADCの動的性能は、通信アプリケーションでは決定的に重要な意味を持ちます。レシーバ・システムの仕様全体は、ADCの動的性能に大きく依存します。データ・コンバータの特性には、次のようなものがあります。

- 有効ビット数(ENOB) 通常はシステムの動作周波数に 対して測定・指定されるため、本当の意味での性能評価と なります。

- スプリアス・フリー・ダイナミック・レンジ (SFDR) ADC の、ノイズ・スパイクから着信信号を分離するための機能 は、この特性によって決まります。

- 全高調波歪み (THD) ADCが信号に付加する歪みの指標 となります。

- 信号-ノイズ比(SNR) ADCのノイズと、他のノイズ源からのノイズの両方が含まれます。

- サンプリング・レート

- フルスケール範囲 (FSR)

### GSM信号処理のADC要件

携帯電話基地局のデータ・コンバータ要件は、選択された 通信プロトコルにも依存します。最も一般的な通信プロト コルは、CDMAとGSMの2つです。この例ではGSMに重点 を置いて説明します。

GSM仕様を詳細に論じることは本論の範囲を超えていますが、主要な点は次のようなものです。

- SNR<sub>THERMAL</sub> = GSM-900の場合は9dB

- 必要なプロセス·ゲイン = 24dB (fS/BW)

- 選択されたADC<sub>SNR</sub> = サーマル・ノイズ (熱雑音) より37dB 高い

- ベースバンドのコンバータ = 46dB SNR

- $SNR_{ADC} = (46 24) = 22 dB$

- ENOB (有効ビット数) = (SNR-1.76) / 6.02 = 3.36ビット の信号(4ビットが必要)

- 干渉信号 = 40 dB ≈ 6.3ビット

量子化電力の二乗平均は  $P_{qn} = q_s^2/12R$  です。ここで、 $q_s$ は量子化のステップ・サイズ、RはADCの入力抵抗 (通常は600 $\Omega$ ~1000 $\Omega$ ) です。THS1052やTHS1265のような通信用ADCでは通常、フルスケール範囲が1Vpp~2Vpp(FSR)です。入力/出力終端が50 $\Omega$ と仮定すると、12ビットで65MSPSのADCの量子化ノイズ電力は-74dBmになります。ノイズ制限のあるレシーバ(受信機)でのレシーバ・ノイズ電力は、「任意のレシーバのBW (帯域幅) + レシーバ・ノイズ指数」でのサーマル・ノイズ電力として計算できます

帯域幅200kHzのGSMチャネルで、 $T_A$  = 25°C、NFが4~6dBの場合、レシーバ・ノイズ電力は-115dBmです。レシーバ・ノイズ電力を量子化ノイズ電力のレベルまで引き上げるには、42dBのゲインが必要です。GSM-900の最小の1%ビット誤り率 (BER: bit error rate) は-104dBmであり、したがってサーマル・ノイズ成分に起因するベースバンドでのSNRは、SNR<sub>THERMAL</sub> =  $E_b/N_o$  = -104 dBm +115 dBm = 9dBmという式で計算できます。GSMシステムでの生のBERが1%の場合にテスト曲線と標準曲線を見れば、このパフォーマンスには9dBのベースパンドSNRが必要であることが分かります。

プロセス・ゲインは、 $G_p = f_s/BW = 52 \times 10^6 / 200 \times 10^3 = 2.6 \times 10^2 = 24 dB$ となります。この場合、GSMのチャネル帯域幅 (BW) は200kHzであり、 $f_s$ は52MHz (ADCサンプル周波数) です。ベースバンドでのコンバータのノイズは、電波ノイズ (サーマル・ノイズ+プロセス・ゲイン) よりもずっと良好であるはずです。したがって、ベースバンドでのコンバータのノイズ= SNR\_{ADC} + プロセス・ゲイン ( $G_p$ ) となります。

$SNR_{ADC}$ は $SNR_{THERMAL}$ よりも37dB大きな値として選択されるので、ベースパンドのコンバータのノイズは9dB+ 37dB = 45dBとなります。GSM-900規格を満たすために必要なSNRADCは、(46-24) dB = 22dBです。ADCのENOBは、= (SNR-1.76)/6.02@4ビットである必要があります。フィルタによって干渉信号が50dB分減衰すると仮定すると、干渉信号は113dBmから-53dBm、つまりGSM信号より40dB分高い値にまで下がります。干渉信号を収容するのに必要なビット数は40dB/6dB/ビット=6.3ビットです。干渉信号を収容するのに6ビット、GSM信号用に4ビット、 $\sim$ ッドルーム用に2ビットを要するため、必要なのは12ビット・コンバータであることが分かります。

| パラメータ     | 值           | OPA685 | 単位                     |

|-----------|-------------|--------|------------------------|

| ノイズ電圧     | 2.7 to 8    | 2.7    | nV $/\sqrt{\text{Hz}}$ |

| ノイズ電流     | 1 to 30     | 11.9   | pA /\sqrt{Hz}          |

| THD       | 70 to 95    | 82     | dBc                    |

| スルー・レート   | 260 to 3500 | 1700   | V/μS                   |

| 小信号帯域幅    | 200 to 600  | 900    | MHz                    |

| 大信号帯域幅    | ≥100        | 135    | MHz                    |

| 同相入力電圧    | 3           | ±2.9   | V                      |

| 電源電圧      | ±5          | ±5     | V                      |

| セトリング時間   | 8 to 20     | 15     | nS                     |

| 出力電流      | 40 to 100   | 80     | mA                     |

| 出力インピーダンス | ≤20         | 0.02   | Ω                      |

| PSRR      | -60         | -64    | dB                     |

| CMRR      | -70         | 50     | dB                     |

| 入力オフセット電圧 | 10          | ±5     | mV                     |

表 3. オペアンプ要件

SFDRとIMDは、オペアンプの選択に影響を与える非常に重要なADC/DACパラメータです。最低限の要件は「オペアンプ側のSFDRまたはIMDを動作周波数で測定した場合、そのSFDRまたはIMDはコンバータ側の同じ仕様よりも5dB~10dB分高くなる」というものです。完全な12ビットADCのSFDRまたはIMDは72dBですが、そのオペアンプのSFDRまたはIMDは77dB~82dBでなければならないということです。ADCではサンプリング時間内に、データをLSBの何分の1かの範囲内に安定させる必要があるため、高速のセトリング時間が必須となります。

現在では低電圧システムが広く普及しているため、設計者は、AC仕様がテスト電源電圧でのみ有効であることに注意する必要があります。異なる電源電圧でオペアンプを動作させることは、電源電圧のAC仕様が変わることを意味するからです。

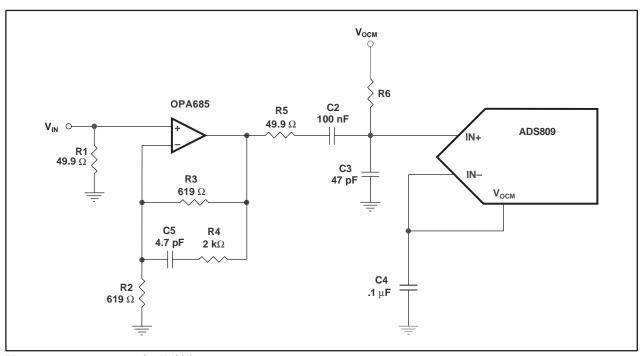

図21は、ADCバッファ・オペアンプの設計例です。入力は R1 (抵抗49.9 $\Omega$ ) で終端処理されています。OPA685は電流帰還アンプであり、(R3とR2に設定された) 非反転ゲイン2によって動作します。C5とR4は補償部品です(電流帰還アンプの帰還部に直接キャパシタを置くことは絶対にやめてください)。アンプの出力と直列になっている49.9 $\Omega$ の抵抗(R5) は、接地した47pFのキャパシタ(C3)と結合して、ADCの入力容量の補償となります。R5はまた、アンプの出力を容量性負荷から切り離します。C2はアンプの出力をAC結合し、 $V_{OCM}$ につながるR6は入力電圧にバイアスをかけて、コンバータの同相範囲と同じにします。その値は、決定的に重要なものとはなりません。

図 21. バッファ・オペアンプの設計例

# ご注意

日本テキサス・インスツルメンツ株式会社(以下TIJといいます)及びTexas Instruments Incorporated(TIJの親会社、以下TIJないしTexas Instruments Incorporatedを総称してTIといいます)は、その製品及びサービスを任意に修正し、改善、改良、その他の変更をし、もしくは製品の製造中止またはサービスの提供を中止する権利を留保します。従いまして、お客様は、発注される前に、関連する最新の情報を取得して頂き、その情報が現在有効かつ完全なものであるかどうかご確認下さい。全ての製品は、お客様とTIJとの間に取引契約が締結されている場合は、当該契約条件に基づき、また当該取引契約が締結されていない場合は、ご注文の受諾の際に提示されるTIJの標準販売契約約款に従って販売されます。

TIは、そのハードウェア製品が、TIの標準保証条件に従い販売時の仕様に対応した性能を有していること、またはお客様とTIJとの間で合意された保証条件に従い合意された仕様に対応した性能を有していることを保証します。検査およびその他の品質管理技法は、TIが当該保証を支援するのに必要とみなす範囲で行なわれております。各デバイスの全てのパラメーターに関する固有の検査は、政府がそれ等の実行を義務づけている場合を除き、必ずしも行なわれておりません。

TIは、製品のアプリケーションに関する支援もしくはお客様の製品の設計について責任を負うことはありません。TI製部品を使用しているお客様の製品及びそのアプリケーションについての責任はお客様にあります。TI製部品を使用したお客様の製品及びアプリケーションについて想定されうる危険を最小のものとするため、適切な設計上および操作上の安全対策は、必ずお客様にてお取り下さい。

TIは、TIの製品もしくはサービスが使用されている組み合せ、機械装置、もしくは方法に関連しているTIの特許権、著作権、回路配置利用権、その他のTIの知的財産権に基づいて何らかのライセンスを許諾するということは明示的にも黙示的にも保証も表明もしておりません。TIが第三者の製品もしくはサービスについて情報を提供することは、TIが当該製品もしくはサービスを使用することについてライセンスを与えるとか、保証もしくは是認するということを意味しません。そのような情報を使用するには第三者の特許その他の知的財産権に基づき当該第三者からライセンスを得なければならない場合もあり、またTIの特許その他の知的財産権に基づきTIからライセンスを得て頂かなければならない場合もあります。

TIのデータ・ブックもしくはデータ・シートの中にある情報を複製することは、その情報に一切の変更を加えること無く、かつその情報と結び付られた全ての保証、条件、制限及び通知と共に複製がなされる限りにおいて許されるものとします。当該情報に変更を加えて複製することは不公正で誤認を生じさせる行為です。TIは、そのような変更された情報や複製については何の義務も責任も負いません。

TIの製品もしくはサービスについてTIにより示された数値、特性、条件その他のパラメーターと異なる、あるいは、それを超えてなされた説明で当該TI製品もしくはサービスを再販売することは、当該TI製品もしくはサービスに対する全ての明示的保証、及び何らかの黙示的保証を無効にし、かつ不公正で誤認を生じさせる行為です。TIは、そのような説明については何の義務も責任もありません。

TIは、TIの製品が、安全でないことが致命的となる用途ないしアプリケーション(例えば、生命維持装置のように、TI製品に不良があった場合に、その不良により相当な確率で死傷等の重篤な事故が発生するようなもの)に使用されることを認めておりません。但し、お客様とTIの双方の権限有る役員が書面でそのような使用について明確に合意した場合は除きます。たとえTIがアプリケーションに関連した情報やサポートを提供したとしても、お客様は、そのようなアプリケーションの安全面及び規制面から見た諸問題を解決するために必要とされる専門的知識及び技術を持ち、かつ、お客様の製品について、またTI製品をそのような安全でないことが致命的となる用途に使用することについて、お客様が全ての法的責任、規制を遵守する責任、及び安全に関する要求事項を満足させる責任を負っていることを認め、かつそのことに同意します。さらに、もし万一、TIの製品がそのような安全でないことが致命的となる用途に使用されたことによって損害が発生し、TIないしその代表者がその損害を賠償した場合は、お客様がTIないしその代表者にその全額の補償をするものとします。

TI製品は、軍事的用途もしくは宇宙航空アプリケーションないし軍事的環境、航空宇宙環境にて使用されるようには設計もされていませんし、使用されることを意図されておりません。但し、当該TI製品が、軍需対応グレード品、若しくは「強化プラスティック」製品としてTIが特別に指定した製品である場合は除きます。TIが軍需対応グレード品として指定した製品のみが軍需品の仕様書に合致いたします。お客様は、TIが軍需対応グレード品として指定していない製品を、軍事的用途もしくは軍事的環境下で使用することは、もっぱらお客様の危険負担においてなされるということ、及び、お客様がもっぱら責任をもって、そのような使用に関して必要とされる全ての法的要求事項及び規制上の要求事項を満足させなければならないことを認め、かつ同意します。

TI製品は、自動車用アプリケーションないし自動車の環境において使用されるようには設計されていませんし、また使用されることを意図されておりません。但し、TIがISO/TS 16949の要求事項を満たしていると特別に指定したTI製品は除きます。お客様は、お客様が当該TI指定品以外のTI製品を自動車用アプリケーションに使用しても、TIは当該要求事項を満たしていなかったことについて、いかなる責任も負わないことを認め、かつ同意します。

Copyright © 2007, Texas Instruments Incorporated 日本語版 日本テキサス・インスツルメンツ株式会社

## 弊社半導体製品の取り扱い・保管について

半導体製品は、取り扱い、保管・輸送環境、基板実装条件によっては、お客様での実装前後に破壊/劣化、または故障を起こすことがあります。

弊社半導体製品のお取り扱い、ご使用にあたっては下記の点を遵守して下さい。 1. 静電気

- 素手で半導体製品単体を触らないこと。どうしても触る必要がある場合は、リストストラップ等で人体からアースをとり、導電性手袋等をして取り扱うこと。

- 弊社出荷梱包単位(外装から取り出された内装及び個装)又は製品 単品で取り扱いを行う場合は、接地された導電性のテーブル上で(導 電性マットにアースをとったもの等)、アースをした作業者が行う こと。また、コンテナ等も、導電性のものを使うこと。

- マウンタやはんだ付け設備等、半導体の実装に関わる全ての装置類は、静電気の帯電を防止する措置を施すこと。

- 前記のリストストラップ・導電性手袋・テーブル表面及び実装装置 類の接地等の静電気帯電防止措置は、常に管理されその機能が確認 されていること。

#### 2. 温·湿度環境

■ 温度:0~40℃、相対湿度:40~85%で保管・輸送及び取り扱いを行うこと。(但し、結露しないこと。)

- 直射日光があたる状態で保管・輸送しないこと。

- 3. 防湿梱包

- 防湿梱包品は、開封後は個別推奨保管環境及び期間に従い基板実装すること。

#### 4. 機械的衝撃

● 梱包品(外装、内装、個装)及び製品単品を落下させたり、衝撃を与えないこと。

#### 5. 熱衝撃

はんだ付け時は、最低限260℃以上の高温状態に、10秒以上さら さないこと。(個別推奨条件がある時はそれに従うこと。)

#### 6. 汚染

- はんだ付け性を損なう、又はアルミ配線腐食の原因となるような汚染物質(硫黄、塩素等ハロゲン)のある環境で保管・輸送しないこと。

- はんだ付け後は十分にフラックスの洗浄を行うこと。(不純物含有率が一定以下に保証された無洗浄タイプのフラックスは除く。)

以上