TPS92830-Q1

JAJSE12A - OCTOBER 2017-REVISED OCTOBER 2017

# TPS92830-Q1 3チャネル、大電流のリニアLEDコントローラ

# 特長

- AEC-Q100認定済み

- デバイス温度グレード1:動作時周囲温度範囲 -40°C~125°C

- デバイスHBM ESD分類レベルH2

- デバイスCDM ESD分類レベルC4B

- 広い入力電圧範囲: 4.5V~40V

- 3チャネルのハイサイド電流駆動およびセンシン

- チャネル独立の電流設定

- チャネル独立のPWM入力

- PWM入力および電源の両方によるPWM調光

- EMCに対して最適化されたスルー・レート

### 高精度のLED駆動

- 外部NチャネルMOSFETによる高精度の電流レ ギュレーション(許容誤差2.5%)

- 20:1のアナログ調光プロファイルとオフボードのビ ン抵抗サポート

- 完全デューティ・サイクル・マスクを持つ高精度 PWMジェネレータ(許容誤差2%)

- オープン・ドレインのPWM出力による同期

#### 保護および診断機能

- 外付けMOSFETの過熱保護用の可変出力電流 ディレーティング

- LEDストリングの開路または短絡の診断および自 動回復機能

- 診断イネーブルと可変スレッショルドによる低電圧 動作

- 最大15個のデバイスのフォルト・バス、どれか1 つに障害が発生すれば全体を障害とするか、障害 の発生したチャネルのみをオフにするかを選択可

- フォルト・モードでの低い静止電流(デバイスごとに 0.75mA未満)

- 動作時の接合部温度範囲: -40℃~150℃

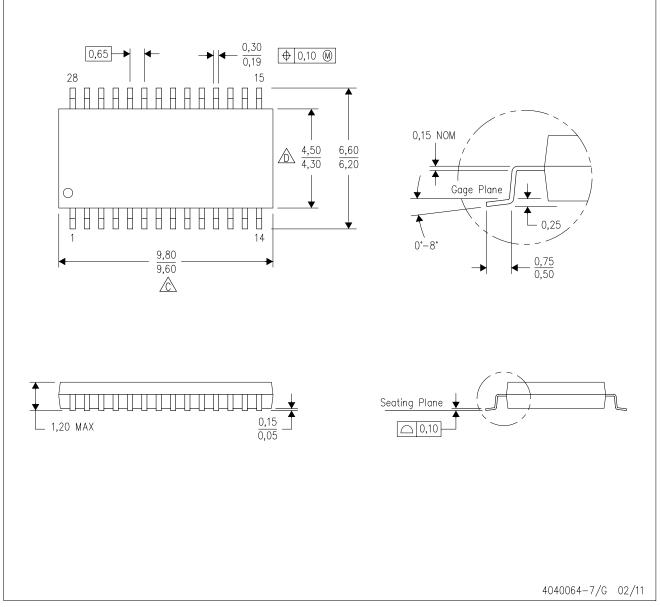

- TSSOP 28パッケージ(PW)

# 2 アプリケーション

- 後方ライト テール・ランプとストップ・ラン プ、後方ウインカー、フォッグ・ランプ、バッ ク・ランプ

- 前方ライト 位置灯、昼間走行灯、前方ウイン カー、ロービーム

# 3 概要

ライトの均一性が求められる傾向から、車載用の前方およ び後方ランプには多くの場合に大電流LEDが、拡散板や 導光板とともに使用されます。その一方で、厳格なEMC および信頼性の要件に合致するため、リニアLEDドライバ が車載用アプリケーションで多く使われています。しかし、 リニアLEDドライバ用の大電流を内蔵のパワー・トランジス タで供給するのは困難です。TPS92830-Q1デバイスは、 外付けのNチャネルMOSFETを使用して大電流を供給す るための、高度な車載グレードのハイサイド定電流リニア LEDコントローラです。このデバイスには、車載用アプリ ケーション向けの完全な機能セットがあり、広範なNチャネ ルMOSFETと互換性があります。

TPS92830-Q1デバイスの各チャネルは、センス抵抗の値 により、独立にチャネル電流を設定します。内蔵の高精度 定電流レギュレーション・ループは、センス抵抗の両端の 電圧によってチャネルの電流を検出し、それに応じて NチャネルMOSFETのゲート電圧を制御します。このデバ イスには、低ドロップアウト動作用の2段のチャージ・ポンプ も内蔵されています。チャージ・ポンプの電圧は十分に高 く、広範なNチャネル MOSFETをサポートできます。

### 製品情報(1)

| 型番          | パッケージ      | 本体サイズ(公称)     |

|-------------|------------|---------------|

| TPS92830-Q1 | TSSOP (28) | 9.70mm×4.40mm |

(1) 利用可能なすべてのパッケージについては、このデータシートの末 尾にある注文情報を参照してください。

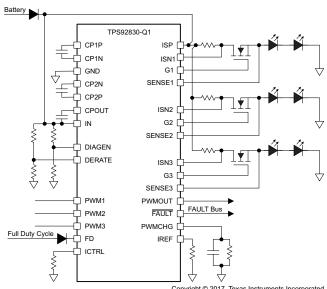

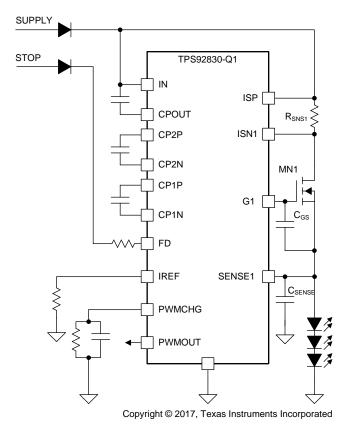

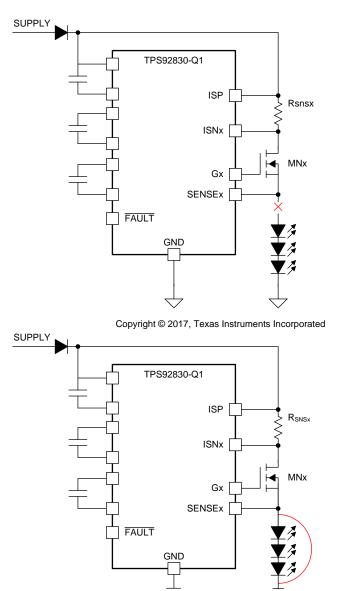

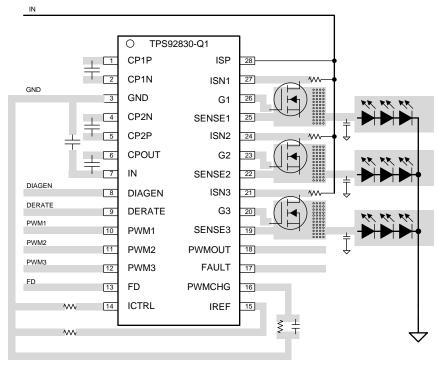

#### 概略回路図

Copyright © 2017, Texas Instruments Incorporated

| ·—         |

|------------|

|            |

| <i>1</i> 人 |

| 1 | 特長1                                            |    | 8.2 Functional Block Diagram   | . 14 |

|---|------------------------------------------------|----|--------------------------------|------|

| 2 | アプリケーション1                                      |    | 8.3 Feature Description        | . 15 |

| 3 | 概要1                                            |    | 8.4 Device Functional Modes    | . 29 |

| 4 | 改訂履歴                                           | 9  | Application and Implementation | 30   |

| 5 | 概要(続き)                                         |    | 9.1 Application Information    | . 30 |

| 6 | Pin Configuration and Functions                |    | 9.2 Typical Applications       | . 30 |

| 7 | •                                              | 10 | Layout                         | 36   |

| ′ | Specifications                                 |    | 10.1 Layout Guidelines         |      |

|   | 7.1 Absolute Maximum Ratings 6 7.2 ESD Ratings |    | 10.2 Layout Example            | . 36 |

|   | 7.2 ESD Ratings                                | 11 | デバイスおよびドキュメントのサポート             | 37   |

|   | 7.4 Thermal Information                        |    | 11.1 ドキュメントの更新通知を受け取る方法        | . 37 |

|   | 7.5 Electrical Characteristics                 |    | 11.2 コミュニティ・リソース               | . 37 |

|   | 7.6 Timing Requirements                        |    | 11.3 商標                        | . 37 |

|   | 7.7 Typical Characteristics                    |    | 11.4 静電気放電に関する注意事項             | . 37 |

| 8 | Detailed Description                           |    | 11.5 Glossary                  | . 37 |

| U | 8.1 Overview                                   | 12 | メカニカル、パッケージ、および注文情報            | 37   |

|   |                                                |    |                                |      |

# 4 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| 20 | <b>117</b> 年7月発行のものから更新                                                                                                                  | Page |

|----|------------------------------------------------------------------------------------------------------------------------------------------|------|

| •  | 「特長」セクションで電流レギュレーションとPWMジェネレータの許容誤差を変更                                                                                                   | 1    |

| •  | Changed values for several parameters throughout the Electrical Characteristics table                                                    | 7    |

| •  | Changed parameter definitions for I <sub>(DRV_source)</sub> and I <sub>(DRV_sink)</sub> in the <i>Electrical Chaaracteristics</i> table  | 7    |

| •  | Changed parameter symbols for analog dimming accuracy in the Electrical Characteristics table                                            |      |

| •  | Changed parameter descriptions for V <sub>(OPEN_th_rising)</sub> , V <sub>(OPEN_th_falling)</sub> ,                                      | 8    |

| •  | Changed parameter descriptions for t <sub>(SG_retry_OFF)</sub> and t <sub>(OPEN_retry_OFF)</sub> in the <i>Timing Requirements</i> table | 9    |

| •  | Added a condition for Typical Characteristic 🗵 6                                                                                         |      |

| •  | Deleted a condition from Typical Characteristic 🗵 8                                                                                      | 12   |

| •  | Deleted a Fast Power Down and Slow Power Up typical characteristic graph                                                                 | 12   |

| •  | Added a Fast Power Down and Slow Power Up typical characteristic graph                                                                   | 13   |

| •  | Added a condition for Typical Characteristic 🗵 17                                                                                        | 13   |

| •  | Added a condition for Typical Characteristic 🗵 18                                                                                        | 13   |

| •  | Changed heat dissipation to current distribution in Parallel MOSFET Driving                                                              | 17   |

| •  | Deleted a sentence from the PWM Dimming by Input section                                                                                 | 18   |

| •  | Added resistor and capacitor reference designators                                                                                       | 19   |

| •  | Deleted percentage values for V <sub>(ICTRL_LIN_BOT)</sub> and V <sub>(ICTRL_LIN_TOP)</sub> in the Analog Dimming Topology section       | 21   |

| •  | Changed V <sub>(SG_th_rising)</sub> and V <sub>(SG_th_falling)</sub> with each other in the LED Short-to-GND Detection section           |      |

| •  | Changed symbol of short-to-ground retry current to I <sub>(Retry_short)</sub>                                                            |      |

| •  | Changed symbol of LED-open retry current to I <sub>(Retry_open)</sub> in the LED Open-Circuit Auto Retry section                         |      |

| •  | Changed some FAULT TYPE names in 表 4                                                                                                     |      |

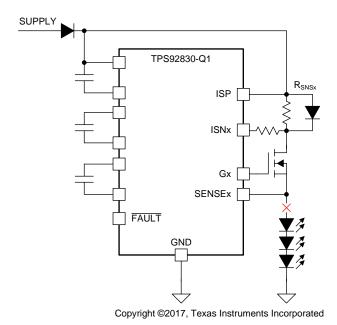

| •  | Updated application schematic.                                                                                                           | 30   |

| •  | Changed the value of R8 from 75 k $\Omega$ to 76 k $\Omega$ for the PWM threshold setting                                                | 31   |

| •  | Changed the equation for calculating K <sub>(RES_DiagEn)</sub>                                                                           | 31   |

| •  | Changed the values of R13 and R6 for                                                                                                     |      |

| •  | Changed the equation for calculating K <sub>(RES_DERATE)</sub>                                                                           | 31   |

| •  | Changed component values in the PWM equations of the Detailed Design Procedure                                                           |      |

|    |                                                                                                                                          |      |

# 改訂履歴 (continued)

| • | Added an application curve                                                             | 34 | 4 |

|---|----------------------------------------------------------------------------------------|----|---|

| • | Added text in the Layout Guidelines for keeping LED ground separate from device ground | 36 | 6 |

# 5 概要(続き)

PWM調光により、複数のソースとして内部PWMジェネレータ、外部PWM入力、または電源調光を柔軟に使用できます。 車載アプリケーションに特化して設計された、各種の診断および保護機能により、システムはより堅牢で使いやすくなります。どれか1つに障害が発生すれば全体を障害とするフォルト・バスでは、TPS92830-Q1がTPS92630-Q1、TPS92638-Q1、およびTPS9261x-Q1ファミリとともに動作し、各種のフォルト処理要件を満たすことができます。

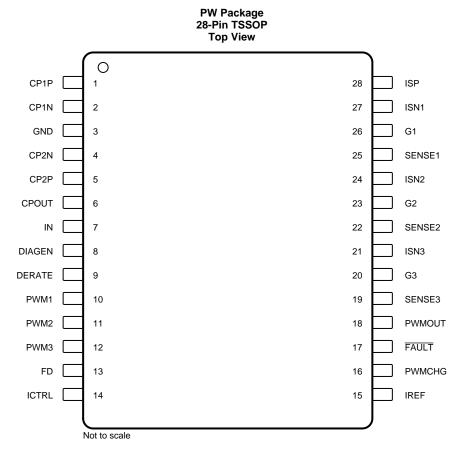

# 6 Pin Configuration and Functions

#### **Pin Functions**

| PIN                                                                |     | I/O                                                       | DESCRIPTION                                                                                                                                                                                                      |  |  |

|--------------------------------------------------------------------|-----|-----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME                                                               | NO. | 1/0                                                       | DESCRIPTION                                                                                                                                                                                                      |  |  |

| CP1N                                                               | 2   | 0                                                         | Charge pump first-stage flying capacitor negative output, charge pump to provide gate-drive voltage for external MOSFET. Connect a 10-nF flying capacitor between CP1P and CP1N.                                 |  |  |

| CP1P                                                               | 1   | 0                                                         | Charge pump first-stage flying capacitor positive output                                                                                                                                                         |  |  |

| CP2N                                                               | 4   | 0                                                         | Charge pump second-stage flying capacitor negative output. Connect a 10-nF flying capacitor between CP2P and CP2N.                                                                                               |  |  |

| CP2P 5 O Charge pump second-stage flying capacitor positive output |     | Charge pump second-stage flying capacitor positive output |                                                                                                                                                                                                                  |  |  |

| CPOUT                                                              | 6   | 0                                                         | Charge-pump output voltage. Connect a 150-nF storage capacitor between CPOUT and IN.                                                                                                                             |  |  |

| DERATE                                                             | 9   | I                                                         | Voltage input for current derating. Connect to GND to disable the derate feature.                                                                                                                                |  |  |

| DIAGEN                                                             | 8   | I                                                         | Input pin with comparator to enable diagnostics to avoid false open-fault diagnostics when the device works in low-dropout mode. Use a resistor divider to set a threshold according to the LED forward voltage. |  |  |

| FAULT                                                              | 17  | I/O                                                       | Fault bus pin to support one-fails-all-fail feature. Float: one-fails-all-fail; strong pullup: only-fails-off                                                                                                    |  |  |

# Pin Functions (continued)

| PIN    |     |     |                                                                                                                                                                                               |

|--------|-----|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME   | NO. | I/O | DESCRIPTION                                                                                                                                                                                   |

| FD     | 13  | 1   | Full duty-cycle input, HIGH: 100% PWM; LOW: using external resistor-capacitor network to set PWM duty cycle                                                                                   |

| G1     | 26  | 0   | Channel 1 gate driver output, connect to CH 1 N-channel MOSFET gate                                                                                                                           |

| G2     | 23  | 0   | Channel 2 gate driver output, connect to CH 2 N-channel MOSFET gate                                                                                                                           |

| G3     | 20  | 0   | Channel 3 gate driver output, connect to CH 3 N-channel MOSFET gate                                                                                                                           |

| GND    | 3   | _   | GND                                                                                                                                                                                           |

| ICTRL  | 14  | 1   | Analog dimming input, modulates the regulation voltage across the current-sense resistor. Apply a voltage source or connect a resistor between ICTRL and GND to set the analog dimming ratio. |

| IN     | 7   | I   | Power supply for the device. LED current only flows from the external MOSFET to the LED.                                                                                                      |

| ISN1   | 27  | 1   | Channel 1 current-sense negative input. Connect a current-sense resistor between ISP and ISN1 to set the CH 1 current.                                                                        |

| ISN2   | 24  | 1   | Channel 2 current-sense negative input. Connect a current-sense resistor between ISP and ISN2 to set the CH 2 current.                                                                        |

| ISN3   | 21  | 1   | Channel 3 current-sense negative input. Connect a current-sense resistor between ISP and ISN3 to set the CH 3 current.                                                                        |

| IREF   | 15  | 0   | Internal current reference. Connect an 8-kΩ resistor between IREF and GND,                                                                                                                    |

| ISP    | 28  | I   | Channel current-sense positive input. Kelvin-sense to LED sense-resistor positive node.                                                                                                       |

| PWM1   | 10  | I   | Channel 1 PWM input                                                                                                                                                                           |

| PWM2   | 11  | I   | Channel 2 PWM input                                                                                                                                                                           |

| PWM3   | 12  | I   | Channel 3 PWM input                                                                                                                                                                           |

| PWMCHG | 16  | I/O | On-chip PWM generator pin for external R-C. Connect a resistor and a capacitor between PWMCHG and GND to set the PWM duty cycle and frequency.                                                |

| PWMOUT | 18  | 0   | High-voltage PWM open-drain output. Connect a 10-kΩ resistor between IN and PWMOUT                                                                                                            |

| SENSE1 | 25  | I/O | Channel 1 diagnostics pin. Connect to the CH 1 MOSFET source terminal                                                                                                                         |

| SENSE2 | 22  | I/O | Channel 2 diagnostics pin. Connect to the CH 2 MOSFET source terminal                                                                                                                         |

| SENSE3 | 19  | I/O | Channel 3 diagnostics pin. Connect to the CH 3 MOSFET source terminal                                                                                                                         |

# 7 Specifications

# 7.1 Absolute Maximum Ratings

over operating junction temperature range  $T_J = -40$ °C to 150°C (unless otherwise noted)<sup>(1)</sup>

|                                       |                                                                                                                   | MIN  | MAX                     | UNIT |

|---------------------------------------|-------------------------------------------------------------------------------------------------------------------|------|-------------------------|------|

| Supply voltage                        | IN <sup>(2)</sup>                                                                                                 | -0.3 | 45 <sup>(3)</sup>       | V    |

| Input voltage                         | DERATE, DIAGEN, FD, ICTRL, ISN1, ISN2, ISN3, ISP, PWM1, PWM2, PWM3, PWMOUT, SENSE1, SENSE2, SENSE3 <sup>(2)</sup> | -0.3 | V <sub>(IN)</sub> + 0.3 | V    |

| Output voltage                        | CP1P, CP2P, CPOUT, G1, G2, G3 <sup>(2)</sup>                                                                      | -0.3 | V <sub>(IN)</sub> + 10  | V    |

| Current-sense voltage                 | $V_{(ISP)} - V_{(ISNx)}$                                                                                          | -0.3 | 1                       | V    |

| Gate-source voltage                   | $V_{(Gx)} - V_{(SENSEx)}$                                                                                         | -1   | 12                      | V    |

| 1/0                                   | FAULT <sup>(2)</sup>                                                                                              | -0.3 | 22                      | V    |

| I/O                                   | CP1N, CP2N, IREF, PWMCHG <sup>(2)</sup>                                                                           | -0.3 | 6                       | V    |

| Storage temperature, T <sub>stg</sub> |                                                                                                                   | -65  | 150                     | °C   |

| Junction temperature, T <sub>J</sub>  |                                                                                                                   | -40  | 150                     | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 7.2 ESD Ratings

|                    |                         |                                              |                                      | VALUE | UNIT |

|--------------------|-------------------------|----------------------------------------------|--------------------------------------|-------|------|

|                    |                         | Human-body model (HBM), per AEC Q100         | -002 <sup>(1)</sup>                  | ±2000 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per AEC Q100-011 | Corner pins (CP1P, ICTRL, IREF, ISP) | ±750  | V    |

|                    |                         | Q100-011                                     | Other pins                           | ±500  |      |

<sup>(1)</sup> AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

# 7.3 Recommended Operating Conditions

over operating junction temperature range  $T_J = -40$ °C to 150°C (unless otherwise noted)

|                        |                          | MIN | MAX               | UNIT |

|------------------------|--------------------------|-----|-------------------|------|

| Device supply voltage  | IN                       | 4.5 | 40                | V    |

| Sense voltage          | ISP                      | 0   | V <sub>(IN)</sub> | V    |

| PWM inputs             | PWMx                     | 0   | V <sub>(IN)</sub> | V    |

| Diagnostics enable pin | DIAGEN                   | 0   | V <sub>(IN)</sub> | V    |

| Current-sense voltage  | $V_{(ISP)} - V_{(ISNx)}$ | 0   | 1                 | V    |

| Fault bus              | FAULT                    | 0   | 20                | V    |

| PWM open-drain output  | PWMOUT                   | 0   | V <sub>(IN)</sub> | V    |

| Analog dimming input   | ICTRL                    | 0   | V <sub>(IN)</sub> | V    |

| Current derating input | DERATE                   | 0   | V <sub>(IN)</sub> | V    |

| Full duty-cycle input  | FD                       | 0   | V <sub>(IN)</sub> | V    |

<sup>(2)</sup> All voltages are with respect to GND.

<sup>(3)</sup> Absolute maximum voltage 45 V for 200 ms.

#### 7.4 Thermal Information

|                        |                                              | TPS92830-Q1 |      |

|------------------------|----------------------------------------------|-------------|------|

|                        | THERMAL METRIC <sup>(1)</sup>                |             | UNIT |

|                        |                                              | 28 PINS     |      |

| $R_{\theta JA}$        | Junction-to-ambient thermal resistance       | 79.4        | °C/W |

| $R_{\theta JC(top)}$   | Junction-to-case (top) thermal resistance    | 20.1        | °C/W |

| $R_{\theta JB}$        | Junction-to-board thermal resistance         | 37.4        | °C/W |

| ΨЈТ                    | Junction-to-top characterization parameter   | 0.5         | °C/W |

| ΨЈВ                    | Junction-to-board characterization parameter | 36.9        | °C/W |

| R <sub>0</sub> JC(bot) | Junction-to-case (bottom) thermal resistance | N/A         | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see Semiconductor and IC Package Thermal Metrics.

### 7.5 Electrical Characteristics

$V_{IN} = 5 \text{ V to } 40 \text{ V}$ ,  $V_{ICTRI} = 3 \text{ V}$ ,  $V_{DERATE} = 0 \text{ V}$ ,  $T_{I} = -40 ^{\circ}\text{C}$  to  $150 ^{\circ}\text{C}$ , (1) (unless otherwise noted)

|                            | PARAMETER                                   | TEST CONDITIONS                                                           | MIN   | TYP   | MAX   | UNIT |

|----------------------------|---------------------------------------------|---------------------------------------------------------------------------|-------|-------|-------|------|

| BIAS                       |                                             |                                                                           |       |       |       |      |

| V <sub>(POR_rising)</sub>  | Supply voltage POR, rising threshold        |                                                                           |       |       | 4.5   | V    |

| I <sub>(Quiescent)</sub>   | Device standby current                      | PWMx = HIGH, FD = HIGH                                                    |       | 3.5   |       | mA   |

| I <sub>(FAULT)</sub>       | Device current in fault mode                | PWMx = HIGH, FAULT = LOW                                                  |       | 0.5   | 0.75  | mΑ   |

| I <sub>(IREF)</sub>        | Reference current                           | $R_{(IREF)} = 8 k\Omega$                                                  |       | 99    |       | μΑ   |

| C <sub>(IREF)</sub>        | IREF loading capacitance                    | $R_{(IREF)} = 8 k\Omega$                                                  | 0     |       | 4.3   | nF   |

| CHARGE PUMP                |                                             | •                                                                         | •     |       | ·     |      |

| V <sub>(cp_drv)</sub>      | Charge-pump operating voltage               |                                                                           | 6.1   | 8.5   | 10    | V    |

| f <sub>(cp_sw)</sub>       | Charge-pump switching frequency             |                                                                           |       | 2.65  |       | MHz  |

| C <sub>(cp_flying)</sub>   | Charge-pump flying capacitor                |                                                                           |       | 10    |       | nF   |

| C <sub>(cp_storage)</sub>  | Charge-pump storage capacitor               |                                                                           |       | 150   |       | nF   |

|                            | N LOGIC INPUTS (DIAGEN, PWMx,               | FD)                                                                       | •     |       | ·     |      |

| V <sub>IL(DIAGEN)</sub>    | Input logic-low voltage, DIAGEN             |                                                                           | 1.105 | 1.145 | 1.185 | V    |

| V <sub>IH(DIAGEN)</sub>    | Input logic-high voltage,<br>DIAGEN         |                                                                           | 1.193 | 1.224 | 1.255 | V    |

| V <sub>IL(PWMx)</sub>      | Input logic-low voltage, PWMx               |                                                                           | 1.094 | 1.128 | 1.161 | V    |

| $V_{IH(PWMx)}$             | Input logic-high voltage, PWMx              |                                                                           | 1.176 | 1.212 | 1.248 | V    |

| $V_{IL(FD)}$               | Input logic-low voltage, FD                 |                                                                           | 1.105 | 1.133 | 1.161 | V    |

| V <sub>IH(FD)</sub>        | Input logic-high voltage, FD                |                                                                           | 1.186 | 1.216 | 1.246 | V    |

| CONSTANT-CUR               | RENT EXTERNAL N-CHANNEL MO                  | SFET DRIVER                                                               |       |       |       |      |

| V <sub>(CS_REG_FULL)</sub> | Current-sense-resistor regulation voltage   | V <sub>(ICTRL)</sub> = 3 V, V <sub>(DERATE)</sub> = 0 V                   |       | 295   |       | mV   |

| (2)(3)                     | Current-sense-resistor                      | V <sub>(ICTRL)</sub> = 3 V, V <sub>(DERATE)</sub> = 0 V, channel accuracy | -1.5% |       | 1.5%  |      |

| $\Delta V_{(CS)}^{(2)(3)}$ | regulation-voltage accuracy                 | V <sub>(ICTRL)</sub> = 3 V, V <sub>(DERATE)</sub> = 0 V, device accuracy  | -2.5% |       | 2.5%  |      |

| I <sub>(DRV_source)</sub>  | Gate-driver current-source capability at Gx |                                                                           | 190   | 230   | 270   | μΑ   |

(1) External N-channel MOSFET  $C_{iss}$  = 200 pF,  $C_{oss}$  = 70 pF, at  $V_{DS}$  = 25 Vdc,  $V_{GS}$  = 0 Vdc, f = 1 MHz,  $V_{th}$ = 4 V, compensation capacitor

(1) External N-channel MOSFET

$$C_{iss} = 200 \text{ pF}, C_{oss} = 70 \text{ pF}, \text{ at } V_{DS} = 25 \text{ Vdc}, V_{GS} = 0 \text{ Vdc}, f = 1 \text{ MHz}$$

$$C_{gs} = 4 \text{ nF} \qquad \qquad 3 \times V_{(CS\_REG\_x)}$$

$$\Delta V_{(CS\_Channel\_CHx)} = 1 - \frac{3 \times V_{(CS\_REG\_x)}}{\left(V_{(CS\_REG\_1)} + V_{(CS\_REG\_2)} + V_{(CS\_REG\_3)}\right)}, x = 1,2,3$$

(2)

$$\Delta V_{(CS\_Device\_CHx)} = 1 - \frac{V_{(CS\_REG\_x)}}{0.295}, x = 1,2,3$$

# **Electrical Characteristics (continued)**

$V_{IN} = 5 \text{ V to } 40 \text{ V}, V_{ICTRL} = 3 \text{ V}, V_{DERATE} = 0 \text{ V}, T_{J} = -40^{\circ}\text{C} \text{ to } 150^{\circ}\text{C},^{(1)} \text{ (unless otherwise noted)}$

|                                  | PARAMETER                                                                                                                                                                         | TEST CONDITIONS                                                                                                                                               | MIN        | TYP        | MAX        | UNIT |

|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------------|------------|------|

| I <sub>(DRV_sink)</sub>          | Gate-driver current-sink capability at Gx                                                                                                                                         |                                                                                                                                                               | 190        | 230        | 270        | μΑ   |

| V <sub>(GS_clamp_neg)</sub>      | Gate-source negative clamp voltage                                                                                                                                                |                                                                                                                                                               | -0.9       | -0.7       | -0.5       | V    |

| $V_{(GS\_clamp\_pos)}$           | Gate-source positive clamp voltage                                                                                                                                                |                                                                                                                                                               | 9.8        | 10.4       | 11.3       | V    |

| I <sub>(ISNx_leakage)</sub>      | Leakage current sink on ISNx pins                                                                                                                                                 |                                                                                                                                                               |            | 1.3        | 2.3        | μΑ   |

| INTERNAL PWM DI                  | MMING                                                                                                                                                                             |                                                                                                                                                               |            |            | ·          |      |

| V <sub>(PWMCHG_th_rising)</sub>  | Internal PWM generator, rising threshold                                                                                                                                          |                                                                                                                                                               | 1.45       | 1.48       | 1.51       | V    |

| V <sub>(PWMCHG_th_falling)</sub> | Internal PWM generator, falling threshold                                                                                                                                         |                                                                                                                                                               | 0.78       | 0.8        | 0.82       | V    |

| V <sub>(PWMCHG_th_hys)</sub>     | Internal PWM generator hysteresis                                                                                                                                                 |                                                                                                                                                               |            | 0.68       |            | V    |

| I <sub>(PWMCHG)</sub>            | PWM generator pullup current                                                                                                                                                      | V <sub>(PWMCHG)</sub> = 0 V, FD = LOW                                                                                                                         | 194        | 200        | 206        | μΑ   |

| V <sub>OL(PWMOUT)</sub>          | Open-drain PWMOUT pulldown voltage                                                                                                                                                | V <sub>(PWMCHG)</sub> = 3 V, I <sub>(PWMOUT)</sub> pullup<br>current = 4 mA                                                                                   |            |            | 0.4        | V    |

| r <sub>DS(on)(PWMOUT)</sub>      | Open-drain PWMOUT pulldown MOSFET r <sub>DS(on)</sub>                                                                                                                             |                                                                                                                                                               | 40         | 55         | 90         | Ω    |

| ANALOG DIMMING                   |                                                                                                                                                                                   |                                                                                                                                                               |            |            |            |      |

| V <sub>(ICTRL_FULL)</sub>        | Full-range ICTRL voltage                                                                                                                                                          |                                                                                                                                                               |            |            | 1.65       | V    |

| V <sub>(ICTRL_LIN_TOP)</sub>     | Upper boundary for linear ICTRL dimming                                                                                                                                           |                                                                                                                                                               |            | 1.425      |            | V    |

| V <sub>(ICTRL_LIN_BOT)</sub>     | Lower boundary for linear ICTRL dimming                                                                                                                                           |                                                                                                                                                               |            | 75         |            | mV   |

| $\Delta V_{(CS\_ICTRL\_H)}$      | Analog dimming accuracy                                                                                                                                                           | $ \begin{array}{l} V_{(ICTRL)} = 1.35 \; V, \; V_{(DERATE)} = 0 \; V, \\ accuracy: \; 1 - (V_{(CS\_REG\_x)} / \; 0.27), \; x = \\ 1, \; 2, \; 3 \end{array} $ | -2.5%      |            | 2%         |      |

| $\Delta V_{(CS\_ICTRL\_M)}$      | Analog dimming accuracy                                                                                                                                                           | $V_{(ICTRL)} = 0.75 \text{ V}, V_{(DERATE)} = 0 \text{ V},$ accuracy: $1 - (V_{(CS\_REG\_x)} / 0.15), x = 1, 2, 3$                                            | -4%        |            | 4%         |      |

| $\Delta V_{(CS\_ICTRL\_L)}$      | Analog dimming accuracy                                                                                                                                                           | $\begin{array}{l} V_{(ICTRL)} = 0.15 \ V, \ V_{(DERATE)} = 0 \ V, \\ accuracy: \ 1 - V_{(CS\_REG\_x)} \ / \ 0.03, \ x = \\ 1, \ 2, \ 3 \end{array}$           | -18%       |            | 18%        |      |

| I <sub>(ICTRL_pullup)</sub>      | ICTRL internal pullup current                                                                                                                                                     |                                                                                                                                                               | 0.95       | 0.985      | 1.02       | mA   |

| CURRENT DERATI                   | NG                                                                                                                                                                                |                                                                                                                                                               |            |            |            |      |

| V <sub>(DERATE_FULL)</sub>       | Full-range DERATE voltage                                                                                                                                                         |                                                                                                                                                               |            | 1.83       |            | V    |

| $V_{(DERATE\_HALF)}$             | Half-range DERATE voltage                                                                                                                                                         |                                                                                                                                                               |            | 2.38       |            | V    |

| $K_{(DERATE)}$                   | Derate dimming ratio                                                                                                                                                              | $V_{(DERATE)} = 1.966 \text{ V}$ $V_{(DERATE)} = 2.316 \text{ V}$                                                                                             | 81%<br>51% | 87%<br>58% | 95%<br>65% |      |

| DIAGNOSTICS                      |                                                                                                                                                                                   | (52.3112)                                                                                                                                                     |            |            |            |      |

| $V_{(OPEN\_th\_rising)}$         | LED open rising threshold, device triggers open-circuit diagnostics V <sub>(SG_th_rising)</sub> , and V <sub>(SG_th_falling)</sub> in the <i>Electrical Characteristics</i> table | $V_{(ISNx)} - V_{(SENSEx)}, x = 1, 2, 3$                                                                                                                      | 100        | 145        | 190        | mV   |

| $V_{(OPEN\_th\_falling)}$        | LED open falling threshold,<br>device releases from open-<br>circuit diagnostics                                                                                                  | $V_{(ISNx)} - V_{(SENSEx)}, x = 1, 2, 3$                                                                                                                      | 240        | 280        | 320        | mV   |

| V <sub>(OPEN_th_hyst)</sub>      |                                                                                                                                                                                   |                                                                                                                                                               |            | 135        |            | mV   |

| I <sub>(Retry_open)</sub>        | LED-open retry current                                                                                                                                                            |                                                                                                                                                               | 8          | 10         | 12         | mA   |

# **Electrical Characteristics (continued)**

$V_{IN} = 5 \text{ V}$  to 40 V,  $V_{ICTRL} = 3 \text{ V}$ ,  $V_{DERATE} = 0 \text{ V}$ ,  $T_{J} = -40 ^{\circ}\text{C}$  to  $150 ^{\circ}\text{C}$ , (1) (unless otherwise noted)

|                               | PARAMETER                                                                                                                         | TEST CONDITIONS             | MIN   | TYP   | MAX  | UNIT |

|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-------|-------|------|------|

| V <sub>(SG_th_rising)</sub>   | Channel output V <sub>SENSEx</sub> short-<br>to-ground rising threshold,<br>device triggers short-to-ground<br>diagnostics        |                             | 0.885 | 0.92  | 0.95 | V    |

| $V_{(SG\_th\_falling)}$       | Channel output V <sub>SENSEx</sub> short-<br>to-ground falling threshold,<br>device releases from short-to-<br>ground diagnostics |                             | 1.17  | 1.215 | 1.26 | V    |

| V <sub>(SG_th_hyst)</sub>     | Channel output V <sub>SENSEx</sub> short-to-ground hysteresis                                                                     |                             |       | 295   |      | mV   |

| I <sub>(Retry_short)</sub>    | Channel output V <sub>SENSEx</sub> short-<br>to-ground retry current                                                              |                             | 0.75  | 1     | 1.25 | mA   |

| FAULT                         |                                                                                                                                   |                             |       |       |      |      |

| V <sub>IL(FAULT)</sub>        | Logic-input low threshold                                                                                                         |                             |       |       | 0.7  | V    |

| V <sub>IH(FAULT)</sub>        | Logic-input high threshold                                                                                                        |                             | 2     |       |      | V    |

| V <sub>OL(FAULT)</sub>        | Logic-output low threshold                                                                                                        | With 500-µA external pullup |       |       | 0.4  | V    |

| V <sub>OH(FAULT)</sub>        | Logic-output high threshold                                                                                                       | With 1-µA external pulldown | 2.7   |       | 3.4  | V    |

| I <sub>(FAULT_pulldown)</sub> | FAULT internal pulldown current                                                                                                   |                             | 650   | 750   | 800  | μΑ   |

| I <sub>(FAULT_pullup)</sub>   | FAULT internal pullup current                                                                                                     |                             | 6.5   | 7.6   | 9.5  | μΑ   |

| THERMAL PROT                  | ECTION                                                                                                                            |                             |       |       |      |      |

| T <sub>(TSD)</sub>            | Thermal shutdown threshold                                                                                                        |                             |       | 176   |      | °C   |

| T <sub>(TSD_HYS)</sub>        | Thermal shutdown hysteresis                                                                                                       |                             |       | 15    |      | °C   |

# 7.6 Timing Requirements

|                                |                                                                                                                             | MIN   | NOM  | MAX   | UNIT |

|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------|-------|------|-------|------|

| t <sub>(OPEN_deg)</sub>        | LED open-circuit deglitch time, described in LED open-circuit diagnostics section                                           | 100   | 125  | 150   | μs   |

| t <sub>(SG_deg)</sub>          | LED short-to-GND detection deglitch time, described in the LED short-to-GND diagnostics section                             | 100   | 125  | 150   | μs   |

| t <sub>(SG_retry_ON)</sub>     | Channel output SENSEx short-to-ground retry on-time, described in the LED short-to-GND auto retry section                   | 100   | 125  | 150   | μs   |

| t <sub>(SG_retry_OFF)</sub>    | Channel output SENSEx short-to-ground retry off-time, described in LED short-to-GND auto retry section                      |       | 10.8 |       | ms   |

| t <sub>OPEN_retry_ON)</sub>    | Channel output SENSEx open-circuit retry on-time                                                                            | 100   | 125  | 150   | μs   |

| t <sub>(OPEN_retry_OF</sub> F) | Channel output SENSEx open-circuit retry off-time                                                                           |       | 10.8 |       | ms   |

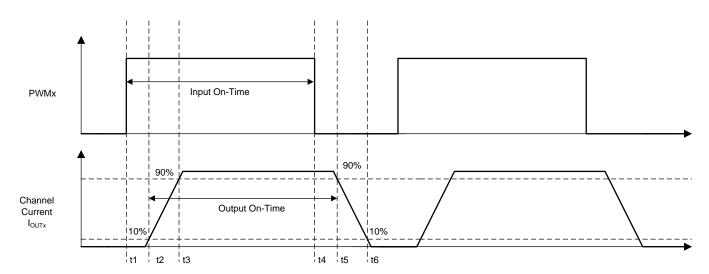

| D <sub>(PWM_50)</sub>          | PWM generated internally, nominal 50% duty cycle, as measured on output channel; see $\ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ $ | 49.6% | 50%  | 50.4% |      |

| t <sub>d(DERATE)</sub>         | Derate current-response delay time when DERATE steps from 1.8 V to 2.4 V $$                                                 |       | 25   |       | μs   |

| t(CP_STARTUP)                  | V <sub>(IN)</sub> = 14 V, Cs = 150 nF, CPOUT voltage reaches 18 V as shown in<br>Device Start-Up Delay diagram              |       | 25   |       | μs   |

| f <sub>(DRV_PWM)</sub>         | Recommended PWM driving-frequency range                                                                                     |       |      | 2000  | Hz   |

Copyright © 2017, Texas Instruments Incorporated

図 1. Channel-Current Output Timing Diagram

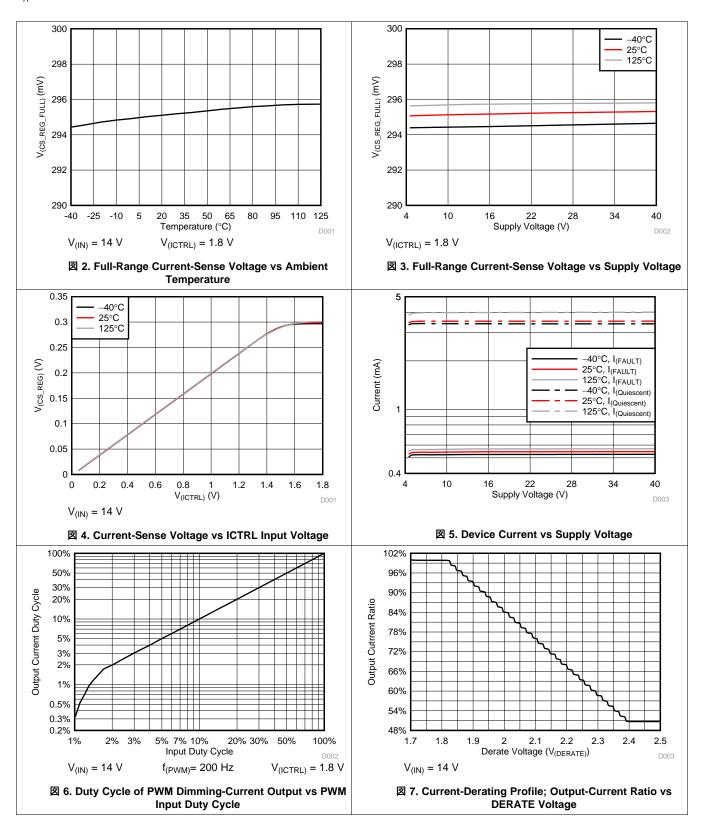

# 7.7 Typical Characteristics

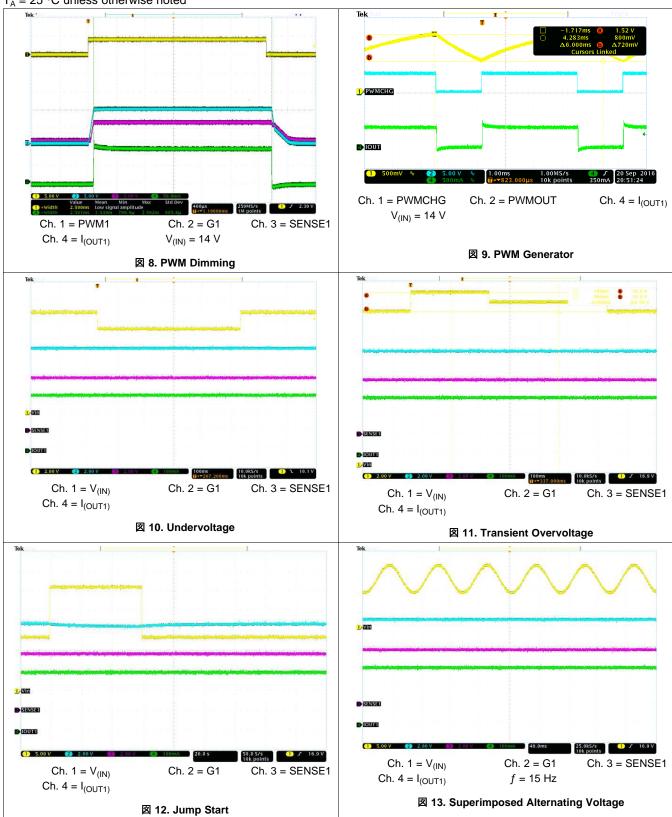

T<sub>A</sub> = 25 °C unless otherwise noted

# **Typical Characteristics (continued)**

T<sub>A</sub> = 25 °C unless otherwise noted

# **Typical Characteristics (continued)**

T<sub>A</sub> = 25 °C unless otherwise noted

# 8 Detailed Description

#### 8.1 Overview

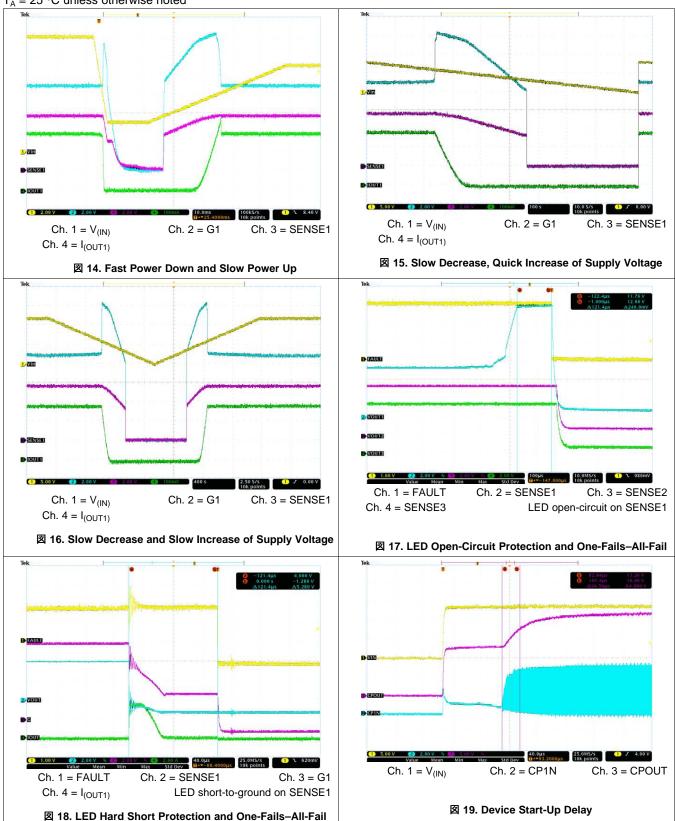

The TPS92830-Q1 device is an advanced automotive-grade high-side constant-current linear LED controller for delivering high current using external N-channel MOSFETs. The device has a full set of features for automotive applications. Each channel of the TPS92830-Q1 device sets the channel current independently by the sense-resistor value. An internal precision constant-current regulation loop senses the channel current by the voltage across the sense resistor and controls the gate voltage of the N-channel MOSFET accordingly. The device also integrates a two-stage charge pump for low-dropout operation. The charge-pump voltage is high enough to support a wide selection of N-channel MOSFETs. PWM dimming allows multiple sources for flexibility—internal PWM generator, external PWM inputs, or power-supply dimming. Various diagnostics and protection features specially designed for automotive applications help improve system robustness and ease of use. A one-fails—all-fail fault bus supports TPS92830-Q1 operation together with the TPS92630-Q1, TPS92638-Q1, and TPS9261x-Q1 family to fulfill various fault-handling requirements.

# 8.2 Functional Block Diagram

#### 8.3 Feature Description

The TPS92830-Q1 device uses IN voltage to generate device bias. A two-stage charge pump provides gate driving voltage above the IN voltage for the high-side N-channel MOSFET. Each channel current is independently set by sense resistors. The analog-dimming ICTRL input supports off-board resistors as bin-setting resistors as well as direct voltage input. An integrated precision PWM generator could be used for PWM dimming locally.

#### 8.3.1 Device Bias

The TPS92830-Q1 device has internal bias-generation and power-on-reset circuits for internal bias.

#### 8.3.1.1 Power-On-Reset (POR)

The TPS92830-Q1 device has an internal power-on-reset (POR) function. When power is applied to IN, the internal POR holds the device in the reset condition until  $V_{IN}$  reaches  $V_{(POR\_rising)}$ .

When the supply rises above POR threshold  $V_{(POR\_rising)}$ , the charge pump starts working. The maximum gate-drive voltage is determined by the charge-pump voltage between CPOUT and IN.

#### 8.3.1.2 Current Reference (IREF)

The TPS92830-Q1 device has a constant reference-voltage output on the IREF pin and uses current  $I_{(IREF)}$  as the internal current reference. The analog-dimming internal-pullup current on ICTRL, and the PWM-generator internal charge current on PWMCHG, use  $I_{(IREF)}$  as a reference current. The recommended value of reference resistor  $R_{(IREF)}$  for IREF is 8 k $\Omega$ .

#### 8.3.1.3 Low-Current Fault Mode

The TPS92830-Q1 device consumes minimal quiescent current when it is in fault mode. If the FAULT voltage is pulled low either by internal diagnostics or externally, the device performs as follows:

- The charge pump is shut down.

- All drivers are turned off with their gates internally pulled down.

- The PWM generator and PWMOUT are turned off.

- · IREF current is turned off.

- · ICTRL current is turned off.

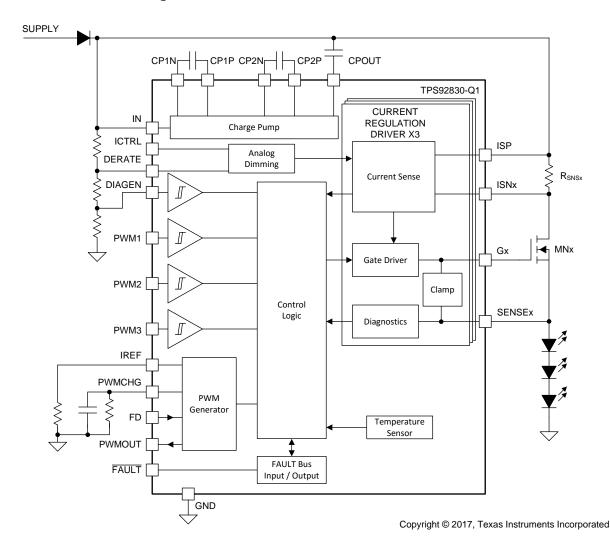

#### 8.3.2 Charge Pump

#### 8.3.2.1 Charge Pump Architecture

The TPS92830-Q1 device uses a two-stage charge pump to generate the high-side gate-drive voltage. The charge pump is a voltage tripler using external flying and storage capacitors.

$C_{P1}$  is the first-stage flying capacitor, connected between CP1P and CP1N, which are the positive and negative nodes, respectively.  $C_{P2}$  is the second-stage flying capacitor, connected between CP2P and CP2N, which are the positive and negative nodes, respectively.  $C_S$  is the storage capacitor, connected between CPOUT and IN.  $C_S$  stores charge for the high-side gate driver.

The charge pump switches at frequency  $f_{(cp\ sw)}$  to optimize EMI performance.

Negative nodes CP1N and CP2N are driven by a 5-V driver, thus the maximum voltage on charge-pump output node CPOUT is approximately  $V_{(IN)} + V_{(CP\_drv)}$ . The charge pump voltage across storage capacitor  $C_S$  is not dependent on  $V_{(IN)}$ .

copyright of zorry reside mediamente meerpere

図 20. Charge Pump

### 8.3.3 Constant-Current Driving

The TPS92830-Q1 device has three independent constant-current driving channels. Each channel sets channel current with an external high-side current-sense resistor,  $R_{SNSx}$ . Channel current is set as  $V_{(CS\ REG)}$  /  $R_{SNSx}$ .

Considering that both ICTRL and DERATE voltages reduce current-sense voltage  $V_{(CS\_REG)}$  independently, channel current can be calculated using the following equation. Each of the dimming ratios is described separately in following sections.

$$I_{(CHx)} = \frac{V_{(CS\_REG\_FULL)} \times k_{(ICTRL\_DIM)} \times k_{(DERATE\_DIM)}}{R_{SNSx}}$$

(1)

### 8.3.3.1 High-Side Current Sense

The sense voltage across external current-sense resistor R<sub>SNSx</sub> feeds back current information to the controller. An internal feedback control loop within the TPS92830-Q1 device regulates the external gate-overdrive voltage of the N-channel MOS transistor to keep the sense voltage at the desired level. By setting the external current-sense resistance value, the output current can be set individually on each channel.

### 8.3.3.2 High-Side Current Driving

To regulate the output current, the gate-source voltage of the external MOSFET must be regulated accordingly. The constant-current source is used to charge and discharge the N-channel MOSFET gate. During the current-slewing period, constant-current sourcing and sinking ensures the smooth slewing of the output current. The control loop requires sufficient MOSFET gate capacitance to ensure loop stability. In case the MOSFET gate capacitance is insufficient, a capacitor  $C_{GS}$  must be added across Gx and SENSEx. TI also recommends always putting a  $C_{SENSE}$  of 10 nF from each of the SENSEx pins to GND, and close to the device for EMC.

When a channel is switched on, current source  $I_{(DRV\_source)}$  charges the gate of the external N-channel MOSFET. When a channel is switched off, current sink  $I_{(DRV\_sink)}$  discharges the gate of the external MOSFET transistor down to ground.

図 21. MOSFET Gate Capacitance Compensation

#### 8.3.3.3 Gate Overdrive Voltage Protection

A bidirectional clamp is used to protect the gate-source path of the external N-channel MOSFETs from overstress conditions. Gate-source voltage  $V_{(GS)}$  is clamped between  $V_{(GS\_clamp\_neg)}$  and  $V_{(GS\_clamp\_pos)}$  for MOSFET protection.

#### 8.3.3.4 High-Precision Current Regulation

The TPS92830-Q1 device has a high-precision current-regulation loop. Its precision is at the maximum when the voltage across the current-sense resistor is set to maximum. The analog-dimming or current-derating function reduces the current-sense voltage, thus decreasing current-regulation accuracy.

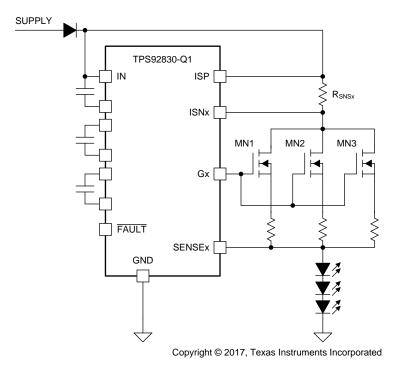

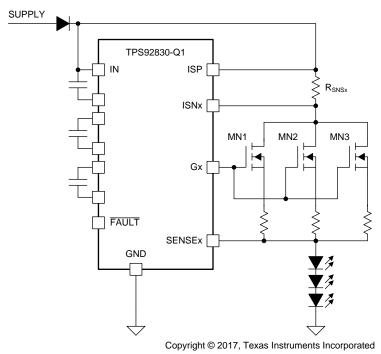

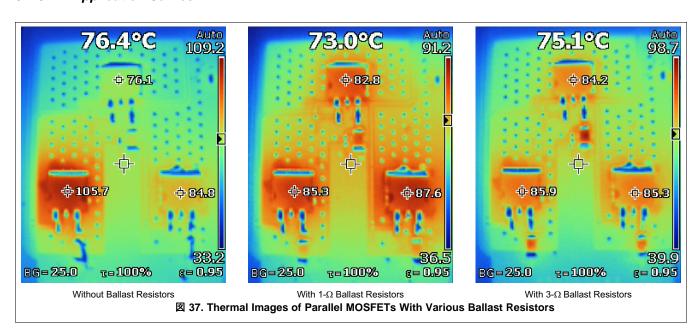

#### 8.3.3.5 Parallel MOSFET Driving

The TPS92830-Q1 device is designed to support parallel N-channel MOSFETs driving within the same channel. To balance heat dissipation, multiple MOSFETs could be paralleled together. A ballast resistor for each MOSFET is recommended to balance current distribution among parallel MOSFETs.

Larger variation on threshold mismatches requires larger ballast resistors.  $V_{(TH\_MISMATCH)}$  is the threshold for mismatches within the same batch of MOSFETs.  $I_{(CH\_MISMATCH)}$  is the allowed mismatch current between the parallel channels. Typically,  $I_{(CH\_MISMATCH)}$  can be set to 10% of full-range current. The ballast resistor value is set as calculated in the following equation.

$$R_{\text{(Ballast)}} = \frac{V_{\text{(TH\_MISMATCH)}}}{I_{\text{(CH\_MISMATCH)}}}$$

(2)

The ballast resistor typically ranges from hundreds of milliohms to several ohms depending on the channel current and MOSFET threshold-voltage variations.

図 22. Parallel MOSFET Driving

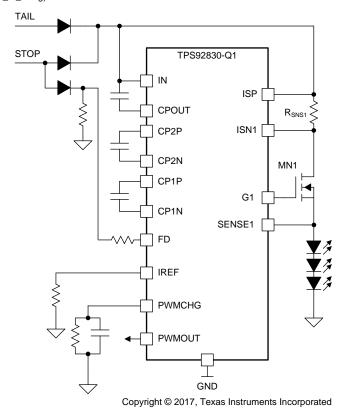

#### 8.3.4 PWM Dimming

The TPS92830-Q1 device supports a variety of PWM dimming methods, including PWM supply dimming, external PWM dimming by inputs, and internal PWM dimming by the internal PWM generator. Each PWM cycle should allow enough positive cycle time for gate charging and enough negative cycle time for gate discharging in order to achieve an accurate PWM dimming duty cycle.

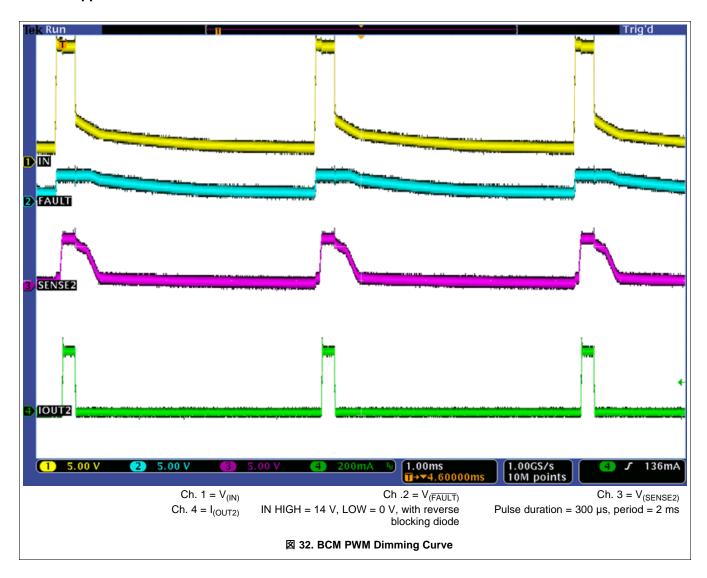

#### 8.3.4.1 Supply Dimming

In the case of supply dimming, the supply of the whole LED driver module is PWM dimmed, for example by body-control-module (BCM) high-side switches. The TPS92830-Q1 device supports supply dimming with a short power-on delay. Device supply  $V_{IN}$  should be always equal to  $V_{(ISP)}$  to ensure that the charge pump voltage is high enough to turn on the MOSFET.

When supply dimming is used, it is recommended to be used together with PWM input, so that the channel is only turned on when the input voltage is above the device UVLO threshold. By keeping enough delay time between device power up and channel turnon, output current spikes can be avoided to ease EMC design.

#### 8.3.4.2 PWM Dimming by Input

Each channel has individual PWM dimming by inputs.

The internal thresholds for PWM1–PWM3 are designed with high precision. With external resistor dividers, each channel threshold can be set flexibly and independently.

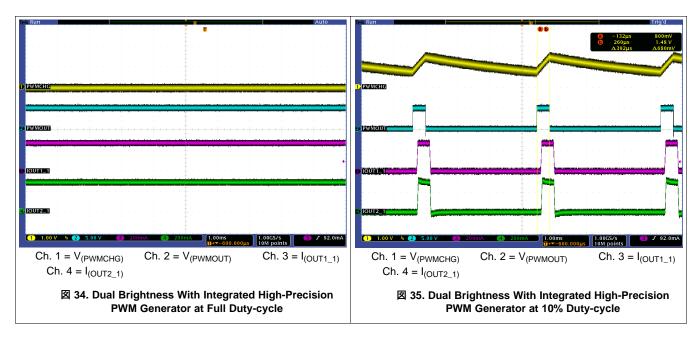

#### 8.3.4.3 Internal Precision PWM Generator

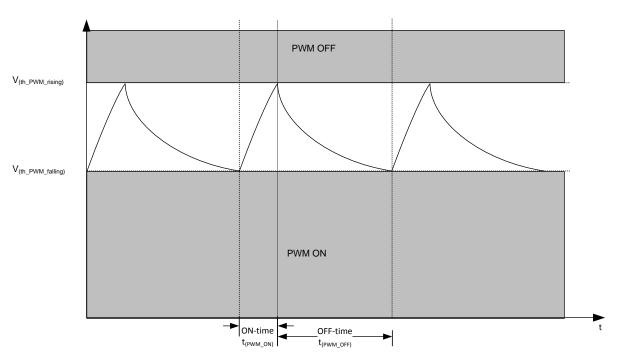

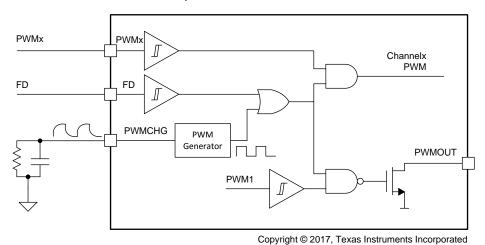

The TPS92830-Q1 device has an integrated precision PWM generator for on-chip PWM dimming as shown in . The device supports open-drain PWMOUT for synchronization between devices. Each device can be connected as a master, generating PWM, or as a slave, relying on external PWM sources. An external RC circuit precisely sets the duty cycle of the PWM generator across a wide duty-cycle range. Variation of the capacitor value affects the output frequency but not the duty cycle.

The PWM generator uses reference current 2 x I<sub>(IREF)</sub> as the internal charge current, I<sub>(PWMCHG)</sub>.

When  $V_{(PWMCHG)}$  increases above rising threshold  $V_{(PWMCHG\_th\_rising)}$ , the constant-current source is turned off and  $V_{(PWMCHG)}$  decays through the external resistor-capacitor circuit. The PWM output is set LOW. The PWMCHG threshold is set to  $V_{(PWMCHG\_th\_falling)}$ . When  $V_{(PWMCHG)}$  decreases below falling threshold  $V_{(PWMCHG\_th\_falling)}$ , the constant-current source is turned on again to charge up the external capacitor. The PWM output is HIGH and the threshold is set to  $V_{(PWMCHG\_th\_rising)}$ .

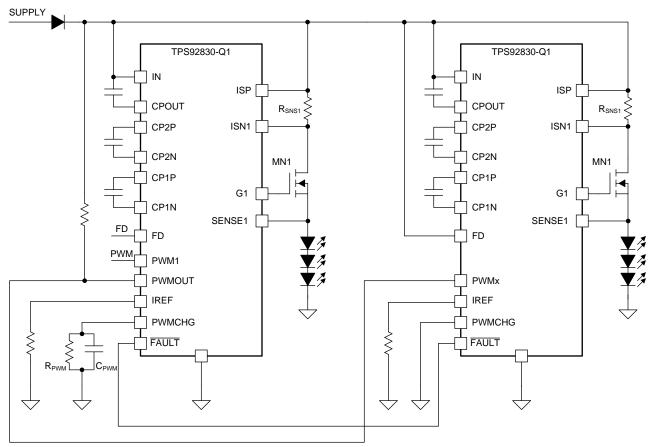

**図 23. PWM Generator Dual-Brightness Configuration**

An external resistor R<sub>(PWMEXT)</sub> and capacitor C<sub>(PWMEXT)</sub> are used to set the PWM cycle time.

$$t_{(PWM\_ON)} = R_{(PWMEXT)} \times C_{(PWMEXT)} \times In \left( \frac{V_{(PWMCHG\_th\_falling)} - I_{(PWMCHG)} \times R_{(PWMEXT)}}{V_{(PWMCHG\_th\_rising)} - I_{(PWMCHG)} \times R_{(PWMEXT)}} \right)$$

$$t_{(PWM\_OFF)} = R_{(PWMEXT)} \times C_{(PWMEXT)} \times In \left( \frac{V_{(PWMCHG\_th\_rising)}}{V_{(PWMCHG\_th\_falling)}} \right)$$

$$t_{(PWMEXT)} = \frac{1}{R_{(PWMEXT)} \times C_{(PWMEXT)} \times \left[ In \left( \frac{V_{(PWMCHG\_th\_falling)} - I_{(PWMCHG)} \times R_{(PWMEXT)}}{V_{(PWMCHG\_th\_rising)} - I_{(PWMCHG)} \times R_{(PWMEXT)}} \right) + In \left( \frac{V_{(PWMCHG\_th\_rising)}}{V_{(PWMCHG\_th\_falling)}} \right) \right]$$

$$t_{(PWMEXT)} = \frac{In \left( \frac{V_{(PWMCHG\_th\_falling)} - I_{(PWMCHG\_th\_rising)} - I_{(PWMCHG)} \times R_{(PWMEXT)}}{V_{(PWMCHG\_th\_falling)} - I_{(PWMCHG)} \times R_{(PWMEXT)}} \right) }{In \left( \frac{V_{(PWMCHG\_th\_falling)} - I_{(PWMCHG)} \times R_{(PWMEXT)}}{V_{(PWMCHG\_th\_rising)} - I_{(PWMCHG)} \times R_{(PWMEXT)}} \right) + In \left( \frac{V_{(PWMCHG\_th\_rising)}}{V_{(PWMCHG\_th\_falling)}} \right)$$

$$t_{(PWMCHG\_th\_rising)} = \frac{In \left( \frac{V_{(PWMCHG\_th\_falling)} - I_{(PWMCHG)} \times R_{(PWMEXT)}}{V_{(PWMCHG\_th\_rising)} - I_{(PWMCHG)} \times R_{(PWMEXT)}} \right) + In \left( \frac{V_{(PWMCHG\_th\_rising)}}{V_{(PWMCHG\_th\_falling)}} \right)$$

図 24. PWM Dimming Profile

### 8.3.4.4 Full Duty-Cycle Switch

The TPS92830-Q1 device can flexibly switch between the internal PWM modulation mode and the 100% duty-cycle mode by using the FD input. Once  $V_{(FD)}$  is higher than threshold  $V_{IH(FD)}$ , the internal PWM generator is bypassed and output is merely controlled by the PWM inputs.

If FD is HIGH, the PWMCHG current source is turned off and  $V_{(PWMCHG)}$  decays to GND through the external resistor-capacitor circuit. When FD falls below the threshold,  $V_{(PWMCHG)}$  increases from GND due to the internal charge current.

If FD is HIGH, PWM generator oscillation stops, and PWMOUT is controlled by PWM1 only.

External PWM inputs and internal PWM inputs are combined together for channel PWM dimming, or external PWM inputs can be used as channel enable inputs.

図 25. PWM Dimming Internal Block Diagram

### 表 1. Truth Table When Driving With PWM

| PWMx | FD   | PWMCHG | CHANNELx PWM          |

|------|------|--------|-----------------------|

| LOW  | X    | X      | LOW                   |

| HIGH | HIGH | Х      | HIGH                  |

| HIGH | LOW  | R-C    | PWM generated with RC |

### 表 2. Truth Table When Driving With PWMOUT

| PWM1 | FD   | PWMCHG | PWMOUT                |

|------|------|--------|-----------------------|

| LOW  | X    | X      | LOW                   |

| HIGH | HIGH | X      | HIGH                  |

| HIGH | LOW  | R-C    | PWM generated with RC |

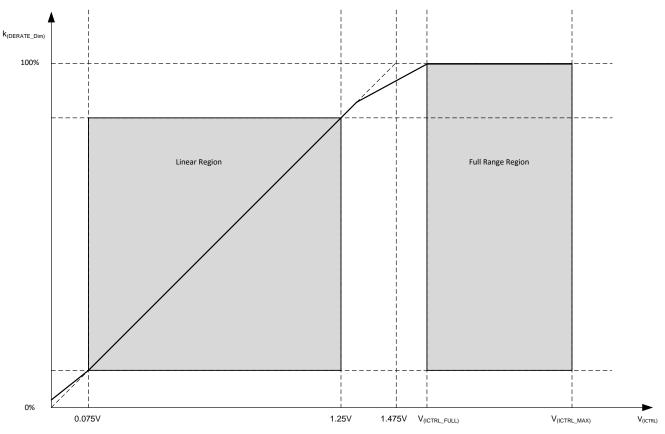

### 8.3.5 Analog Dimming

The TPS92830-Q1 device has a linear analog input pin, ICTRL, for output-current dimming. Voltage across the sense resistors is linearly reduced if the ICTRL input voltage  $V_{(ICTRL)}$  decreases. Analog dimming can be used for brightness control, LED bin brightness correction, and thermal protection with a thermistor. ICTRL also supports off-board connection for LED binning and thermistor connection.

### 8.3.5.1 Analog Dimming Topology

Voltage at the ICTRL pin,  $V_{(ICTRL)}$ , is used for analog dimming control. To set  $V_{(ICTRL)}$ , either a reference input voltage can be applied or a resistor between ICTRL and GND can be used.

When  $V_{(ICTRL)}$  is greater than  $V_{(ICTRL\_FULL)}$ , analog dimming is not enabled; thus the analog dimming ratio is at 100%.

When  $V_{(ICTRL)}$  is between  $V_{(ICTRL\_LIN\_BOT)}$  and  $V_{(ICTRL\_LIN\_TOP)}$ , the analog dimming ratio is directly proportional to  $V_{(ICTRL)}$ . The analog dimming ratio can be calculated using the following equation.  $V_{(ICTRL\_LIN\_BOT)}$  and  $V_{(ICTRL\_LIN\_TOP)}$  represent the ICTRL voltage boundaries of the linear region.

$$k_{(ICTRL\_DIM)} = \frac{V_{(ICTRL)}}{1.475 \,\text{V}} \times 100\% \tag{7}$$

When  $V_{ICTRL}$  is between  $V_{(ICTRL\_LIN\_TOP)}$  and  $V_{(ICTRL\_FULL)}$  or between  $V_{(ICTRL\_LIN\_BOT)}$  and 0, analog dimming is in a transition region, and linearity is not assured. Thus it is not recommended to use ICTRL in these regions.

Copyright © 2017, Texas Instruments Incorporated

図 26. Analog Dimming Ratio

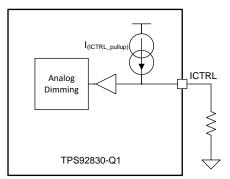

# 8.3.5.2 Internal High-Precision Pullup Current Source

An internal precision pullup current  $I_{(ICTRL\_pullup)}$  is provided within the device to minimize external component count.  $I_{(ICTRL\_pullup)}$  uses current reference  $I_{(IREF)}$  as reference. With the internal pullup current source, only an external resistor between the ICTRL pin and GND is needed to set the ICTRL voltage and the analog dimming ratio.

If a voltage source or resistor divider is used, the internal pullup current must be taken into account to set the analog dimming ratio accurately.

The pullup current source pulls the ICTRL pin voltage up to input voltage  $V_{(IN)}$  if the ICTRL pin is unconnected. When ICTRL is not used, it is recommended to leave the ICTRL pin floating.

Copyright © 2017, Texas Instruments Incorporated

図 27. Internal High-Precision Pullup Current Source

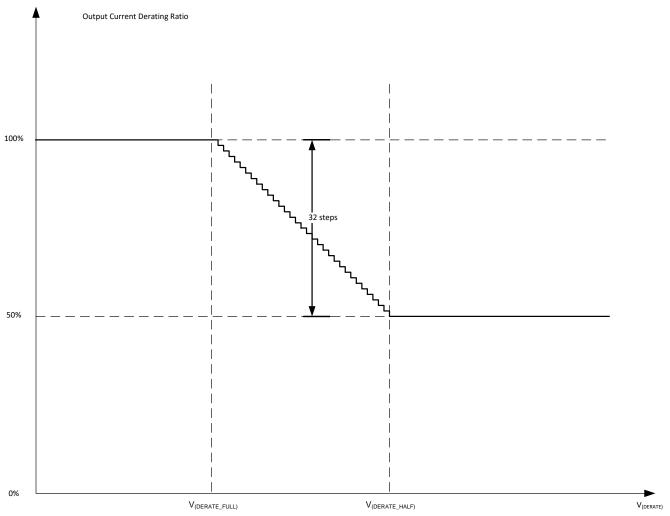

#### 8.3.6 Output Current Derating

The TPS92830-Q1 device has an integrated output-current derating function. Voltage across the sensing resistors is reduced if DERATE input voltage V<sub>DERATE</sub> increases. The output current derating function can be used for supply overvoltage protection and thermal protection with a thermistor. The DERATE current curves are divided into 32 steps between 100% and 50% with hysteresis.

In the case where DERATE is used for battery voltage sensing, the resistor-divider ratio can be set in a typical application as follows.

- In the normal supply-voltage range, for example, (9 V-16 V), the output-current-derating function is disabled.

- In the overvoltage range, for example, (18 V-24 V), the output current starts to derate and reaches 50% when  $V_{IN}$  is at 24 V.

- When the voltage is even higher, for example, (24 V-26 V), the output current is saturated at 50%.

### 8.3.6.1 Output-Current Derating Topology

Voltage at the DERATE pin, V<sub>(DERATE)</sub>, is used for output-current-derating control. To set the V<sub>(DERATE)</sub> voltage, a resistor divider on supply voltage V<sub>IN</sub> is typically used for supply overvoltage protection.

- When V<sub>DERATE</sub> is lower than V<sub>(DERATE\_FULL)</sub>, output current derating is not enabled; thus, output-current derating ratio k<sub>(DERATE Dim)</sub> is at 100%.

- When V<sub>DERATE</sub> is higher than V<sub>(DERATE HALF)</sub>, output current derating is limited to 50%; thus, output-current derating ratio k<sub>(DERATE Dim)</sub> is at 50%.

- When  $V_{(DERATE)}$  is between  $V_{(DERATE\_FULL)}$  and  $V_{(DERATE\_HALF)}$ , the output-current-derating ratio is negatively proportional to  $V_{(DERATE)}$  with 32 steps. Current derating is rounded to the next-lower step. The output-current-derating ratio can be calculated using the following equations.

$$V_{(DERATE\_STEP)} = \frac{V_{(DERATE\_HALF)} - V_{(DERATE\_FULL)}}{32}$$

$$k_{(DERATE\_Dim)} = 100\% - \left(\frac{V_{(DERATE)} - V_{(DERATE\_FULL)}}{V_{(DERATE\_STEP)}}\right) \times \frac{50\%}{32}$$

(9)

(9)

Copyright © 2017, Texas Instruments Incorporated

図 28. Output-Current Derating Profile

### 8.3.7 Diagnostics and Fault

The TPS92830-Q1 device provides advanced diagnostics and fault protection methods for automotive exterior lighting systems. The device is able to detect and protect from LED output short-to-GND as well as from LED output open-circuit scenarios. The device also supports a one-fails—all-fail fault bus that could flexibly fit different legislative requirements.

Copyright © 2017, Texas Instruments Incorporated

図 29. LED Open and Short Scenarios

### 8.3.7.1 LED Short-to-GND Detection

The TPS92830-Q1 device has channel-independent LED short-to-GND detection. Short-to-GND detection is only enabled during channel on-time. Once an LED short-to-GND failure is detected, the device turns off the faulty channel and retries automatically. If the auto-retry mechanism detects that the LED short-to-GND fault has been removed, the device resumes normal operation. section

The device monitors voltage  $V_{(SENSEx)}$  and compares it with the internal reference voltage to detect short-to-GND failures. If the period during which  $V_{(SENSEx)}$  falls below  $V_{(SG\_th\_rising)}$  is longer than the deglitch time of  $t_{(SG\_deg)}$ , the device asserts a short-to-GND fault on this channel. During the deglitch time period, if  $V_{SENSEx}$  rises above  $V_{(SG\_th\_falling)}$ , the timer is reset.

If a fault is detected, a constant-current source pulls the fault bus down. If FAULT is low, all devices connected to the fault bus are off in the fault mode.

### 8.3.7.2 LED Short-to-GND Auto Retry

Once the channel has asserted a short-to-GND fault, it automatically retries periodically. In PWM mode, the device sources  $I_{(Retry\_short)}$  through the SENSEx pin to pull up the LED loads with a pulse duration of  $t_{(SG\_retry\_OR)}$ . The device waits for  $t_{(SG\_retry\_OFF)}$  until the next retry pulse. Once auto retry detects that the short-to-GND fault is removed, the device resumes normal operation. During auto retry mode, the device ignores PWM inputs.

#### 8.3.7.3 LED Open-Circuit Detection

The TPS92830-Q1 device has channel-independent LED open-circuit detection. Once an LED open-circuit failure is detected, the device turns off the faulty channel and retries automatically. If the retry mechanism detects that the LED open-circuit fault is removed, the device resumes normal operation.

The device monitors MOSFET dropout voltage differences between the ISNx and SENSEx pins. Voltage difference  $V_{(ISNx)} - V_{(SENSEx)}$  is compared with internal reference voltage  $V_{(OPEN\_th\_rising)}$  to detect an LED open-circuit failure. If  $V_{(ISNx)} - V_{(SENSEx)}$  falls below the  $V_{(OPEN\_th\_rising)}$  voltage and it stays there longer than the deglitch time of  $t_{(OPEN\_deg)}$ , the device asserts an open-load fault on this channel. During the deglitching time period, if  $V_{(ISNx)} - V_{(SENSEx)}$  rises above  $V_{(OPEN\_th\_falling)}$ , the deglitch timer is reset.

In normal operation, the N-channel MOSFET operates in the saturation region with a gate-source voltage close to its threshold voltage. In this case, the drain-source voltage of the N-channel MOSFET is typically much higher than open-circuit threshold  $V_{(OPEN\_th\_rising)}$ . In the LED open-circuit condition, the N-channel MOSFET operates in the linear region with a gate-source voltage much higher than its threshold voltage. The N-channel MOSFET is fully on.

If a fault is detected, a constant-current source pulls the fault bus down. If the FAULT pin is low, all devices connected to the fault bus are off in the fault mode.

#### 8.3.7.4 LED Open-Circuit Auto Retry

Once the channel has asserted an open-circuit fault, it automatically retries periodically. The device sources  $I_{(Retry\_open)}$  through the SENSEx pin to pull up the LED loads with a pulse duration of  $t_{(OPEN\_retry\_ON)}$ . In PWM mode, the device waits for  $t_{(OPEN\_retry\_OFF)}$  until the next retry pulse. Once auto retry detects that the open-circuit fault has been removed, the device resumes normal operation. During auto retry mode, the device ignores PWM inputs. In the open-circuit scenario, the retry current cannot find a path to ground; thus, total current consumption does not increase.

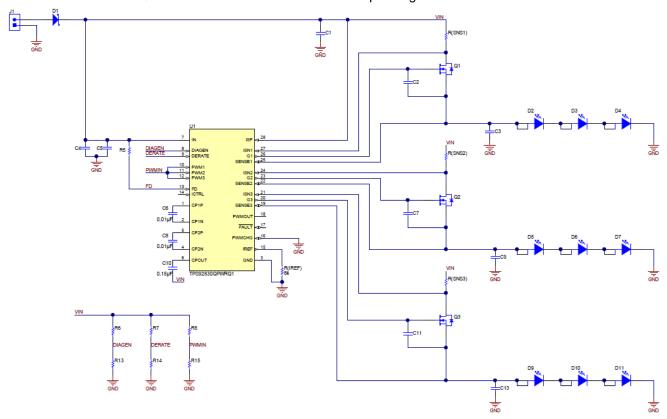

#### 8.3.7.5 Dropout-Mode Diagnostics

When the input voltage is not high enough to keep the external N-channel MOSFET in the constant-current saturation region, the TPS92830-Q1 device tries to regulate current by driving the external N-channel MOSFET in the linear region. This state is called the dropout mode, because voltage across the sense resistor is not able to reach the regulation threshold.

In dropout mode, LED open-circuit detection must be disabled via the DIAGEN input. Otherwise, the dropout mode would be treated as an LED open-circuit fault. The DIAGEN pin is used to avoid false diagnostics on an output channel due to low supply voltage.

When the DIAGEN voltage is low, the LED open-circuit detection is ignored. When the DIAGEN voltage is high, LED open-circuit detection resumes normal operation.

In dropout mode, the MOSFET is driven at maximum gate-source voltage to regulate current to the desired value. When the supply voltage increases, the MOSFET gate voltage is pulled down internally by a control loop. If the supply-voltage slew rate is fast, a high-current pulse can be observed on the LED for a short period of time. At the same time, the current-sense voltage may exceed the normal operating range and damage internal circuitry. A parallel diode or a current-limiting resistor less than 1 k $\Omega$  is recommended to clamp the voltage across the sensing resistor in the case of a large pulse current.

図 30. Resistor and Diode for Sense-Resistor Protection

#### 8.3.7.6 Overtemperature Protection

The TPS92830-Q1 device monitors device junction temperature. When the junction temperature reaches the thermal shutdown threshold  $T_{(TSD)}$ , all outputs shut down and the charge pump also stops working. Once the junction temperature falls below  $T_{(TSD)} - T_{(TSD\_HYS)}$ , the device resumes normal operation. During overtemperature protection, the FAULT bus is pulled low.

### 8.3.7.7 FAULT Bus Output With One-Fails-All-Fail

The TPS92830-Q1 device has a FAULT bus for diagnostics output. It also supports a one-fails—all-fail function with other TPS92830-Q1, TPS9261x-Q1, TPS92630-Q1, or TPS92638-Q1 devices.

In normal operation,  $\overline{\text{FAULT}}$  is weakly pulled up by internal pullup current source  $I_{(\text{FAULT\_pullup})}$  to a voltage higher than  $V_{\text{OH}(\text{FAULT})}$ . If any fault scenario occurs, the  $\overline{\text{FAULT}}$  bus is strongly pulled low by internal pulldown current source  $I_{(\text{FAULT\_pulldown})}$ . Once  $V_{(\text{FAULT})}$  falls below  $V_{\text{IL}(\text{FAULT})}$ , all outputs are shut down for protection. The faulty channel keeps retrying until the fault condition is removed. The charge pump is shut down, and current consumption is also reduced to  $I_{(\text{FAULT})}$  to save quiescent current.

If  $\overline{\mathsf{FAULT}}$  is externally pulled up with a current higher than  $I_{(\mathsf{FAULT\_pulldown})}$ , the one-fails–all-fail function is disabled and only the faulty channel is turned off. The charge pump remains operating normally, and the device is in normal operation mode. The  $\overline{\mathsf{FAULT}}$  bus is able to support up to 15 pieces of TPS92830-Q1, TPS92630-Q1, TPS92638-Q1, or TPS9261x-Q1 devices.

# 8.3.7.8 Fault Table

# 表 3. Fault Table With DIAGEN = HIGH

| FAULT TYPE               | DETECTION<br>MECHANISM                                                    | CHANNEL<br>STATE | DEGLITCH TIME           | FAULT BUS                                           | FAULT<br>HANDLING<br>ROUTINE                                                               | FAULT<br>RECOVERY |  |

|--------------------------|---------------------------------------------------------------------------|------------------|-------------------------|-----------------------------------------------------|--------------------------------------------------------------------------------------------|-------------------|--|

| FAULT FLOATING           | )                                                                         |                  |                         | !                                                   | -                                                                                          |                   |  |

| LED open-circuit         | V <sub>ISNx</sub> - V <sub>SENSEx</sub> < V <sub>(OPEN_th_rising)</sub>   | On               | t(OPEN_deg)             |                                                     | All channels<br>turned off. Pulsed<br>pullup retry of<br>faulty channel.                   |                   |  |

| LED short-to-<br>GND     | V <sub>SENSEx</sub> < V <sub>(SG_th_rising)</sub>                         | On               | <sup>t</sup> (SG_deg)   | Constant-current                                    | All channels<br>turned off. Pulsed<br>pullup retry of<br>faulty channel.                   | Auto recover      |  |

| LED short-to-<br>battery | V <sub>ISNx</sub> - V <sub>SENSEx</sub> < V <sub>(OPEN_th_rising)</sub>   | On or off        | t <sub>(OPEN_deg)</sub> | pundown                                             | All channels<br>turned off. Faulty<br>channel pulsed<br>pullup retry of<br>faulty channel. |                   |  |

| Overtemperature          | $T_J > T_{(TSD)}$                                                         | On or off        |                         |                                                     | All channels turned off.                                                                   |                   |  |

| FAULT EXTERNA            | LLY PULLED UP                                                             |                  | _                       |                                                     |                                                                                            |                   |  |

| LED open-circuit         | V <sub>ISNx</sub> - V <sub>SENSEx</sub> < V <sub>(OPEN_th_rising)</sub>   | On               | t <sub>(OPEN_deg)</sub> |                                                     | Only faulty channel turned off. Pulsed pullup retry of faulty channel.                     |                   |  |

| LED short-to-<br>GND     | V SENSEX < V(SG_th_rising)                                                | On               | t <sub>(SG_deg)</sub>   | Externally pulled up with internal constant-current | Only faulty<br>channel turned<br>off. Pulsed pullup<br>retry of faulty<br>channel.         | Auto recover      |  |