## **TI Designs**

JAJU206

# 12ビット、4/8チャネル、統合アナログ入力モジュール、 プログラマブル・ロジック・コントローラ (PLC)用

# TEXAS INSTRUMENTS

## **TI Designs**

TI Designsは、システムをすばやく評価してカスタマイズす るために必要な、手法、テスト、デザイン・ファイルなどの基 盤を提供し、開発期間の短縮に役立ちます。

# デザイン・リソース

| 出力モジュール用デザイン・<br>ファイル |

|-----------------------|

| IOコントローラ用デザイン<br>ファイル |

| 製品フォルダ                |

|                       |

TI E2E<sup>™</sup> Community

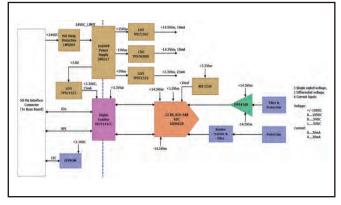

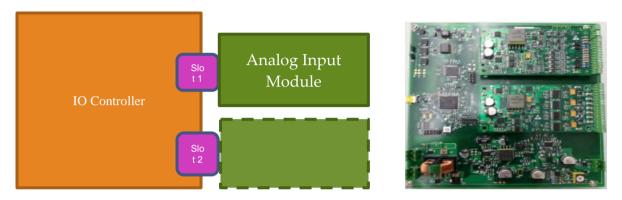

## ブロック図

Ask The Analog Experts

WEBENCH<sup>®</sup> Design Center

この資料は、Texas Instruments Incorporated(TI)が英文で記述した資料 を、皆様のご理解の一助として頂くために日本テキサス・インスツルメンツ (日本TI)が英文から和文へ翻訳して作成したものです。 資料によっては正規英語版資料の更新に対応していないものがあります。

資料によっくは止残央語放資料の更新に対応していないものかあります。 日本TIによる和文資料は、あくまでもTI正規英語版をご理解頂くための補 助的参考資料としてご使用下さい。

製品のご検討およびご採用にあたりましては必ず正規英語版の最新資料を ご確認下さい。

TIおよび日本TIは、正規英語版にて更新の情報を提供しているにもかかわ らず、更新以前の情報に基づいて発生した問題や障害等につきましては如 何なる責任も負いません。

## デザインの特長

- ESD、EFT、およびサージに対するIEC61000-4規 格に準拠した設計

- ●最大8チャネルのユーザー・プログラマブル入力を 備え、最大20%の範囲外測定を設定可能

- 4つの電圧入力:(シングルエンド×3、差動×1、イン ピーダンス > 1M)

- ±10V、±5V、±2.5V、0~10V、0~5V

外部リファレンスにより最大±12V

- 4つの電流入力:(入力インピーダンス250Ω時)

0~20mA、4~20mA

- デジタル絶縁型SPIインターフェイスを備えた12 ビットのSAR ADC

- 入力範囲全体の精度 電圧:フルスケールの±0.2%未満(25℃) 電流:フルスケールの±0.35%未満(25℃)

- 突入電流保護を備えたオンボードの絶縁型Flybuck電源

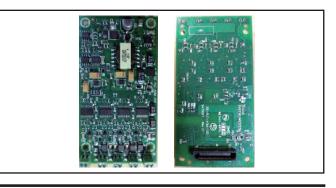

- スリムなフォーム・ファクタ:96×50.8×10mm(L×W×H)

- IOコントローラに接続可能で評価が容易 (TIDA-00123)

- LabViewベースのGUIによる機能テストおよび特性測定

# 主なアプリケーション

- PLC:電流および電圧入力モジュール

- リモートPLCおよびDCS

- データ・アクイジション・システム

- 試験機器、計測機器

TIDU192 翻訳版

最新の英語版資料 http://www.ti.com/lit/tidu192

## **Table of Contents**

| 1 |     | System Description                              | 3  |

|---|-----|-------------------------------------------------|----|

| 2 |     | Design Specification                            | 3  |

| 3 |     | Block Diagram                                   | 4  |

| 4 |     | Circuit design and Component Selection          | 5  |

|   | 4.1 | 1 ADC                                           | 5  |

|   | 4.2 | .2 Power Supply                                 | 7  |

|   | 4.3 | .3 Isolation                                    | 8  |

|   | 4.4 | .4 Interface                                    | 8  |

|   | 4.5 | .5 Analog Input Module SPI communication timing | 9  |

| 5 |     | Software Description                            |    |

| 6 |     | Test Setup                                      | 13 |

|   | 6.1 | .1 Hardware Test setup                          |    |

|   | 6.2 | .2                                              | 14 |

| 7 |     | Test Results                                    | 15 |

|   | 7.1 | .1 Typical performance characteristics          | 15 |

|   | 7.2 | .2 Results Summary                              |    |

|   | 7.3 | .3 Pre compliance Testing                       |    |

| 8 |     | References                                      |    |

|   | 8.2 | 2 Schematics                                    | 24 |

|   | 8.3 | .3 Bill of Materials                            |    |

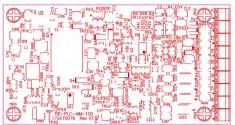

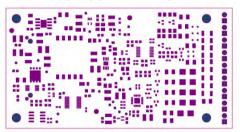

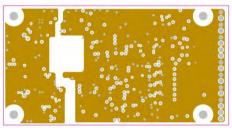

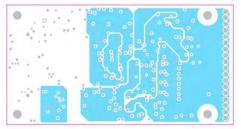

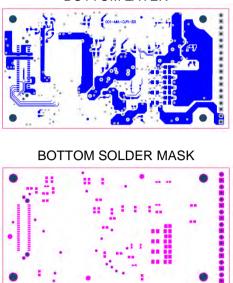

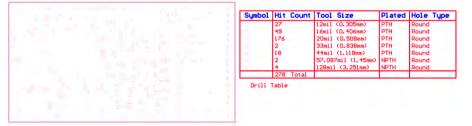

|   | 8.4 | .4 PCB Layout                                   |    |

|   | 8.5 | .5 Altium Project                               |    |

www.ti.com

## 1 システム説明

標準の産業用アナログ入力 (AI) モジュールは、一般に専用の電圧または電流入力です。ADS8638を使用したこのリファレンス・デザインでは、標準の産業用電圧および電流入力を測定します。モジュールには8個のチャネルがあります。

このアナログ入力モジュール・リファレンス・デザインは、PLC、データ・アクイジション、試験/計測システムなどの最終機器を開発するための評価モジュールとして設計されています。このデザインは、SPIインターフェイス用のデジタル・アイソレータおよび電源絶縁用のFlybuckトランスを備えた、絶縁型アナログ入力モジュールです。校正データやモジュール設定の格納用にオンボードEEPROMを搭載しています。各入力チャネルの端子はネジ式で、配線が簡単です。電源状態の表示用に、LEDが搭載されています。

このリファレンス・デザインは、アナログ入力モジュールを設計するための包括的なガイドとなります。異なる複数の範囲の電圧または電流入力を設定でき、スリムなフォーム・ファクタで提供されます。このモジュールは、IOコントローラ(TIDA-00123)に接続できるように設計され、すばやいテストや評価が可能です。また、産業環境に対するEMC規格に準拠するよう設計されています。デザイン・ファイルには、回路図、BOM、レイヤ・プロット、Altiumファイル、Gerberファイル、および使いやすいグラフィカル・ユーザー・インターフェイス(GUI)が含まれています。

アナログ入力モジュールは、以下に関してテスト済みです。

- > 絶縁型SPIインターフェイス

- > 電圧および電流入力の機能と精度

- > サージ、EFT、ESD: IEC61000-4規格に事前準拠

## 2 設計仕様

12ビット分解能のSAR ADCの構成は以下のとおりです。

- シングルエンド電圧

- 差動電圧

- シングルエンド電流

#### ソフトウェアでプログラミング可能な入力範囲

|   | Voltage | Current   |

|---|---------|-----------|

| • | ±10V,   | • 0-20 mA |

| • | ±5V,    | • 4-20 mA |

| • | ±2.5V,  |           |

| • | 0- 10V, |           |

| • | 0- 5V   |           |

\*最大20%の過電圧を測定するように設定可能

## 入力インピーダンス

| Voltage > 1M Ω | Current < 300 $\Omega$ |

|----------------|------------------------|

|                |                        |

#### 全体精度

| Voltage Input: ±0.2% full scale at 25 °C Curi | rrent Input: ±0.35% full scale at 25 °C |

|-----------------------------------------------|-----------------------------------------|

|-----------------------------------------------|-----------------------------------------|

#### 絶縁

| Power supply: 1500VAC  | Signal: 2500 |

|------------------------|--------------|

| I POWER SUDDIV TOUUVAU | 50081 2500   |

|                        | eignal: 2000 |

#### EMC

| Test                                      | Levels                 |

|-------------------------------------------|------------------------|

| IEC61000-4-2: Electro Static Discharge    | ±8k Air Discharge,     |

|                                           | ±4kV Contact Discharge |

| IEC61000-4-4 : Electrical Fast Transients | ±2kV, 5kHz             |

|                                           | ±2kV,100kHz            |

| IEC61000-4-5 : Surge                      | ±1kV Common Mode       |

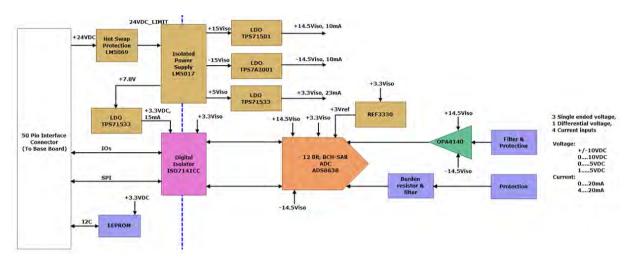

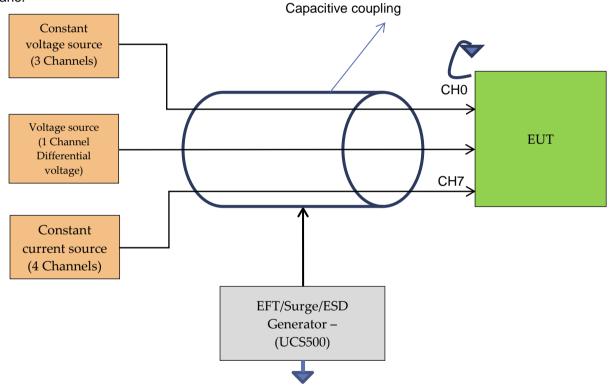

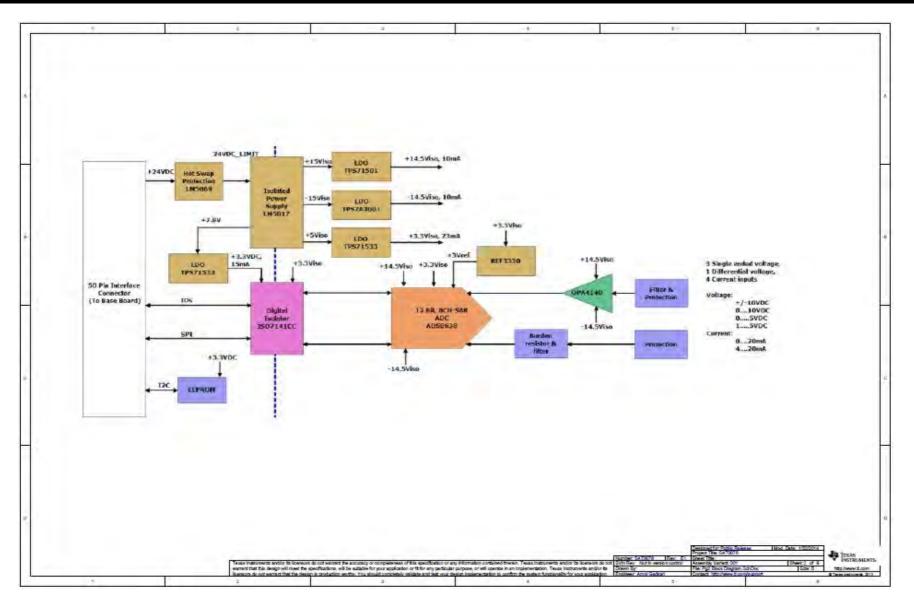

## 3 Block Diagram

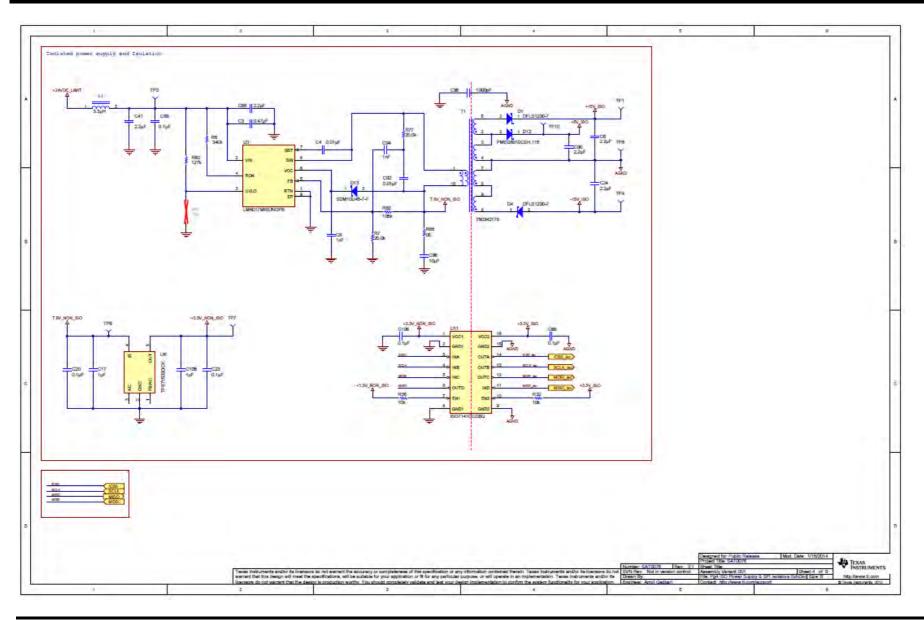

The Analog Input Module has the following blocks:

- 1. Analog-to-Digital Convertor (ADC)

- 2. Power supply

- 3. Isolation

- 4. Interface

#### Figure 1 Block Level Design

#### Analog-to-Digital Converter (ADC):

This Module utilizes TI's 12-Bit resolution ADS8638. This ADC has 8 multiplexed input channels with software programmable input ranges for individual channels. Maximum sampling rate is upto 1MSPS/ (Number of selected channels).Digital output of ADC is read over SPI interface. The module has an EEPROM that store all the calibration data and configuration.

#### Power Supply:

The required voltage rails for non-isolated and isolated sections are generated on-board using Flybuck converter topology. The voltage rails are derived from 24VDC from the IO Controller. The ADC and Op Amp needs +/-14.5V power supply. The ADC additionally needs 3.3V for digital interface and 3V reference. The power supply section uses LDO to reduce ripple.

#### Isolation:

Most AI modules require isolation from the backplane and other modules. This is typically accomplished by isolating the digital signals between the host processor/controller and the ADC in the AI Module. There are many topologies available to achieve the isolation but galvanic (capacitive) isolation has many advantages over other topologies and has been selected for this design. The Power supply isolation is achieved by the use of Flybuck configured transformer.

#### Interface:

The Analog Input Module has one 50 Pin connector for interface with IO Controller. This SPI signals, I2C signals and control signals from the IO controller card is connected to the AI module through this connector. Eight 2-pin connectors have been provided for connecting analog inputs and one 2-Pin connector for connecting system earth has been provided.

## 4 Circuit design and Component Selection

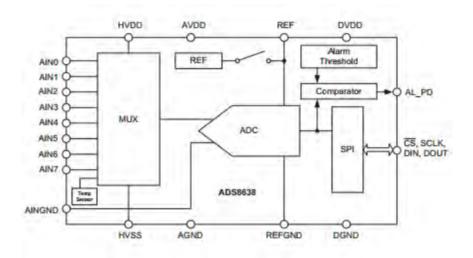

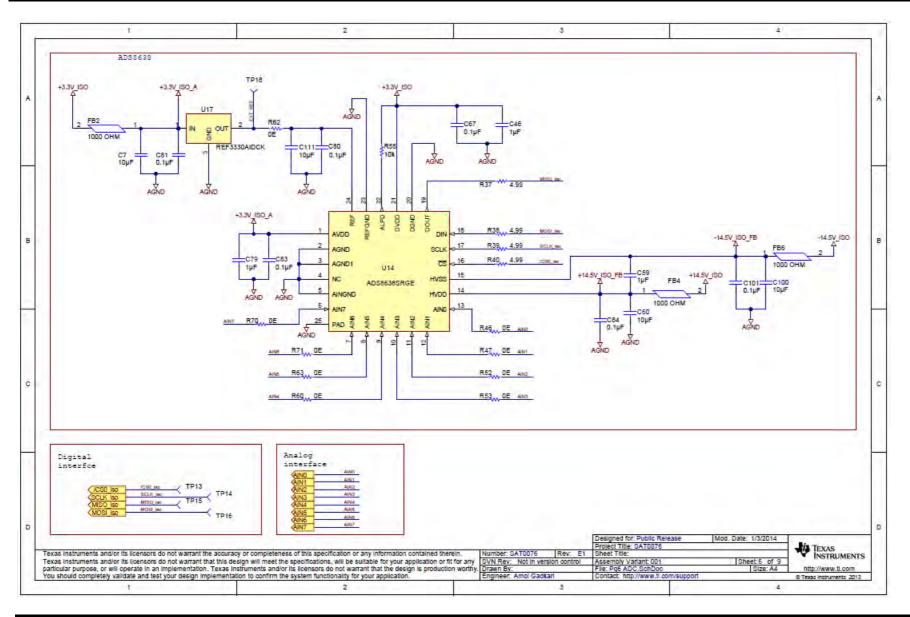

### 4.1 ADC

ADS8638 was chosen for this design for its wide bipolar and unipolar input range. ADS8638 is capable of measuring inputs up to  $\pm 10V$  at 1MSPS with no missing code and INL<  $\pm 1LSB$ . ADS8638 uses a capacitor-based switching method to create an adjustable input voltage range option. The device also features two preset alarms with hysteresis per channel. During normal operation, ADS8638 dissipates < 22.5 mW at 5V AVDD and  $\pm 15V$  supplies.

ADS8638 features software-selectable bipolar and unipolar ranges, has an internal reference (with an internal temperature sensor) with option to use an external reference. ADS8638 offers multiple software-programmable ranges  $\pm 10V$ ,  $\pm 5V$ ,  $\pm 2.5V$ , 0- 5V, and 0-10V with a 2.5V reference. Any of these ranges can be assigned to any analog input (for instance,  $\pm 10V$  can be assigned to AIN1  $\pm 2.5V$  to AIN2, 0- 10V can be assigned to AIN3, and so on). The Block Diagram is shown in figure2.

Figure 2 ADC Block Diagram

Bipolar Range Ideal Output Codes:

| Bipolar | Range | Ideal | Output | Codes |

|---------|-------|-------|--------|-------|

|---------|-------|-------|--------|-------|

| ±10V RANGE (V)        | ±5V RANGE (V)                              | ±2.5V RANGE (V)                              | IDEAL OUTPUT CODE |

|-----------------------|--------------------------------------------|----------------------------------------------|-------------------|

| 2 10 × (211-1)/211(2) | ≥ 5 × (2 <sup>11</sup> -1)/2 <sup>11</sup> | ≥ 2.5 × (2 <sup>11</sup> -1)/2 <sup>11</sup> | FFFb              |

| 10/211                | 5/211                                      | 2.5/211                                      | 801h              |

| 0                     | 0                                          | 0                                            | 800h              |

| -10/211               | -5/211                                     | -2.5/211                                     | 7FFh              |

| 5-10 × (211-1)/211    | 5-5 × (211-1)/211                          | 5-2.5 × (2 <sup>11</sup> -1)/2 <sup>11</sup> | 000h              |

Unipolar Range Ideal Output Codes:

Unipolar Range Ideal Output Codes

| INPUT SIGNAL        | (AINx - AINGND)                             |                   |

|---------------------|---------------------------------------------|-------------------|

| OV TO 10V RANGE (V) | OV TO 5V RANGE (V)                          | IDEAL OUTPUT CODE |

| ≥ 10 × (212- 1)/212 | 2 5 × (2 <sup>12</sup> - 1)/2 <sup>12</sup> | FFFh              |

| 10/212              | 5/212                                       | 001h              |

| < 10/212            | < 5/212                                     | 000h              |

## 4.1.1 ADC reference

The ADS8638 can be configured for internal or external reference. The external reference used is REF3330AIDCK, which allows increasing input range by 20%. An external reference can be connected to ADC using zero ohm resistors.

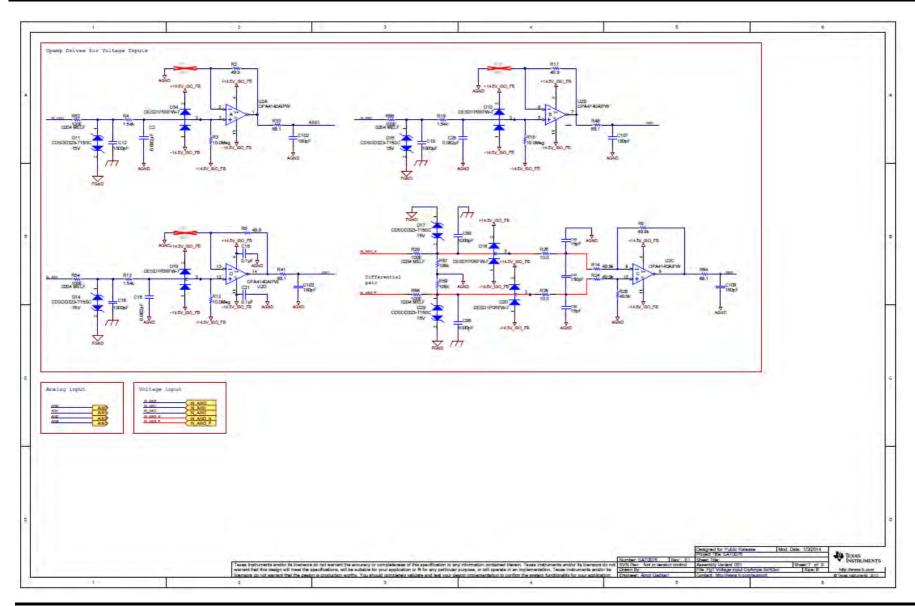

## 4.1.2 Voltage Input

The Analog Input Module has been configured for three single ended voltage inputs and one differential voltage input. The front end of the ADC input includes an OPA4140. The Op Amp is configured as unity gain amplifier and has RC low-pass filters. This filter at the input stage filters external noise. To achieve the best performance from the ADC, Op Amp input signal chain, Op Amp with high PSRR has been selected. The high input impedance of Op Amp reduces loading effect when external transducers are connected and also meets input impedance requirement of >1M $\Omega$ .

## 4.1.3 Current Input

The current input has an impedance of 250  $\Omega$ . The Current inputs are single ended and has the required protection and filtering at the front end.

## 4.1.4 ADC input filter

The RC filter is placed at the inputs to filter noise, minimize aliasing (i.e. frequency harmonics folding back into the pass band) and to serve as a "flywheel" or charge reservoir for the internal sample and hold circuitry of the ADC. The RC forms low pass filter with a cutoff frequency of  $1/2\pi$ RC. The voltage droop due to sampling capacitor of the ADC would be less than 5% of actual value if CFLT  $\ge 20$ \*CSH. Since CSH is 8pF, CFLT is set to 180pF for voltage channel and 0.1µF for current channel.

## 4.1.5 Filter and Protection for Surge, EFT and ESD

The input stage is designed to meet ESD, EFT and Surge requirements for industrial environment. Transient Voltage Suppressors (TVS diodes) are used to clamp the surge voltage.

Voltage Inputs:

| Surge<br>voltage | Surge<br>generator<br>resistor<br>(Ω) | CDN<br>resistance<br>(Ω) | Series<br>resistor<br>(Ω) | R total<br>(Ω) | Clamping<br>voltage of<br>the diode<br>(V) | Delta<br>(V) | Current<br>(A) | Wattage<br>(W) | Package     |

|------------------|---------------------------------------|--------------------------|---------------------------|----------------|--------------------------------------------|--------------|----------------|----------------|-------------|

| 1200             | 2                                     | 40                       | 100                       | 142            | 29.5                                       | 1170.5       | 8.24           | 243.16         | SOD-<br>323 |

| Selected Device     | Condition                | Wattage<br>(W) |

|---------------------|--------------------------|----------------|

|                     | Wattage at 25°C          | 400            |

| CD SOD323 - T 12 SC | Wattage de rated at 50°C | 320            |

CD SOD323 - T 12 SC has a clamp voltage of 29.5V at 14A. The IO signals need to meet 1kV surge level. To limit the maximum voltage seen by the Op Amp input stage, we need to limit the current to <14A for a voltage drop of 29.5V at the Op Amp inputs. For a 1kV surge and 10A max current through the TVS diodes, we will need a series resistance of  $100\Omega$  and of Pulse withstanding type.

| Surge<br>voltage | Surge<br>generator<br>resistor<br>(Ω) | CDN<br>resistance<br>(Ω) | Series<br>resistor<br>(Ω) | R total<br>(Ω) | Clamping<br>voltage of<br>the diode<br>(V) | Delta<br>(V) | Current<br>(A) | Wattage<br>(W) | Package             |

|------------------|---------------------------------------|--------------------------|---------------------------|----------------|--------------------------------------------|--------------|----------------|----------------|---------------------|

| 1200             | 2                                     | 40                       | 33                        | 75             | 29.2                                       | 1170.5       | 15.61          | 460.40         | SMB<br>(DO-<br>214A |

| Selected Device | Condition               | Wattage<br>(W) |

|-----------------|-------------------------|----------------|

|                 | Wattage at 25°C         | 600            |

| SMBJ18CA        | Wattage derated at 50°C | 480            |

SMBJ18CA has a clamp voltage of 29.2V at 20.6A. The IO signals need to meet 1kV surge levels. To limit the maximum voltage seen by the Op Amp input stage, we need to limit the current to <20.6A for a voltage drop of 29.2V at the Op Amp inputs. For a 1kV surge and 15A max current through the TVS diodes, we will need a series resistance of  $33\Omega$  and of Pulse withstanding type.

The ESD protection diodes also protect against overvoltage inputs. Layout guidelines have to be followed to ensure compliance to EMC standards. The protection devices are selected to dissipate the required energy.

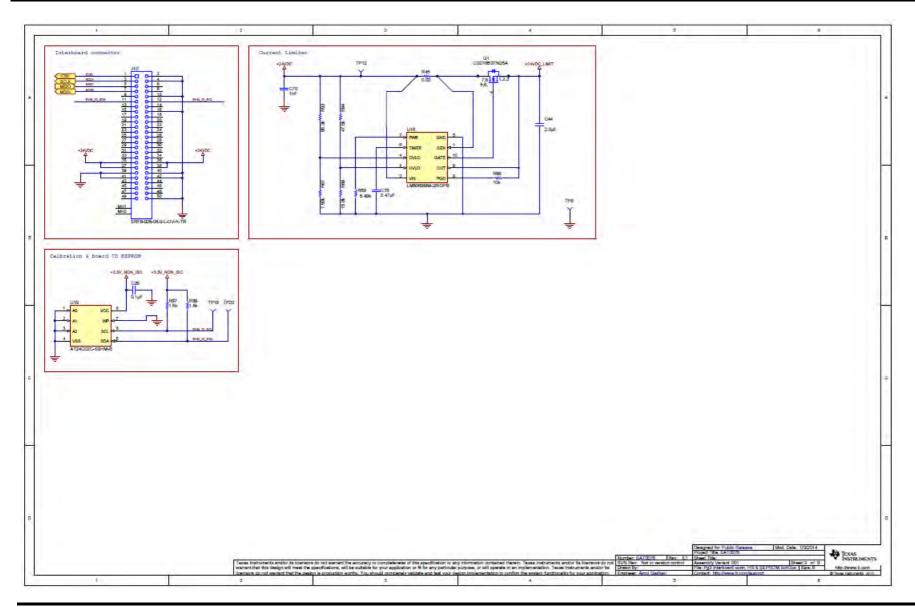

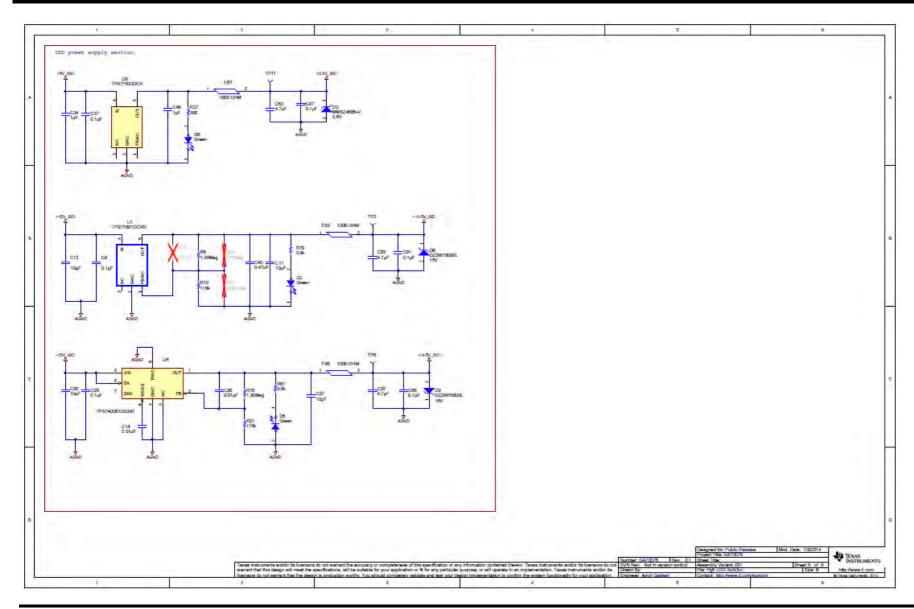

## 4.2 Power Supply

The Analog Input Module uses 24V DC from the IO Controller.

The LM5069 hot swap controller provides intelligent control of the power supply connections during insertion and removal of module from the powered IO Controller. The LM5069 provides in-rush current limiting during turn-on and monitoring of the load current for faults during normal operation. Additional functions include Under-Voltage Lock-Out (UVLO) and Over-Voltage Lock-Out (OVLO) to ensure voltage is supplied to the load only when the system input voltage is within a range. The inrush current of the module is limited to 2.75A.

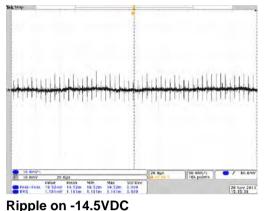

The ADC and Op Amps are supplied with +/- 14.5V, which is derived from Flybuck DC-DC converter (LM5017) followed by a low noise LDOs. A 0.47µF capacitor is placed near the LM5017 to provide a bypass path for the high frequency component of the switching current. This reduces the switching noise. The Flybuck DC-DC converter is designed to give +/-15V and 5V with a ripple of <50mV peak. A soft-start feature is implemented to the LM5017 to limit the inrush current.

The DC-DC converter output is given to LDO TPS71501DCKR and TPS7A3001, which has a PSRR of 55dB from 10kHz to 1MHz frequency range, refer <u>AN-2292</u>.

| an di bata per meneraktika at lana tangan milara di bahar di bata di tangan pertamanak kampatan an lan<br>Apar pada pertaman pertama perta | na <mark>hand kan di san kanalang kang sana na sana na kana na kang na kang na kang mana na kang mana kang na kang n<br/>Ina kang na kang na sana na kang na kang</mark> |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                  |  |  |  |  |

|                                                                                                                                                                                                                            | 1                                                                                                                                                                                                                                                |  |  |  |  |

TIDU192– January 2014

12-Bit, 4/8 Channel, Integrated Analog Input module for Programmable Logic Controllers (PLC)

#### Ripple on 3.3VDC power supply

Ripple on +14.5VDC

#### Ripple on -14.5VDC

#### 4.3 Isolation

#### 4.3.1 Power Isolation

The LM5017 based Flybuck Isolated Power Supply provides Galvanic Isolation to the IO controller. This Isolation is required to keep the IO controller protected from any unexpected overvoltage on the Analog input field connections. The level of isolation depends on the Coupled Inductor's specification. This design utilizes a coupled Inductor of 1500VAC, Isolation.

## 4.3.2 Digital Isolation

The IO Controller SPI is connected to the ADC SPI interface by the High Speed Digital Isolator ISO7141CC. 2.5kVrms Galvanic Isolation between IO Controller and Analog Input Module is maintained to protect IO Controller.

The SPI Signals isolated are: SCLK, MISO, MOSI, and /CS. Series termination resistors are provided to maintain Signal Integrity. In order to maintain isolation from the host controller, these signals are isolated through a digital isolator. The SPI Signals isolated are: SCLK, MISO, MOSI, CSO (Latch), CLR, SDRDY. The IO Controller is connected to the ADC by the High Speed Digital Isolator ISO7141CC and ISO7221. With this digital isolator the Host Processor on IO Controller maintains 2.5kVrms of galvanic isolation. Ten ohms termination resistance is placed near to the Isolators to maintain Signal Integrity.

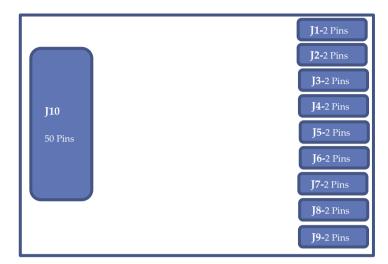

#### 4.4 Interface

The Analog Input Board has the following connector:

- 1. J1 to J8 : 2 Pin Screw Terminal type 2.54mm Pitch connectors for interfacing external inputs

- 2. J9 : 2 Pin Screw Terminal type 2.54mm Pitch connectors for connecting protective Earth

- 3. J10: 50 Pin connector for connecting SPI, I2C and Power Supply from the IO Controller

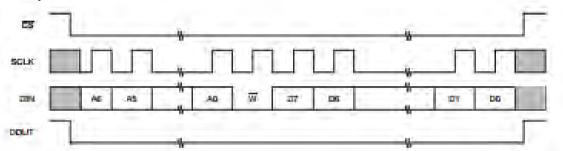

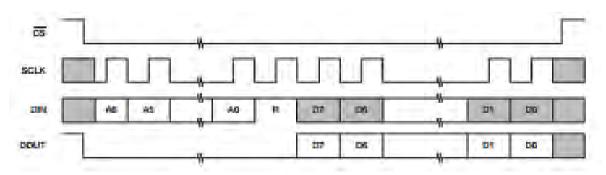

## 4.5 Analog Input Module SPI communication timing

#### **SPI Communication**

The Master and Slave transmit the data on the bus on one clock phase and read the data on the next/opposite clock phase. SPI communication works fine without bit shift as long as the total round trip propagation delay is less than half of the clock period. Using Digital Isolators on the SPI bus for isolation can reduce the operating speed due to its propagation delay. The max speed at which Analog. Input Module can operate with isolators is derived below:

SPI Communication with Isolation

| ADC clock to D <sub>out</sub> output delay | 33nsec (Max)    |

|--------------------------------------------|-----------------|

| Isolator propagation Delay                 | 45nsec (Max)    |

| MCU setup time                             | 17.15nsec (Min) |

| Total Delay                                | 95.15nsec       |

Max SPI clock speed up to which SPI works with isolator: 5.25MHz To increase the speed, CPLD solution has been implemented on the IO Controller board.

#### **5** Software Description

The ADS8638 internal registers are mapped in two pages: page 0 and page 1. Page 0 is selected by default after power-up and reset.

Page 0 registers are used to select the channel sequencing mode, program the configuration registers, and to read the alarm flags. Page 1 resisters are used to program the alarm thresholds for each channel and for the temperature sensor.

A brief overview is as described here. For details refer the datasheet of ADS8638.

| REGISTER                                  | REGISTER<br>ADDRESS<br>BITS[15:9] | DEFAULT<br>VALUE <sup>(9)</sup> | BIT 7                                       | BIT 6                                        | BIT 5                                      | BIT 4                                       | BIT 3                            | BIT 2                             | BIT 1                            | BIT 0                             |  |

|-------------------------------------------|-----------------------------------|---------------------------------|---------------------------------------------|----------------------------------------------|--------------------------------------------|---------------------------------------------|----------------------------------|-----------------------------------|----------------------------------|-----------------------------------|--|

| Channel Sequencing Contr                  | ol Registers                      |                                 |                                             |                                              |                                            |                                             | -                                |                                   |                                  |                                   |  |

| Manual                                    | 04h                               | 00h                             | 0                                           | c                                            | hannel Select[2                            | :0]                                         | F                                | Range Select[2:                   | 0]                               | Sel Temp<br>Sensor                |  |

| Auto                                      | 05h                               | 00h                             | Reset-Seq                                   | 0                                            | 0                                          | 0                                           | F                                | ange Select[2:                    | ange Select[2:0]                 |                                   |  |

| Holding the DIN line low cont<br>manual). | inuously (equivale                | nt to writing '0'               | to all 16 bits) du                          | ring device oper                             | nation as per Fig                          | gure 85 continue                            | es device operat                 | tion in the last s                | elected mode (a                  | no ofue                           |  |

| Configuration Registers                   |                                   |                                 |                                             |                                              |                                            |                                             |                                  |                                   |                                  |                                   |  |

| Reset-Device                              | 01h                               | 00h                             | 0                                           | 0                                            | 0                                          | 0                                           | 0                                | 0                                 | 0                                | Reset-Dev                         |  |

| Aux-Config                                | O6h                               | 08h                             | ٥                                           | Ū.                                           | o                                          | 0                                           | AL_PD<br>Control                 | Int Veer<br>Enable                | Temp<br>Sensor<br>Enable         | ٥                                 |  |

| Auto-Md Ch-Sel                            | OCh                               | 00h                             | Sel Ch0                                     | Sel Ch1                                      | Sel Ch2                                    | Sel Ch3                                     | Sel Ch4                          | Sel Ch5                           | Sel Ch6                          | Sel Ch7                           |  |

| Ch0-1 Range                               | 10h                               | 11h                             | 0                                           | Range Select Ch0[2:0]                        |                                            |                                             | 0                                | Ra                                | nge Select Ch1                   | 2:0]                              |  |

| Ch2-3 Range                               | 11h                               | 11h                             | 0                                           | Range Select Ch2[2:0]                        |                                            |                                             | 0                                | Ra                                | nge Select Ch3                   | 2:0]                              |  |

| Ch4-5 Range                               | 12h                               | 11h                             | 0                                           | Range Select Ch4[2:0]                        |                                            |                                             | 0                                | Ra                                | nge Select Ch5                   | 2:0]                              |  |

| Ch6-7 Range                               | 13h                               | 11h                             | 0                                           | Range Select Ch6[2:0]                        |                                            |                                             | 0                                | Range Select Ch7[2:0]             |                                  |                                   |  |

| Alarm Flag Registerss (Rea                | id-Only)                          |                                 |                                             |                                              |                                            |                                             |                                  |                                   |                                  | -                                 |  |

| Temp-Flag                                 | 20h                               | 00h                             | Tripped<br>Alarm Flag<br>Temperature<br>Low | Tripped<br>Alarm Flag<br>Temperature<br>High | Active Alarm<br>Flag<br>Temperature<br>Low | Active Alarm<br>Flag<br>Temperature<br>High | 0                                | 0                                 | Ū.                               | o                                 |  |

| Ch0-3 Tripped-Flag                        | 21h                               | 00h                             | Tripped<br>Alarm Flag<br>Ch0 Low            | Tripped<br>Alarm Flag<br>Ch0 High            | Tripped<br>Alarm Flag<br>Ch1 Low           | Tripped<br>Alarm Flag<br>Ch1 High           | Tripped<br>Alarm Flag<br>Ch2 Low | Tripped<br>Alarm Flag<br>Ch2 High | Tripped<br>Alarm Flag<br>Ch3 Low | Tripped<br>Alarm Flag<br>Ch3 High |  |

| Ch0-3 Active-Flag                         | 22h                               | 00h                             | Active Alarm<br>Flag Ch0<br>Low             | Active Alarm<br>Flag Ch0<br>High             | Active Alarm<br>Flag Ch1<br>Low            | Active Alarm<br>Flag Ch1<br>High            | Active Alarm<br>Flag Ch2<br>Low  | Active Alarm<br>Flag Ch2<br>High  | Active Alarm<br>Flag Ch3<br>Low  | Active Alam<br>Flag Ch3<br>High   |  |

| Ch4-7 Tripped-Flag                        | 23h                               | 00h                             | Tripped<br>Alarm Flag<br>Ch4 Low            | Tripped<br>Alarm Flag<br>Ch4 High            | Tripped<br>Alarm Flag<br>Ch5 Low           | Tripped<br>Alarm Flag<br>Ch5 High           | Tripped<br>Alarm Flag<br>Ch6 Low | Tripped<br>Alarm Flag<br>Ch6 High | Tripped<br>Alarm Flag<br>Ch7 Low | Tripped<br>Alarm Flag<br>Ch7 High |  |

| Ch4-7 Active-Flag                         | 24h                               | 00h                             | Active Alarm<br>Flag Ch4<br>Low             | Active Alarm<br>Flag Ch4<br>High             | Active Alarm<br>Flag Ch5<br>Low            | Active Alarm<br>Flag Ch5<br>High            | Active Alarm<br>Flag Ch6<br>Low  | Active Alarm<br>Flag Ch6<br>High  | Active Alarm<br>Flag Ch7<br>Low  | Active Alam<br>Flag Ch7<br>High   |  |

| Page Selection Register                   |                                   |                                 |                                             |                                              |                                            |                                             |                                  |                                   | -                                | -                                 |  |

| Page                                      | 7Eb                               | 00h                             | 0                                           | 0                                            | 0                                          | 0                                           | 0                                | 0                                 | 0                                | Page Addr                         |  |

#### Page 0 Register Map for the ADS8638

(1) All registers are reset to the default values at power-on or at device reset using the register settings method.

| REGISTER             | REGISTER<br>ADDRESS<br>BITS[15:9] | DEFAULT<br>VALUE <sup>(1)</sup> | BIT 7                               | BIT 6                  | BIT 5         | BIT 4        | BIT 3     | BIT 2        | BIT 1   | BIT 0   |  |  |  |

|----------------------|-----------------------------------|---------------------------------|-------------------------------------|------------------------|---------------|--------------|-----------|--------------|---------|---------|--|--|--|

| Alarm Threshold Reg  | isters                            |                                 |                                     |                        |               |              |           |              |         |         |  |  |  |

| TLA MSB              | 00h                               | 00h                             |                                     | TLA Hyst               | eresis[3:0]   |              | 1 m       | TLA          | [11:8]  |         |  |  |  |

| TLA LSB              | 01h                               | 00h                             |                                     |                        |               | TLA          | (7:0]     |              |         |         |  |  |  |

| THA MSB              | 02h                               | OOh                             |                                     | THA Hyst               | eresis[3:0]   |              | THA[11:8] |              |         |         |  |  |  |

| THA LSB              | 03h                               | OOh                             |                                     |                        |               | TH           | [7:0]     |              |         |         |  |  |  |

| ChOLA MSB            | 04h                               | DOh                             |                                     | ChO-LA Hy              | steresis[3:0] |              |           | Ch0-L        | A[11:8] |         |  |  |  |

| ChOLA LSB            | 05h                               | DOh                             |                                     | Ch0-LA[7:0]            |               |              |           |              | -       |         |  |  |  |

| ChOHA MSB            | OGh                               | OOh                             |                                     | Ch0-HA Hysteresis[3:0] |               |              |           | Ch0-H        | A[11:8] |         |  |  |  |

| ChOHA LSB            | 07h                               | 00h                             |                                     |                        |               | Ch0-ł        | HA[7:0]   |              |         |         |  |  |  |

| Ch1LA MSB            | 06h                               | 00h                             |                                     | Ch1-LA Hy              | steresis[3:0] | 1.00         |           | Ch1-L        | A[11:8] |         |  |  |  |

| Ch1LA LSB            | 09h                               | 00h                             | Ch1-LA[7:0]                         |                        |               |              |           |              |         |         |  |  |  |

| Ch1 HA MSB           | QAh                               | 00h                             |                                     | Ch1-HA Hy              | storesis[3:0] | 1000         | 1.1       | Ch1-H        | A[11:8] |         |  |  |  |

| Ch1 HA LSB           | OBh                               | 00h                             |                                     |                        |               | Ch1-ł        | HA[7:0]   |              |         |         |  |  |  |

| Ch2 LA MSB           | OCh                               | 00h                             | -                                   | Ch2-LA Hysteresis[3:0] |               |              |           | Ch2-L        | A[11:8] |         |  |  |  |

| Ch2 LA LSB           | ODh                               | OOh                             |                                     | Ch2-LA[7:0             |               |              |           |              |         |         |  |  |  |

| Ch2 HA MSB           | OEh                               | OOh                             |                                     | Ch2-HA Hysteresis[3:0] |               |              |           | Ch2-H        | A[11:8] |         |  |  |  |

| Ch2 HA LSB           | OFh                               | OOh                             | Ch2-H                               |                        |               |              | 4A[7:0]   |              |         |         |  |  |  |

| Ch3 LA MSB           | 10h                               | OOh                             | Ch3-LA Hysteresis[3:0]              |                        |               |              |           | Ch3-L        | A[11:8] |         |  |  |  |

| Ch3 LA LSB           | 11h                               | 00h                             | Ch3-LAI7                            |                        |               |              | A[7:0]    |              |         |         |  |  |  |

| Ch3 HA MSB           | 12h                               | 00h                             |                                     | Ch3-HA Hystoresis[3:0] |               |              |           | Ch3-HA[11:8] |         |         |  |  |  |

| Ch3 HA LSB           | 13h                               | 00h                             |                                     |                        |               | Ch3-ł        | HA[7:0]   |              |         |         |  |  |  |

| Ch4 LA MSB           | 14h                               | 00h                             |                                     | Ch4-LA Hy              | steresis[3:0] |              |           | Ch4-LA[11:8] |         |         |  |  |  |

| Ch4 LA LSB           | 15h                               | 00h                             |                                     |                        |               | Ch4-I        | A[7:0]    | _            |         |         |  |  |  |

| Ch4 HA MSB           | 16h                               | 00h                             |                                     | Ch4-HA Hy              | steresis[3:0] |              |           | Ch4-H        | A[11:8] |         |  |  |  |

| Ch4 HA LSB           | 17h                               | OOh                             |                                     |                        |               | Ch4-         | (A[7:0]   |              |         |         |  |  |  |

| Ch5 LA MSB           | 18h                               | OOh                             |                                     | Ch5-LA Hy              | steresis[3:0] |              |           | Ch5-L        | A[11:8] |         |  |  |  |

| Ch5 LA LSB           | 19h                               | OOh                             |                                     |                        |               | Ch5-         | A[7:0]    |              |         |         |  |  |  |

| Ch5 HA MSB           | tAh                               | OOh                             |                                     | Ch5-HA Hy              | steresis[3:0] | ( 10 mg - 10 |           | Ch5-H        | A[11:8] |         |  |  |  |

| Ch5 HA LSB           | 1Bh                               | 00h                             | _                                   |                        |               | Ch5-ł        | IA[7:0]   |              |         |         |  |  |  |

| Ch6 LA MSB           | 1Ch                               | 00h                             | 1                                   | Ch6-LA Hy              | storesis[3:0] |              |           | Ch6-L        | A[11:8] |         |  |  |  |

| Ch6 LA LSB           | 1Dh                               | 00h                             |                                     |                        |               | Ch6-I        | A[7:0]    |              |         |         |  |  |  |

| Ch6 HA MSB           | 1Eh                               | 00h                             |                                     | Ch6-HA Hy              | storesis[3:0] | 10.00        |           | Ch6-H        | A[11:8] |         |  |  |  |

| Ch6 HA LSB           | 1Fh                               | 00h                             |                                     |                        |               | Ch6-ł        | HA[7:0]   |              |         |         |  |  |  |

| Ch7 LA MSB           | 20h                               | OOh                             |                                     |                        |               |              | Ch7-L     | A[11:8]      |         |         |  |  |  |

| Ch7 LA LSB           | 21h                               | OOh                             |                                     |                        |               | Ch7-         | A[7:0]    |              | -       |         |  |  |  |

| Ch7 HA MSB           | 22h                               | OOh                             | Ch7-HA Hysteresis[3:0] Ch7-HA(11:8) |                        |               |              |           |              |         |         |  |  |  |

| Ch7 HA LSB           | 23h                               | OOh                             |                                     |                        |               | Ch7-ł        | HA[7:0]   |              | -       |         |  |  |  |

| Page Selection Regis | ter                               |                                 |                                     |                        |               |              | _         |              |         |         |  |  |  |

| Page                 | 7Fh                               | 00h                             | 0                                   | 0                      | 0             | 0            | 0         | 0            | 0       | Page Ad |  |  |  |

## Page 1 Register Map for the ADS8638

(1) All registers are reset to the default values at power-on or at device reset using the register settings method.

- Channel Sequencing Control Registers: There are two modes for channel sequencing: auto and manual mode

- Auto-scan mode: the device automatically scans the preselected channels in sequential order with a new channel selected for every conversion

- o Manual mode, the channel is manually selected for the next conversion

- In both modes, the preselected signal range is considered for each channel independently

- Configuration Registers: The configuration registers allow device configuration (signal range selection for individual channels, selection of channels for auto sequence, enabling/disabling of the internal reference and temperature sensor, and configuration of the AL\_PD pin as either an alarm output or a power-down input). All registers can be reset to the default values using the configuration register

- Alarm Flag Registers: The alarm conditions related to individual channels are stored in these

registers. The flags can be read when an alarm interrupt is received on the AL\_PD pin. There

are two types of flag for every alarm: active and tripped. The active flag is set to '1' under the

alarm condition (when data cross the alarm limit) and remains so as long as the alarm

condition persists. The tripped flag turns on the alarm condition similar to the active flag, but it

remains set until it is read. This feature relieves the device from having to track alarms

- Page Selection Register: The registers are arranged on two pages: page 0 and page 1. The page register selects the register page

- Alarm Threshold Setting Registers: The ADS8638 feature high and low alarms individually for the temperature sensor and each of the eight channels. Each alarm threshold is 12-bit wide

with a 4-bit hysteresis. This 16-bit setting is accomplished through two 8-bit registers associated with every high/low alarm

A typical programming sequence for the ADS868 is:

- 1. When module is powered up, by default ADC starts in manual mode channel 0, ±10V input range

- 2. Program the Configuration Registers (Page 0, Register 06h)

- 3. Program the Range Select Register (Page 0, Register 10h to 13h)

- 4. Program mode of operation:

- o Manual Mode: Page 0, Register 04h

- Auto Mode: Page 0, Register 05h

Write Cycle Command Word:

|     | 1.000     |           | REGIS     | TER ADI   | ORESS     | RD/<br>WR |           | DATA  |       |       |       |       |       |       |       |      |  |

|-----|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-------|-------|-------|-------|-------|-------|-------|-------|------|--|

| PIN | BR 15     | Bit 14    | Bit 13    | Bit 12    | Bit 11    | Bit 10    | Bit 9     | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | BR 0 |  |

| DIN | ADDR<br>6 | ADDR<br>5 | ADDR<br>4 | ADDR<br>3 | ADDR<br>2 | ADOR<br>1 | ADDR<br>0 | R/W   | DIN7  | DING  | DINS  | DIN4  | DIN3  | DIN2  | DIN1  | DINO |  |

Write cycle:

Read Cycle Command Word:

|      |           | REGISTER ADDRESS |           |           |           |           | RD/<br>WR |       |           |           |           |           |           |           |           |       |

|------|-----------|------------------|-----------|-----------|-----------|-----------|-----------|-------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-------|

| PIN  | Bit 15    | Bit 14           | Bit 13    | Bit 12    | Bit 11    | Bit 10    | Bit 9     | Bit 8 | Bit 7     | Bit 6     | Bit 5     | Bit 4     | Bit 3     | Bit 2     | Bit 1     | Bit 0 |

| DIN  | ADDR<br>6 | ADDR<br>5        | ADDR<br>4 | ADDR<br>3 | ADDR<br>2 | ADDR<br>1 | ADDR<br>0 | RW    | x         | x         | x         | ×         | x         | ×         | ×         | x     |

| DOUT | x         | x                | x         | x         | x         | x         | x         | x     | DOUT<br>7 | DOUT<br>6 | DOUT<br>5 | DOUT<br>4 | DOUT<br>3 | DOUT<br>2 | DOUT<br>1 | DOUT  |

Read Cycle:

## 6 Test Setup

#### 6.1 Hardware Test setup

#### Functional Test setup

The IO Controller has the required connectors and the MCU to interface with the Analog Input Module. 24V power input to the Analog Input Module is supplied by the IO Controller.

The IO Controller communicates with the Analog Input Module through an isolated SPI interface. A graphical user interface is provides to communicate with the IO Controller.

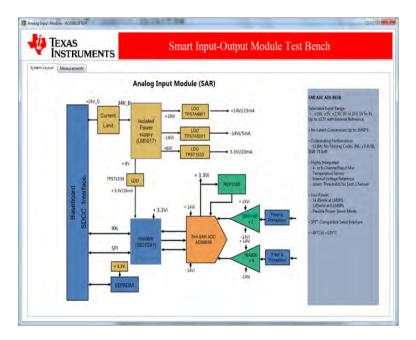

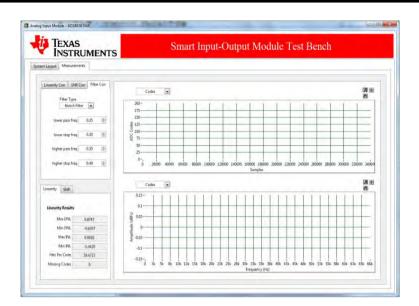

#### GUI to demonstrate the signal chain information

#### GUI to demonstrate the results

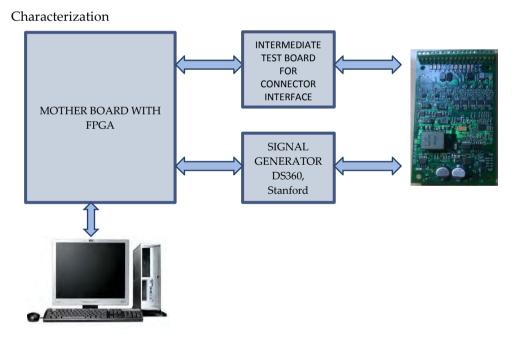

The design verification setup uses FPGA and GUI based Test Setup. The GUI on the PC connects to the FPGA based data capture card through USB communication. The FPGA based data capture card then controls the Analog Input Card via SPI interface. The setup has a precision signal generator (DS360, Stanford Research Systems), which feeds the analog input signal to the Analog Input Module. The Digital Output generated is measured by the data capture card. The GUI does the computation of results.

The GUI is LabView based software. It can set the below functionalities:

- 1. Configures all the registers in the ADS8638

- 2. The GUI controls data capture card to generate the required serial communication patterns

- 3. Reads the digitized data from the module

- 4. Post processing of the data

- 5. Result Options: SNR, ENOB, DNL, INL and CMRR

12-Bit, 4/8 Channel, Integrated Analog Input module for Programmable Logic Controllers (PLC)

## 7 Test Results

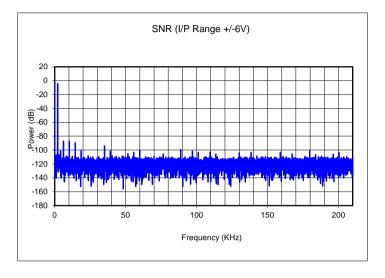

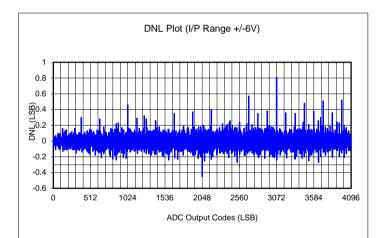

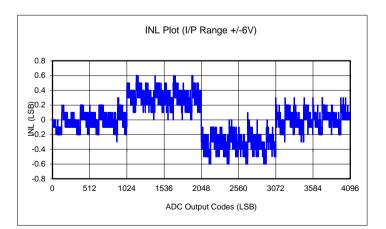

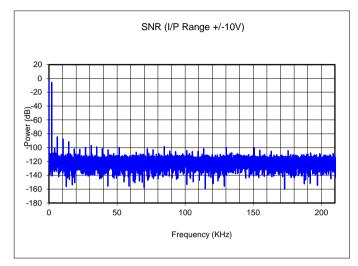

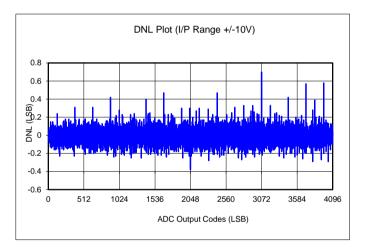

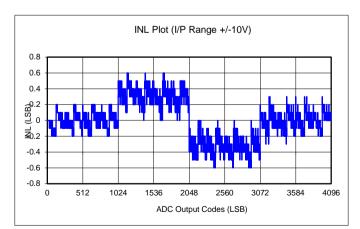

## 7.1 Typical performance characteristics

## 7.2 Results Summary

| Sr. No. | Parameter                    | 6V Range | 10V Range | Expected<br>Result | Note                                                       |

|---------|------------------------------|----------|-----------|--------------------|------------------------------------------------------------|

| 1       | Signal to Noise ratio        | 72.19dB  | 71.13dB   | 71.8dB             | Measured For 10V<br>Range , used ADC<br>internal reference |

| 2       | Total Harmonic<br>Distortion | 78.80dB  | 76.00dB   | 81 dB              |                                                            |

| 3       | SINAD                        | 71.33dB  | 69.92dB   | 71.3dB             |                                                            |

| 4       | SFDR                         | 82.83dB  | 78.71dB   | 83 dB              |                                                            |

| 5       | ENOB                         | 11.56    | 11.32     | 11.59              |                                                            |

| 6       | Max DNL                      | 0.8137   | 0.6995    | 1.6                |                                                            |

| 7       | Min DNL                      | -0.4491  | -0.3753   | -1                 |                                                            |

| 8       | Max INL                      | 0.636    | 0.7106    | 1.5                |                                                            |

| 9       | Min INL                      | -0.6254  | -0.7312   | -1.5               |                                                            |

| 10      | CMRR                         | 100 dB   | 110 dB    | 95 to 115<br>dB    | Measured at At 1KHz                                        |

| 11      | CMRR                         | 104 dB   | 110 dB    | 95 to 115<br>dB    | Measured at At 50Hz                                        |

#### Table 1 Measurement Results Summary

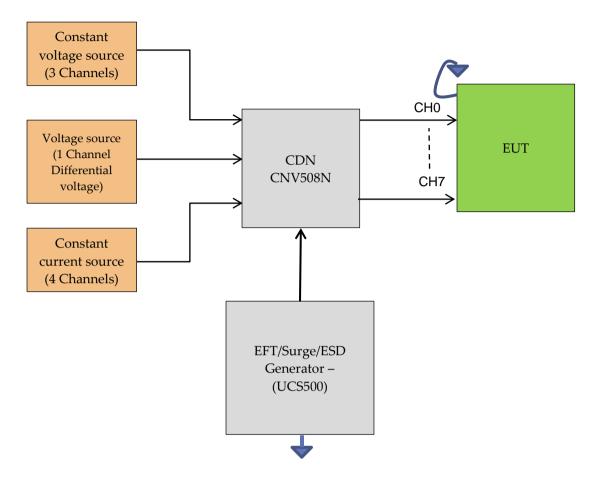

## 7.3 Pre compliance Testing

The Analog Input Module has been designed to meet standard EMC requirements for Industrial PLC application.

The following EMC tests have been performed

| Tests                      | Standards    |

|----------------------------|--------------|

| Electro Static Discharge   | IEC61000-4-2 |

| Electrical Fast Transients | IEC61000-4-4 |

| Surge                      | IEC61000-4-5 |

12-Bit, 4/8 Channel, Integrated Analog Input module for Programmable Logic Controllers (PLC)

#### Criteria and performance as per IEC61131-2

| Criteria | Performance (Pass) Criteria                                                                                                                                                                                                              |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A        | The Analog Output Module shall continue to operate as intended. No loss of function or performance even during the test.                                                                                                                 |

| В        | Temporary degradation of performance is accepted.<br>After the test Analog Output Module shall continue to<br>operate as intended without manual intervention.                                                                           |

| С        | During the test loss of functions accepted, but no<br>destruction of hardware or software.<br>After the test Analog Output Module shall continue to<br>operate as intended automatically, after manual restart<br>or power off/power on. |

The targeted accuracy for criteria A is

- Voltage Terminal: ±0.2% full scale at 25 °C

- Current Terminal: ±0.35% full scale at 25 °C

The next sections explain the test setup, procedures and observations.

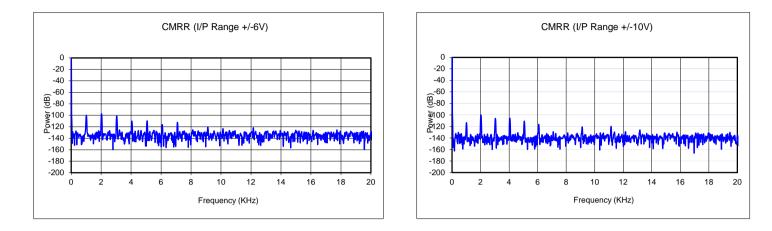

## 7.3.1 Test Set-Up

## 7.3.2 Electro Static Discharge (ESD): IEC61000 -4-2

## Test Level & Expected Performance

The ESD level at I/O connectors and the performance criteria expected are as follows:

| Generic Test Standard | Test Level                                                            | Performance                                                                               |

|-----------------------|-----------------------------------------------------------------------|-------------------------------------------------------------------------------------------|

| ESDIEC 61000-4-2      | 4 kV contact discharges –<br>Level 2<br>8 kV air discharges – Level 3 | Criteria B<br>(After the test Analog Input<br>Module continued to operate<br>as intended) |

## Setup Description

The ESD is injected to the EUT in two ways: Contact discharge or Air discharge.

The EUT is placed on a horizontal coupling plane (HCP) of 160 x 80cm dimensions on top of a wooden table 80cm high and located above ground reference plane. The EUT and its attached cables were isolated from the HCP by a thin insulating support of 0.5mm thickness. Electrostatic discharges were applied using an ESD gun directly (via contact or air discharges) or indirectly (via horizontal coupling plane). EUT operation was monitored after the test. The EUT is tested in active mode using unshielded 3m cables on IO ports.

- Connect the EUT as shown in the Test Setup. The shield Pin is connected to Local Earth same as the Test Generator

- Power on the EUT

- The test s/w is configured to check the Analog Input for level with in a tolerance limit of 0.2%

- If the input level exceed the tolerance limit, the LED on the IO Controller toggles

- Set the voltage level to 3VDC and current level to 8mA

- The ESD test is performed as per below test levels mentioned in below table

- After the test is performed, to check the degradation conduct a performance test

• Repeat the test by changing the input voltage level to 6VDC and current level to 16mA

#### Results

| Test No | Test Mode    | Observation |

|---------|--------------|-------------|

| 1       | Air +2kV     | PASS        |

| 2       | Air–2kV      | PASS        |

| 3       | Air +4kV     | PASS        |

| 4       | Air -4kV     | PASS        |

| 5       | Air +6kV     | PASS        |

| 6       | Air -6kV     | PASS        |

| 7       | Air +8kV     | PASS        |

| 8       | Air +8kV     | PASS        |

| 9       | Contact +1kV | PASS        |

| 10      | Contact -1kV | PASS        |

| 11      | Contact +2kV | PASS        |

| 12      | Contact -2kV | PASS        |

| 13      | Contact +4kV | PASS        |

| 14      | Contact -4kV | PASS        |

| 15      | HCP +2kV     | PASS        |

| 16      | HCP – 2kV    | PASS        |

| 17      | HCP +4kV     | PASS        |

| 18      | HCP -4kV     | PASS        |

| 19      | VCP +2kV     | PASS        |

| 20      | VCP – 2kV    | PASS        |

| 21      | VCP +4kV     | PASS        |

| 22      | HCP -4kV     | PASS        |

## 7.3.3 Electric Fast Transients test: EFT – IEC61000 – 4-4

#### Test Level & Expected Performance

The EFT burst at I/O connectors and the performance criteria expected are as follows:

| Generic Test Standard | Test Level                             | Performance |

|-----------------------|----------------------------------------|-------------|

| EFT/B IEC 61000-4-4   | ±2 KV at 5 KHz, 100KHz on signal ports | Criteria A  |

#### Description

#### Setup:

The burst signal is injected on all cables together using a Capacitive Coupling Clamp.

EUT is connected to auxiliary sources by unshielded cables. The lengths of the cables are set to 3m and cables are placed 10cm above the reference plane. The test is carried out with the EUT placed 10cm above the reference plane on insulating material, and with the EUT placed on the reference plane.

#### Monitoring:

- Connect the EUT as shown in the Test Setup. The shield Pin is connected to Local Earth same as the Test Generator.

- Power on the EUT

- The test s/w is configured to check the Analog Input for level with in a tolerance limit of 0.2%

- If the input level exceed the tolerance limit, the LED on the IO Controller toggles

- Set the voltage level to 3VDC and current level to 8mA

- The EFT test is performed as per below test levels mentioned in below table

- After the test is performed, to check the degradation conduct a performance test

- Repeat the test by changing the input voltage level to 6VDC and current level to 16mA

Results

٠

12-Bit, 4/8 Channel, Integrated Analog Input module for Programmable Logic Controllers (PLC)

Result summary to be updated with observations.

| Test No | Test Mode         | Observation |

|---------|-------------------|-------------|

| 1       | + 0.5 kV , 5kHz   | PASS        |

| 2       | - 0.5 kV , 5kHz   | PASS        |

| 3       | + 1 kV , 5kHz     | PASS        |

| 4       | - 1 kV , 5kHz     | PASS        |

| 5       | + 1.5 kV , 5kHz   | PASS        |

| 6       | - 1.5 kV , 5kHz   | PASS        |

| 7       | + 2 kV , 5kHz     | PASS        |

| 8       | - 2 kV , 5kHz     | PASS        |

| 9       | + 0.5 kV , 100kHz | PASS        |

| 10      | - 0.5 kV , 100kHz | PASS        |

| 11      | + 1 kV , 100kHz   | PASS        |

| 12      | - 1 kV , 100kHz   | PASS        |

| 13      | + 1.5 kV , 100kHz | PASS        |

| 14      | - 1.5 kV , 100kHz | PASS        |

| 15      | + 2 kV , 100kHz   | PASS        |

| 16      | - 2 kV , 100kHz   | PASS        |

## 7.3.4 SURGE- IEC61000 -4-5

## Test Level & Expected Performance

The Common-Mode Surge at I/O connectors and the performance criteria expected are as follows:

| Generic Test Standard | Test Level              | Performance                                                                                                              |

|-----------------------|-------------------------|--------------------------------------------------------------------------------------------------------------------------|

| Surge IEC 61000-4-5   | ±1kV CM on signal ports | Criteria B<br>(After the test Analog Input<br>Module continued to operate as<br>intended without manual<br>intervention) |

#### Description

#### Setup:

The EUT and analog input cable were placed on non-conductive support 10cm above a reference ground plane. Surge was injected into analog input cable (I/O cable) for testing via Coupling Decoupling Network. The EUT operation was monitored before and after the test.

EUT operation monitored after the test. All the eight channels were monitored after the test by the MCU (on IO Controller) and compared with a Set Value (equivalent of the external constant voltage or current source). The Error should be within accuracy as mentioned in Section 6.3.1. Method of monitoring:

- Connect the EUT as shown in the Test Setup. The shield Pin is connected to Local Earth same as the Test Generator.

- Power on the EUT

- The test s/w is configured to check the Analog Input for level with in a tolerance limit of 0.2%

- If the input level exceed the tolerance limit, the LED on the IO Controller toggles

- Set the voltage level to 3VDC and current level to 8mA

- The Surge test is performed as per below test levels mentioned in below table

- After the test is performed, to check the degradation conduct a performance test

- Conduct the test by changing the input voltage level to 6VDC and current level to 16mA

#### Results

| Test No | Test Mode | Observation |

|---------|-----------|-------------|

| 1       | + 0.5 kV  | PASS        |

| 2       | - 0.5 kV  | PASS        |

| 3       | + 1 kV    | PASS        |

| 4       | - 1 kV    | PASS        |

#### 8 References

- 1. Texas Instruments Application Report, Noise Analysis in Operational Amplifier Circuits, SLVA043A, 1999

- 2. Op Amp Noise Theory and Applications Literature Number SLOA082 Design files

## 8.1.1 Terminology

#### Signal-to-Noise Ratio (SNR)

SNR is a measure that compares the level of a desired signal to the level of background noise. It is defined as the ratio of signal power to the noise power. The Signal-to-Noise Ratio (SNR) specification provides information regarding the noise energy excluding the fundamental and harmonic energy present in the frequency spectrum for a particular input frequency. The SNR calculation usually integrates noise till Nyquist frequency.

#### SNR = P<sub>SIGNAL</sub> / P<sub>NOISE</sub>

SNR = 10 log10 (Signal Power 2 / (Sum of all harmonic amplitudes without  $F_{IN}$  and without DC) \* 2)

#### Total Harmonic Distortion (THD)

The Total Harmonic Distortion (THD) specification provides information regarding the harmonic energy present in the frequency spectrum for a particular input frequency. The frequency spectrum is typically shown till the Nyquist frequency and the THD calculation usually takes into account all the harmonics energy till Nyquist. Harmonics beyond Nyquist fall back into the frequency spectrum as noise or spurious tone. These are taken care of in the SNR and SINAD specifications.

THD = Summation of harmonic energy / Fundamental input energy

#### Signal-to-Noise and Distortion (SINAD)

The Signal-to-Noise and Distortion (SINAD) specification provides information regarding the noise and harmonic energy present in the frequency spectrum.

SINAD = Fundamental input energy / Summation of noise + distortion energy

#### Spurious Free Dynamic Range (SFDR)

The Spurious Free Dynamic Range (SFDR) specification provides information regarding the difference between maximum amplitude tone in frequency spectrum and the fundamental input tone.

SFDR = Fundamental input energy – Max (all frequency bins except fundamental)

#### Differential Non Linearity (DNL) and Integral Non Linearity (INL)

DNL is the deviation between two analog values corresponding to adjacent input digital values. Ideally, any two adjacent digital codes correspond to output analog voltages that are exactly one LSB apart. Any deviation from the ideal step width (LSB) is the Differential Non-Linearity. DNL errors accumulate to produce a total Integral Non-Linearity (INL). DNL and INL values are usually specified using one of the following units: LSB or %FSV

#### Common-Mode Rejection Ratio (CMRR)

The common-mode rejection ratio (CMRR) is the tendency of the devices to reject common noise from the input signal.

CMRR = Output Signal power (dB) – 20 log (Voltage Range/Input power)

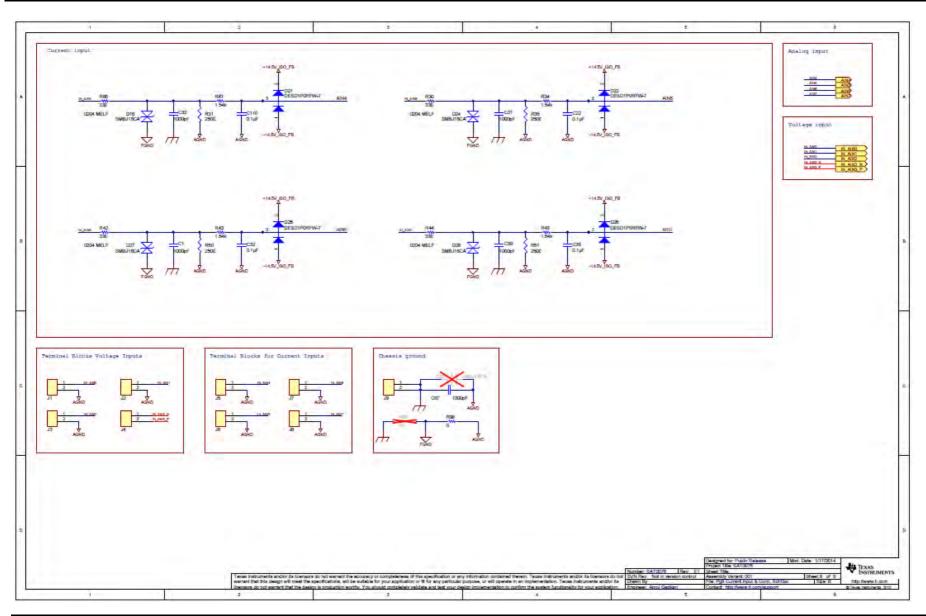

## 8.2 Schematics

| Page 2 |                                                 |                                    |           |  | - |          |                  |   |

|--------|-------------------------------------------------|------------------------------------|-----------|--|---|----------|------------------|---|

|        | Ebok Diagnete                                   |                                    |           |  |   |          |                  |   |

| Page 3 | 50 Pin Connector to EVM Board, Hot Swap contro  | der, UEFROM                        |           |  |   | Tastalor | Revision History | - |

| Page 4 | section of the section by suck Power Supply for | +15V_(50,-15V_(50, 15V_50) and (5) | V_NON_IBD |  |   | Testinot | NON              |   |

| Page 5 | LDD to generate +14.5V_ISO, -14.5V_ISO and +    | SSUB0                              |           |  |   |          |                  |   |

| Page 6 | AGE                                             |                                    |           |  |   |          |                  |   |

| Page 7 | Votage insut                                    |                                    |           |  |   |          |                  |   |

| Page 8 | Carsed input, consectors                        |                                    |           |  |   |          |                  |   |

| Page 9 | Mounting holes, Fidadela Merking                |                                    |           |  |   |          |                  |   |

<sup>12-</sup>Bit, 4/8 Channel, Integrated Analog Input module for Programmable Logic Controllers (PLC)

12-Bit, 4/8 Channel, Integrated Analog Input module for Programmable Logic Controllers (PLC)

12-Bit, 4/8 Channel, Integrated Analog Input module for Programmable Logic Controllers (PLC)

TEXAS INSTRUMENTS www.ti.com

12-Bit, 4/8 Channel, Integrated Analog Input module for Programmable Logic Controllers (PLC) TIDU192– January 2014

TIDU192– January 2014 12-Bit, 4/8 Channel, Integrated Analog Input module for Programmable Logic Controllers (PLC) 31 Copyright © 2013, Texas Instruments Incorporated

## 8.3 Bill of Materials

| Fitted | Description                                   | Designator                                                                                                            | Manufacturer             | PartNumber         | Quantity | RoHS | PackageReference |

|--------|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|--------------------------|--------------------|----------|------|------------------|

| Fitted | Printed Circuit Board                         | !PCB                                                                                                                  | Any                      | SAT0076            | 1        | 0    |                  |

| Fitted | CAP, CERM, 1000pF, 2KV 10%<br>X7R 1206        | C1, C12, C16,<br>C19, C31, C33,<br>C36, C39, C87,<br>C98, C99                                                         | Johanson Dielectrics Inc | 202R18W102KV4E     | 11       | Y    | 1206             |

| Fitted | CAP, CERM, 0.082uF, 50V, +/-10%,<br>X7R, 0805 | C2, C15, C28                                                                                                          | AVX                      | 08055C823KAT2A     | 3        | Y    | 0805             |

| Fitted | CAP, CERM, 0.47uF, 100V, +/-10%, X7R, 1206    | C3                                                                                                                    | MuRata                   | GRM31MR72A474KA35L | 1        | Y    | 1206             |

| Fitted | CAP, CERM, 0.01uF, 100V, +/-5%,<br>X7R, 0603  | C4, C14, C26,<br>C92                                                                                                  | AVX                      | 06031C103JAT2A     | 4        | Y    | 0603             |

| Fitted | CAP, CERM, 2.2uF, 25V, +/-10%,<br>X7R, 0805   | C6, C24, C90                                                                                                          | MuRata                   | GRM21BR71E225KA73L | 3        | Y    | 0805             |

| Fitted | CAP, CERM, 10uF, 35V, +/-20%,<br>X7R, 1210    | C7, C11, C13,<br>C27, C30, C60,<br>C96, C100,<br>C111                                                                 | Taiyo Yuden              | GMK325AB7106MM-T   | 9        | Y    | 1210             |

| Fitted | CAP, CERM, 1uF, 50V, +/-10%,<br>X5R, 0603     | C8, C17, C34,<br>C46, C48, C59,<br>C79, C105                                                                          | MuRata                   | GRM188R61H105KAALD | 8        | Y    | 0603             |

| Fitted | CAP, CERM, 0.1uF, 50V, +/-10%,<br>X7R, 0603   | C9, C18, C20,<br>C21, C23, C25,<br>C29, C37, C47,<br>C67, C68, C80,<br>C81, C83, C84,<br>C89, C91, C95,<br>C101, C106 | Kemet                    | C0603C104K5RACTU   | 20       | Y    | 0603             |

| Fitted | CAP, CERM, 0.1uF, 50V, +/-5%,<br>X7R, 0805    | C22, C32, C35,<br>C110                                                                                                | AVX                      | 08055C104JAT2A     | 4        | Y    | 0805             |

| Fitted | CAP, CERM, 15pF, 50V, +/-5%,<br>C0G/NP0, 0402 | C38, C43                                                                                                              | MuRata                   | GRM1555C1H150JA01D | 2        | Y    | 0402             |

| Fitted | CAP, CERM, 0.47uF, 50V, 10%, X5R, 0603        | C40, C78                                                                                                              | Taiyo Yuden              | UMK107ABJ474KA-T   | 2        | Y    | 0603             |

| Fitted | CAP, CERM, 2.2uF, 100V, +/-10%,<br>X7R, 1210  | C41, C44, C88                                                                                                         | MuRata                   | GRM32ER72A225KA35L | 3        | Y    | 1210             |

| Fitted | CAP, CERM, 150pF, 50V, +/-5%,<br>C0G/NP0, 0603                                                                                                                                                                  | C42                                                                | AVX                     | 06035A151JAT2A          | 1  | Y | 0603                         |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|-------------------------|-------------------------|----|---|------------------------------|

| Fitted | CAP, CERM, 4.7uF, 50V, +/-10%, X5R, 0805                                                                                                                                                                        | C53, C93, C97                                                      | TDK                     | C2012X5R1H475K125AB     | 3  | Y | 0805                         |

| Fitted | CAP, CERM, 1000pF, 100V, +/-<br>20%, X7R, 0603                                                                                                                                                                  | C70, C94                                                           | AVX                     | 06031C102MAT2A          | 2  | Y | 0603                         |

| Fitted | CAP, CERM, 180pF, 50V, +/-5%,<br>C0G/NP0, 0603                                                                                                                                                                  | C102, C103,<br>C107, C109                                          | AVX                     | 06035A181JAT2A          | 4  | Y | 0603                         |

| Fitted | Diode, Schottky, 200V, 1A,<br>PowerDI123                                                                                                                                                                        | D1, D4                                                             | Diodes Inc.             | DFLS1200-7              | 2  | Y | PowerDI123                   |

| Fitted | LED SmartLED Green 570NM                                                                                                                                                                                        | D2, D5, D8                                                         | OSRAM                   | LG L29K-G2J1-24-Z       | 3  |   | 0603                         |

| Fitted | Diode, Zener, 3.6V, 500mW, SOD-<br>123                                                                                                                                                                          | D3                                                                 | Vishay-Semiconductor    | MMSZ4685-V              | 1  | Y | SOD-123                      |

| Fitted | Diode, Zener, 15V, 1W, SOD-123                                                                                                                                                                                  | D6, D9                                                             | Panasonic               | DZ2W15000L              | 2  | Y | SOD-123                      |

| Fitted | Diode, P-N, 70V, 0.2A, SOT-323                                                                                                                                                                                  | D10, D18, D19,<br>D20, D21, D22,<br>D25, D26, D34                  | Diodes Inc              | DESD1P0RFW-7            | 9  | Y | SOT-323                      |

| Fitted | Diode, TVS, ARRAY, 15V, SOD323                                                                                                                                                                                  | D11, D14, D15,<br>D17, D29                                         | Bourns Inc.             | CDSOD323-T15SC          | 5  | Y | SOD-323                      |

| Fitted | Diode, Schottky, 60V, 1A, SOD-<br>123F                                                                                                                                                                          | D12                                                                | NXP Semiconductor       | PMEG6010CEH,115         | 1  | Y | SOD-123F                     |

| Fitted | Diode, Schottky, 45V, 0.1A, SOD-<br>523                                                                                                                                                                         | D13                                                                | Diodes Inc.             | SDM10U45-7-F            | 1  | Y | SOD-523                      |

| Fitted | TVS 18 VOLT 600 WATT BI-DIR<br>SMB                                                                                                                                                                              | D16, D24, D27,<br>D28                                              | Littelfuse Inc          | SMBJ18CA                | 4  |   | SMB                          |

| Fitted | FERRITE CHIP 1000 OHM 300MA<br>0603                                                                                                                                                                             | FB1, FB2, FB3,<br>FB4, FB5, FB6                                    | TDK Corporation         | MMZ1608B102C            | 6  | Y | 0603                         |

| Fitted | [NoValue], [NoValue], [NoValue],<br>[NoValue], [NoValue], [NoValue],<br>Mountin hole, NPTH Drill 3.2mm,<br>Mountin hole, NPTH Drill 3.2mm,<br>Mountin hole, NPTH Drill 3.2mm,<br>Mountin hole, NPTH Drill 3.2mm | FID1, FID2,<br>FID3, FID4,<br>FID5, FID6,<br>MH1, MH2,<br>MH3, MH4 |                         |                         | 10 |   |                              |

| Fitted | Terminal Block, 4x1, 2.54mm, TH                                                                                                                                                                                 | J1, J2, J3, J4,<br>J5, J6, J7, J8,<br>J9                           | On Shore Technology Inc | OSTVN02A150             | 9  | Y | TERM_BLK, 2pos<br>2.54mm     |

| Fitted | Receptacle, 0.8mm, 25x2, SMT                                                                                                                                                                                    | J10                                                                | Samtec                  | ERF8-025-05.0-L-DV-K-TR | 1  | Y | 25x2 Socket Strip            |

| Fitted | Inductor, Chip, ±10%                                                                                                                                                                                            | L1                                                                 | Panasonic               | ELJ-EA3R3MF             | 1  |   | 1210                         |

| Fitted | Thermal Transfer Printable Labels,<br>0.650" W x 0.200" H - 10,000 per roll                                                                                                                                     | LBL1                                                               | Brady                   | THT-14-423-10           | 1  | Y | PCB Label 0.650"H<br>0.200"W |

12-Bit, 4/8 Channel, Integrated Analog Input module for Programmable Logic Controllers (PLC)

TEXAS INSTRUMENTS www.ti.com

| Fitted | MOSFET, N-CH, 60V, 50A, SON<br>5x6mm | Q1                                           | Texas Instruments     | CSD18537NQ5A       | 1 | Y | SON 5x6mm |

|--------|--------------------------------------|----------------------------------------------|-----------------------|--------------------|---|---|-----------|

| Fitted | RES, 49.9 ohm, 1%, 0.063W, 0402      | R2, R9, R17                                  | Vishay-Dale           | CRCW040249R9FKED   | 3 | Y | 0402      |

| Fitted | RES, 10.0Meg ohm, 1%, 0.063W, 0402   | R3, R12, R18                                 | Vishay-Dale           | CRCW040210M0FKED   | 3 | Y | 0402      |

| Fitted | RES, 1.54k ohm, 1%, 0.125W, 0805     | R4, R13, R19,<br>R34, R43, R49,<br>R61       | Vishay-Dale           | CRCW08051K54FKEA   | 7 | Y | 0805      |

| Fitted | RES, 1.30Meg ohm, 1%, 0.125W, 0805   | R5, R15                                      | Vishay-Dale           | CRCW08051M30FKEA   | 2 | Y | 0805      |

| Fitted | RES, 340k ohm, 1%, 0.1W, 0603        | R6                                           | Vishay-Dale           | CRCW0603340KFKEA   | 1 | Y | 0603      |

| Fitted | RES, 20.0k ohm, 1%, 0.1W, 0603       | R7, R77                                      | Yageo America         | RC0603FR-0720KL    | 2 | Y | 0603      |

| Fitted | RES, 49.9k ohm, 0.1%, 0.1W, 0603     | R8, R14, R24,<br>R28                         | Yageo America         | RT0603BRD0749K9L   | 4 | Y | 0603      |

| Fitted | RES, 118k ohm, 0.1%, 0.1W, 0603      | R10                                          | Yageo America         | RT0603BRD07118KL   | 1 | Y | 0603      |

| Fitted | RES, 115k ohm, 0.1%, 0.1W, 0603      | R21                                          | Yageo America         | RT0603BRD07115KL   | 1 | Y | 0603      |

| Fitted | RES, 10.0 ohm, 1%, 0.1W, 0603        | R25, R26                                     | Vishay-Dale           | CRCW060310R0FKEA   | 2 | Y | 0603      |