Design Guide: TIDA-01606

# 10kW、双方向、3 相、3 レベル (T タイプ) インバータと PFC のリファレンス・デザイン

# TEXAS INSTRUMENTS

# 概要

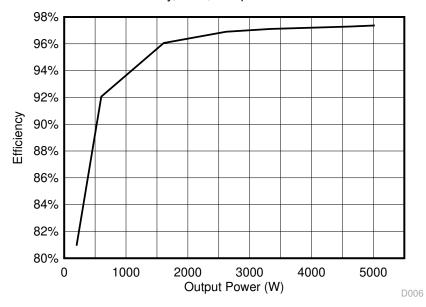

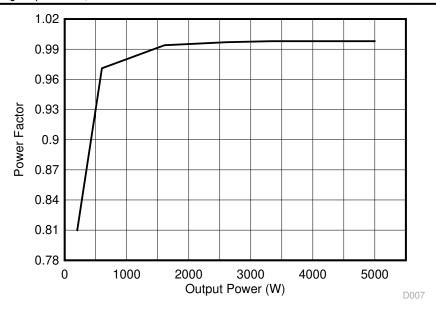

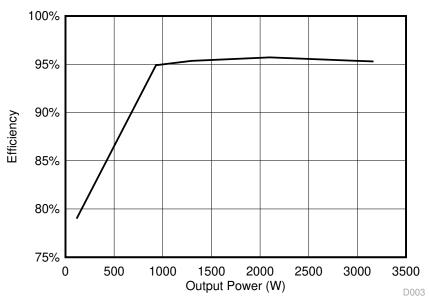

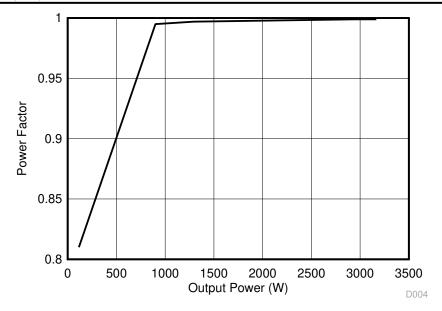

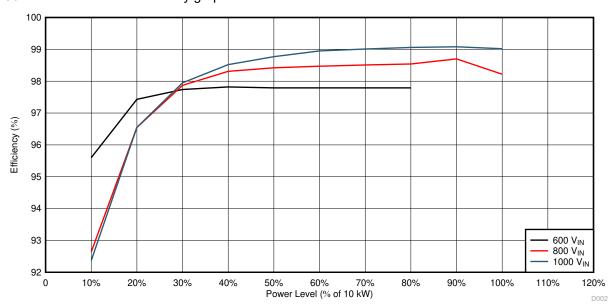

このリファレンス・デザインでは、双方向 3 レベル、3 相、SiC ベースのアクティブ・フロント・エンド (AFE) インバータおよび PFC 段を実装する方法の概要を紹介します。このデザインでは、50kHz のスイッチング周波数と LCL 出力フィルタを使用して、磁気素子のサイズを縮小しています。99% のピーク効率を達成しています。このデザインは、DQドメインに完全な 3 相 AFE 制御を実装する方法を示しています。制御とソフトウェアは、実際のハードウェアと、ループ内ハードウェア (HIL) のセットアップ上で検証されます。

# リソース

TIDA-01606 デザイン・フォルダ プロダクト・フォルダ TMS320F28379D C2000WARE-DIGITALPOWER-SDK ツール・フォルダ UCC21710, UCC5320 プロダクト・フォルダ TMDSCNCD28379D ツール・フォルダ プロダクト・フォルダ AMC1306M05, OPA4340 LM76003、PTH08080W プロダクト・フォルダ TLV1117LV, OPA350 プロダクト・フォルダ UCC14240 プロダクト・フォルダ

TIのTIE2E<sup>™</sup> サポート・エキスパートにお問い合わせください。

# 特長

- 定格公称入力電圧 DC 800V、最大入力電圧 DC 1000V、最大電力 10kW/10kVA (400V AC L-L 50Hz または 60Hz 時)

- スイッチング周波数 50kHz のコンパクトな出力 LCL フィルタ

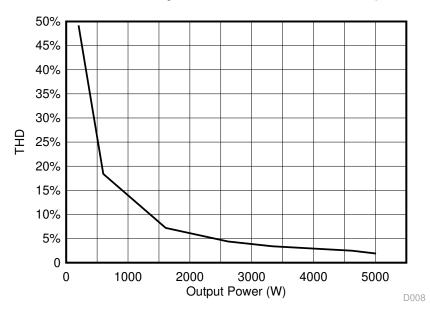

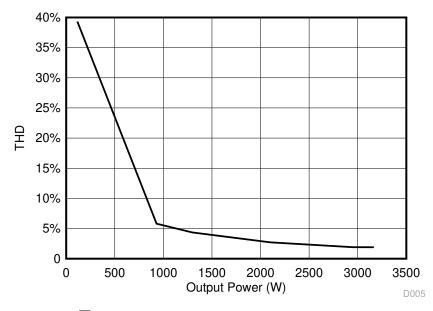

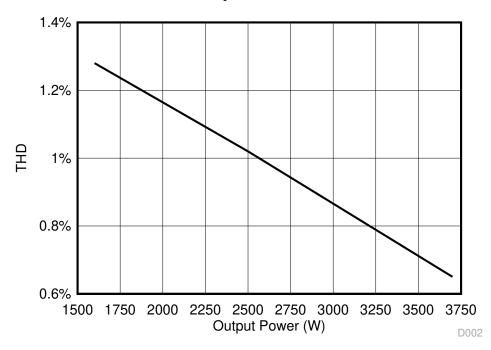

- 全負荷時の 2% 未満の出力電流全高調波歪み (THD)

- 強化絶縁付きの絶縁ドライバ UCC21710 により高電 圧の SiC MOSFET を駆動し、UCC5320S により中電 圧の SiC MOSFET を駆動

- 負荷電流制御および監視を目的とする AMC1301 を 使用した絶縁型電流検出

- 三角関数演算ユニット (TMU) を使用してフェーズ・ロック・ループ (PLL) の計算を高速化するデジタル制御用 TMS320F28379D 制御カード、保護機能を実装するためのコンパレータ・サブシステム、制御ループをコプロセッサにオフロードする制御補償器アクセラレータ (CLA)

# アプリケーション

- ストリング・インバータ

- セントラル・インバータ

- オンボード・チャージャ (OBC) およびワイヤレス・チャージャ

- DC 充電 (バッテリ) ステーション

- ポータブル DC チャージャ

- エネルギー・ストレージ電力変換システム (PCS)

STRUMENTS System Description www.tij.co.jp

# 1 System Description

Modern commercial scale solar inverters are seeing innovation on two fronts, which lead to smaller, higher efficiency products on the market:

- The move to higher voltage solar arrays

- Reducing the size of the onboard magnetics

By increasing the voltage to 1000-V or 1500-V DC from the array, the current can be reduced to maintain the same power levels. This reduction in current results in less copper and smaller power conducting devices required in the design. The reduction in di/dt also reduces the stress on electrical components. However, sustained DC voltages of > 1 kV can be difficult to design to, or even find components that can survive it.

To compensate for the voltage stresses generated by high-voltage solar arrays, new topologies of solar inverters have been designed. Traditional half bridges block the full input voltage on each switching device. By adding additional switched blocking and conduction components, the overall stress on the device can be significantly reduced. This reference design shows how to implement a three-level converter. Higher level converters are also possible, further increasing the voltage handling capability.

Additional power density in solar electronics is also being enabled by moving to higher switching speeds in the power converters. As this design shows, even a modestly higher switching speed reduces the overall size requirement of the output filter stage—a primary contributor to the design size.

Traditional switching devices have a limit in how quickly they can switch high voltages, or more appropriately, the dV/dt ability of the device. This slow ramp up and down increases conduction loss because the device spends more time in a switching state. This increased switch time also increases the amount of dead time required in the control system to prevent shoot-through and shorts. The solution to this has been developed in newer switching semiconductor technology like SiC and GaN devices with high electron mobility. This reference design uses SiC MOSFETs alongside TI's SiC gate driver technology to demonstrate the potential increase in power density.

Similarly for Onboard Chargers (OBC) higher power chargers (11 kW and 22 kW) are increasingly required. For which three phase PFC is necessary, this design shows implementation of three phase PFC using DQ control and presents the complete control loop model.

#### 1.1 Key System Specifications

表 1-1. Key System Specifications

| PARAMETER                    | SPECIFICATIONS       | DETAILS       |

|------------------------------|----------------------|---------------|

| Output power                 | 10 kW                | セクション 2.3     |

| Output voltage               | Three-phase 400-V AC | セクション 2.3     |

| Output frequency             | 50 or 60 Hz          | セクション 2.3     |

| Output current               | 18 A (max)           | セクション 2.3     |

| Nominal input voltage        | 800-V DC             | セクション 2.3     |

| Input voltage range          | 600-V to 1000-V DC   | セクション 2.3     |

| Inverter switching frequency | 50 kHz               | セクション 2.3     |

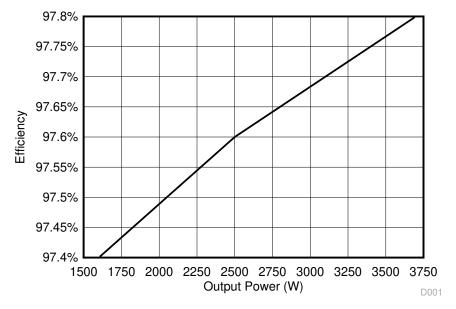

| Efficiency                   | 99%                  | セクション 2.3.1.5 |

| Power density                | 1 kW/L+              |               |

# 2 System Overview

# 2.1 Block Diagram

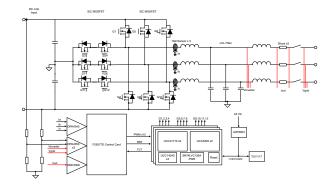

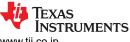

図 2-1. TIDA-01606 Block Diagram

This reference design is comprised of four separate boards that intercommunicate. The following boards work in tandem to form this three-phase inverter reference design:

- · A power board, comprising all of the switching device, LCL filter, sensing electronics, and power structure

- A TMS320F28379D control card to support the DSP

- Three gate driver cards, each with two UCC21710 and two UCC5320 gate drivers

- A DC bus voltage measuring board (TIDA-01606 ISOHVCARD)

#### 2.2 Highlighted Products

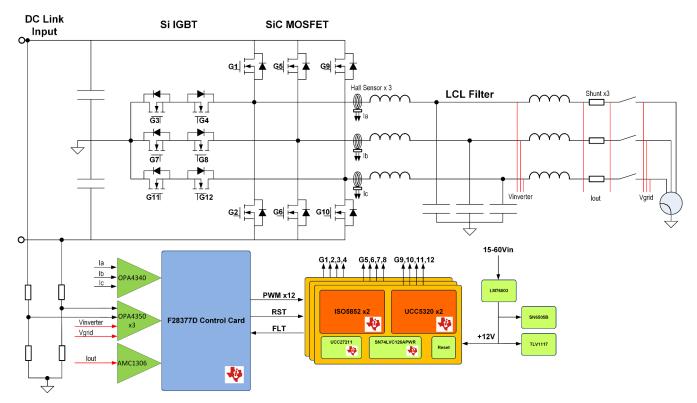

#### 2.2.1 UCC21710

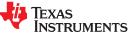

The UCC21710 device is a 5.7-kV<sub>RMS</sub>, reinforced isolated gate driver for Insulated-Gate Bipolar Transistors (IGBT) and SiC MOSFETs with split outputs, providing 10-A source and 10-A sink current. The input side operates from a single 3-V to 5.5-V supply. The output side allows for a supply range from minimum 13 V to maximum 33 V. Two complementary CMOS inputs control the output state of the gate driver. The short propagation time of 130 ns provides accurate control of the output stage. UCC21710 integrates short circuit protection, detected via Overcurrent detection, with a fast response time needed to protect SiC MOSFETs.

- 150-kV/µs minimum common-mode transient immunity (CMTI)

- Split outputs to provide 10-A peak source and 10-A peak sink currents

- Short propagation delay: 90 ns (typ), 130 ns (max)

- 4-A active Miller clamp

- · Output short-circuit clamp

- · Soft turn off (STO) during short circuit

- · Fault alarm upon desaturation detection is signaled on FLT and reset through RST

- Input and output undervoltage lockout (UVLO) with Ready (RDY) pin indication

- Active output pulldown and default low outputs with low supply or floating inputs

- 2.25-V to 5.5-V input supply voltage

System Overview www.tij.co.jp

- 15-V to 30-V output driver supply voltage

- CMOS compatible inputs

- Rejects input pulses and noise transients shorter than 40 ns

- Operating temperature: -40°C to +150°C ambient

- Isolation surge withstand voltage of 12800-V<sub>PK</sub>

図 2-2. UCC21710 Functional Block Diagram

#### 2.2.2 UCC5320

The UCC53x0 is a family of compact, single-channel, isolated IGBT, SiC, and MOSFET gate drivers with best-inclass isolation ratings and variants for pinout configuration, and drive strength.

The UCC53x0 is available in an 8-pin SOIC (DWV) package. This package has a creepage and clearance of 8.5 mm and can support isolation voltage up to 5 kV<sub>RMS</sub>, which is good for applications where reinforced isolation is needed. With these various options and wide power range, the UCC53x0 family is a good fit for motor drives and industrial power supplies.

- 3-V to 15-V input supply voltage

- 13.2-V to 33-V output driver supply voltage

- · Feature options:

- Split outputs (UCC5320S and UCC5390S)

- UVLO with respect to MOSFET collector (UCC5320E and UCC5390E)

- Miller clamp option (UCC5310M and UCC5350M)

- · Negative 5-V handling capability on input pins

- 60-ns (typical) propagation delay for UCC5320S, UCC5320E, and UCC5310M

- 100-kV/µs minimum CMTI

- Isolation surge withstand voltage: 4242 V<sub>PK</sub>

- · Safety-related certifications:

- 4242-V<sub>PK</sub> isolation per DIN V VDE V 0884-10 and DIN EN 61010-1 (planned)

- 3000-V<sub>RMS</sub> isolation for 1 minute per UL 1577 (planned)

- CSA Component Acceptance Notice 5A, IEC 60950-1 and IEC 61010-1 End Equipment Standards (Planned)

- CQC Certification per GB4943.1-2011 (Planned)

- 4-kV ESD on all pins

- CMOS inputs

- 8-pin narrow body SOIC package

- Operating temperature: –40°C to +125°C ambient

図 2-3. UCC5320 Functional Block Diagram (S Version)

#### 2.2.3 TMS320F28379D

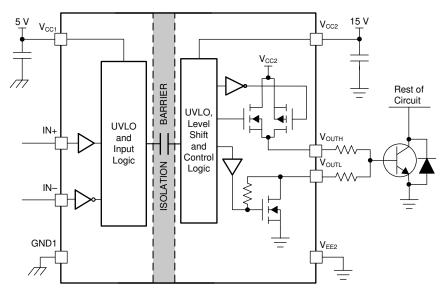

The Delfino™ TMS320F2837xD is a powerful 32-bit floating-point microcontroller unit (MCU) designed for advanced closed-loop control applications such as industrial drives and servo motor control; solar inverters and converters; digital power; transportation; and power line communications. Complete development packages for digital power and industrial drives are available as part of the powerSUITE and DesignDRIVE initiatives. While the Delfino product line is not new to the TMS320C2000™ portfolio, the F2837xD supports a new dual-core C28x architecture that significantly boosts system performance. The integrated analog and control peripherals also let designers consolidate control architectures and eliminate multiprocessor use in high-end systems.

- · Dual-core architecture:

- Two TMS320C28x 32-bit CPUs

- 200 MHz

- IEEE 754 single-precision floating-point unit (FPU)

- Trigonometric math unit (TMU)

- Viterbi/complex math unit (VCU-II)

- Two programmable control law accelerators (CLAs)

- 200 MHz

- IEEE 754 single-precision floating-point instructions

STRUMENTS System Overview www.tij.co.jp

- Executes code independently of main CPU

- On-chip memory

- 512KB (256 kW) or 1MB (512 kW) of Flash (ECC-protected)

- 172KB (86 kW) or 204KB (102 kW) of RAM (ECC-protected or parity-protected)

- Dual-zone security supporting third-party development

- Clock and system control:

- Two internal zero-pin 10-MHz oscillators

- On-chip crystal oscillator

- Windowed watchdog timer module

- Missing clock detection circuitry

- 1.2-V core, 3.3-V I/O design

- System peripherals:

- Two external memory interfaces (EMIFs) with ASRAM and SDRAM support

- Dual six-channel direct memory access (DMA) controllers

- Up to 169 individually programmable, multiplexed general-purpose input/output (GPIO) pins with input filtering

- Expanded peripheral interrupt controller (ePIE)

- Multiple low-power mode (LPM) support with external wakeup

- Communications peripherals:

- USB 2.0 (MAC + PHY)

- Support for 12-pin 3.3-V compatible universal parallel port (uPP) interface

- Two controller area network (CAN) modules (pin-bootable)

- Three high-speed (up to 50-MHz) SPI ports (pin-bootable)

- Two multichannel buffered serial ports (McBSPs)

- Four serial communications interfaces (SCI/UART) (pin-bootable)

- Two I<sup>2</sup>C interfaces (pin-bootable)

- Analog subsystem:

- Up to four analog-to-digital converters (ADCs):

- 16-bit mode

- 1.1 MSPS each (up to 4.4-MSPS system throughput)

- Differential inputs

- Up to 12 external channels

- 12-bit mode

- 3.5 MSPS each (up to 14-MSPS system throughput)

- Single-ended inputs

- Up to 24 external channels

- Single sample-and-hold (S/H) on each ADC

- Hardware-integrated post-processing of ADC conversions:

- Saturating offset calibration

- Error from setpoint calculation

- High, low, and zero-crossing compare, with interrupt capability

- Trigger-to-sample delay capture

- Eight windowed comparators with 12-bit digital-to-analog converter (DAC) references

- Three 12-bit buffered DAC outputs

- Enhanced control peripherals:

- 24 pulse width modulator (PWM) channels with enhanced features

- 16 high-resolution pulse width modulator (HRPWM) channels:

- High resolution on both A and B channels of eight PWM modules

- Dead-band support (on both standard and high resolution)

- Six enhanced capture (eCAP) modules

- Three enhanced quadrature encoder pulse (eQEP) modules

- Eight sigma-delta filter module (SDFM) input channels, two parallel filters per channel:

- Standard SDFM data filtering

- Comparator filter for fast action for out of range

図 2-4. TMS320F28379D Functional Block Diagram

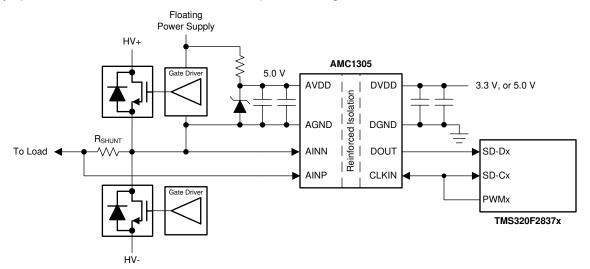

#### 2.2.4 AMC1305M05

The AMC1305 device is a precision, delta-sigma ( $\Delta\Sigma$ ) modulator with the output separated from the input circuitry by a capacitive double isolation barrier that is highly resistant to magnetic interference. This barrier is certified to provide reinforced isolation of up to 7000 V<sub>PEAK</sub> according to the DIN V VDE V 0884-10, UL1577, and CSA standards. Used in conjunction with isolated power supplies, the device prevents noise currents on a high common-mode voltage line from entering the local system ground and interfering with or damaging low voltage circuitry.

- Pin-compatible family optimized for shunt-resistor-based current measurements:

- ±50-mV or ±250-mV input voltage ranges

- CMOS or LVDS digital interface options

- Excellent DC performance supporting high-precision sensing on system level:

- Offset error: ±50 μV or ±150 μV (max)

- Offset drift: 1.3 µV/°C (max)

- Gain error: ±0.3% (max)

- Gain drift: ±40 ppm/°C (max)

- Safety-related certifications:

- 7000-V<sub>PK</sub> reinforced isolation per DIN V VDE V 0884-10 (VDE V 0884-10): 2006-12

- 5000-V<sub>RMS</sub> isolation for 1 minute per UL1577

- CAN/CSA No. 5A-Component Acceptance Service Notice, IEC 60950-1, and IEC 60065 End Equipment Standards

- Transient immunity: 15 kV/µs (min)

- High electromagnetic field immunity (see ISO72x Digital Isolator Magnetic-Field Immunity)

- External 5-MHz to 20-MHz clock input for easier system-level synchronization

Fully specified over the extended industrial temperature range

図 2-5. AMC1305M05 Simplified Schematic

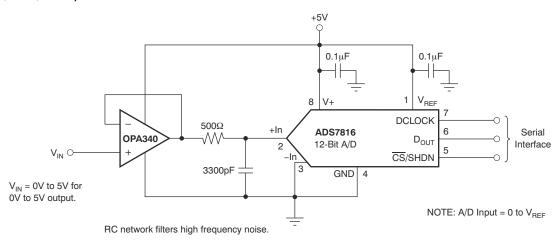

#### 2.2.5 OPA4340

The OPA4340 series rail-to-rail CMOS operational amplifiers are optimized for low-voltage, single-supply operation. Rail-to-rail input and output and high-speed operation make them ideal for driving sampling ADCs. These op amps are also well-suited for general purpose and audio applications as well as providing I/V conversion at the output of DACs. Single, dual, and quad versions have identical specifications for design flexibility.

- Rail-to-rail input

- Rail-to-rail output (within 1 mV)

- · MicroSize packages

- · Wide bandwidth: 5.5 MHz

- High slew rate: 6 V/µs

- Low THD + noise: 0.0007% (f = 1 kHz)

Low guiescent current: 750 µA/channel

- · Single, dual, and quad versions

図 2-6. OPA4340 in Non-Inverting Configuration

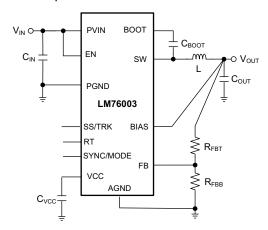

#### 2.2.6 LM76003

The LM76002/LM76003 regulator is an easy-to-use synchronous step-down DC/DC converter capable of driving up to 2.5 A (LM76002) or 3.5 A (LM76003) of load current from an input up to 60 V. The LM76002/LM76003 provides exceptional efficiency and output accuracy in a very small solution size. Peak current-mode control is employed. Additional features such as adjustable switching frequency, synchronization, FPWM option, power-good flag, precision enable, adjustable soft start, and tracking provide both flexible and easy-to-use solutions for a wide range of applications. Automatic frequency foldback at light load and optional external bias improve efficiency. This device requires few external components and has a pinout designed for simple PCB layout with best-in-class EMI (CISPR22) and thermal performance. Protection features include thermal shutdown, input UVLO, cycle-by-cycle current limit, and short-circuit protection. The LM76002/LM76003 device is available in the WQFN 30-pin leadless package with wettable flanks.

- Integrated synchronous rectification

- Input voltage: 3.5 V to 60 V (65 V maximum)

- · Output current:

- LM76002: 2.5 A

- LM76003: 3.5 A

- Output voltage: 1 V to 95% V<sub>IN</sub>

- 15-µA quiescent current in regulation

- · Wide voltage conversion range:

- t<sub>ON-MIN</sub> = 65 ns (typical)

- t<sub>OFF-MIN</sub> = 95 ns (typical)

- · System-level features:

- Synchronization to external clock

System Overview www.tij.co.jp

- Power-good flag

- Precision enable

- Adjustable soft start (6.3 ms default)

- Voltage tracking capability

- Pin-selectable FPWM operation

- High-efficiency at light-load architecture (PFM)

- Protection features:

- Cycle-by-cycle current limit

- Short-circuit protection with hiccup mode

- Overtemperature thermal shutdown protection

図 2-7. LM76003 Simplified Schematic

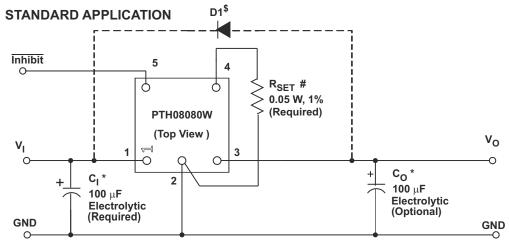

#### 2.2.7 PTH08080W

The PTH08080W is a highly integrated, low-cost switching regulator module that delivers up to 2.25 A of output current. The PTH08080W sources output current at a much higher efficiency than a TO-220 linear regulator, thereby eliminating the need for a heat sink. Its small size (0.5 × 0.6 in) and flexible operation creates value for a variety of applications.

- Up to 2.25-A output current at 85°C

- 4.5-V to 18-V input voltage range

- Wide-output voltage adjust (0.9 V to 5.5 V)

- Efficiencies Up To 93%

- On/off inhibit

- UVLO

- Output overcurrent protection (non-latching, auto-reset)

- Overtemperature protection

- Ambient temperature range: -40°C to +85°C

- Surface-mount package

- Safety agency approvals: UL/CUL 60950, EN60950

- \* See The Capacitor Application Information

- $\mbox{\# See}$  the Specification Table for the  $\mbox{R}_{\mbox{\scriptsize SET}}$  value.

- \$ Diode is Required When  $\rm V_O \geq 5.25~V$  and  $\rm V_I \geq 16~V.$

図 2-8. PTH08080W Standard Application

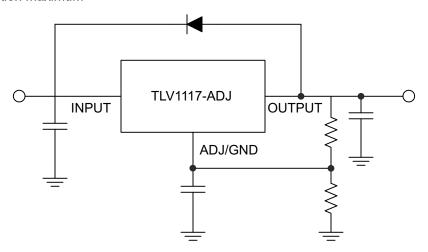

#### 2.2.8 TLV1117

The TLV1117 device is a positive low-dropout voltage regulator designed to provide up to 800 mA of output current. The device is available in 1.5-V, 1.8-V, 2.5-V, 3.3-V, 5-V, and adjustable-output voltage options. All internal circuitry is designed to operate down to 1-V input-to-output differential. Dropout voltage is specified at a maximum of 1.3 V at 800 mA, decreasing at lower load currents.

- 1.5-V, 1.8-V, 2.5-V, 3.3-V, 5-V, and adjustable-output voltage options

- Output current: 800 mA

- · Specified dropout voltage at multiple current levels

- 0.2% line regulation maximum

- 0.4% load regulation maximum

図 2-9. TLV1117 Simplified Schematic

#### 2.2.9 OPA350

The OPA350 series of rail-to-rail CMOS operational amplifiers are optimized for low voltage, single-supply operation. Rail-to-rail input and output, low noise (5 nV/ $\sqrt{\text{Hz}}$ ), and high speed operation (38 MHz, 22 V/ $\mu$ s) make the amplifiers ideal for driving sampling ADCs. They are also suited for cell phone PA control loops and video processing (75- $\Omega$  drive capability), as well as audio and general purpose applications. Single, dual, and quad versions have identical specifications for maximum design flexibility.

Rail-to-rail input

System Overview www.tij.co.jp

- Rail-to-rail output (within 10 mV)

- Wide bandwidth: 38 MHz

- High slew rate: 22 V/µs

- Low noise: 5 nV/√Hz

- Low THD+noise: 0.0006%

- Unity-gain stable

- MicroSize packages

- Single, dual, and quad

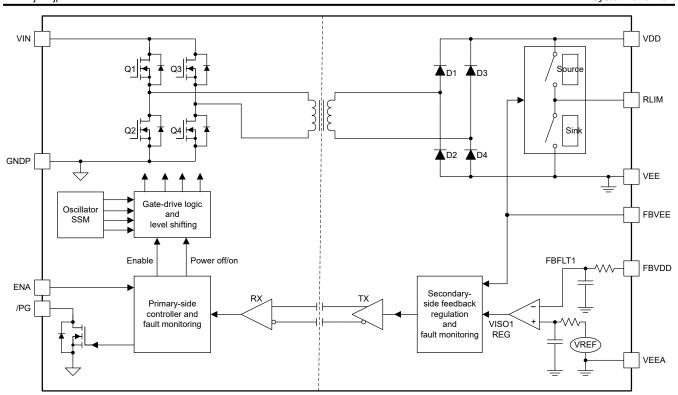

#### 2.2.10 UCC14240

The UCC14240-Q1 is a high-isolation, automotive qualified 2.0-W DC/DC module designed to provide power to SiC or IGBT gate drivers. The device integrates a transformer and DC/DC controller through proprietary architecture to achieve the smallest design size and high power density, while achieving high efficiency with very low emissions. The high-accuracy (±1.3 %), adjustable output voltages optimize gate drive voltage to provide higher system efficiency at high switching frequencies. Power-Limit and Fault Protection features maintain reliable SiC and IGBT FET operation.

- Fully integrated high-density isolated DC/DC module with isolation transformer

- Isolated DC/DC for driving: IGBTs, SiC FETs

- Input voltage range: 21 V to 27 V with 32-V absolute maximum

- 2.0-W output power at  $T_A \le 85^{\circ}$ C and > 1.5 W at  $T_A = 105^{\circ}$ C

- Adjustable (VDD VEE) output voltage (with external resistors): 18 V to 25 V, ±1.3 % regulation accuracy over full temperature range

- Adjustable (COM VEE) output voltage (with external resistors): from 2.5 V to (VDD VEE), ±1.3 % regulation accuracy over full temperature range

- Low electromagnetic emission with spread spectrum modulation and integrated transformer design

- Enable, Power Good, UVLO, OVLO, soft-start, short-circuit, power-limit, under-voltage, overvoltage, and overtemperature protection

- CMTI > 150 kV/µs

- AEC-Q100 qualified for automotive applications

- Temperature grade 1: –40°C ≤ T<sub>1</sub> ≤ 150°C

- Temperature grade 1: –40 °C ≤ T<sub>A</sub> ≤ 125°C

- Functional Safety-Capable

- Documentation available to aid functional safety system design

- Planned safety-related certifications:

- 4243-V<sub>PK</sub> basic isolation per DIN EN IEC 60747-17 (VDE 0884-17) –

- 3000-V<sub>RMS</sub> isolation for 1 minute per UL1577 -

- Basic insulation per CQC GB4943.1

- 36-pin, wide SSOP package

図 2-10. UCC14240 Typical Application

# 2.3 System Design Theory

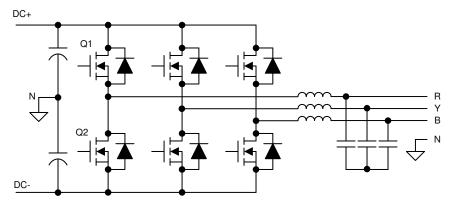

## 2.3.1 Three-Phase T-Type Inverter

#### 2.3.1.1 Architecture Overview

To understand the impetus behind a three level t-type inverter, some background on a traditional two-level inverter is required. A typical implementation of this architecture is shown in  $\boxtimes$  2-11.

図 2-11. Two-Level, Three-Phase Inverter Architecture

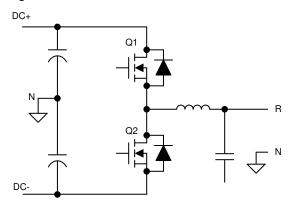

To simplify the analysis, a single leg can be isolated.

図 2-12. Two-Level, Single-Phase Inverter Leg

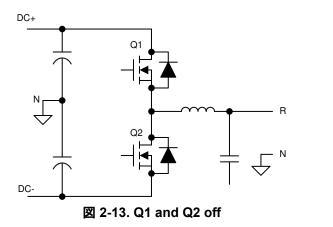

In this example, the two switching devices as a pair have four possible conduction states, independent of the other phases:

By observing the current path through the inverter, each switching device must be capable of blocking the full DC link voltage present between DC+ and DC-. In traditional low-voltage systems (< 600 V), this capability is fairly trivial with common off-the-shelf IGBTs. However, if the DC link voltage is pushed higher to increase the power throughput without increasing current, as is a common trend in power electronics, this limitation puts an upper level on the supported voltage ranges.

Additionally, the increased voltage does result in increased switching losses in the traditional IGBTs. The low dV/dt exacerbates itself in these devices, even if they are able to support the higher voltages. This dV/dt is what determines how quickly one device can transition from on to off (or vice versa), thus dictating the dead time between each of these states. An elongated switch time or dead time means the switches spend less time at full conduction, resulting in decreased efficiency.

These two primary drawbacks of a two-level inverter are what drives the implementation in this design.

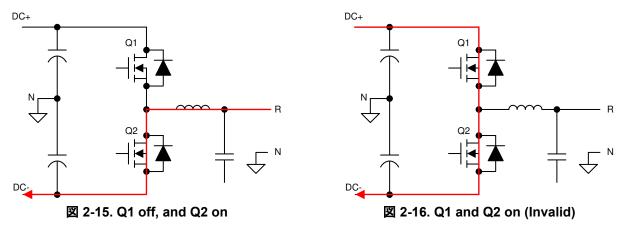

The next step up from a standard two-level inverter is a T-type three-level inverter. This type is implemented by inserting two back-to-back switching devices between the switch node and the neutral point of the DC link created by the bulk input capacitors. These two switch devices are placed in a common emitter configuration so that current flow can be controlled by switching one or the other on or off. This configuration also enables both of them to share a common bias supply as the gate-emitter voltage is identically referenced.

2-17 shows a simplified view of the implementation.

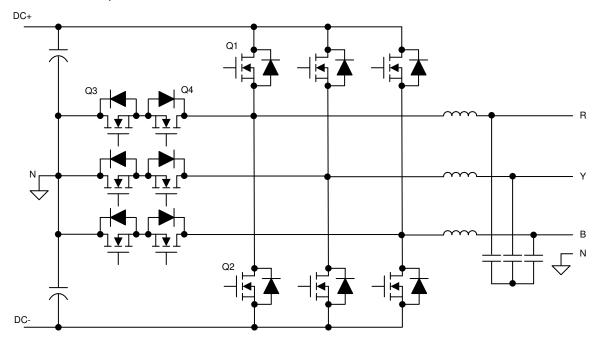

図 2-17. Three-Level T-Type, Three-Phase Inverter Architecture

RUMENTS System Overview www.tij.co.jp

To assist in understanding the benefits of the architecture, the inverter is again reduced to a single leg.

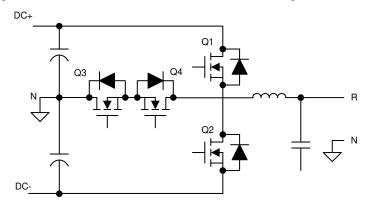

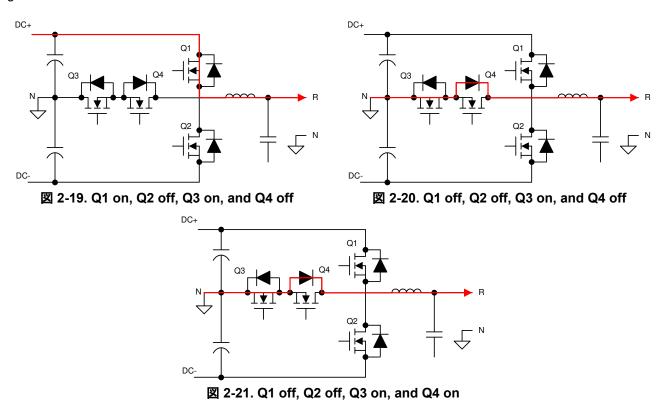

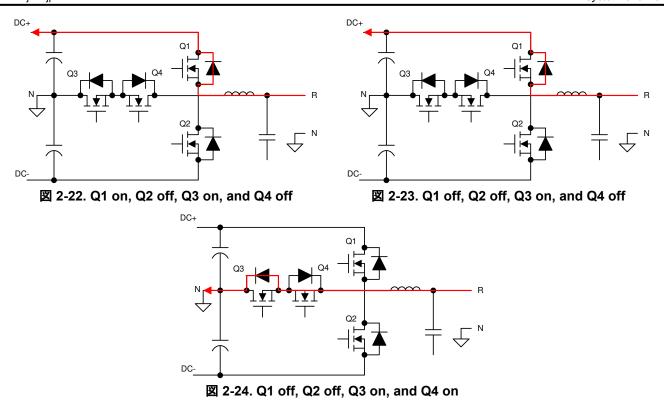

図 2-18. Three-Level T-Type, Single-Phase Inverter Leg

Adding two extra switching devices complicates the control of the system, but the same process of evaluating current flow during various modulation points illustrates the architecture benefits. Additionally, a simplified commutation scheme can be demonstrated, illustrating that control of a T-type inverter is not substantially more difficult than a traditional two-level architecture.

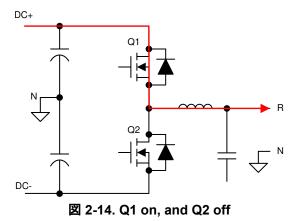

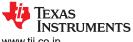

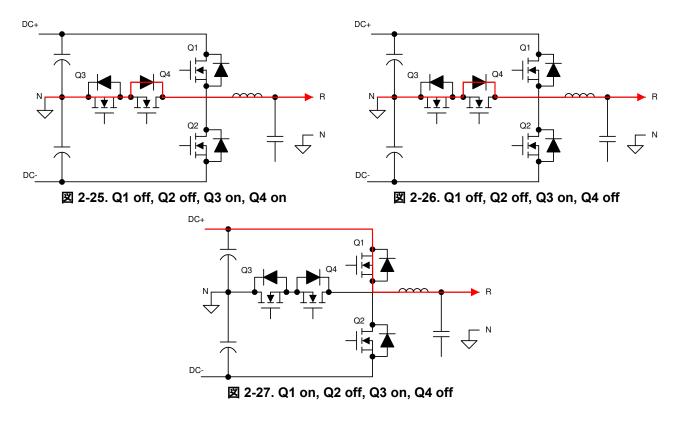

A single leg has three potential connection states: DC+, DC-, or N. This connection can be accomplished by closing Q1, closing Q3 and Q4, and closing Q2, respectively. However, this scheme depends on the current path in the system. Rather, for a DC+ connection, Q1 and Q3 can be closed, Q2 and Q4 for a neutral connection, and Q2 and Q4 for a DC- connection. This scheme acts independent of current direction as shown in the following figures.

This example starts with the output phase connected to DC+ by closing Q1 and Q3, resulting in current output from the system. To transition to an N connection, Q1 is opened and after a dead-time delay, and Q4 is closed. This setup allows current to naturally flow through Q3 and the diode of Q4.

For a negative current, the same sequence can be used. Once Q4 is closed, current then flows through it and the diode of Q3 rather than the diode of Q1.

System Overview

INSTRUMENTS

www.tij.co.jp

A similar natural current flow can be observed when connecting the output leg from N to DC+ with a positive current. Q3 and Q4 start closed with a full N connection. Q4 is switched off, but current still flows through its associated diode. Closing Q1 now naturally switches the current flow from N to DC+.

As in the earlier example when moving from a DC+ to N connection on a negative current, the same scheme can also be used here for a positive current. Q3 and Q4 begin closed, conducting current into N. Q4 is opened, causing current to flow through the diode of Q1. Lastly, Q1 is closed, and current remains flowing in the same direction.

All four of these transition states (DC+ to N, N to DC+, with both forward and reverse current) all share two simple switching schemes. This also holds true for transitions to and from DC- through Q2. By maintaining this scheme through all switching cycles, a simple dead-zone delay between switching events is all that is needed to avoid shoot-though; however, additional protection can be added in the control software with relative ease.

An additional benefit from this modulation scheme is that Q3 and Q4 never switch at the same time. This benefit reduces voltage stress on the devices as well as the power rating of the bias supply to drive these devices effectively. As mentioned earlier, Q3 and Q4 can share a single supply sized for one driver rather than two.

Q1 and Q2 still need to block the full DC link voltage as they would in the traditional architecture. To use a higher DC bus voltage, full-voltage FETs still need to be in place here; however, because they are back to back and do not switch at the same time, the two switches on the center leg can be at a lower rating.

#### 2.3.1.2 LCL Filter Design

Any system of power transfer to the grid is required to meet certain output specifications for harmonic content. In voltage sourced systems like modern photo-voltaic inverters, a high-order LCL filter typically provides sufficient harmonic attenuation, along with reducing the overall design size versus a simpler filter design. However, due to the higher order nature, take some care in its design to control resonance.

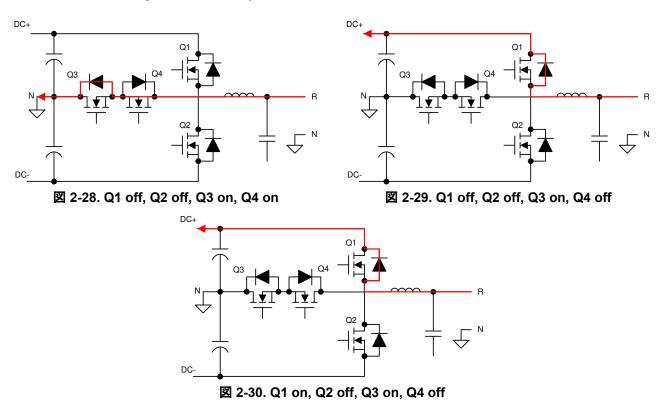

2-31 shows a typical LCL filter.

図 2-31. LCL Filter Architecture

One of the key benefits of using SiC MOSFETs (as this reference design does) is the ability to increase the switching frequency of the power stage significantly versus traditional Si-based switching elements. This increased switching frequency has a direct impact on the inverter's output filter resonant design, which needs to be accounted for. To ensure that the filter is designed correctly around this switch frequency, this known mathematical model is used in this design.

The primary component is the inverter inductor, or  $L_{inv}$ , which can be derived using  $\pm 1$ :

$$L_{inv} = \frac{V_{DC}}{8 \times f_{SW} \times I_{grid\_rated} \times \%ripple}$$

(1)

Using re-determined system specifications, one can easily calculate the primary inductor value:

$$L_{inv} = \frac{1000 \text{ V}}{8 \times 50 \text{ kHz} \times 18 \text{ A} \times 40\%} = 347 \text{ } \mu\text{H} \tag{2}$$

The sizing of the primary filter capacitor is handled in a similar fashion using  $\pm 3$ :

$$C_{f} = \frac{\%x \times Qrated}{2 \times \pi \times F_{grid} \times V_{grid}^{2}}$$

(3)

Make some design assumptions to finalize the value of  $C_f$ , namely, limiting the total reactive power absorbed by the capacitor to 5%. Scaling the total system power by the per phase power results in a primary capacitor value of:

$$I_{att} = \frac{1}{\left|1 + r \times \left(1 - L_{inv} \times C_b \times \left(2 \times \pi \times f_{SW}\right)^2 \times x\right)\right|} \times 100$$

(4)

$$C_{f} = \frac{5\% \times \frac{10 \text{ kW}}{3}}{2 \times \pi \times 50 \text{ Hz} \times \left(\frac{400}{\sqrt{3}}\right)^{2}} = 9.947 \text{ } \mu\text{F}$$

(5)

$$C_{b} = \frac{C_{f}}{x\%} = 199 \,\mu\text{F}$$

(6)

For the remainder of the filter design, determine the values by defining the attenuation factor between the allowable ripple in grid inductor and the inverter inductor. This factor needs to be minimized while still maintaining a stable and cost effective total filter. By assuming an attenuation factor, an r value, which defines the ratio between the two inductors, is determined using 34:

To obtain an attenuation factor of 10%, and using the earlier derived values, the value of r can be evaluated to be:

$$r = \left| \frac{\frac{1}{10\%} - 1}{1 - 347 \ \mu \text{H} \times 199 \ \mu \text{F} \times \left( 2 \times \pi \times 50 \ \text{kHz} \right)^2 \times 5\%} \right| = 2.7\%$$

(7)

The resultant value for  $L_{\text{grid}}$  is then:

$$L_{grid} = r \times L_{inv} = 9.34 \ \mu h \tag{8}$$

The filter design can be validated by determining its resonant frequency ( $F_{res}$ ). A good criteria for ensuring a stable  $F_{res}$  is that it is an order of magnitude above the line frequency and less than half the switching frequency. This criteria avoids issues in the upper and lower harmonic spectrums. The resonant frequency of the filter is defined using 3:

$$F_{res} = \frac{\frac{1}{\sqrt{\frac{L_{grid} \times L_{inv}}{L_{grid} + L_{inv}} \times C_{f}}}}{2 \times \pi}$$

(9)

Or, using the derived filter values:

$$F_{res} = \frac{\frac{1}{\sqrt{\frac{9.34 \ \mu H \times 347 \ \mu H}{9.34 \ \mu H + 347 \ \mu H}} \times 9.95 \ \mu F}}{2 \times \pi} = 16.733 \ kHz \tag{10}$$

This value for F<sub>res</sub> meets the criteria listed earlier and validates the filter design.

The remaining value to determine is the passive damping that must be added to avoid oscillation. Generally, a damping resistor at the same relative order of magnitude as the  $C_f$  impedance at resonance is suitable. This impedance is easily derived using  $\stackrel{>}{\underset{\sim}{\sim}}$  11:

$$R_{d} = \frac{1}{6 \times \pi \times F_{res} \times C_{f}}$$

(11)

$$R_{d} = \frac{1}{6 \times \pi \times 16.733 \text{ kHz} \times 9.95 \text{ } \mu\text{H}} = 0.316 \text{ } \Omega \tag{12}$$

For the final implementation in hardware, use real values for all of these components based on product availability and must be chosen to be appropriately close (±10% typically). When final values are determined, recalculate the resonant frequency to ensure the filter is still stable.

#### 2.3.1.3 Inductor Design

With the filter being one of the major contributors to the size and weight of a solar inverter, ensure that the individual components are correctly sized. As seen in セクション 2.3.1.2, the increase in the system switching speed provided by the SiC MOSFETs has already resulted in an inverter inductor that is of much smaller value than normal.

In  $\pm$ 1, the switching frequency is in the denominator. Any increase in switch frequency, all else being the same, results in an inverse relationship. Looking at the simplified equation for the inductance of a given inductor, there is a positive relationship between inductance and inductor cross sectional area by a number of turns. Both have a direct effect on the size of the component.

$$L = \frac{0.4 \times \pi \times \mu \times N^2 \times A \times 10^{-2}}{\ell}$$

(13)

#### where

- µ is core permeability

- · N is the number of turns

- · A is the cross sectional area

- · I is the mean magnetic path length

The starting point for evaluating a solution to the variables in  $\pm$  13 is to determine a valid core material and subsequent permeability. The core manufacturer typically has a range of suitable materials with selection criteria based on the design inductance and the inductor current. For this design, the nominal inductor current (with an overload factor of 105%) is defined as:

$$I_{ind\_nom} = \frac{KVA_{out} \times 105\%}{\sqrt{3} V_{grid}}$$

(14)

$$I_{ind\_nom} = \frac{10 \text{ kVA} \times 105\%}{\sqrt{3} \times 400} = 15.155 \text{ A}$$

(15)

Using a selection guide for a toroidal inductor core manufacturer, at 347  $\mu$ H, the core permeability comes to 26  $\mu$ H. The core also provides a value for the inductance factor, A<sub>L</sub>, which enables a quick path to selecting the number of turns.

$$N = \sqrt{\frac{L \times 10^3}{A_L}} \tag{16}$$

$$N = \sqrt{\frac{347 \ \mu H \times 10^3}{49}} = 84 \tag{17}$$

One last piece of information required for the inductor design is the winding wire size. This size is easily computed using the nominal inductor current rating. Using copper, with a current carrying density of 4 A/mm, this inductor requires a cross sectional area of:

$$A_{w} = \frac{I_{ind\_nom}}{4} = \frac{15.155}{4} = 3.789 \text{ mm}^{2}$$

(18)

This area is an equivalent to American Wire Gauge #12, which has a cross sectional area of 3.309 mm<sup>2</sup>. This slight derating is acceptable because the switching current allows a smaller gauge to be used when compared to a static DC bias current. For this inductor, flat winding is used to increase surface area for cooling and decrease potential skin depth effects.

Using the overall design of the core, with the flat 12 AWG winding, the total length of each winding is determined to be 64.87 mm. At this point, the DC resistance of the inductor can be calculated using Pouillet's Law:

$$R_{DC} = \rho \frac{\ell}{A} \tag{19}$$

$$R_{DC} = \left(17 \times 10^{-9}\right) \frac{84 \times 64.87 \text{ mm} \times 10^{-3}}{3.309 \text{ mm}^2 \times 10^{-6}} = 0.028 \Omega$$

(20)

To determine the AC resistance, first calculate the skin depth at the inverter switching frequency:

$$S_{d} = 1000 \times \sqrt{\frac{\rho}{\pi \times f_{SW} \times \mu_{o}}}$$

(21)

$$S_d = 1000 \times \sqrt{\frac{17 \times 10^{-9}}{\pi \times 50 \text{ kHz} \times 4 \times \pi \times 10^{-7}}} = 0.293 \text{ mm}$$

(22)

R<sub>AC</sub> is then determined by R<sub>DC</sub>, S<sub>d</sub>, and S<sub>s</sub>, which is the equivalent square conductor width.

$$R_{AC} = R_{DC} \times \frac{1}{2} \times \left(\frac{S_s}{S_d}\right) \times \left(\frac{\sinh\left(\frac{S_s}{S_d}\right) + \sin\left(\frac{S_s}{S_d}\right)}{\cosh\left(\frac{S_s}{S_d}\right) - \cos\left(\frac{S_s}{S_d}\right)}\right) = 0.087 \ \Omega$$

(23)

This determination of R<sub>AC</sub> helps determine total system losses.

#### 2.3.1.4 SiC MOSFETs Selection

As shown in the architecture overview, the main switching device needs to support the full switching voltage. To support the 1000-V DC link voltage of this design, use 1200-V FETs; however, at this voltage, the migration to SiC is necessitated by several factors:

- The switching speed of a 1200-V SiC MOSFET is significantly faster than a traditional IGBT, leading to a reduction in switching losses.

- The reverse recovery charge is significantly smaller in the SiC MOSFET, resulting in reduced voltage and current overshoot.

- · A lower temperature dependence at full load due to reduced conduction loss.

The middle switches are only exposed to half of the DC link voltage, or 500 V in this design. As such, a 650-V device is acceptable. A full SiC design provides the best performance due to these same features. For this design, the reverse recovery loss and voltage overshoot limits the device selection. As such, a 1200-V SiC MOSFET + 650-V MOSFET design is used.

Conduction loss is mainly determined by the  $R_{DS(on)}$  of the 1200-V SiC MOSFET and the on  $R_{DS(on)}$  of the 650-V SiC MOSFET. The 75-m $\Omega$  SiC devices have a good high-temperature performance, and the  $R_{DS(on)}$  only increases 40% at 150°C junction temperature. With the high temperature I-V curve in the data sheet, calculate the conduction loss on the devices.

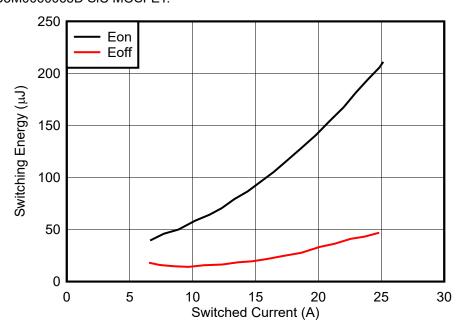

Switching loss is a function of the switching frequency and switching energy of each switching transient, the switching energy is related with device current and voltage at the switching transient. Using the switching energy curve in the data sheet, one can estimate the total switching loss.

Similarly, the conduction loss and switching loss can be estimated for all the devices and efficiency can be estimated. With the thermal impedance information of the thermal system design, the proper device rating can be selected. The 1200-V/75-m $\Omega$  SiC MOSFET and 650-V/60-m $\Omega$  SiC MOSFET is a good tradeoff among thermal, efficiency and cost.

System Overview

#### 2.3.1.5 Loss Estimations

The primary source of lost efficiency in any inverter is going to be a result of the losses incurred in the switching devices. These losses are broken into three categories for each device:

- Conduction loss: When the device is on and conducting normally

- Switching loss: When the device is switching between states

- Diode conduction loss: Related to voltage drop and current when in conduction

Each of these are dictated by their own equation, and can be determined from the device data sheet and design parameters that have already been set.

Conduction loss is driven by the on-time of the FET, the switched current, and the on-resistance:

$$P_{cond\_loss} = \frac{1}{T} \int_{0}^{T} V_{ce}(t) \times I_{c}(t) \times D_{Q}(t) dt$$

(24)

#### where

- V<sub>ce</sub> is the conduction voltage drop

- I<sub>c</sub> is the conduction current

- D<sub>O</sub> is the duty cycle

- T represents one modulation cycle

Switching loss is determined by the switching energy of the device and the switching voltage at a selected test point. Determine the value of the switching energy from the device data sheet using the value of the designed external gate resistor. The remainder of the values needed were determined earlier in the design phase.

$$P_{sw\_loss} = \frac{\left(E_{on} + E_{off}\right) \times I_{peak} \times f_{SW} \times V_{DC}}{\pi \times I_{avg} \times V_{nom}}$$

(25)

2-32 shows an example of the graph used to extract the switching energy values from the device data sheet is shown for an C3M0060065D SiC MOSFET.

図 2-32. Switching Energy vs Switched Current for C3M0060065D

The diode conduction loss is similarly calculated using known values:

$$P_{sw\_diode} = \frac{1}{T} \int_{0}^{T} Vf(t) \times If(t) \times D_{D}(t) dt$$

(26)

where

- V<sub>f</sub> is the voltage drop

- · If is the diode current

- D<sub>D</sub> is the duty cycle

- T represents one modulation cycle

Using these three equations, the expected losses of the design are computed for both the SiC MOSFETs as shown in  $\frac{1}{2}$  2-1.

| 表 | 2-1. | <b>Expected</b> | Losses | of Swi | tching | <b>Devices</b> |

|---|------|-----------------|--------|--------|--------|----------------|

|---|------|-----------------|--------|--------|--------|----------------|

| PARAMETER       | C3M0075120D (Q1) | C3M0060065D (Q3) |

|-----------------|------------------|------------------|

| Conduction loss | 5.76 W           | 4.5 W            |

| Switching loss  | 1.8 W            | 1.13 W           |

| Diode loss      | 0 W              | 0 W              |

| Total           | 7.56 W           | 5.63 W           |

The final piece of the total system loss estimation is the inductor losses. These losses are determined using the value of the inductor DC and AC resistance and expected inductor current from セクション 2.3.1.3.

$$Pind\_loss = I_{ind\_ac\_rms}^{2} \times R_{DC} + I_{ind\_ripple\_rms}^{2} \times R_{AC}$$

(27)

$$P_{\text{ind\_loss}} = (0.81 \text{ A})^2 \times 0.024 \Omega + (15.155)^2 \times 0.076 \Omega = 5.64 \text{ W}$$

(28)

The total major energy loss for this design is then:

$$P_{loss\_total} = 6 \times \left(P_{Q1\_total} + P_{Q3\_total}\right) + 3 \times P_{int\_loss}$$

(29)

$$P_{loss\_total} = 6 \times (5.631 \text{ W} + 7.56 \text{ W}) + 3 \times 5.64 \text{ W} = 96.102 \text{ W}$$

(30)

Use  $\gtrsim 30$  to determine the total expected inverter efficiency. Note that this is an estimation, but the estimate allows the design to be validated up to this point.

$$\eta = \frac{P_{out}}{P_{out} + P_{loss\_total}} \times 100$$

(31)

$$\eta = \frac{10 \text{ kW}}{10 \text{ kW} + 96.102 \text{ W}} = 99.048\% \tag{32}$$

#### 2.3.1.6 Thermal Considerations

The loss estimations can also allow the heat output of the design to be characterized. Any electrical loss in the system is converted to waste heat.

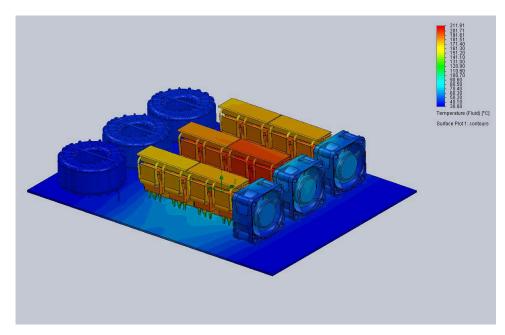

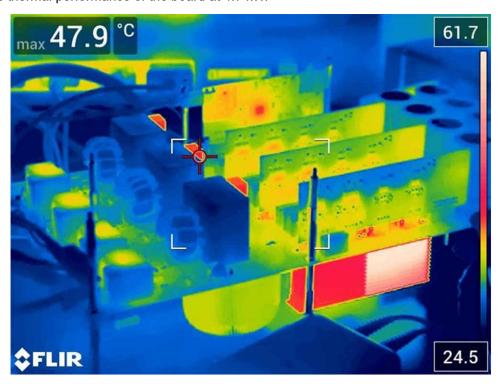

Thermal simulations where performed using the physical layout of the design, as well as the expected energy losses. An off the shelf heat sink from Wakefield-Vette (OMNI-UNI-18-50) was selected to simplify the design process and provide a starting reference point for understanding the thermal performance. Use this data as a starting point for a thermal design, and not a fully-validated design.

System Overview

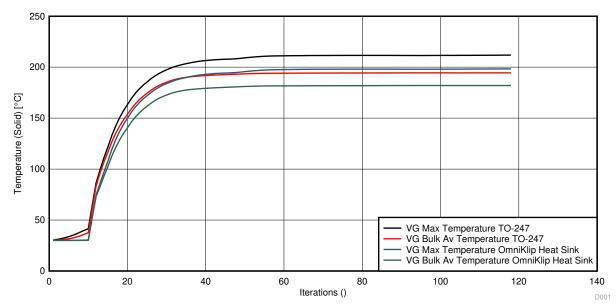

The system was simulated using a worse-than-calculated thermal output of 10 W per switching device. This meant 120 W of total power dissipation across all three phases. Z 2-33 and Z 2-34 show the thermal simulation results with no fans.

図 2-33. Simulated Temperature vs Time

図 2-34. Passive Thermal Simulation Result

In this simulation, with only natural convection and small off the shelf heat sinks, the TO-247 package of the MOSFETs reaches a maximum temperature of 215°C, and the SiC MOSFET reaches 197°C. These temperatures are both outside the maximum allowed temperature range of the devices.

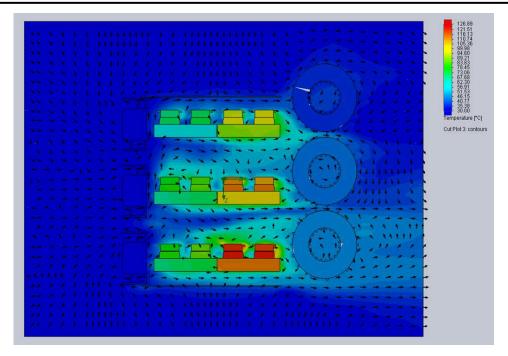

☑ 2-35 shows the next simulation, which includes active airflow and full ducting of the heat generating devices. This airflow reduces the maximum temperature of the MOSFET under a 130% load to be 130°C. This temperature is within the design constraint of the 175°C junction temperature of the C3M0060065D, which is the major heat generator. Please contact wakefield-Vette for details on the thermal simulation.

System Overview Vision Overvie

図 2-35. Active Ducted Thermal Simulation

#### 2.3.2 Voltage Sensing

Voltage sensing happens at two points in the inverter signal path to aid in control: before and after the primary output relay. By enabling measurement on both sides of the relay, the control system can lock into the grid voltage and frequency before connecting, thus preventing any mismatch issues.

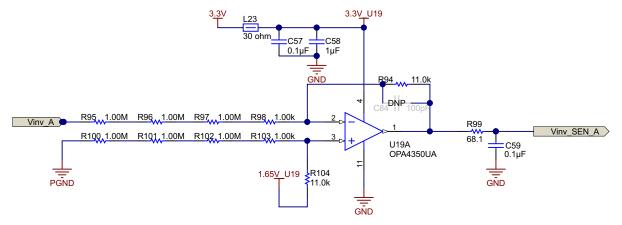

Both sensing topologies are similar. First, PGND is used as a virtual neutral using a resistor network. On the grid side of the relay, only neutral is used. The high voltage signal is attenuated using a series of large value resistances. An offset of 1.65 V is added to the attenuated neutral point to center the voltage signal in the middle of the input range of the OPA4350, and the attenuated value from the phase voltage is measured.

2-36 shows this sensing arrangement.

図 2-36. High-Voltage Sensing Signal Path

#### 2.3.3 Current Sensing

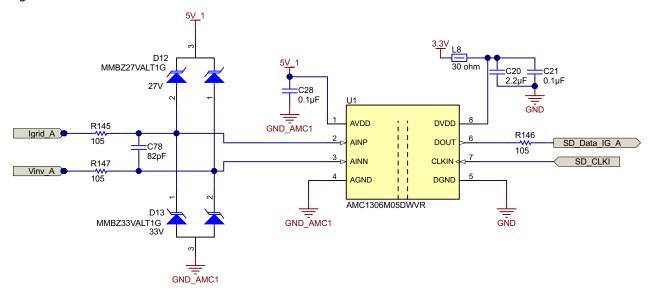

Critical to attaining a closed-loop control system is accurate current measurement of the inverter. In this design, current measurement is done at two locations with different sensing technologies. The first location is on the grid output using shunt resistors. Because the output is high voltage and the controller needs to remain isolated, the AMC1306M05 reinforced modulator is used to measure the resistor voltage drop. To keep system losses low, the AMC1306M05 has a ±50-mV input range. When compared to other devices with a typical input range of ±250 mV, the total power loss across the shunt is significantly reduced.

Sizing the shunt resistor for this design is a trade-off between sensing accuracy and power dissipation. A 0.002- $\Omega$  shunt provides a  $\pm 50$ -mV output signal at the approximate  $\pm 25$ -A output inverter but also only generates 0.5 W of heat at full load. When choosing an actual device, select a high accuracy value to eliminate the need to calibrate each sensor path.

The voltage across the shunt resistor is fed into the AMC1306M05 sigma-delta modulator, which generates the sigma-delta stream that is decoded by the SDFM demodulator present on the C2000™ MCU. The clock for the modulator is generated from the eCAP peripheral on the C2000 MCU, and the AMC1306M05 data is decided using the built-in SDFM modulator.

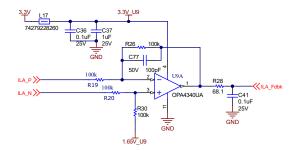

図 2-37. Isolated Shunt Sensing With AMC1305M05

The second location is a Hall-effect sensor, which is used to sense the current through the inductor. The Hall-effect sensor has a built-in offset, and the range is different than what ADC can measure. Therefore, the voltage is scaled to match the ADC range using the circuit shown in 区 2-39 and 式 33. Of note here, the OPA4340 is used over the OPA4350 in the voltage sense path due to the lower bandwidth of the former. The low bandwidth helps to reduce accidental amplification of switching noise that can be picked up by long traces in the PCB.

図 2-38. Isolated Hall Effect Current Sensing

図 2-39. Hall Effect Sensor Matching

$$V_{out} = \frac{R_f}{R_e} \left( \frac{V_{nominal}}{I_{max}} + V_{offset} \right)$$

(33)

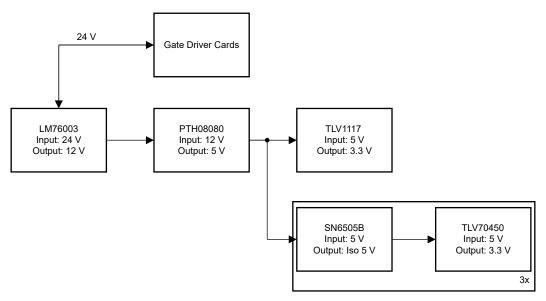

#### 2.3.4 System Power Supplies

This reference design uses multiple voltage domains across the system:

- A primary high-voltage input to power the entire board (up to 24 V)

- 24 V to power the gate drive cards, further described in セクション 2.3.5

- 5 V to power the control card and drive isolated supplies

- Non-isolated 3.3 V for analog sensing

- · Isolated 3.3 V for current shunt sensing

2-40 shows the full tree for all of these domains.

図 2-40. Power Tree

## 2.3.4.1 Main Input Power Conditioning

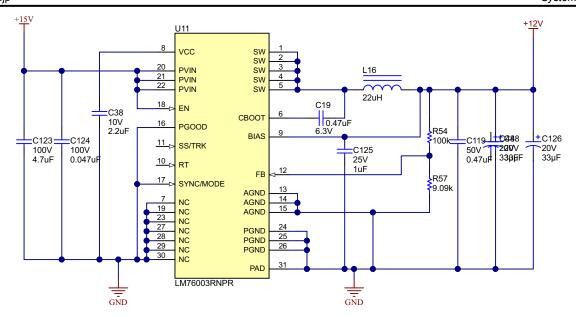

The primary voltage input for the design is rated for 15 V to 60 V. This wide  $V_{IN}$  enables the inverter to be powered from a variety of industrial voltage sources that might be used in a larger system. The range is enabled by the LM76003 synchronous step-down converter.

The converter is configured for a 12-V output using the R54 and R57 feedback resistor divider. This 12-V rail is then used to power the relays, fans, isolated gate drive bias supplies, and the remainder of the step-down converters in the system. The 3.5-A output support of the LM76003 is sufficient for this operation. The design also includes dual parallel output capacitors to reduce ESR and subsequent ripple and load transients and loads switch on an off.

図 2-41. LM76003 12-V DC/DC Converter

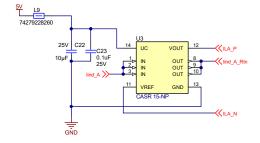

#### 2.3.4.2 Isolated Bias Supplies

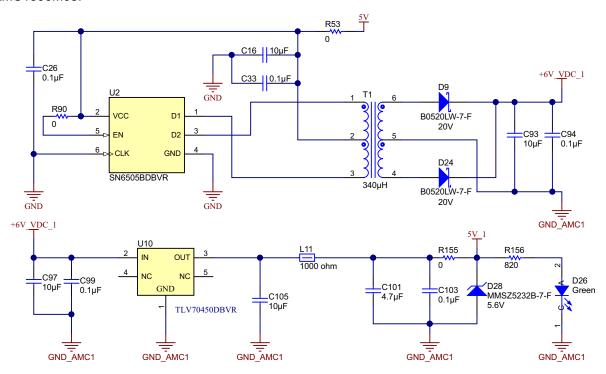

To generate the isolated bias supplies for the AMC1306M05 isolated modulators, the SN6505B transformer driver is used to drive a Würth 750313638 transformer in a push-pull configuration. This is a recommended configuration from the SN6505B data sheet to build a 5-V  $\rightarrow$  6-V isolated supply.

The 6-V output is used to feed a TLV70450 LDO to generate a clean 5-V rail for the analog and digital circuitry of the AMC1306M05.

図 2-42. SN6505 Bias Voltage Supply

System Overview www.tij.co.jp

#### 2.3.5 Gate Drivers

#### 2.3.5.1 1200-V SiC MOSFETs

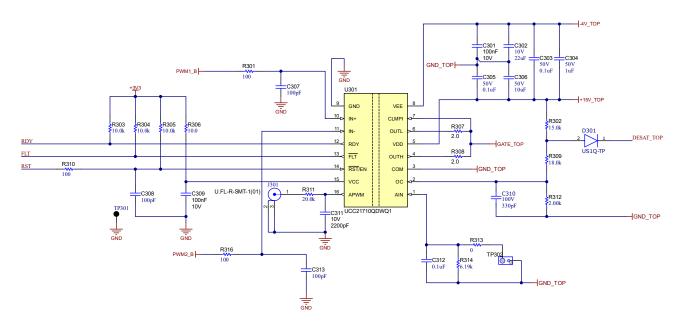

for the input side of the UCC21710 device. The supply voltage at VCC can range from 3.0 V to 5.5 V with respect to GND. VDD and COM are the supply pins for the output side of the UCC21710 device. VEE is the supply return for the output driver and COM is the reference for the logic circuitry. The supply voltage at VDD can range from 15 V up to 30 V with respect to VEE. The PWM is applied across the IN+ and IN- pins of the gate driver.

On the secondary-side of the gate driver, gate resistors R308 and R307 control the gate current of the switching device. The DESAT fault detection prevents any destruction resulting from excessive collector currents during a short-circuit fault. To prevent damage to the switching device, the UCC21710 slowly turns off the SiC MOSFET in the event of a fault detection. A slow turnoff makes sure the overcurrent is reduced in a controlled manner during the fault condition. The DESAT diode D301 conducts the bias current from the gate driver, which allows sensing of the MOSFET-saturated collector-to-emitter voltage when the SiC MOSFET is in the ON condition.

図 2-43. UCC21710 Gate Drive Circuit

#### 2.3.5.2 650-V SiC MOSFETs

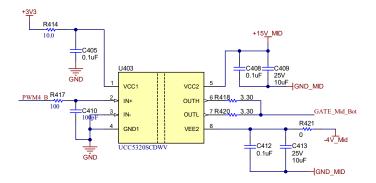

powered by a 3.3-V rail. A 0.1-µF ceramic capacitor is placed close to the VCC1 pin for noise decoupling. The positive going UVLO threshold on the supply is 2.6 V and the negative going threshold is 2.5 V.

The PWM input to the gate driver is provided by the controller PWM output peripheral. Dead time must be inserted between the low-side and high-side PWM signals to prevent both switches turning on at the same time. The signal is single ended and is filtered by RC low-pass filter comprising of R417 and C410 before connecting to the gate driver input. The filter attenuates high-frequency noise and prevents overshoot and undershoot on the PWM inputs due to longer tracks from the controller to the gate driver. The inverting PWM input IN- is not used in the design and is connected to primary side ground.

The UCC5320S has split outputs that allow for controlling the turn-on rise time and turn-off fall time of the MOSFETs individually. A 3.3-Ω gate resistor R418 is used for MOSFETs turn-on. A 3.3-Ω MOSFET turn-off resistor R420 allows for strong turn-off, helping reduce turn-off losses. The low value of the turn-off resistor also increases the immunity of the gate drive circuit to Miller induced parasitic turn-on effects. A 10-kΩ resistor is connected across the MOSFET gate to collector pins close to the MOSFET on the main power board. This connection ensures that the MOSFET remains in the off state in case the gate driver gets disconnected from the MOSFET due to faults.

図 2-44. UCC5320 Gate Drive Circuit

#### 2.3.5.3 Gate Driver Bias Supply

セクション 2.3.5.1 and セクション 2.3.5.2 show that the gate drivers rely on isolated bias voltages to drive the gates across the high-voltage barrier. In this architecture, there are four drivers per phase, but only three isolated domains are needed as described in セクション 2.3.1.1. These domains are:

- 1. +15 V and -4 V for high SiC MOSFET switch

- 2. +15 V and -4 V for low SiC MOSFET switch

- 3. +15 V and -4 V for both SiC MOSFETs in the neutral leg

The same architecture used in 29222.3.4.2 can generate the domains individually. However, to increase the power density of the design, the UCC1424 with integrated power supply was used. By using the following IC, this architecture decreases system complexity, cost, and size.

#### 2.3.6 Control Design

Terminology:

$V_{bus}$  or  $V_{dc}$  bus voltage for the inverter

$\begin{array}{ll} \textbf{L}_i \ \ \text{and} \ \ \textbf{R}_i & \text{inductance of the inverter side inductor and series resistance} \\ \textbf{L}_g \ \ \text{and} \ \ \textbf{R}_g & \text{inductance of the grid side inductor, and series resistance} \\ \textbf{C}_f \ \ \text{and} \ \ \textbf{R}_f & \text{capacitance value and series resistor plus any damping resistor} \end{array}$

v<sub>i\_a</sub>,v<sub>i\_b</sub>,v<sub>i\_c</sub> output voltage from the three phase bridge, this voltage is what is controlled using the duty cycle control of the three phase bridge

Therefore, for control purposes it is assumed now only the modulation needs to change between 2-level and 3-level inverter for the power stage and control design can remain the same. Where  $_{,}D_{a}$ ,  $_{,}D_{b}$ ,  $_{,}D_{c}$ , are the control variable generated such that the output voltage of the inverter can be represented as  $_{,}^{+}$ 34:

$$v_{i_a} = D_a \times \frac{V_{DC}}{2}$$

(34)

i<sub>i a</sub>, i<sub>i b</sub>, i<sub>i c</sub> current through the inverter side inductor

$\boldsymbol{v}_{\boldsymbol{x}\_\boldsymbol{a}}, \boldsymbol{v}_{\boldsymbol{x}\_\boldsymbol{b}}, \boldsymbol{v}_{\boldsymbol{x}\_\boldsymbol{c}}$  voltage across the filter capacitor

$i_{g\_a}$ ,  $i_{g\_b}$ ,  $i_{g\_c}$  voltage across the filter capacitor

v<sub>q</sub> a, v<sub>q</sub> b, v<sub>q</sub> c grid frequency

#### 2.3.6.1 Current Loop Design

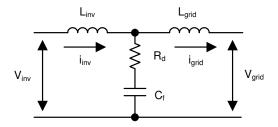

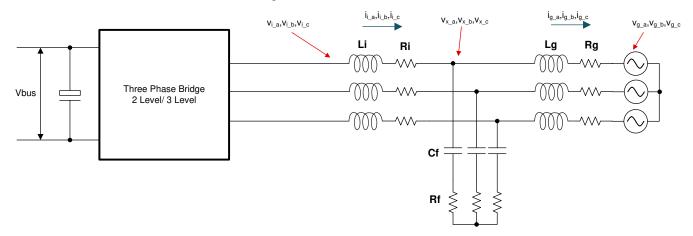

For the inverter filter shown in 図 2-45, using KCL and KVL 式 35 can be written.

図 2-45. Inverter Model

$$v_{i_a} - L_i \frac{di_{i_a}}{dt} - R_i i_{i_a} = v_{x_a}$$

(35)

Upon re-arranging, 式 35 can be written as 式 36:

$$\frac{di_{\underline{i}_{\underline{a}}}}{dt} = \frac{1}{L_{i}} V_{\underline{i}_{\underline{a}}} - \frac{1}{L_{i}} (R_{i} i_{\underline{i}_{\underline{a}}} + V_{\underline{x}_{\underline{a}}})$$

(36)

Similarly on another node, using KCL and KVL, 式 37 can be written as 式 37:

www.tij.co.jp

$$\frac{di_{g_a}}{dt} = \frac{1}{L_2} v_{x_a} - \frac{1}{L_2} \left( R_2 i_{g_a} + v_{g_a} \right)$$

(37)

Assuming  $R_f$  is negligible  $\stackrel{>}{

ightarrow}$  38 can be written for the capacitor voltage:

$$\frac{dV_{x_a}}{dt} = \frac{1}{C_f} \left( i_{i_a} - i_{g_a} \right) \tag{38}$$

Typically a synchronous reference frame control is designed, where a  $d_q$  rotating reference frame at grid frequency speed, and oriented such that the d axis is aligned to the grid voltage vector is used. Using basic trigonometric identities,  $i_d$  and  $i_q$  can be written as  $\not\equiv$  39 and  $\not\equiv$  40.

$$i_{d} = \frac{2}{3} \left( i_{a} \cos \omega t + i_{b} \cos \left( \omega t - 120 \right) + i_{c} \cos \left( \omega t + 120 \right) \right) \tag{39}$$

$$i_{q} = -\frac{2}{3} (i_{a} \sin \omega t + i_{b} \sin (\omega t - 120) + i_{c} \sin (\omega t + 120))$$

(40)

Taking the derivative, and using the partial derivative theorem, 式 41 is written:

The following state equations can be written:

$$\frac{di_{i\_d}}{dt} = \frac{1}{L_i} v_{i\_d} + \omega i_{i\_q} - \frac{1}{L_i} (R_i i_{i\_d} + v_{x\_d})$$

(42)

$$\frac{di_{\underline{i}_{q}}}{dt} = \frac{1}{L_{i}} v_{\underline{i}_{q}} - \omega i_{\underline{i}_{d}} - \frac{1}{L_{i}} (R_{i} i_{\underline{i}_{q}} + v_{\underline{x}_{q}})$$

(43)

Hence, using these equations, and substituting in 式 44:

$$(sL_{i})i_{i\_d}(s) = v_{i\_d}(s) + (\omega L_{i})i_{i\_q}(s) - (R_{i}i_{i\_d}(s) + v_{x\_d}(s))$$

(44)

Taking the Laplace function on the previous equations:

$$(sL_{i})i_{i_{q}}(s) = v_{i_{q}}(s) - (\omega L_{i})i_{i_{q}}(s) - (R_{i}i_{q}(s) + v_{x_{q}}(s))$$

(45)

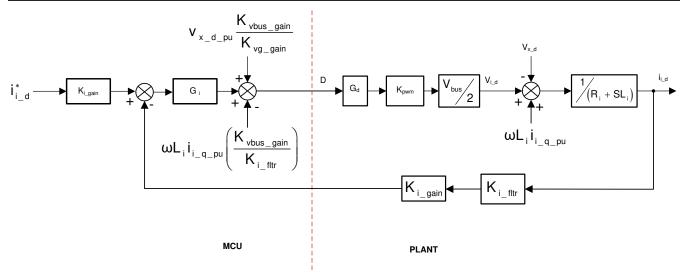

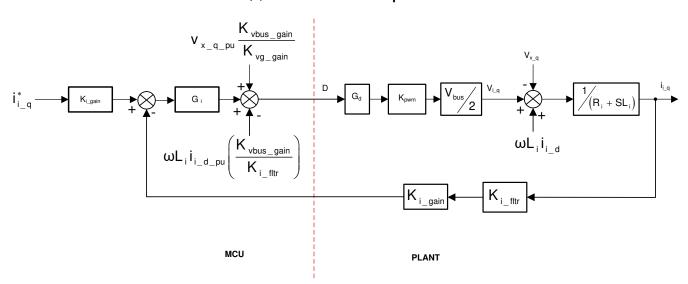

When written in control diagram format, this looks like the following. Feedforward elements are added to remove additional sources of disturbances and errors in the model, two feedforward elements are added,

- 1. For the coupling term from the other axis in synchronous frame

- 2. For the output grid voltage

The diagram is drawn as shown in ≥ 2-46.

System Overview

#### where:

- i\*i d is the current reference

- K<sub>i\_gain</sub> is the current sense scalar which is one over max current sense

- K<sub>i</sub> fltr is the filter that is connected on the current sense path. current sense scalar which is one over max

- K<sub>vbus gain</sub> is the voltage sense scalar for the bus, which is one over max voltage sensed

- $K_{vq}$  gain is the voltage sense scalar for the grid voltage, which is one over max voltage sensed

# 図 2-46. Id Current Loop Model

図 2-47. Iq Current Loop Model

With the feedforward elements, the small signal model can be written as 式 46(Note: Separate scaling factors are applied to bus voltage and grid voltage due to the differences in the sensing range.):

$$\frac{\hat{i}_{i\_d\_pu}}{\hat{d}} = G_d K_{pwm} \frac{1}{K_{vbus\_gain}} K_{i\_gain} K_{i\_fltr} \frac{1}{(R_i + sL_i)}$$

(46)

In the case of an LCL filter, the following can be assumed as a simplified model as in  $\pm$  47:

$$\frac{\hat{\mathbf{i}}_{\underline{\mathsf{d}}_{\mathsf{pwm}}}}{\hat{\mathbf{d}}} = \mathbf{G}_{\mathsf{d}} \, \mathbf{K}_{\mathsf{pwm}} \, \frac{1}{\mathbf{K}_{\mathsf{vbus}_{\mathsf{gain}}}} \, \mathbf{K}_{\underline{\mathsf{i}}_{\mathsf{gain}}} \, \mathbf{K}_{\underline{\mathsf{i}}_{\mathsf{fltr}}} \frac{1}{\left(Z_{\mathsf{i}} + Z_{\mathsf{c}} Z_{\mathsf{f}} / (Z_{\mathsf{c}} + Z_{\mathsf{f}})\right)} \tag{47}$$

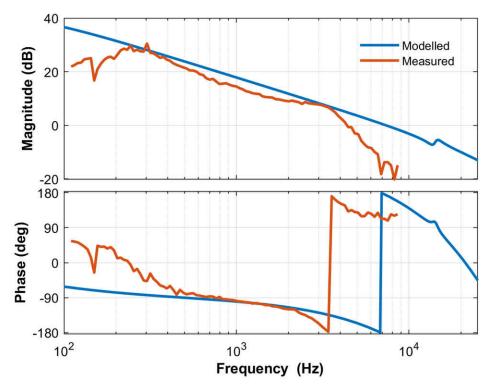

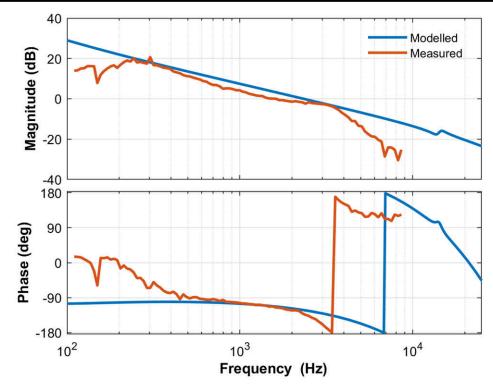

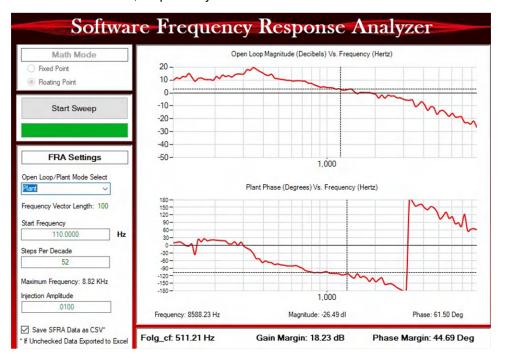

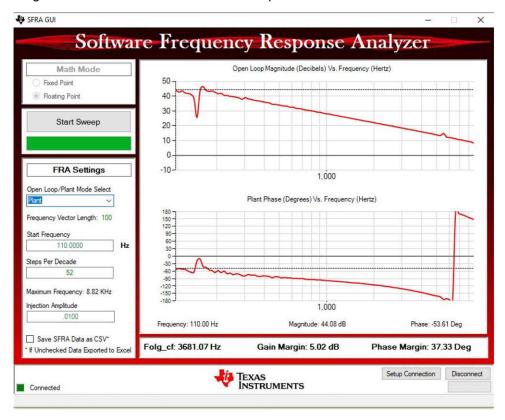

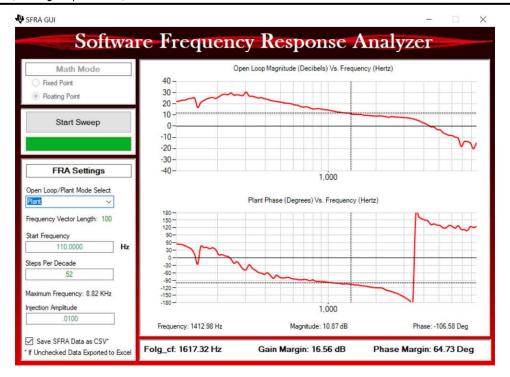

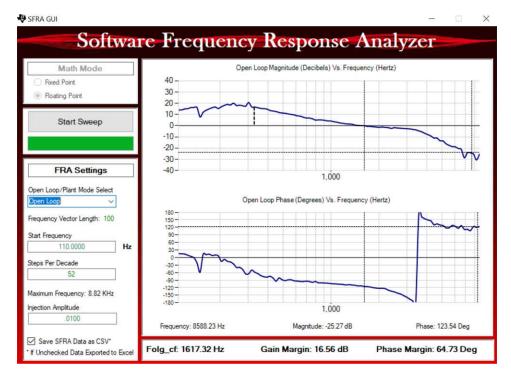

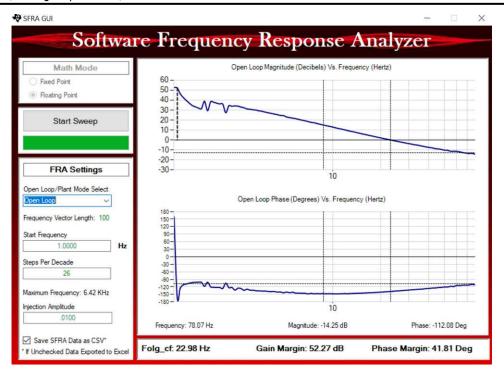

The current loop plant is compared with the SFRA measured data for the current loop as illustrated in ⊠ 2-48.

図 2-48. Current Loop Plant Frequency Response Modelled vs Measured

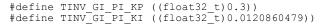

式 48 represents the compensator designed for the closed-loop operation:

$$G_{i} = 0.3 \times \frac{\left(s + 2\pi \times 95.6\right)}{s} \tag{48}$$

With which the open loop plot in  $\boxtimes$  2-49 is achieved, gives roughly > 1-kHz bandwidth in the  $I_d$  and  $I_g$  loop.

図 2-49. Current Loop, Open Loop Response Modelled vs Measured

#### 2.3.6.2 PFC DC Bus Voltage Regulation Loop Design

Before looking at the voltage loop model, the power measurement from DQ domain can be written as:

$$P = v_{a}i_{a} + v_{b}i_{b} + v_{c}i_{c} = \begin{bmatrix} v_{a} & v_{b} & v_{c} \end{bmatrix} \begin{bmatrix} i_{a} \\ i_{b} \\ i_{c} \end{bmatrix} = \begin{pmatrix} T_{abc->dq0} & T_{dq0} & T_{dq0} & T_{dq0} & T_{dq0} \\ T_{dq0->abc} & T_{dq0} & T_{abc->dq0} & T_{abc->dq0} & T_{abc->dq0} & T_{dq0} \\ T_{abc->dq0} & T_{abc->dq$$

$$T_{abc\rightarrow dq0} = \frac{2}{3} \begin{bmatrix} \cos(\omega t) & \cos(\omega t - \frac{2\pi}{3}) & \cos(\omega t + \frac{2\pi}{3}) \\ -\sin(\omega t) & -\sin(\omega t - \frac{2\pi}{3}) & -\sin(\omega t + \frac{2\pi}{3}) \\ \frac{1}{2} & \frac{1}{2} & \frac{1}{2} \end{bmatrix}$$

where

Hence:

$$P = \frac{3}{2} \left( v_{gd} i_d + v_{gq} i_q \right) \tag{50}$$

$$Q = -v_{gd}i_d + v_{gq}i_q$$

(51)

The DC Bus regulation loop is assumed to be providing the power reference, which is divided by the square of the line voltages RMS to provide the conductance. When further multiplied by the line voltage gives the instantaneous current.

www.tij.co.jp System Overview

図 2-50. Voltage Loop Model

A small-signal model of the DC bus regulation loop is developed by linearizing 式 52 around the operating point:

$$i_{\text{DC}}v_{\text{bus}} = 3\eta v_{\text{g\_rms}}i_{\text{g\_rms}} \Rightarrow \hat{i}_{\text{DC}} = 3\eta \frac{\overline{V}_{\text{g\_rms}}}{\overline{V}_{\text{bus}}}\hat{i}_{\text{g\_rms}}$$

$$(52)$$

Because transformation is an amplitude invariant, translating from RMS to peak quantities using

$$\hat{\mathbf{i}}_{g_{\text{rms}}} = \frac{1}{\sqrt{2}} \hat{\mathbf{i}}_{gd}$$

and  $\hat{\mathbf{v}}_{g_{\text{rms}}} = \frac{1}{\sqrt{2}} \hat{\mathbf{v}}_{gd}$ ,  $\pm 53$  can be derived.

$$\hat{\mathbf{i}}_{DC} = \frac{3}{2} \frac{\overline{V}_{gd}}{\overline{V}_{bus}} \hat{\mathbf{i}}_{gd} \tag{53}$$

Also for resistive load on the DC Bus:  $\hat{v}_{\text{bus}} = \frac{Z_{\text{c}} R_{\text{L}}}{Z_{\text{c}} + R_{\text{L}}} \; \hat{i}_{\text{DC}}$

Therefore, the voltage loop plant can be written as 式 54

$$G_{v\_bus} = \frac{Z_c R_L}{Z_c + R_L} \times p \times \frac{K_{vbus_{fltr}} \times K_{vbus_{gain}}}{K_{i_{gain}}} \times \frac{1}{\left(V_{bus} \times K_{vg_{gain}}\right)} \times \frac{3}{2} \times \left(\frac{V_{g\_peak}}{V_{g\_Sense\_max}}\right) \tag{54}$$

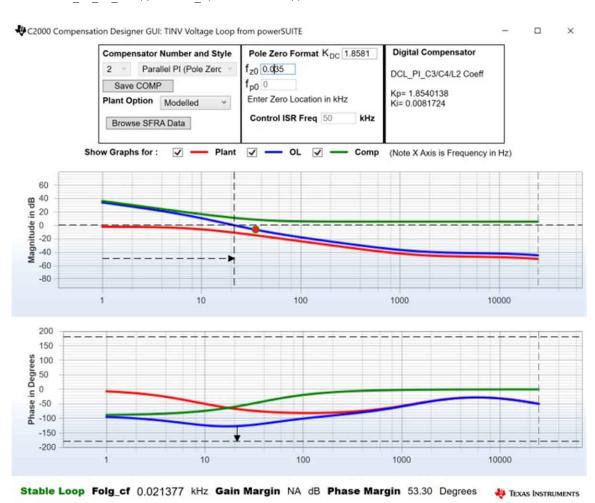

Using the previous model the following compensator, 式 55 is designed for the voltage loop:

$$G_{v} = 1.8581 \times \frac{\left(s + 2\pi \times 35\right)}{s} \tag{55}$$

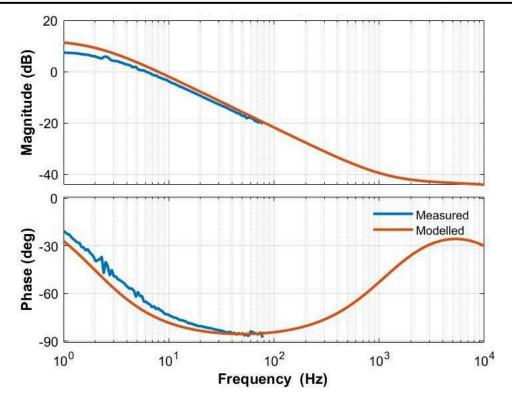

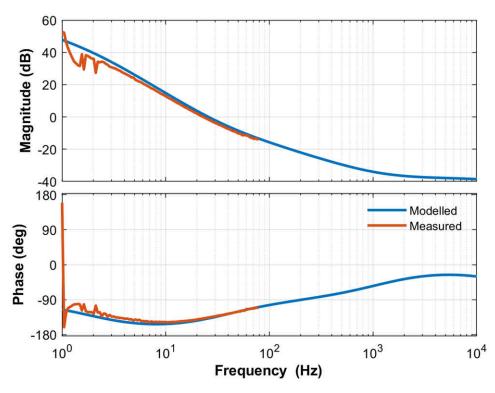

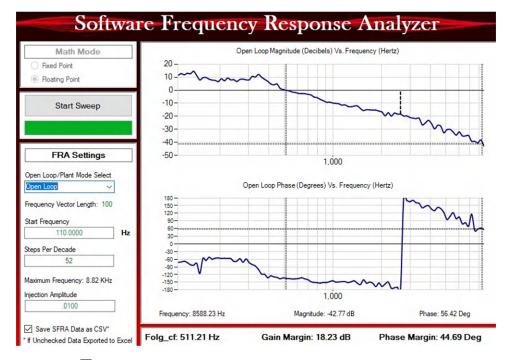

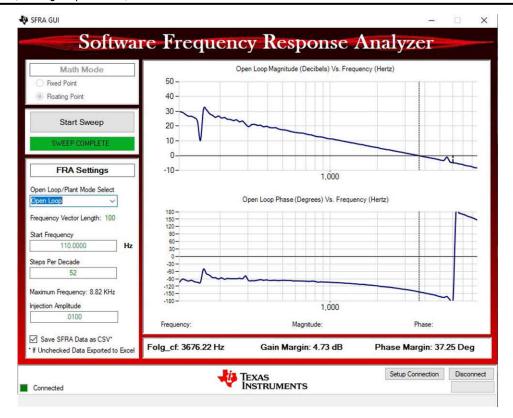

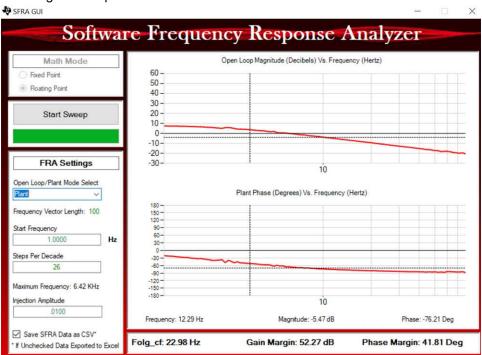

SFRA is used to measure the voltage loop bandwidth, and compare against the model which shows good correlation to the model.

2-51 shows the plant frequency response comparison and

2-52 shows the open-loop frequency response comparison of modelled versus measured.

図 2-51. Voltage Loop Plant Frequency Response Measured vs Modelled

図 2-52. Voltage Loop, Open-Loop Frequency Response Modelled vs Measured

# 3 Hardware, Software, Testing Requirements, and Test Results

# 3.1 Required Hardware and Software

This section details the hardware and explains the different sections on the board and how to set them up for the experiments as outlined in this design guide.

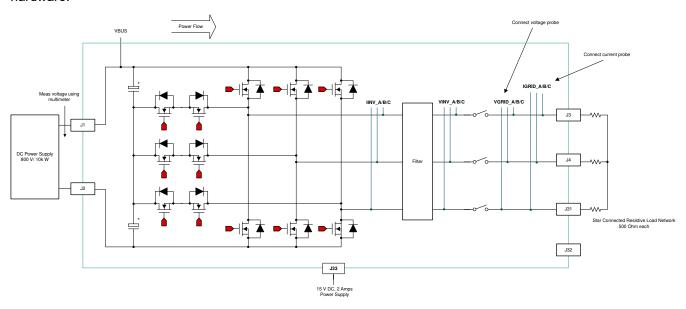

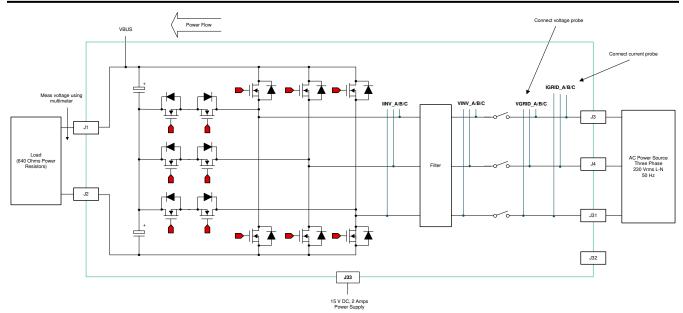

### 3.1.1 Hardware

## 3.1.1.1 Test Hardware Required

The DUT in this design is set up and is operated in several pieces:

- One TIDA-01606 power board

- Three TIDA-01606 gate driver cards

- One TIDA-01606 ISOHVCARD

- TMS320F28379D Control Card

- Mini USB cable

- · One USB isolator

- · Laptop or other computer

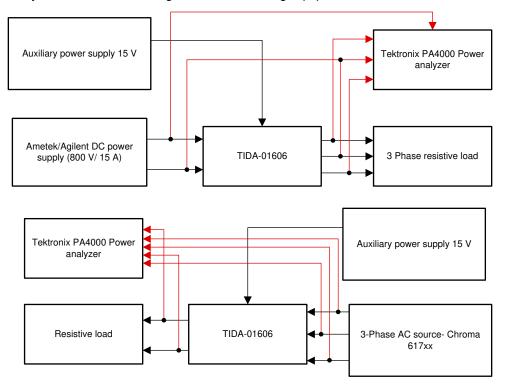

The test equipment required to power and evaluate the design is as follows:

- 24-V, 4-A bench style supply for primary board power

- · For PFC Mode

- 400 V<sub>I-I</sub> capable three-phase AC source

- > 10-kVA resistive load to be connected at the DC output

- For Inverter Mode

- Star connected resistive load network like the 10-kW Simplex PowerStart load bank

- 800-V, 12-A power supply for DC link input

- · Four-channel, power quality analyzer

- · Oscilloscope, voltage meter, and current probes

The design follows an HSEC control card concept. This design can be scaled across multiple devices from the C2000™ MCU product family with a compatible HSEC control card. The key resources used for controlling the power stage on the MCU are listed in  $\gtrsim$  3-1.

# 3.1.1.2 Microcontroller Resources Used on the Design

$\pm$  3-1 details the key controller peripherals used for control of the power stage on the board and  $\pm$  3-2 lists the key connectors and functions.

表 3-1. Key Controller Peripherals Used for Control of Power Stage on Board

| Pin Number     | DESCRIPTION                           | SOFTWARE NAME          |  |

|----------------|---------------------------------------|------------------------|--|

| 15, 31, 28     | Grid Voltage Sense Phase A, B, C      | TINV_VGRID_A, B, C     |  |

| 21, 33, 30     | Inverter Side Voltage Phase A, B, C   | TINV_VINV_A, B, C      |  |

| 25, 37, 34     | Inverter Side Current Phase A         | TINV_IINV_A, B, C      |  |

| 42             | Bus Voltage Sensing                   | TINV_VBUS              |  |

| 40             | Bus Voltage Mid Point Sensing         | TINV_VBUS_MID          |  |

| 12, 14, 18, 20 | Temperature A, B, C and Ambient       | TINV_TEMP_A, B, C, AMB |  |

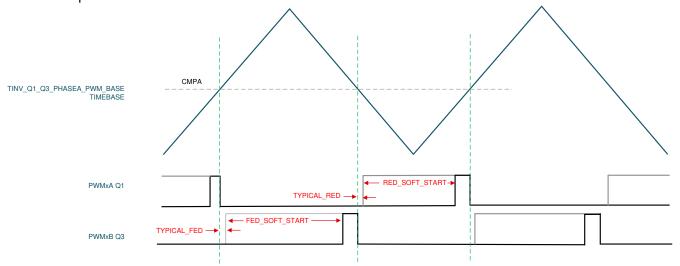

| 49, 50, 58     | Q1 PWM Phase A, B, C                  | TINV_Q1_A, B, C        |  |

| 51, 52, 60     | Q3 PWM Phase A, B, C                  | TINV_Q3_A, B, C        |  |

| 53, 54, 62     | Q2 PWM Phase A, B, C                  | TINV_Q2_A, B, C        |  |

| 99, 103, 107   | SDFM Data IG A, B, C                  | TINV_IGRID_A, B, C     |  |

| 101, 105, 109  | SDFM Clock IG A, B, C                 |                        |  |

| 57, 75         | SDFM Clock Source                     |                        |  |

| 89, 87 , 85    | SiC Fault Signal A, B, C (active Low) | TINV_FAULT_A, B, C     |  |

| 86, 88, 90, 92 | Relay on A, B, C, N                   | TINV_RELAY_A, B, C, N  |  |

| 61, 63         | Gate driver supply PWM                | TINV_GATE_DRIVE        |  |

| 59             | Control GPIO for FAN                  | TINV_FAN               |  |

# 表 3-1. Key Controller Peripherals Used for Control of Power Stage on Board (continued)

| <b>2.</b> • • • • • • • • • • • • • • • • • • • |                                                                                                           |                   |  |  |

|-------------------------------------------------|-----------------------------------------------------------------------------------------------------------|-------------------|--|--|

| Pin Number                                      | DESCRIPTION                                                                                               | SOFTWARE NAME     |  |  |

| 108, 110                                        | These pins are used to see ISR nesting and so forth, on the docking station while starting firmware debug | TINV_PROFILING1,2 |  |  |

| 95                                              | Gate driver enable                                                                                        | TNV_PWM_EN        |  |  |

| 81                                              | Gate driver Reset                                                                                         | TINV_R            |  |  |

# 表 3-2. Key Connectors and Functions

| CONNECTOR NAME          | FUNCTION                                |

|-------------------------|-----------------------------------------|

| J1, J2                  | DC+ and DC– terminals                   |

| J3, J4, J31, J32        | Phases A, B, C and neutral terminals    |

| J33                     | 15-V auxiliary power supply             |

| J34                     | Jumper for auxiliary power supply       |

| J5, J13                 | HSEC control card connector slot        |

| J23, J7, J17, J14, J20  | Phase Agate driver card connector slot  |

| J24, J15, J21, J9, J18  | Phase B gate driver card connector slot |

| J25, J16, J22, J12, J19 | Phase C gate driver card connector slot |

The following lists shows the hardware changes to TIDA-01606 - REV-6.

- 1. The resistors R1, R5, and R47 were changed to 2-m $\Omega$  current sense resistors.

- 2. The current-sense resistors along with AMC1306M05 (U1, U5, and U8) is used for current sensing in this design. The current sense out phase A LEM sensor has a noise pick-up issue and therefore is not used for current sensing and running the control loop.

- 3. Replaced R146, R149, R152 to 33 Ω.

- 4. On the TIDA-01606E4-ISOHVCARD, replaced R18 to 15-k  $\Omega$  and R26 to 0  $\Omega$ .

## 3.1.1.3 F28377D, F28379D Control-Card Settings

Certain settings on the device control card are needed to communicate over JTAG and use the isolated UART port. The settings also provide a correct ADC reference voltage. The following are the settings required on revision 1.1 of the F28379D control card.

Refer to the information sheet located inside C2000Ware at <sdk install path>\c2000ware\boards\controlCARDs\TMDSCNCD28379D:

- 1. A:SW1 on the control card must be set on both ends to ON (up) position to enable JTAG connection to the device and the UART connection for SFRA GUI. If this switch is OFF (down), one cannot use the isolated JTAG built in on the control card nor can SFRA GUI communicate to the device.

- 2. A:J1 is the connector for the USB cable that is used to communicate to the device from a host PC on which Code Composer Studio (CCS) runs.

- 3. A 3.3-V reference is desired for the control loop tuning on this design; therefore, set the appropriate jumpers to provide a 3.3-V reference externally to the on-chip ADC. For version 1.3 of the F28379D control card, this means SW3 and SW2 are moved to the end with "." that is, to the left, which puts 3.3-V VDDA as the reference for the ADC. Refer to the information sheet for more information.

### 3.1.2 Software

Find related software information at the following link:

# 3.1.2.1 Getting Started With Firmware

### 3.1.2.1.1 Opening the CCS project

The software of this design is available inside C2000Ware\_DigitalPower\_SDK and is supported inside the powerSUITE framework. To open the project:

Copyright © 2023 Texas Instruments Incorporated

- 1. Install CCS (version 10.1 or above)

- 2. Install C2000Ware DigitalPower SDK from the tool page

- 3. Open CCS, and create a new workspace

Inside CCS, go to View -> Resource Explorer. Under Resource Explorer, go to Software -> C2000Ware DigitalPower SDK - <version> -> development kits and select this solution; that is, TIDA-01606/ TIDA-010039, and click import project.

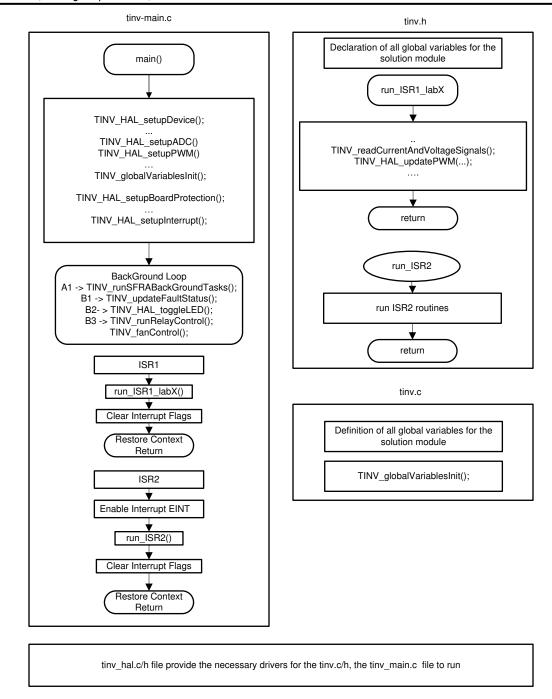

### 3.1.2.1.2 Digital Power SDK Software Architecture

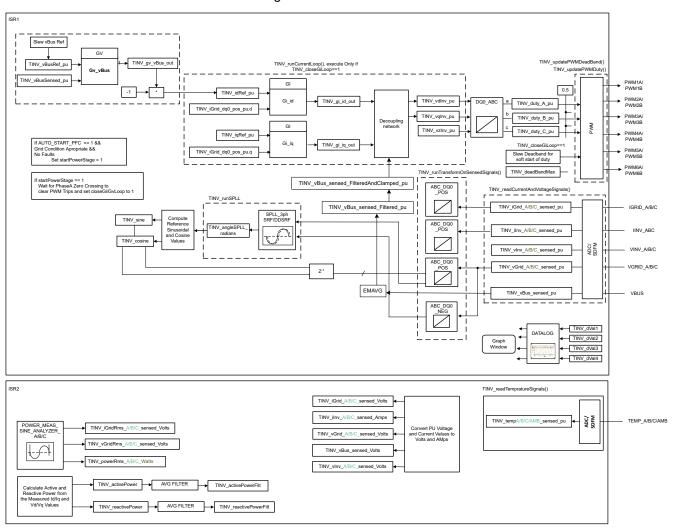

The general structure of the project is shown in <>. Once the project is imported, the Project Explorer will appear inside CCS.

Solution-specific and device-independent files that consist of the core algorithmic code are in "<solution>.c/h".

Board-specific and device-specific files are in "<solution>\_hal.c/h". This file consists of device-specific drivers to run the solution. If the user wants to use a different modulation scheme or a different device, the user is required only to make changes to these files, besides changing the device support files in the project.

The "<solution>-main.c" file consists of the main framework of the project. This file consists of calls to the board and solution file that help in creating the system framework, along with the interrupt service routines (ISRs) and slow background tasks.

For this design, <solution> is "tinv" which is also referred to as the module name.

The powerSUITE page can be opened by clicking on the "main.syscfg" file, listed under the Project Explorer. The powerSUITE page generates the "<solution>\_settings.h" file. This file is the only C based file used in the compile of the project that is generated by the powerSUITE page. The user must not modify this file manually, as the changes will be overwritten by powerSUITE each time the project is saved. "<solution>\_user\_settings.h" is included by the "<solution>\_settings.h"and can be used to keep any settings that are outside the scope of powerSUITE tools such as #defines for ADC mapping, GPIOs etc.

The "Kit.json" and "solution.js" files are used internally by powerSUITE and also must not be modified by the user. Any changes to these files will result in the project not functioning properly.

The solution name is also used as the module name for all the variables and defines used in the solution.

Therefore, all variables and function calls are prepended by the **TINV** name (for example, **TINV**\_vSecSensed\_pu). This naming convention lets the user combine different solutions while avoiding naming conflicts.

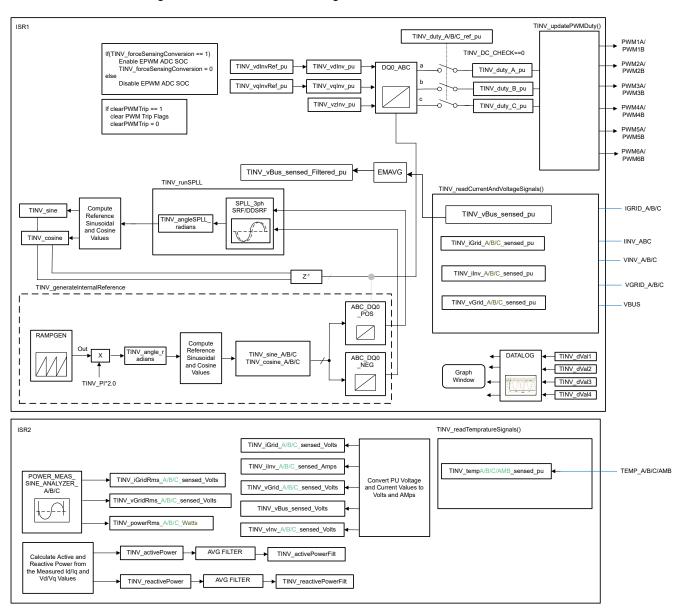

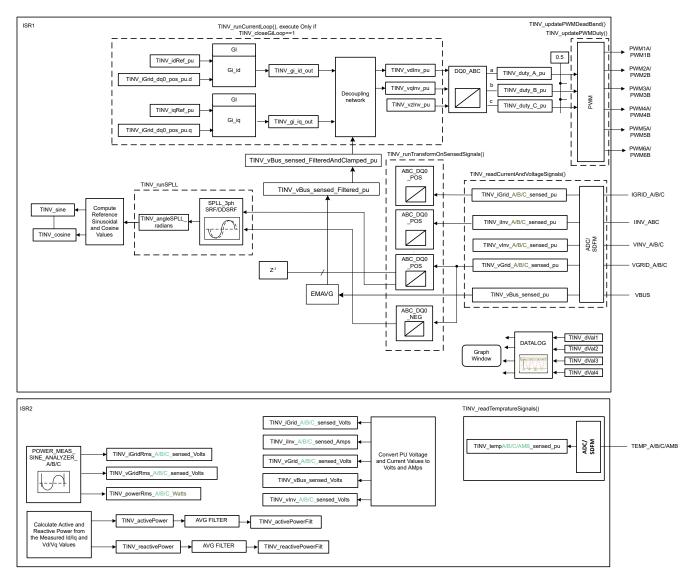

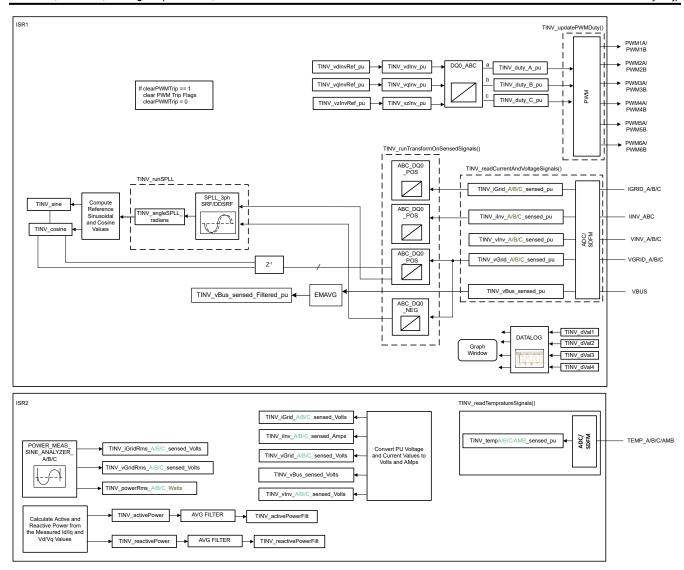

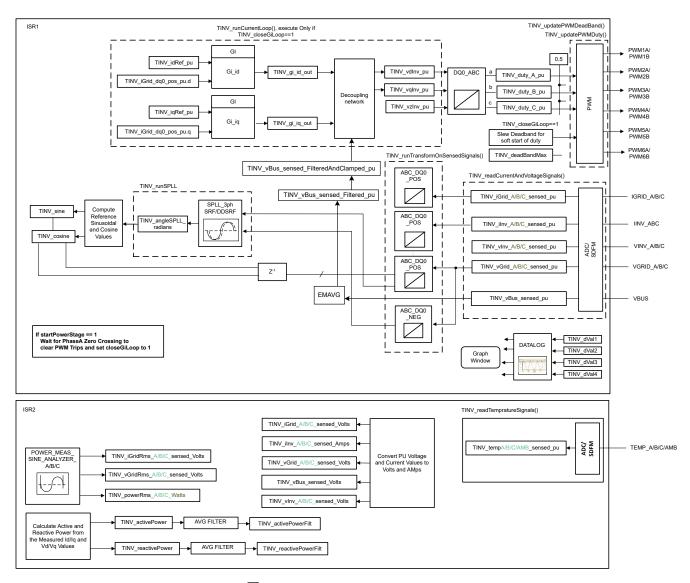

### 3.1.2.1.3 Interrupts and Lab Structure

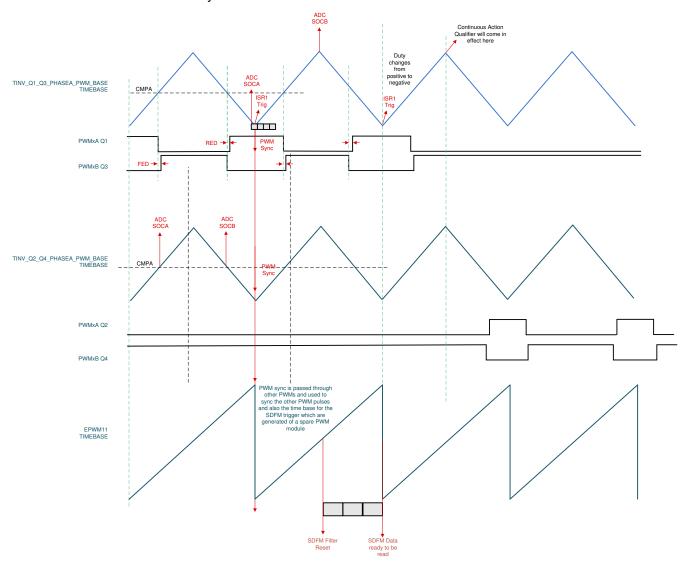

The project consists of two ISRs (ISR1 and ISR2) with ISR1 being the fastest and non-nestable ISR. ISR1 is reserved for the control loop and the PWM update. ISR1 is triggered by the PRIM\_LEG1\_PWM\_BASE → EPWM\_INT\_TBCTR\_U\_CMPC event.

ISR2 is triggered by CPU Timer INT which is initiated by an overflow on CPU timer. It is used to run housekeeping functions such as doing a running average on the currents and voltage signals to remove noise and running the slew rate function for commanded references.

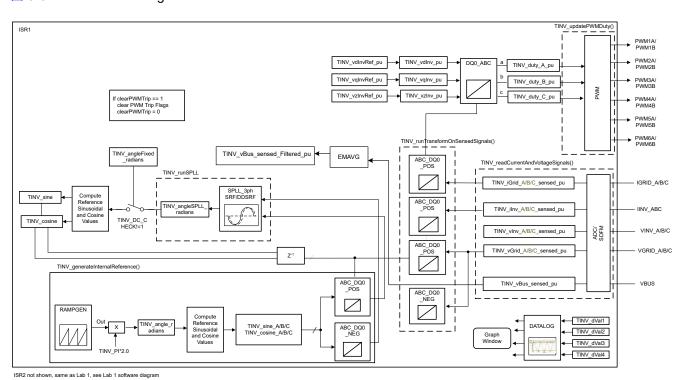

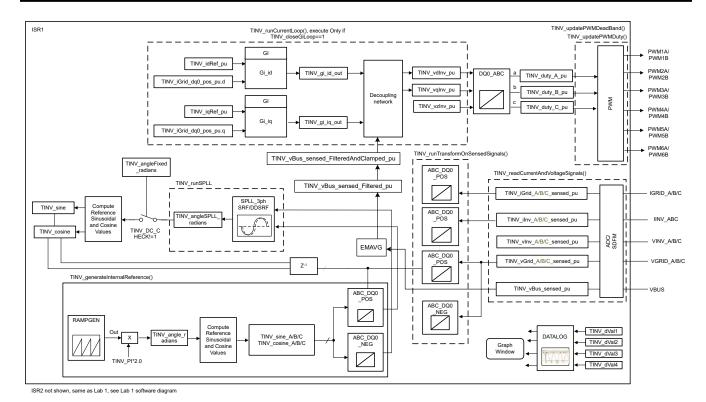

図 3-1. Software Flow Diagram

The software of this reference design is organized in seven labs, 表 3-3 lists the labs and how they have been tested. All the labs can be run on the C28x Main CPU or the *Control Law Accelerator*.

# 表 3-3. Overview of Labs to Test Reference Design

| LAB NUMBER | DESCRIPTION                                                                                      | COMMENTS                                                                                                                                                               | TEST ENVIRONMENT                                               |

|------------|--------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| 1          | INV: PWM and ADC check                                                                           | Test the PWM driver, ISR structure and execution rate, can be run on a control card. Unit test protection mechanisms. Test ADC mapping and reading of conversion data. | Control Card                                                   |

| 2          | INV: Open loop check                                                                             | PWM Check, ADC check,<br>Protection Check, inverter mode<br>DC bus connected and resistive<br>star network as load                                                     | Control Card + Power Stage<br>Hardware                         |

| 3          | INV: Closed Current Loop, Resistive load connected at AC                                         |                                                                                                                                                                        | Control Card + Power Stage<br>Hardware                         |

| 4          | INV: Closed Current Loop, Grid connected test inverter mode                                      |                                                                                                                                                                        | Control Card + Emulated power stage under Hardware In-the Loop |

| 5          | PFC: Three phase AC source , Resistive load at DC, open Loop check                               | Check if the vGridRms, iGridRms, vBus meas are correct     Check if PLL is locked.                                                                                     | Control Card + Power Stage<br>Hardware                         |

| 6          | PFC: Closed Current Loop, Resistive load connected at DC, three phase AC?                        |                                                                                                                                                                        | Control Card + Power Stage<br>Hardware                         |

| 7          | PFC: Closed Voltage loop + Current Loop ,<br>Resistive load connected at DC, three<br>phase AC ? |                                                                                                                                                                        | Control Card + Power Stage<br>Hardware                         |

## 3.1.2.1.4 Building, Loading and Debugging the Firmware

To build the project, right-click on the project name and click Rebuild Project. The project builds successfully.

To load the project, first make sure in the Project Explorer the correct target configuration file is set as Active under targetConfigs (\*.ccxml file). Then, click  $Run \rightarrow Debug$  to launch a debugging session. In case of dual-CPU devices, a window may appear for the user to select the CPU on which the debug is to be performed. In this case, select CPU1. The project will then load on the device and the CCS debug view will become active. The code will halt at the start of the main routine.

To debug the system one would monitor the variables in the watch/expressions window. To populate this window with the correct variables, click View → Scripting Console to open the scripting console dialog box. On the upper right corner of this console, click on *Open* and then browse to the "setupdebugenv\_lab<Number>.js" script file located inside the project folder. This will populate the watch window with the appropriate variables needed to debug the system. Enable Continuous Refresh button on the watch window to enable continuous update of values from the controller.

Real-time emulation is a special emulation feature that allows windows within Code Composer Studio to be updated while the MCU is running. This allows graphs and watch views to updated, but also allows the user to change values in watch or memory windows, and see the effect of these changes in the system without halting the processor. To enable real-time mode click on this button on the top bar of CCS <insert image>. A message box may appear. If so, select YES to enable debug events. This will set bit 1 (DGBM bit) of status register 1 (ST1) to a "0". DGBM is the debug enable mask bit. When the DGBM bit is set to "0", memory and register values can be passed to the host processor for updating the debugger windows.

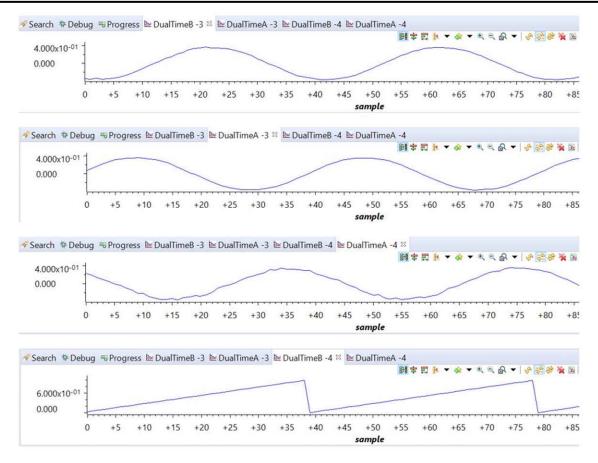

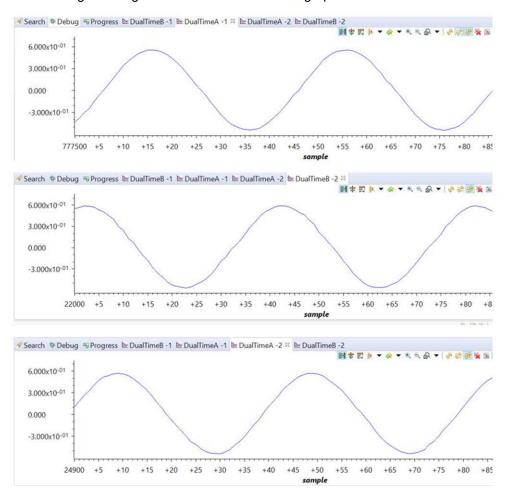

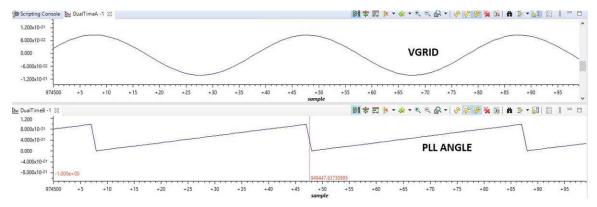

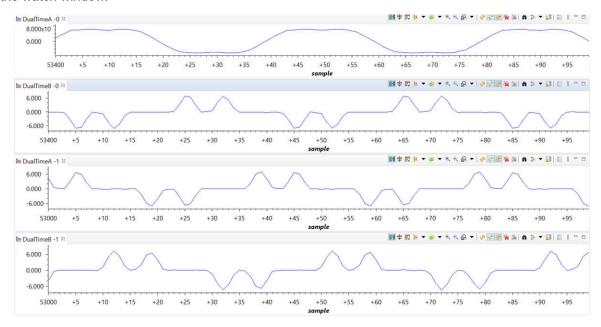

In different labs, sometimes the currents and voltages measured or the control variables need to be verified by viewing the data in the graph window. For this Graph window can be used which in conjunction with a piece of code that runs on the controller can show a snapshot of how the values are being sensed by the controller. The values are logged by the datalogger typically in the slower ISRs. To import the graph into the CCS view select Tools => Graph => DualTime, and click Import and point to the graph1. GraphProp file inside the project folder. Two graphs will appear in CCS. Click Continuous Refresh on these graphs. A second set of graphs can also be added by importing the graph2. GraphProp file.

# **CPU Loading**

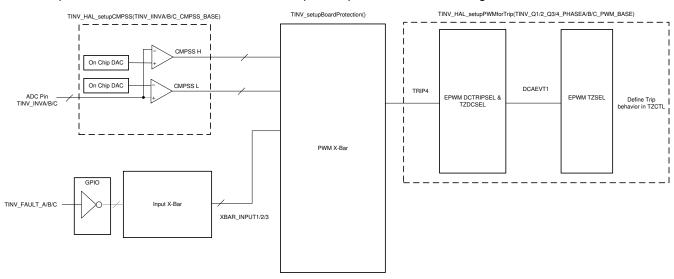

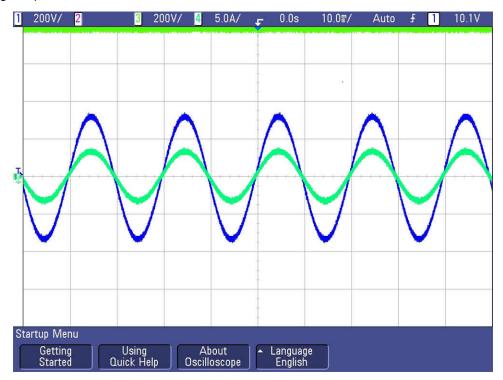

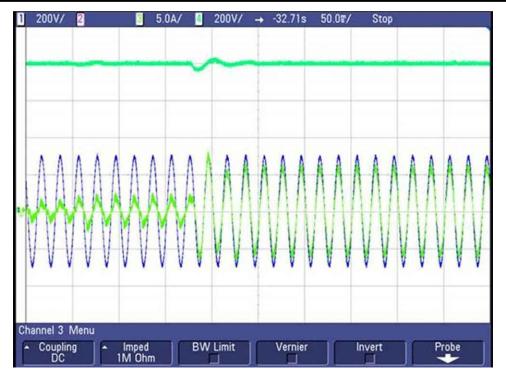

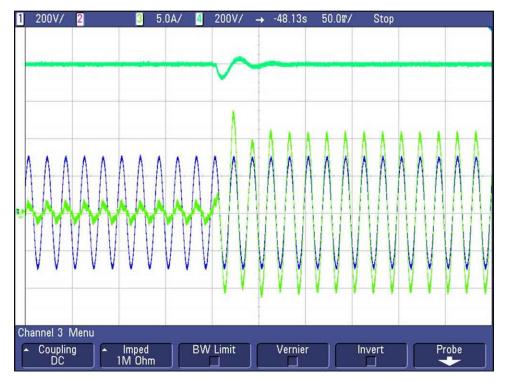

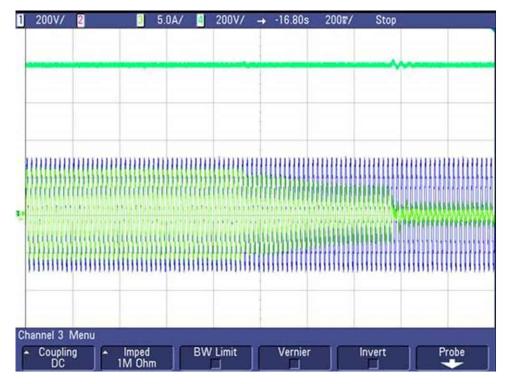

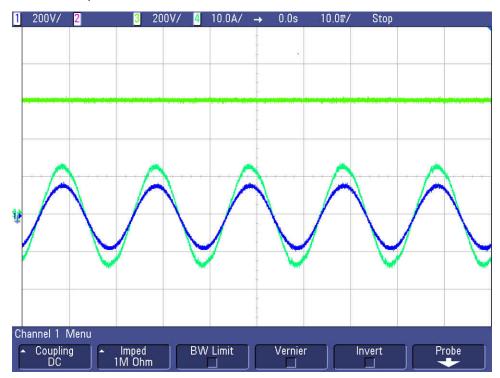

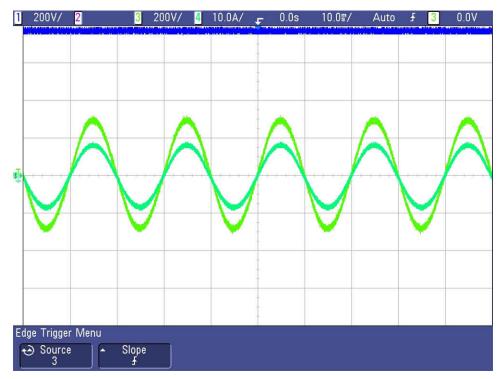

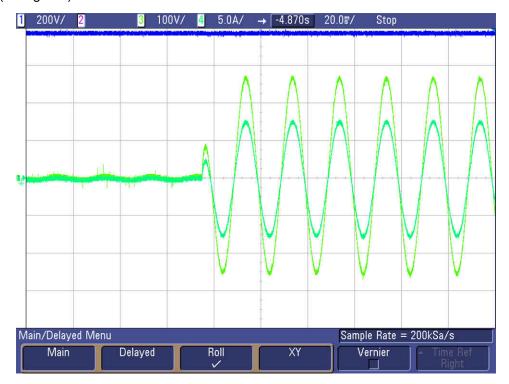

The main control ISR with Lab 3 and Lab 7 takes approximately 54 MIPS at 50-kHz rate when running from CPU1, that is approximately 27% of the CPU when running from 200-MHz F2837x processor. This includes the ADC drivers, abc-dq0 and dq0-abc transformation, transformation, PWM generation, two current control loops, one voltage loop, and the SFRA call.