# TI Designs: TIDA-00892

# 信号および電力が統合された絶縁RS-485のリファレンス・デザイン

# TEXAS INSTRUMENTS

#### 概要

このTI Designは、絶縁DC電力を供給し、絶縁RS-485 通信をサポートする、小型のソリューションを実現します。 TIDA-00892は、電源内蔵の強化絶縁型デジタル・アイソレータとRS-485トランシーバの組み合わせで構成されています。このソリューションは、最小限の占有面積で目的の機能を実現するよう設計されています。

#### リソース

TIDA-00892

デザイン・フォルダ

ISOW7841

プロダクト・フォルダ

SN65HVD1473

プロダクト・フォルダ

E2Eエキスパートに質問

## 特長

- 最小の組み合わせソリューション

- ISOW7841デバイスの占有面積と同等

- 単一電源のソリューション

- インターフェイス側の部品に別の電源は不要

- 別の変圧器が必要ないため、ソリューションのBOMコストを低減

- 設計の単純化

- 他の全二重RS-485トランシーバに拡張可能

- SN65HVD14xx、SN65HVD7x、SN65HVD3x

- 多少のレイアウト変更により、半二重にも拡張可能

#### アプリケーション

- グリッド通信モジュール

- ビルディング・オートメーションおよびHVAC

- 産業用オートメーション

- 医療用機器

- モータ・ドライブ

使用許可、知的財産、その他免責事項は、最終ページにあるIMPORTANT NOTICE(重要な注意事項)をご参照くださいますようお願いいたします。 英語版のTI製品についての情報を翻訳したこの資料は、製品の概要を確認する目的で便宜的に提供しているものです。 該当する正式な英語版の最新情報は、www.ti.comで閲覧でき、その内容が常に優先されます。 TIでは翻訳の正確性および妥当性につきましては一切保証いたしません。 実際の設計などの前には、必ず最新版の英語版をご参照くださいますようお願いいたします。

System Overview www.tij.co.jp

## 1 System Overview

#### 1.1 Design Theory

#### 1.1.1 Isolation in Data Communication

Most industrial interface systems are areas where noise can seriously affect the integrity of data transfer. A tested method of improving noise performance for any interface circuit is galvanic isolation. Isolating the low-voltage (LV) microcontroller (MCU) side from the high-voltage (HV) interface side has proven to be an effective solution to protect from data corruption and to protect LV side components from seeing HV stresses like electrostatic discharge (ESD), electrical fast transient (EFT), and surge.

Common-mode noise effects and many forms of radiated noise can affect the communication system. Unwanted currents and voltages on a cable bus connecting multiple systems can cause severe problems. These voltages and currents come primarily from two sources: ground loops and electrical line surges. Ground loops occur when a bus or system uses multiple ground paths. Two system grounds connected to the bus and separated by hundreds or thousands of meters may not have the same potential. Because of this potential difference, current flows between these points. This unintended current flow can cause bit errors and damage or destroy components. Electrical surges can be caused by many sources, the result of currents coupled onto cable lines through induction. Long cable lines in industrial environments are especially susceptible to this phenomenon. The operation of electric motors, in particular, causes rapid changes in the ground potential. These changes can generate a current flow through any nearby lines to equalize the ground potential. Other HV stress voltage sources include ESDs, coupled transient noises (EFT) and lightning strikes (surge). These induced surges can result in thousands of volts of potential on the line and manifest themselves as transient current and voltage surges. Thus, a remote node may receive a 5-V switching signal superimposed on a HV level with respect to the local ground. These uncontrolled voltages and currents can corrupt the signal and be catastrophic to the device and system, damaging or destroying the components connected to the bus and resulting in system failure. RS-485 systems that run over long distances and connect multiple systems are especially susceptible to these events.

Isolating the RS-485 system devices from each of the systems connected to the bus prevents ground loops and electrical surges from destroying circuits. Isolation prevents ground loops as each system connected to RS-485 cable bus and each RS-485 circuit has a separate and isolated ground. By referencing each RS-485 circuit only to one ground, ground loops are eliminated. Isolation also allows the RS-485 circuit reference voltage levels to rise and fall with any surges that appear on the cable line. Allowing the circuit voltage reference to move with surges, rather than being clamped to a fixed ground, prevents devices from being damaged or destroyed. To accomplish system isolation, both the RS-485 signal lines and power supplies must be isolated.

# 1.1.2 RS-485 Communication

Industrial and instrumentation applications (I and I) require transmission of data between multiple systems often over very long distances. The RS-485 bus standard is one of the most widely used physical layer bus designs in I and I applications.

The key features of RS-485 that make it ideal for use in I and I communications applications are:

- Long distance links of up to 4000 feet

- Bidirectional communications possible over a single pair of twisted cables

- Differential transmission increases noise immunity and decreases noise emissions

www.tij.co.jp System Overview

- Multiple drivers and receivers can be connected on the same bus

- Wide common-mode range allows for differences in ground potential between the driver and receiver

In harsh and noisy environments such as multi-unit residential buildings or industrial settings, an RS-485 bus architecture can be used to implement a low-cost, yet robust communications network. The differential nature of RS-485 signaling makes it less susceptible to external interference. Moreover, the RS-485 specification supports multidrop configurations, thus allowing the connection of multiple meters to a single bus. For instance, RS-485 can be used in an apartment building to transmit data from meters in each apartment to a central unit that aggregates the data from the individual meters, which can then be read through a wireless or PLC link. A similar approach can be used in industrial systems that require multiple cost centers to be metered.

#### 1.2 System Description

The TIDA-00892 reference design combines both data and power isolation along with RS-485 communication interface to provide a robust, low-cost, low footprint solution that customers can directly place on their designs. This TI Design combines a High-Performance Reinforced Digital Isolator with Integrated High-Efficiency, Low Emissions DC-DC Converter (ISOW7841) with a Robust 3.3V Full-Duplex RS-485 Transceiver (SN65HVD1473).

The TIDA-00892 does not require any additional components to generate the isolated power. This makes the solution less than a quarter of the size of all existing solutions using a discrete transformer to generate the required isolated power. This TI Design takes a single power supply input (3 to 5.5 V) and digital signals referred to the input supply level. The board generates an isolated power supply using an integrated DC-DC converter. This isolated supply is used to power the RS-485 transceiver. The input signals are isolated and connected to the transceiver, which converts the digital signals into its RS-485 counterpart.

An electricity grid without adequate communications is simply a power broadcaster. It is through the addition of two-way communications that the power grid is made "smart." Communications enables utilities to achieve three key objectives: intelligent monitoring, security, and load balancing. By using two-way communications, data can be collected from sensors and meters located throughout the grid and transmitted directly to the grid operator's control room. This added communications capability provides enough bandwidth for the control room operator to actively manage the grid. The communications must be reliable, secure, and cost effective. The sheer scale of the electrical grid network makes cost a critical consideration when implementing a communications technology. The communications used in grid infrastructure systems is dominated by RS-485. The TIDA-00892 design can fit in to power the RS-485 bus side and provide a cost-effective, low-footprint solution to this requirement.

PLCs and grid communication systems have been an integral part of factory automation and industrial process control. They use digital and analog I/O modules to interface to sensors, actuators, and other equipment. Analog inputs for the PLC system include temperature sensors and transmitters, current sensors, voltage sensors, and others that can convert a physical quantity to an electrical signal. Digital inputs include push-buttons, proximity switches, photo sensors, pressure switches, and more. These signals need to be either group isolated or per channel isolated. PLCs are expected to work in harsh industrial environments. Hence sensor signals are converted to digital domain and coupled through a digital isolator to control domain. For sensor signal conditioning, power is generated from the backplane side by an isolated DC-DC converter. Fitting in the TIDA-00892 can significantly reduce the required area and bring down the BOM cost by eliminating the requirement for discrete transformers.

System Overview www.tij.co.jp

Medical equipment need isolation for patient safety. For ECG, multiple leads are connected to the patient. The signal chain must be robust enough to capture very weak signals, digitize and process it, and pass it to the system controller over the isolation barrier. The power for signal processing units is typically generated by onboard isolated DC-DC converters. This power can be replaced directly with the TIDA-00892 to get both communication and power isolation with the RS-485 interface. Also any peripheral connected to this equipment must be isolated from the controller. This solution makes sense to digitally isolate the interface signals and also power up the transceivers.

www.tij.co.jp System Overview

# 1.3 Key System Specifications

| 衣             | 1. | ney | System | Specifications |  |

|---------------|----|-----|--------|----------------|--|

| CDECIFICATION |    |     |        |                |  |

| FEATURE                | SPECIFICATION      | VALUE                               |

|------------------------|--------------------|-------------------------------------|

| Input supply           | Input voltage      | 3 to 5 V                            |

|                        | Output voltage     | 3.3 V                               |

| Isolated output supply | Output current     | 75 mA (3.3 V <sub>IN</sub> )        |

|                        | Output current     | 130 mA (5 V <sub>IN</sub> )         |

| Communication          | Max data rate      | 20 Mbps (full-duplex communication) |

|                        | Clearance          | > 3 mm                              |

| Isolation              | Working voltage    | 300 V <sub>RMS</sub>                |

|                        | CMTI               | > 100 kV/µs                         |

|                        | ESD                | 6 kV (across barrier)               |

| EMI or EMC             | L3D                | 16 kV (across RS-485 lines)         |

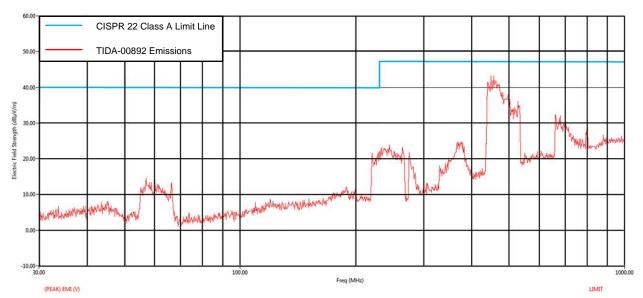

|                        | Radiated emissions | CISPR22 (Class A)                   |

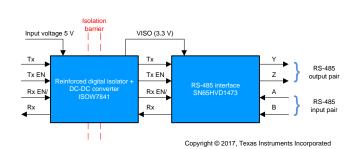

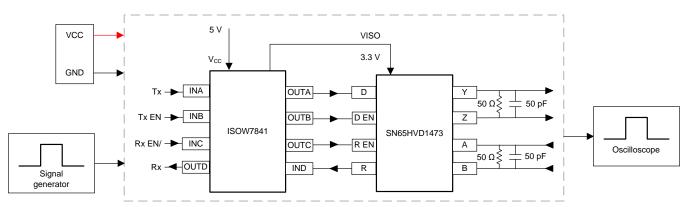

# 1.4 Block Diagram

図 1. TIDA-00892 Block Diagram

☑ 1 shows the high-level block diagram of the TIDA-00892. As previously mentioned, this TI Design can be broken down into two main sections: the isolation block (ISOW7841) and the interface block (SN65HVD1473).

The TIDA-00892 works on a single input of 3 to 5.5 V. The integrated power supply can produce an isolated output voltage of 3.3 V (for any input) or 5 V (for VCC1  $\geq 5 \text{ V}$ ). This can be used to power up the RS-485 interface block. The TIDA-00892 communicates with digital signals on one side and gives the RS-485 lines on the other. The design can be interfaced to an MCU transmitting and receiving data while controlling the TX and RX enable lines. These signals are isolated from the RS-485 lines available for communication to the field side. The SN65HVD1473 RS-485 transceiver and the isolated power supply integrated four channel digital isolator. The side A of the isolator is powered from a 5-V or 3.3-V power supply, the secondary side of the isolator will be powered through the integrated isolated power supply. The integrated power supply can produce two voltage configurations on side B: 5 V or 3.3 V for the 5-V supply on side A and 3.3 V for the 3.3-V supply on side A. The two available voltage configurations enable the same design to be used with other transceivers.

System Overview www.tij.co.jp

The load in this TI Design is the RS-485 transceiver. The design can interface with the MCU to transmit and receive data and enable transmission and reception. The signals to and from the MCU are isolated from the transceiver. The TIDA-00892 board can be broken down to two main sections: the isolation block and the interface block.

www.tij.co.jp System Overview

## 1.5 Highlighted Products

The TIDA-00892 features the following devices from Texas Instruments.

#### 1.5.1 ISOW7841

The ISOW784x is a family of high-performance quad-channel reinforced digital isolators with an integrated high-efficiency power convertor. The integrated DC-DC convertor provides up to 650 mW of isolated power at high efficiency and can be configured for various input and output voltage configurations. These devices eliminate the need for a separate isolated power supply in space-constrained isolated designs. ISOW784x devices provide high electromagnetic immunity and low emissions, while isolating CMOS or LVCMOS digital I/Os. The signal isolation channel has a logic input and output buffer separated by a silicon dioxide (SiO2) insulation barrier, whereas power isolation uses on-chip transformers separated by a thin film polymer as insulation material. These devices prevent noise currents on a data bus or other circuits from entering the local ground and interfering with or damaging sensitive circuitry. Through innovative chip design and layout techniques, the electromagnetic compatibility of the ISOW784x has been significantly enhanced to ease system level ESD, EFT, surge, and emissions compliance. The high efficiency of the power convertor allows operation at a higher ambient temperature. The ISOW784x family of devices is available in a 16-pin SOIC wide-body (DWE) package.

- · Integrated high efficiency DC-DC convertor with on-chip transformer

- Wide input supply range: 3 to 5.5 V

- Regulated 5- or 3.3-V output

- Up to 0.65-W output power

- 130-mA load current (5 to 5 V; 5 to 3.3 V;)

- 75-mA load current (3.3 to 3.3 V)

- · Soft start to limit inrush current

- Overload and short circuit protection

- Thermal shutdown

- Signaling rate up to 100 Mbps

- Low prop-delay: 13 ns typical (5-V supply)

- High CMTI: ±100 kV/µs (min)

- Robust electromagnetic compatibility (EMC)

- System level ESD, EFT, and surge immunity

- Low radiated emissions

- Safety-related certifications

- 7071-V<sub>PK</sub> Reinforced Isolation per DIN V VDE V 0884-10 (VDE V 0884-10): 2006-12

- 5000-V<sub>RMS</sub> Isolation for 1 Minute per UL 1577

- CSA Component Acceptance Notice 5A, IEC 60950-1 and IEC 60601-1 End Equipment Standards

- CQC Approval per GB4943.1-2011

- TUV Certification according to EN 60950-1 and EN 61010-1

- All agency certifications are planned

- Extended temperature range: –40°C to 125°C

System Overview www.tij.co.jp

#### 1.5.2 SN65HVD1473

The SN65HVD1473 is a full-duplex transceiver that features the highest ESD protection in the RS-485 portfolio, supporting ±16-kV IEC61000-4-2 contact discharge and > ±30-kV HBM ESD protection. This RS-485 transceiver has a robust 3.3-V driver and receiver and is offered in a standard SOIC package as well as in a small-footprint MSOP package. The large receiver hysteresis of the SN65HVD1473 device provides immunity to conducted differential noise and the wide operating temperature enables reliability in harsh operating environments. This device combines a differential driver and a differential receiver, which operate from a single 3.3-V power supply. Each driver and receiver has a separate input and output pins for full-duplex bus communications designs. These devices all feature a wide common-mode voltage range which makes the devices suitable for multi-point applications over long cable runs.

The SN65HVD1473 device has active-high driver enables and active-low receiver enables. A low, less than 5-µA standby current can be achieved by disabling both the driver and receiver.

- 1/8 unit-load options available

- Up to 256 nodes on the bus

- · Bus I/O protection

- >±30-kV HBM protection

- >±16-kV IEC-61000-4-2 Contact Discharge

- >±4-kV IEC61000-4-4 Fast Transient Burst

- Extended industrial temperature range:

- –40°C to 125°C

- Large receiver hysteresis (70 mV) for noise rejection

- Low power consumption

- <1.1-mA quiescent current during operation</li>

- Low standby supply current: 10 nA typical, < 5 μA (max)</li>

- Glitch-free power-up and power-down protection for hot-plugging applications

- 5-V tolerant logic inputs compatible with 3.3-V or 5-V controllers

www.tij.co.jp Getting Started Hardware

# 2 Getting Started Hardware

## 2.1 Board Description

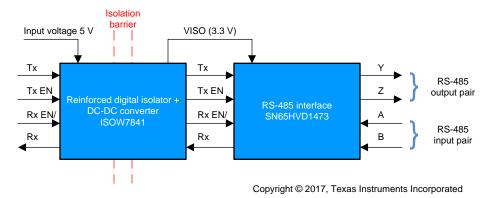

$\boxtimes$  2 shows the size of the isolated RS-485 with an integrated power solution. The solution space within the board has been marked in red and is slightly bigger than the ISOW7841 IC. The full board measures 31 x 13.3 mm while the actual solution space (marked in red) is 11.9 x 11.2 mm.

図 2. Solution Space

3 shows the locations of the connectors on the board for interfacing with the solution.

図 3. Connectors

#### 2.2 Connectors Description

表 2. Connectors

| CONNECTOR | PIN POSITION | PIN NAME | I/O OR POWER | DESCRIPTION               |

|-----------|--------------|----------|--------------|---------------------------|

|           | 1            | VIN      | Power        | Input supply (3 to 5.5 V) |

|           | 2            | Tx       | I            | Digital driver input      |

| J1        | 3            | Tx EN    | I            | Driver enable             |

| 31        | 4            | Rx EN/   | I            | Receiver enable           |

|           | 5            | Rx       | 0            | Digital receiver output   |

|           | 6            | GND1     | Ground       | Input supply ground       |

|           | 1            | VISO     | Power        | Isolated power output     |

| J2        | 2,3          | Y, Z     | 0            | RS-485 output pair        |

| JZ        | 5,4          | A, B     | I            | RS-485 input pair         |

|           | 6            | GND2     | Ground       | Isolated output ground    |

The design comes pre-populated with two of the TI ICs (ISOW7841 and SN65HVD1473) and a  $120-\Omega$  termination resistor on the bus to match the transmission line impedance. VCC1 and GND1 are connected at Pin 1 and Pin 6 of J1, respectively. The digital input can be applied to Pin 2 of J1 and the receiver output can be observed on Pin 5 of J1. On the other side of the board, the differential bus lines A and B (RS-485 input lines) are Pin 5 and Pin 4 respectively on J2, while Y and Z (RS-485 output lines) are connected to Pin 2 and Pin 3 respectively on J2. The boards include male berg heads to allow bus cables to be securely attached.

Connect MCU Tx to Pin 2 of J1 and MCU Rx to Pin 5 of J1. Connect the driver and receiver enable lines from MCU to Pins 3 and 4, respectively. The RS-485 lines, AB and YZ, need to be connected as individual pairs of twisted pair cables. The system can be configured and used for half-duplex or full-duplex communication by providing appropriate transmit and receive enable signal from MCU side.

This TI Design can be extended to other RS-485 transceivers by replacing the existing transceiver on the board and selecting the right voltage configuration. The isolated output voltage configuration can be easily changed by changing the resistor combination of R1 and R2. See 表 3 to understand how to realize the required voltage configuration.

表 3. Voltage Configurations

| INPUT VOLTAGE (V) | OUTPUT VOLTAGE (V) | R1 (Ω)                | R2 (Ω)                |

|-------------------|--------------------|-----------------------|-----------------------|

| 5.0               | 5.0                | Populate              | Do Not Populate       |

| 3.0               | 3.3                | Do Not Populate       | Populate              |

| 3.3               | 3.3                | Do Not Populate       | Populate              |

| 3.3               | 5.0                | Invalid configuration | Invalid configuration |

www.tij.co.jp Testing and Results

# 3 Testing and Results

## 3.1 Test Setups

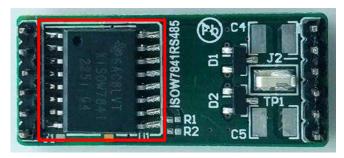

図 4. Full Duplex Communication Test Setup

Copyright © 2017, Texas Instruments Incorporated

図 5. Typical Test Setup

Testing and Results www.tij.co.jp

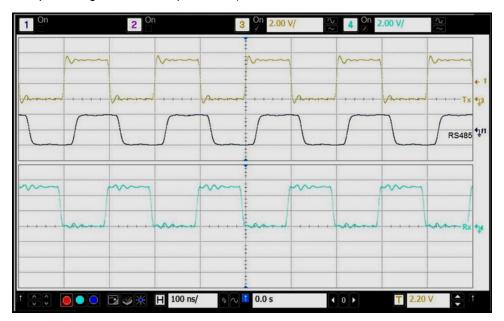

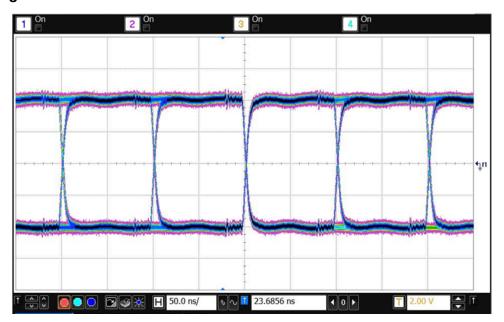

# 3.2 Full-Duplex Communication

As shown in 🗵 4, two boards are connected to each other, forming a full-duplex system for the test setup. Both the boards are powered with a 5-V supply voltage and VISO is configured for 3.3 V in a full-duplex mode (Tx EN pulled high and Rx EN pulled low).

図 6. Full-Duplex Communication

www.tij.co.jp Testing and Results

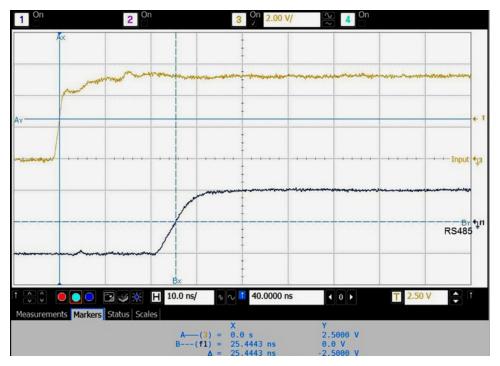

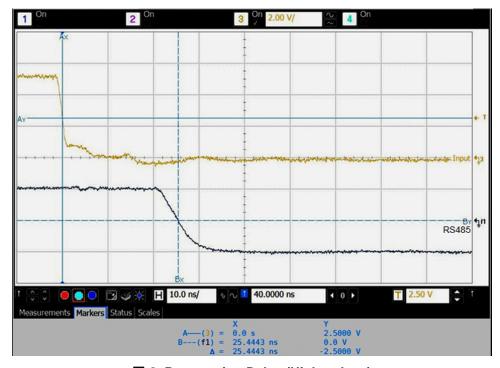

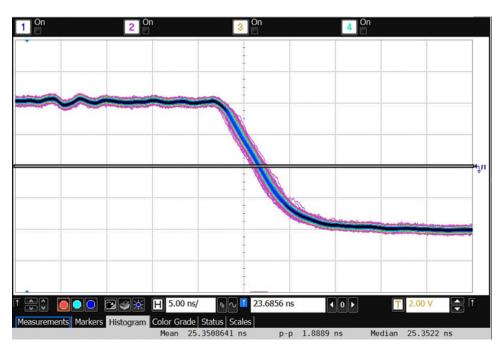

## 3.3 Propagation Delay

As shown in 🗵 5, single board propagation delay from digital side to RS-485 side was measured.

図 7. Propagation Delay (Low to High)

図 8. Propagation Delay (High to Low)

Testing and Results www.tij.co.jp

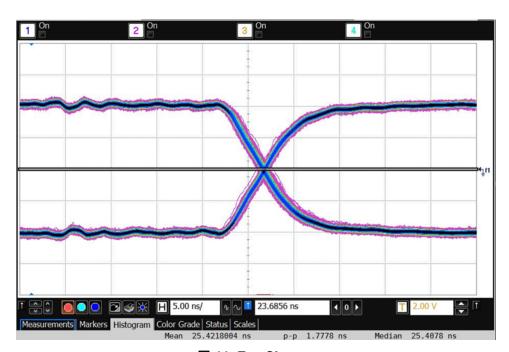

## 3.4 Jitter

図 9. Jitter

www.tij.co.jp Testing and Results

# 3.5 Eye Diagram

図 10. Eye Diagram

図 11. Eye Closure

Testing and Results www.tij.co.jp

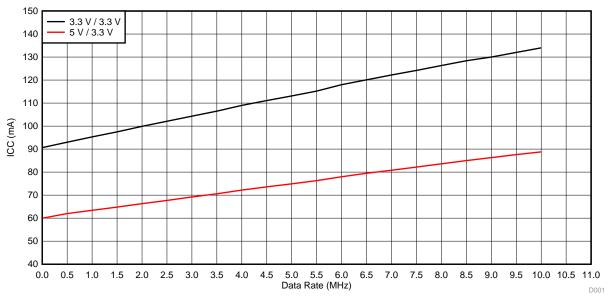

#### 3.6 Current Consumption

Current consumption of the TIDA-00892 was measured with both the RS-485 receiver and transmitter toggling at different data rates. Termination resistors were populated as per ⋈ 5.

図 12. ICC versus Data Rate

# 3.7 IEC-ESD Performance (IEC-61000-4-2)

Contact discharge IEC-ESD testing was performed on the TIDA-00892 using a pointed contact discharge tip. The board was subjected to mainly two kinds of ESD strikes. In the "Across barrier" row, the interface side was struck with the reference ground or power earth connected at the MCU side ground (GND1). Similarly for the "Same side" row, the interface lines were struck with the reference ground or power earth connected to the interface side ground (GND2). 表 4 shows the IEC-ESD test results. Each of the stressed pins were subjected to 10 strikes of each polarity of the corresponding stress voltage.

| NATURE OF STRIKE | STRIKE POINT | STRESS VOLTAGE                                                                                                                                   | RESULT |

|------------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------|--------|

|                  | VISO         | ±6 kV                                                                                                                                            | Pass   |

|                  | Υ            | ±6 kV                                                                                                                                            | Pass   |

| Across barrier   | Z            | ±6 kV                                                                                                                                            | Pass   |

| Across partier   | A            | ±6 kV                                                                                                                                            | Pass   |

|                  | В            | ±6 kV  ±6 kV  ±6 kV  ±6 kV  ±6 kV  ±6 kV  ±16 kV  ±16 kV  ±16 kV                                                                                 | Pass   |

|                  | GND2         | ±6 kV                                                                                                                                            | Pass   |

|                  | Υ            | #6 kV Pass #16 kV Pass #16 kV Pass | Pass   |

| Same side        | Z            |                                                                                                                                                  | Pass   |

| Same side        | A            |                                                                                                                                                  | Pass   |

|                  | В            | ±16 kV                                                                                                                                           | Pass   |

表 4. IEC-ESD Results

www.tij.co.jp Testing and Results

# 3.8 Radiated Emissions (CISPR 22)

The emissions measurements were done according to CISPR 22 standard in a certified facility. 🗵 13 shows the emissions measurement for the TIDA-00892 design when the communication lines were being operated under a static high condition.

図 13. Radiated Emissions (CISPR 22)

Design Files www.tij.co.jp

## 4 Design Files

#### 4.1 Schematics

To download the schematics, see the design files at TIDA-00892.

#### 4.2 Bill of Materials

To download the bill of materials (BOM), see the design files at TIDA-00892.

#### 4.3 PCB Layout Recommendations

#### 4.3.1 Layout Prints

To download the layer plots, see the design files at TIDA-00892.

#### 4.4 Altium Project

To download the Altium project files, see the design files at TIDA-00892.

#### 4.5 Gerber Files

To download the Gerber files, see the design files at TIDA-00892.

## 4.6 Assembly Drawings

To download the assembly drawings, see the design files at TIDA-00892.

#### 5 Related Documentation

- Texas Instruments, ISOW784x High-Performance, 5000-VRMS Reinforced Quad-Channel Digital Isolators With Integrated High-Efficiency, Low-Emissions DC-DC Converter, ISOW784x Datasheet (SLLSEY2)

- 2. Texas Instruments, SN65HVD147x 3.3-V Full-Duplex RS-485 Transceivers With ±16-kV IEC ESD, SN65HVD147x Datasheet (SLLSEJ8)

- 3. Texas Instruments, *Isolated RS-232 With Integrated Signal and Power Reference Design*, TIDA-01230 Design Guide (TIDUCT3)

#### 5.1 商標

All trademarks are the property of their respective owners.

www.tij.co.jp About the Authors

#### 6 About the Authors

**ANAND REGHUNATHAN** is an applications engineer at Texas Instruments, where he is responsible for defining new high-performance products and providing application support on existing products for industrial and automotive markets, specifically for isolation products. Anand brings to the role an experience in EMC testing for both isolation and interface products. Anand earned his bachelor of technology (B.Tech) in electronics and communications engineering from College of Engineering, Trivandrum, India.

**NEERAJ BHARDWAJ** is an applications engineer at Texas Instruments, where he is responsible for defining new high-performance analog products and application support on existing products for industrial and automotive markets. He has a high level of experience in motor drive systems and high-voltage systems with an emphasis in safety applications, standards, test and characterization of mixed signal processors, and EMC cognizant systems design. In his previous role, he led the Systems and Applications team in the Safety and Security Microcontroller Group in TI. He mentors teams on competitive robotics. He has over 20 years of experience in the industry and has worked for TI since 2005. He has a B.E. degree in electrical engineering specialized in high voltage and power electronics from the Government Engineering College Jabalpur and a M.Tech. degree in aerospace engineering specialized in control and guidance from the Indian Institute of Technology Bombay.

改訂履歴 www.tij.co.jp

# 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| 2017年3月発行のものから更新               | Page |

|--------------------------------|------|

| • TIDA-00892ブロック図のインターフェイス名 変更 | 1    |

#### TIの設計情報およびリソースに関する重要な注意事項

Texas Instruments Incorporated ("TI")の技術、アプリケーションその他設計に関する助言、サービスまたは情報は、TI製品を組み込んだアプリケーションを開発する設計者に役立つことを目的として提供するものです。これにはリファレンス設計や、評価モジュールに関係する資料が含まれますが、これらに限られません。以下、これらを総称して「TIリソース」と呼びます。いかなる方法であっても、TIリソースのいずれかをダウンロード、アクセス、または使用した場合、お客様(個人、または会社を代表している場合にはお客様の会社)は、これらのリソースをここに記載された目的にのみ使用し、この注意事項の条項に従うことに合意したものとします。

TIによるTIリソースの提供は、TI製品に対する該当の発行済み保証事項または免責事項を拡張またはいかなる形でも変更するものではなく、これらのTIリソースを提供することによって、TIにはいかなる追加義務も責任も発生しないものとします。TIは、自社のTIリソースに訂正、拡張、改良、およびその他の変更を加える権利を留保します。

お客様は、自らのアプリケーションの設計において、ご自身が独自に分析、評価、判断を行う責任がお客様にあり、お客様のアプリケーション(および、お客様のアプリケーションに使用されるすべてのTI製品)の安全性、および該当するすべての規制、法、その他適用される要件への遵守を保証するすべての責任をお客様のみが負うことを理解し、合意するものとします。お客様は、自身のアプリケーションに関して、(1) 故障による危険な結果を予測し、(2) 障害とその結果を監視し、および、(3) 損害を引き起こす障害の可能性を減らし、適切な対策を行う目的での、安全策を開発し実装するために必要な、すべての技術を保持していることを表明するものとします。お客様は、TI製品を含むアプリケーションを使用または配布する前に、それらのアプリケーション、およびアプリケーションに使用されているTI製品の機能性を完全にテストすることに合意するものとします。TIは、特定のTIリソース用に発行されたドキュメントで明示的に記載されているもの以外のテストを実行していません。

お客様は、個別のTIリソースにつき、当該TIリソースに記載されているTI製品を含むアプリケーションの開発に関連する目的でのみ、使用、コピー、変更することが許可されています。明示的または黙示的を問わず、禁反言の法理その他どのような理由でも、他のTIの知的所有権に対するその他のライセンスは付与されません。また、TIまたは他のいかなる第三者のテクノロジまたは知的所有権についても、いかなるライセンスも付与されるものではありません。付与されないものには、TI製品またはサービスが使用される組み合わせ、機械、プロセスに関連する特許権、著作権、回路配置利用権、その他の知的所有権が含まれますが、これらに限られません。第三者の製品やサービスに関する、またはそれらを参照する情報は、そのような製品またはサービスを利用するライセンスを構成するものではなく、それらに対する関係証または推奨を意味するものでもありません。TIリソースを使用するため、第三者の特許または他の知的所有権に基づく第三者からのライセンス、もしくは、TIの特許または他の知的所有権に基づくTIからのライセンスが必要な場合があります。

TIのリソースは、それに含まれるあらゆる欠陥も含めて、「現状のまま」提供されます。TIは、TIリソースまたはその仕様に関して、明示 的か暗黙的かにかかわらず、他のいかなる保証または表明も行いません。これには、正確性または完全性、権原、続発性の障害に関する保 証、および商品性、特定目的への適合性、第三者の知的所有権の非侵害に対する黙示の保証が含まれますが、これらに限られません。

TIは、いかなる苦情に対しても、お客様への弁護または補償を行う義務はなく、行わないものとします。これには、任意の製品の組み合わせに関連する、またはそれらに基づく侵害の請求も含まれますが、これらに限られず、またその事実についてTIリソースまたは他の場所に記載されているか否かを問わないものとします。いかなる場合も、TIリソースまたはその使用に関連して、またはそれらにより発生した、実際的、直接的、特別、付随的、間接的、懲罰的、偶発的、または、結果的な損害について、そのような損害の可能性についてTIが知らされていたかどうかにかかわらず、TIは責任を負わないものとします。

お客様は、この注意事項の条件および条項に従わなかったために発生した、いかなる損害、コスト、損失、責任からも、TIおよびその代表者を完全に免責するものとします。

この注意事項はTIリソースに適用されます。特定の種類の資料、TI製品、およびサービスの使用および購入については、追加条項が適用されます。これには、半導体製品(http://www.ti.com/sc/docs/stdterms.htm)、評価モジュール、およびサンプル(http://www.ti.com/sc/docs/sampterms.htm)についてのTIの標準条項が含まれますが、これらに限られません。

Copyright © 2018, Texas Instruments Incorporated 日本語版 日本テキサス・インスツルメンツ株式会社