## デザイン・ガイド: TIDA-010047 Si MOSFET 内蔵の 22W/in³、ピーク効率 93.1%、100W USB-PD 3.0 AC/DC アダプタのリファレンス・デザイン

# TEXAS INSTRUMENTS

#### 概要

このテスト済みリファレンス・デザインは、ノート PC アダプタ やスマートフォン用充電器アプリケーション向けの、広い入 力電圧範囲 (100~240VAC) に対応した高効率、高電力 密度の AC/DC アダプタ・ソリューションです。このデザインは、UCC28056 デバイスをベースとするフロント・エンド遷 移モード (TM) 力率補正 (PFC) 回路と、後段にある UCC28780 ベースの絶縁型 DC/DC 変換用アクティブ・クランプ・フライバックとで構成されています。

#### リソース

| TIDA-010047  | デザイン・フォルダ  |

|--------------|------------|

| UCC28056     | プロダクト・フォルダ |

| UCC28780     | プロダクト・フォルダ |

| UCC27712     | プロダクト・フォルダ |

| ATL431       | プロダクト・フォルダ |

| UCC24612     | プロダクト・フォルダ |

| TPS62177     | プロダクト・フォルダ |

| TPS65987D    | プロダクト・フォルダ |

| LMC7111      | プロダクト・フォルダ |

| LP2981-N     | プロダクト・フォルダ |

| TPS7B4250-Q1 | プロダクト・フォルダ |

E2ETMエキスパートに質問

#### 特長

- 比較的低コストのソリューション

- 両端 USB Type-C® ケーブルをベースとするソリューション

- アクティブ・クランプ・フライバック・トポロジによる比較的 高い電力密度

- DoE level VI および CoC Tier2 規制に合致

- 堅牢な保護機能を内蔵

#### アプリケーション

- ノート PC 向け電源アダプタの設計

- モバイル向け充電器の設計

- その他の AC/DC アダプタおよび電源

- 産業用AC/DC

System Description www.tij.co.jp

使用許可、知的財産、その他免責事項は、最終ページにあるIMPORTANT NOTICE (重要な注意事項)をご参照くださいますようお願いいたします。

### 1 System Description

#### 1.1 Key System Specifications

Notebook PCs and smartphones need adapters to charge their batteries. USB Power Delivery (PD) negotiation allows devices to create a contract to deliver the optimum power level for each application under the current battery conditions. This protocol expands USB to deliver up to 100 W (20 V, 5 A) of power. High efficiency and high power density are required for the adapter to save power and make the device easier to carry. A notebook adapter is an AC/DC converter. 🗵 1 shows a typical diagram of this converter. When the output power is higher than 75 W, a power factor correction (PFC) stage is required.

The global regulatory environment surrounding the legislation of external power supply efficiency and noload power draw has rapidly evolved in the last decade. The newer generation power supplies need to meet multiple norms such as the United States Department of Energy (DoE) Level VI standard.

This adapter reference design operates over a wide input voltage range from 100-V to 240-V AC and must be able to power different equipment with different voltage demands automatically. The circuit consists of a front-end transition mode (TM) power factor correction (PFC) circuit, followed by an active-clamp, flyback-based isolated DC/DC power stage. The design uses the UCC28056 controller for the PFC stage and the UCC28780 controller for the ACF stage to achieve a compact and robust control structure. Synchronous rectification based on the UCC24612 helps achieve higher efficiencies. Super junction MOSFETs are used in this design. When faults such as overcurrent, overpower, and overvoltage occur, the adapter reacts quickly to protect the terminal device.

This reference design is a high-efficiency, high power density, 100-W output power AC/DC adapter that achieves a peak efficiency of 93.1% and a 22-W/in³ power density. The input voltage ranges from 100 V to 240 VAC, and the output could be configured as 5-V, 5-A; 9-V, 5-A; 15-V, 5-A; and 20-V, 5-A outputs. When an overcurrent, short-circuit, or over-power event occurs, this adapter reference design can cut off the output and recovery automatically. With overvoltage, the adapter is latched to avoid further damage to the terminal devices. Also, this adapter meets low no-load power consumption, which is less than 140 mW.

This converter operates at a high switching frequency near 200 kHz, which helps decrease the size of the transformer and capacitors. This design is fully tested and validated for various parameters such as regulation, efficiency, output ripple, startup, and switching stresses. Overall, the design meets the key challenges of adapter power supplies to provide safe and reliable power with all protections built in, while delivering high performance with low power consumption

| ax i. Ney System Specifications    |                       |     |               |     |      |  |

|------------------------------------|-----------------------|-----|---------------|-----|------|--|

| PARAMETER                          | Conditions            |     | Specification |     |      |  |

|                                    | Conditions            | Min | Тур           | Max | Unit |  |

| INPUT CHARACTERIST                 | INPUT CHARACTERISTICS |     |               |     |      |  |

| Input voltage (V <sub>INAC</sub> ) | -                     | 100 | 230           | 240 | VAC  |  |

| Frequency (f <sub>LINE</sub> )     | -                     | 47  | 50            | 63  | Hz   |  |

| Brown-in voltage                   | -                     |     | 82            |     | V    |  |

| Brown-out voltage                  | -                     |     | 77            |     | V    |  |

| OUTPUT CHARACTERIS                 | STICS                 | •   | *             |     | •    |  |

表 1. Key System Specifications

System Description www.tij.co.jp

### 表 1. Key System Specifications (continued)

| PARAMETER                     | Conditions                |       | Specification |       | Unit             |

|-------------------------------|---------------------------|-------|---------------|-------|------------------|

| TANAMETER                     | Conditions                | Min   | Тур           | Max   | Unit             |

| Output voltage                | 5-V sink attached         | 4.95  | 5             | 5.05  | V                |

|                               | 9-V sink attached         | 8.91  | 9             | 9.09  | V                |

|                               | 15-V sink attached        | 14.85 | 15            | 15.15 | V                |

|                               | 20-V sink attached        | 19.8  | 20            | 20.2  | V                |

| Output voltage                | 5-V sink attached         |       |               | 5     | А                |

|                               | 9-V sink attached         |       |               | 5     | А                |

|                               | 15-V sink attached        |       |               | 5     | Α                |

|                               | 20-V sink attached        |       |               | 5     | Α                |

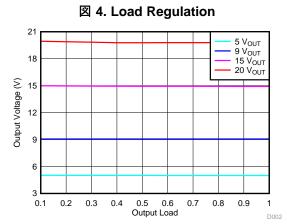

| Load regulation               | 5-V sink attached         |       | 5%            |       | V <sub>OUT</sub> |

|                               | 9-V sink attached         |       | 5%            |       | V <sub>OUT</sub> |

|                               | 15-V sink attached        |       | 5%            |       | V <sub>OUT</sub> |

|                               | 20-V sink attached        |       | 5%            |       | V <sub>OUT</sub> |

| Ripple and noise              | 5-V sink attached         |       | 150           |       | mV               |

|                               | 9-V sink attached         |       | 200           |       | mV               |

|                               | 15-V sink attached        |       | 200           |       | mV               |

|                               | 20-V sink attached        |       | 200           |       | mV               |

| Maximum output power          | For 20 V <sub>OUT</sub>   |       |               | 100   | W                |

| SYSTEM CHARACTERIS            | TICS                      | ı     | -1            |       | Ji               |

| Peak efficiency               | 115 VAC, 60 Hz            |       | 92            |       | %                |

|                               | 230 VAC, 50 Hz            |       | 93.1          |       | %                |

| Operating ambient temperature |                           |       |               | 55    | °C               |

| Board form factor             | Length × Breadth × Height | 95    | 46            | 17    | mm               |

System Overview www.tij.co.jp

#### 2 System Overview

#### 2.1 Block Diagram

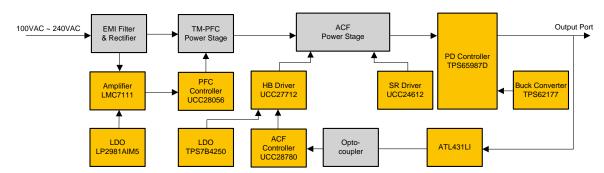

☑ 1 shows the high-level block diagram of the circuit. The circuit consists of a front-end transition mode (TM) power factor correction (PFC) circuit, followed by an active-clamp flyback-based isolated DC/DC power stage. The design uses the UCC28056 controller for the PFC stage and the UCC28780 controller for the ACF stage to achieve a compact and robust control structure. The synchronize rectifier controller UCC24612-1 controls the synchronize rectifier MOSFET for better efficiency performance. The output voltage could be configured as 5-V, 5-A; 9-V, 5-A; 15-V, 5-A; and 20-V, 5-A outputs. The design achieves a peak efficiency of 93.1% at high line input voltage with full load. The power density of the design has been increased to 22 W/in³, which is much higher than traditional solutions.

#### 100VAC ~ 240VAC ACF **Output Port EMI Filter** TM-PFC Power Stage & Rectifier Power Stage PD Controller TPS65987D **PFC** HR Driver SR Driver Ruck Converter Amplifier Controller UCC27712 LMC7111 UCC24612 TPS62177 UCC28056 ACF LDO LDO Opto-Controller ATL431LI LP2981AIM5 TPS7B4250 coupler UCC28780

図 1. TIDA-010047 Block Diagram

### 2.2 Design Considerations

This adapter reference design consists of a front-end transition mode (TM) power factor correction (PFC) circuit, followed by an active-clamp flyback-based isolated DC/DC power stage to achieve high efficiency across universal input voltage condition. This design is fully-compatible USB PD 3.0, and the output voltage could be configured as 5-V, 9-V, 15-V and 20-V based on the end equipment. The high efficiency and high power density are the main focus of this design for targeted applications. More details on the component selection, design equations, and topology descriptions are given in the following section.

### 2.3 Highlighted Products

#### 2.3.1 UCC28056

To implement the high performance, small form factor PFC design at 100-W power, the UCC28056 device is the preferred controller as it offers a series of benefits to address the next generation's need for low total harmonic distortion (THD) norms for desktop PC power supplies. The UCC28056 is a high-performance, 6-pin, fully-featured PFC controller that is small in size and offers excellent light load efficiency and standby power.

www.tij.co.jp System Overview

The UCC28056 simplifies the design of power supply systems requiring good power factor that must also be capable of meeting today's tough standards for efficiency and standby power. At full load, the UCC28056 operates the PFC power stage at maximum switching frequency in transition mode. At reduced load, the part transitions seamlessly into discontinuous conduction mode, automatically reducing switching frequency for maximum efficiency. At light load, DCM operation is combined with burst mode operation to further improve light load efficiency and standby power. The UCC28056 integrates all the features necessary to implement a high performance and robust PFC stage into a 6-pin package and requires a minimal number of external components to interface with the power stage. The UCC28056 maximizes the BOM savings by eliminating need of auxiliary winding.

Key specifications include:

- Innovative DCM control law to prevent valley jumping

- Superior no-load and light-load efficiency

- · Robust protection: fast response 2nd OVP on a dedicated pin

- Soft-start and soft recovery after OVP

- Input voltage brown out detection

- Eliminates need of auxiliary winding

- Innovative DCM control law to prevent valley jumping

- Strong drive capability: -1.0 A and 0.8 A

#### 2.3.2 UCC28780

The UCC28780 is a high-frequency active-clamp flyback controller that enables high-density AC/DC power supplies that comply with stringent global efficiency standards. Zero voltage switching (ZVS) is achieved over a wide operating range with an advanced auto-tuning technique, adaptive dead-time optimization, and variable switching frequency control law. Along with multimode control that changes the operation based on input and output conditions, the UCC28780 controller enables high efficiency without the risk of audible noise. The controller has a variable switching frequency of up to 1 MHz and accurate programmable operating performance points (OPP), which provides consistent thermal design power across a wide line range. This consistent power means passive components can be further reduced and enable high power density.

Key features for this device include:

- Configurable with external Si or GaN FETs

- Adaptive burst control for light-load efficiency with low output ripple and no audible noise

- Secondary-side regulation allows for dynamically scalable output voltage

- · Internal soft start

- Brownout detection without direct line sensing

- Fault protections: internal overtemperature, output overvoltage, overcurrent, short circuit, and pin fault

- NTC resistor interface with external enable

System Overview www.tij.co.jp

#### 2.3.3 UCC24612

The UCC24612 is a high-performance controller and driver for standard and logic-level N-channel MOSFET power devices used for low-voltage, secondary-side synchronous rectification. The combination of controller and MOSFET emulates a near-ideal diode rectifier. This solution not only directly reduces power dissipation of the rectifier, but also indirectly reduces primary-side losses as well due to compounding of efficiency gains. Using drain-to-source voltage sensing, the UCC24612 is ideal for ACF power supplies. This device is available in a 5-pin SOT-23-5 package.

Key features for this device include:

- Up to 1-MHz operating frequency

- VDS MOSFET sensing

- 4-A sink, 1-A source gate-drive capability

- Micro-power sleep current for 90+ designs

- · Automatic light-load management

- Synchronous wake-up from sleep and light-load modes

- · Adaptive minimum off time for better noise immunity

- 16-ns typical turnoff propagation delay

- 9.5-V gate drive clamp levels for minimum driving loss

#### 2.3.4 UCC27712

The UCC27712 is a 620-V, high-side and low-side gate driver with 1.8-A source, 2.8-A sink current, targeted to drive power MOSFETs or IGBTs.

The device consists of one ground-referenced channel (LO) and one floating channel (HO), which is designed for operating with bootstrap or isolated power supplies. The device features fast propagation delays and excellent delay matching between both channels. On the UCC27712 device, each channel is controlled by its respective input pins, HI and LI.

#### 2.3.5 LMC7111

The LMC7111 is a micropower CMOS operational amplifier available in the space-saving SOT-23 package. This makes the LMC7111 ideal for space and weight-critical designs. The wide common-mode input range makes it easy to design battery monitoring circuits which sense signals above the V+ supply. The main benefits of the tiny package are most apparent in small portable electronic devices, such as mobile phones, pagers, and portable computers. The tiny amplifiers can be placed on a board where they are needed, simplifying board layout.

Key features for this device include:

- Tiny 5-pin SOT-23 package saves space

- Very wide common mode input range

- Specified at 2.7 V, 5 V, and 10 V

- Typical supply current 25 μA at 5 V

- 50 kHz gain-bandwidth at 5 V

- Output to within 20 mV of supply rail at 100-kΩ load

- Good capacitive load drive

www.tij.co.jp System Overview

#### 2.3.6 ATL431

The ATL431 is a low-cost three-terminal adjustable shunt regulator with specified thermal stability over applicable automotive, commercial, and industrial temperature ranges. The output voltage can be set to any value between  $V_{REF}$  (approximately 2.5 V) and 36 V with two external resistors. The regulator has a typical output impedance of 0.3  $\Omega$ . The operation current is as low as 100  $\mu$ A (minimum), keeping the power loss at a very low value.

#### 2.3.7 TPS7B4250

The TPS7B4250-Q1 device is a monolithic, integrated low-dropout voltage tracker. The device is available in a SOT-23 package. The TPS7B4250-Q1 device is designed to supply off-board sensors in an automotive environment. The IC has integrated protection for overload, overtemperature, reverse polarity, and output short-circuit to the battery and ground.

A reference voltage applied at the adjust-input pin, ADJ, regulates supply voltages up to  $V_{IN} = 45 \text{ V}$  with high accuracy and loads up to 50 mA.

By setting the adjust and enable input pin, ADJ/EN, to low, the TPS7B4250-Q1 device switches to standby mode which reduces the quiescent current to the minimum value.

Key features for this device include:

- –20-V to 45-V wide, maximum input voltage range

- Input voltage range 4.75 V to 28 V

- · Output current, 50 mA

- Very-low output-tracking tolerance, 5 mV (max)

- 150-mV low dropout voltage when I<sub>OUT</sub> = 10 mA

- Combined reference and enable input

- 40-µA low quiescent current at light load

- Reverse polarity protection

- Overtemperature protection

- Output short-circuit proof to ground and supply

- Undervoltage lockout

- Short-circuit protection

- · Overtemperature protection

- SOT-23 package

#### 2.3.8 LP2981-N

The LP2981-N families of fixed-output, low-dropout regulators offer exceptional, cost-effective performance for both portable and non-portable applications. Available in fixed voltages of 2.8 V, 3 V, 3.3 V, and 5 V, the family has an output tolerance of 0.75% for the A-grade devices and is capable of delivering 100-mA continuous load current. Standard regulator features, such as overcurrent and overtemperature protection, are included.

The LP2981-N have features that make the regulators ideal candidates for a variety of portable applications:

Low dropout: A PNP pass element allows a typical dropout of 200 mV at 100-mA load current and 7

System Overview www.tij.co.jp

mV at 1-mA load.

- Low quiescent current: The use of a vertical PNP process allows for quiescent currents that are considerably lower than those associated with traditional lateral PNP regulators.

- Shutdown: A shutdown feature is available, allowing the regulator to consume only 0.01 μA when the ON/OFF pin is pulled low.

Key features for this device include:

- Output tolerance of 0.75% (A grade) 1.25% (standard grade)

- Ultra-low dropout typically: 200 mV at full load of 100 mA, 7 mV at 1 mA

- Low I<sub>Q</sub>: 600 μA typical at full load of 100 mA

- Shutdown current: 0.01 μA typical

- Fast transient response to line and load

- Overcurrent and thermal protection

- · High peak current capability

- Low Z<sub>OUT</sub> over a wide frequency range

- -40°C to 125°C temperature range

- SOT-23 package

#### 2.3.9 TPS62177

The TPS62177 is a high efficiency synchronous step down DC/DC converter, based on the DCS-Control™ topology.

With a wide operating input voltage range of 4.75 V to 28 V, the device is ideally suited for systems powered from multi-cell Li-lon as well as 12 V and even higher intermediate supply rails, providing up to 500-mA output current.

The TPS62177 automatically enters power save mode at light loads, to maintain high efficiency across the whole load range. As well, it features a sleep mode to supply applications with advanced power save modes like ultra-low power micro controllers. The power good output may be used for power sequencing, or power on reset, or both.

The device features a typical quiescent current of 22  $\mu$ A in normal mode and 4.8  $\mu$ A in sleep mode. In sleep mode, the efficiency at very low load currents can be increased by as much as 20%. In shutdown mode, the shutdown current is less than 2  $\mu$ A and the output is actively discharged.

Key features for this device include:

- DCS-Control<sup>™</sup> topology

- Input voltage range 4.75 V to 28 V

- Quiescent current typically 4.8 μA (sleep mode)

- 100% duty cycle mode

- Active output discharge

- Power Good output

- Output current of 500 mA

- Output voltage range 1 VDC to 6 V

www.tij.co.jp System Overview

- Switching frequency of typically 1 MHz

- Seamless Power Save Mode transition

- Undervoltage lockout

- · Short-circuit protection

- Overtemperature protection

- Available in 2-mm x 3-mm 10-pin WSON package

#### 2.3.10 TPS65987

The TPS65987D is a stand-alone USB Type-C and Power Delivery (PD) controller providing cable plug and orientation detection for a single USB Type-C connector. Upon cable detection, the TPS65987D communicates on the CC wire using the USB PD protocol. When cable detection and USB PD negotiation are complete, the TPS65987D enables the appropriate power path and configures alternate mode settings for external multiplexers. The TPS65987D is fully configurable to fit in many different applications. In this design, the TPS65987D is included to highlight the support of a Texas Instruments Power Duo mode. Power Duo mode allows for the TPS65987D to close both of its power paths in parallel when operating as either a source or a sink. When this mode has been enabled, the effective R<sub>DS(on)</sub> of the TPS65987D is decreased by a factor of 2. Additionally, the current-carrying capability is doubled.

The TPS65987D device is the heart of this design and is used to control the LM3489 output voltage, the  $V_{BUS}$  negotiation,  $V_{BUS}$  voltage selection, *PD Alternate Mode* negotiation, and  $V_{BUS}$  overcurrent protection.

#### 2.4 System Design Theory

This reference design provides universal AC mains powered by 100-W output at 20 V and 5 A. The UCC28056 controls a PFC boost front end, while the UCC28780 active-clamp flyback converts the PFC output to an isolated 20 V and 5 A. The peak system efficiency is 93.1% with a 230-VAC input at full load. In addition, several protections are embedded into this design which includes input undervoltage protection and output short-circuit protection.

Low EMI, high efficiency, high power factor and reliable power supply are the main focus of this design for targeted applications.

#### 2.4.1 PFC Regulator Stage Design

Power factor correction (PFC) circuit shapes the input current of the power supply to maximize the real power available from the mains. In addition, it is important to have the PFC circuit comply with low total harmonic distortion (THD) regulatory requirements such as IEC61000-3-2. Currently, two modes of operation have been widely utilized for PFC implementations. For higher power circuits (> 300 W), the topology of choice is the boost converter operating in continuous conduction mode (CCM) and with average current mode control. For lower power applications (< 250 W), typically the transition mode (TM) or critical conduction mode (CrCM) boost topology is used.

For low power levels such as 100 W, TI recommends using the TM operation as it offers inherent zerocurrent switching of the boost diodes with no reverse-recovery losses, which permits the use of less expensive diodes without sacrificing efficiency. In addition, variable frequency operation results in distributed EMI spectrum and low emissions.

The design process and component selection for this design are illustrated in the following sections.

System Overview www.tij.co.jp

### 2.4.1.1 Circuit Component Design - Design Goal Parameters

表 2 lists the design goal parameters for a PFC converter design. These parameters are used in further calculations for selection of components.

| PARAMETER                          | CONDITIONS |     | SPECIFICATION |     |       |

|------------------------------------|------------|-----|---------------|-----|-------|

| PARAIVIETER                        | CONDITIONS | MIN | TYP           | MAX | UNITS |

| INPUT CHARACTERISTICS              | 3          |     | ,             |     | •     |

| Input Voltage (V <sub>INAC</sub> ) |            | 100 | 230           | 240 | VAC   |

| Frequency ( <sub>fLINE</sub> )     |            | 47  | 50            | 63  | Hz    |

| Brown-in voltage                   |            |     | 82            |     | V     |

| Brown-out voltage                  |            |     | 77            |     | V     |

| OUTPUT CHARACTERISTI               | ics        |     |               |     |       |

| Output voltage                     |            |     | 390           |     | V     |

| Maximum output power               |            |     |               | 100 | W     |

| Efficiency                         |            |     | 97.5          |     | %     |

| Minimum switching frequency        |            | 45  |               |     | kHz   |

| Line regulation                    |            |     | 1             |     | %     |

| Load regulation                    |            |     | 1             |     | %     |

表 2. Design Goal Parameters for PFC Converter

#### 2.4.1.2 Input Current Calculations and Fuse Selection

The input fuse and bridge rectifier are selected based upon the input current calculations. The boost voltage is designed to regulate at 390-VDC for an input AC voltage range of 85- to 265-VAC operation. The boost PFC converter is designed for output power of 110 W, considering the downstream DC/DC converter operating at more than 96% efficiency.

Determine PIN, the maximum input power averaged over the AC line period using 式 1.

$$P_{IN} = \frac{P_{DCBUS}}{\pi_{PFC}} = \frac{110}{0.975} = 112.8 \text{ W}$$

(1)

Determine the maximum average output current using 式 2.

$$I_{DCBUS(max)} = \frac{P_{DCBUS}}{V_{DCBUS(min)}} = \frac{110 \text{ W}}{390 \text{ VDC}} = 0.282 \text{ A}$$

(2)

Determine the maximum RMS input current using 式 3.

$$I_{IN\_RMS(max)} = \frac{P_{DCBUS}}{\pi_{PFC} \times V_{IN(min)} \times PF} = \frac{110 \text{ W}}{0.975 \times 85 \text{ VAC} \times 0.99} 1.34 \text{ A}$$

(3)

Determine the maximum input current  $(I_{IN(max)})$ , and the maximum average input current,  $(I_{IN\_AVG(max)})$  based on the calculated RMS value, assuming the waveform is sinusoidal using  $\pm 4$  and  $\pm 5$ , respectively.

$$I_{IN(max)} = \sqrt{2} \times I_{IN_{RMS(max)}} = \sqrt{2} \times 1.34 = 1.895 \text{ A}$$

(4)

$$I_{IN\_AVG(max)} = \frac{2}{\pi} \times I_{RMS(max)} = \frac{2}{\pi} \times 1.895 = 1.1 \text{ A}$$

(5)

www.tij.co.jp System Overview

#### 2.4.1.3 Boost Inductor Design

For detailed derivation of equations, see the *Detailed Design Procedure* section of the *UCC28056 6-pin single-phase transition-mode PFC controller data sheet*. Only the final equations are used to calculate the following values. The boost inductance value required to ensure that maximum load can be delivered from minimum line voltage may be expressed using  $\vec{x}$  6.

$$I_{PFCO} = \frac{V_{LinRMSMin}^2}{110\% \times P_{LdMax}} \times \frac{T_{ONMAX0}}{2} = 382 \,\mu\text{H}$$

(6)

Considering the inductor manufacture tolerance,  $L_{PFC} = 340 \mu F$

Maximum current in the power components will flow while delivering maximum load when supplied from minimum line voltage. In this condition, the UCC28056 always operates in transition mode (CRM).

Maximum boost inductor RMS current occurs at minimum line voltage and maximum input power.

$$I_{LPFCRMSMax} = \frac{2}{\sqrt{3}} \times \frac{110\% \times P_{LdMax}}{V_{LinRMSMin}} = 1.644 \text{ A}$$

(7)

Based on the inductor requirements in  $\pm$  7, a custom magnetic is designed: 340- $\mu$ H and 5.4-A saturation current.

#### 2.4.1.4 Boost Switch Selection

For detailed derivation of equations, see the *Detailed Design Procedure* section of the *UCC28056 6-pin single-phase transition-mode PFC controller data sheet.* Only the final equations are used to calculate the following values.

Maximum RMS current in the switch occurs at maximum load and minimum line voltage.

$$I_{MosRMSMax} = \frac{110\% \times P_{LdMax}}{V_{LinRMSMin}} \times \sqrt{\frac{4}{3} - \frac{32 \times \sqrt{2} \times V_{I\eta RMSMin}}{9 \times \pi \times V_{OUT}}} = 1.412 \text{ A}$$

(8)

MOSFET selection for the Boost switch can now be done under the following conditions:

- The voltage rating must be greater than the maximum output voltage. Under transient or line surge

testing, the output voltage may rise well above its normal regulation level. For this design example, a

MOSFET voltage rating of 600 V is chosen to support a regulated output voltage of 390 V.

- Based on an acceptable level of conduction loss in the MOSFET, the  $R_{DS(on)}$  value required can be calculated from the maximum RMS current. For this example, design an SiHH120N60E MOSFET, from Vishay was selected with  $R_{DS(on)}$  at 25°C = 0.12  $\Omega$ .

- For best efficiency, use a MOSFET that incorporates a fast body diode. Operating with discontinuous inductor current (DCM) from a low input voltage will incur additional switching power loss if a MOSFET with slow body diode is used.

#### 2.4.1.5 Boost Diode Selection

For detailed derivation of equations, see the *Detailed Design Procedure* section of the *UCC28056 6-pin single-phase transition-mode PFC controller data sheet.* Only the final equations are used to calculate the following values.

The maximum RMS current in the Boost diode occurs at maximum load and minimum line.

$$I_{DioRMSMax} = \frac{4}{3} \times \frac{110\% \times P_{LdMax}}{V_{LinRMSMin}} \times \sqrt{\frac{2 \times \sqrt{2} \times V_{LinRMS}}{\pi \times V_{OUT}}} = 0.841 \, A \tag{9}$$

System Overview www.tij.co.jp

Conduction power loss in the Boost diode is primarily a function of the average output current.

$$I_{DioAVGMax} = \frac{P_{LdMax}}{V_{OUT}} = 0.282 \text{ A}$$

(10)

Boost diode selection can now be made under the following conditions:

- The Boost diode requires the same voltage rating as the Boost MOSFET switch.

- The Boost diode must have average and RMS current ratings that are higher than the previous numbers calculated.

- Diodes are available with a range of different speed and recovery charge. Fast diodes, with low

reverse recovery charge, typically have higher forward voltage drop. Fast diodes will therefore have

higher conduction loss but lower switching loss. Slow diodes, with high reverse recovery charge,

typically have lower forward voltage drop. Slow diodes will therefore have lower conduction loss but

higher switching loss. Maximum efficiency is achieved when the diode speed rating matches the

application.

For this design, the MURS360 diode from Onsemi was selected. This diode has a voltage rating of 600 V and an average current rating of 4 A. This design has a forward-voltage drop of around 0.85 V giving a conduction loss in the Boost diode of less than 0.24 W.

#### 2.4.1.6 Output Capacitor Selection

The hold-up time is the main requirement in determining the output capacitance. ESR and the maximum RMS ripple current rating are also important, especially at higher power levels.

$$C_{OUT(min)} \ge \frac{2 \times P_{DCBUS} \times t_{holdup}}{\left(V_{DCBUS}^2 - V_{holdup}^2\right)}$$

(11)

The system needs to have 10 ms back-up for 80% of load (80 W).

The hold-up voltage is considered as 127 V for continuous operation of downstream DC/DC converter.

$$V_{holdup} = 127 V$$

$$C_{OUT(min)} \ge \frac{2 \times 80 \text{ W} \times 10 \text{ ms}}{\left(390^2 - 127^2\right)} = 29.4 \,\mu\text{F}$$

(12)

The actual value used in the design is a 68-μF, 20%, 450-V capacitor.

#### 2.4.1.7 Output Voltage Set Point

Select the divider ratio of  $R_{FBtop}$  and  $R_{FBbottom}$  to set the  $V_{REF}$  voltage to 2.5 V at the desired output voltage. The current through the divider is reduced to the minimum to keep the no-load power loss as small as possible. Consider the pullup resistor  $R_{FBtop}$  to be 10.052  $M\Omega$ .

Using the internal 2.5-V reference,  $V_{REF}$ , the bottom divider resistor,  $R_{FBbottom}$ , is selected to meet the output voltage design goals.

$$R_{FBbottom} = \frac{V_{REF} \times R_{FBtop}}{V_{OUT} - V_{REF}}$$

(13)

$$R_{FB2} = \frac{2.5 \times 10.052 \,\text{M}\Omega}{390 - 2.5} = 64.9 \,\text{k}\Omega \tag{14}$$

A standard value 64.9-k $\Omega$  resistor for R<sub>FB2</sub> results in a nominal output voltage set point of 390 V.

www.tij.co.jp System Overview

A small capacitor on the VOSNS pin must be added to filter out noise. Limit the value of the filter capacitor such that the RC time constant is limited to approximately 100 µs so as not to significantly reduce the control response time to output voltage deviations.

$$C_{VOSNS} = \frac{150 \text{ u}}{R_{FBbottom}} = 2313 \text{ pH}$$

(15)

The closest standard value of 2200 pF was used on the VOSNS pin.

#### 2.4.2 **ACF Converter Stage Design**

ACF is a two-switch topology that achieves soft switching and recovers leakage inductance energy. Compared with traditional ACF in continuous conduction mode (CCM), ACF in critical conduction mode (CrCM) uses the magnetizing inductance instead of leakage inductance to store ZVS energy. As magnetizing inductance is much larger than leakage inductance, only a small amount of negative magnetizing current is required to achieve full ZVS soft switching. By controlling the amount of negative magnetizing current, ZVS can easily be achieved from zero to full load. With proper design, the output rectifier achieves zero current switching (ZCS) during turnoff. All of these features make ACF successful at high power density and efficiency adapter applications. 表 3 details the ACF converter design goal parameters.

| PARAMETER             | CONDITIONS                                 | SPECIFICATION |      |     | UNITS |

|-----------------------|--------------------------------------------|---------------|------|-----|-------|

|                       | CONDITIONS                                 | MIN           | TYP  | MAX | UNITS |

| INPUT CHARACTERISTICS |                                            | ,             |      |     | '     |

| Input Voltage         | V <sub>INDC</sub>                          | 127           | -    | 400 | V     |

| Line frequency        |                                            | 47            | 50   | 63  | Hz    |

| OUTPUT CHARACTERISTIC | CS                                         |               |      |     |       |

| Output Voltage        |                                            | 5             |      | 20  | V     |

| Maximum Output Power  |                                            |               |      | 100 | W     |

| Efficiency            | 20 V <sub>OUT</sub> at 230 V <sub>AC</sub> |               | 93.1 |     | %     |

| Line regulation       |                                            | -             | 1    | -   | %     |

| Load regulation       |                                            | -             | 5    | -   | %     |

表 3. Design Goal Parameters for ACF Converter

#### 2.4.2.1 Transformer Turns Ratio Calculation

The transformer that turns ratio is determined by the voltage rating of the Primary high-side and low-side MOSFET and synchronous rectification MOSFET. The voltage stress of the IPL60R285P7 is 650 V and the SR MOSFET is a 150-V Si device. Therefore, the maximum and minimum turns ratio can be calculated separately using 式 16 and 式 17, respectively.

$$N_{PS\_max} = \frac{(1 - K_{dera}) \times V_{DS\_GaN} - V_{BULK\_max}}{V_{OUT\_max}} = 6$$

where

- K<sub>dera</sub> is the GaN voltage derating

- V<sub>DS GaN</sub> is the maximum GaN drain-to-source voltage rating

- V<sub>BULK\_max</sub> is the maximum bulk voltage

- V<sub>OUT max</sub> is the maximum output voltage (16)

$$N_{PS\_min} = \frac{V_{BULK\_max}}{\left(1 - K_{dera}\right) \times V_{DS\_SR} - V_{OUT\_max} - Vspike} = 4.7$$

System Overview www.tij.co.jp

where

$V_{\text{DS\_SR}}$  is the SR MOSFET drain-to-source voltage rating

A larger turns ratio means a larger main switch duty cycle and smaller secondary RMS current. In this reference design, the turns ratio is designed as 5.4 to maintain the minimum secondary RMS current, which does better to the efficiency and thermal.

#### 2.4.2.2 Primary Magnetic Inductance Calculation

After NPS is chosen, the primary magnetic inductance (Lm) can be determined based on the minimum switching frequency (f<sub>SW min</sub>) at the minimum bulk voltage (V<sub>BULK min</sub>), maximum duty cycle (D<sub>max</sub>), and maximum output power (POUT max). When selecting the minimum switching, consider the impact on full-load efficiency and EMI filter design.

Calculate the maximum duty cycle and primary inductance using 式 18 and 式 19.

$$D_{max} = \frac{N_{PS} \times V_{OUT\_max}}{V_{BULK\_min} - N_{PS} \times V_{OUT\_max}} = 0.44$$

(18)

$$L_{m} = \frac{D_{max}^{2} \times V_{BULK\_min}^{2} \times \eta}{2 \times f_{SW\_min} \times P_{OUT\_max}}$$

(19)

Finally, a custom magnetic is designed: 110-µH and 7.4-A saturation current.

#### 2.4.2.3 Auxiliary-to-Secondary Turns Ratio Design

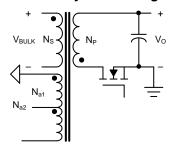

The UCC28780 and both MOSFETs devices are all powered by auxiliary winding at run mode. Two windings are designed to make sure that V<sub>DD</sub> will not be lower than the turnoff voltage and to minimize the power consumption. 2 shows the auxiliary power diagram.

#### 図 2. Auxiliary Power Diagram

The N<sub>a1</sub> winding is designed to power the devices at 5-V and 9-V outputs. Considering the voltage derating at a light load, there should be enough margin on  $V_{DD \ min}$ . Then at a 9-V output, the  $V_{DD}$  is equal to the TVS diode voltage of 16 V. N<sub>a1</sub> must stay a small value to decrease the power consumption on the transistor.

The N<sub>a2</sub> winding is designed to power the devices at 15-V and 20-V outputs. Calculate the auxiliary-tosecondary turns ratio using 式 20 and 式 21.

$$\frac{N_{a1\_min}}{N_S} = \frac{1.5 \times V_{DD\_min}}{5} = 3.3$$

(20)

$$\frac{N_{a2\_min}}{N_S} = \frac{1.5 \times V_{DD\_min}}{15} = 1.1 \tag{21}$$

www.tij.co.jp System Overview

#### 2.4.2.4 Clamp Capacitor Calculation

Consider the design trade-off between conduction loss reduction and turnoff switching loss of the high-side switching device (QH). A higher clamp capacitor ( $C_{\text{clamp}}$ ) results in less RMS current flowing through the transformer windings and switching devices; therefore, the conduction loss can be reduced. However, a higher  $C_{\text{clamp}}$  design results in QH turning off before the clamp current returns to zero. The condition of non-ZCS increases the turnoff switching loss of QH. Therefore,  $C_{\text{clamp}}$  needs to be fine-tuned based on the loss attribution. For best results, design the resonance between leakage inductance ( $L_k$ ) and  $C_{\text{clamp}}$  to be completed by the time between resonant current is zero and QH is turned off. In this setup, the demagnetization time must be equal to around three quarters of the resonant period. Use  $\vec{\pm}$  22,  $\vec{\pm}$  23, and  $\vec{\pm}$  24 to design  $C_{\text{clamp}}$  for obtaining ZCS at a minimum bulk voltage, minimum output voltage, and full load. A low-ESR clamp capacitor is required to minimize the conduction loss.

$$C_{clamp\_max} = \frac{1}{L_k} \times \left( \frac{L_k \times I_{m+}}{1.5\pi \times N_{PS} \times V_{OUT\_min}} \right)^2$$

(22)

$$i_{m+} = \sqrt{\frac{2 \times P_{OUT\_max}}{\eta \times L_m \times f_{SW\_min}}} + i_{m-}^{2}$$

(23)

$$i_{m-} = \sqrt{\frac{C_{SW}}{L_m}} \times V_{BULK\_min}$$

(24)

#### 2.4.2.5 Bleed Resistor Calculation

A large bleed resistor ( $R_{Bleed}$ ) is used to discharge clamp capacitor voltage to a residual voltage ( $V_{residual}$ ) during the 1.44-s fault delay recovery time ( $t_{FDR}$ ). After the converter recovers from the fault mode, the lower  $V_{residual}$  reduces the maximum current flowing through QH and SR within their respective safe operating areas, even if the output voltage is shorted. The target  $V_{residual}$  can be calculated based on the maximum pulse current of QH or the SR current reflected to the primary side, depending on which is lower.

$$R_{Bleed} = \frac{t_{FDR}}{C_{clamp} \times In \left(\frac{N_{PS} \times V_{OUT\_max}}{V_{residual}}\right)}$$

(25)

#### 2.4.2.6 Output Capacitor Calculation

Output capacitance (C<sub>OUT</sub>) is determined by evaluating several factors and choosing the largest of the results.

- The minimum output capacitor value must be enough to meet transient specification of output voltage due to a given load step until the voltage-control loop can respond to restore regulation.

- where

- $\Delta I_{load}$  is maximum load-step magnitude for transient response

- ΔV<sub>trans\_max</sub> is the maximum transient voltage deviation for transient response

- Δt<sub>trans</sub> is the transient response time

- The maximum ESR of the output capacitor is often limited by the maximum output peak-to-peak voltage ripple (V<sub>pk-pk</sub>), where the worst-case output ripple is considered at maximum load (I<sub>OUT\_max</sub>). If the high-frequency switching ripple at the output is mainly dominated by the ESR ripple, a sinusoidal approximation of the secondary current waveform of the ACF is made to calculate the ESR requirement based on the target output ripple specification.

System Overview www.tij.co.jp

$$V_{residual} = min(i_{max\_QH}, i_{max\_SR}) \times \sqrt{\frac{L_k}{C_{clamp}}}$$

(26)

$$C_{OUT\_min} = \frac{\Delta_{load} \times \Delta t_{trans}}{\Delta V_{trans\_max}}$$

(27)

$$R_{CO\_max} = \frac{2 \times \left(1 - D_{max} - f_{SW\_min} \times \pi \times \sqrt{L_k \times C_{SW}}\right) \times V_{pk-pk}}{\pi \times I_{OUT\_max}}$$

(28)

### 3 Hardware, Software, Testing Requirements, and Test Results

#### 3.1 Required Hardware and Software

#### 3.1.1 Hardware

The following hardware is required for this reference design:

- Isolated AC source

- Single-phase power analyzer

- Digital oscilloscope

- Multimeters

- Electronic load

#### 3.2 Testing and Results

#### 3.2.1 Test Setup

Instructions to set up the test equipment follow:

- 1. Connect input terminals of the reference board to the AC power source.

- 2. Connect output terminals to the PMP20413 input terminals.

- 3. Connect the PMP20413 output terminals to electronic load, maintaining correct polarity.

- 4. Set a minimum load of about 0 A and minimum voltage of 25 V.

- 5. Gradually increase the input voltage from 0 V to turn on voltage of 84-V AC.

- 6. Observe that the output voltage across the load terminals has risen to about 5 V.

- 7. Increase the load to maximum load smoothly and observe the switching waveforms.

- 8. Select different output voltages through the PMP20413 device.

- 9. Increase the load to maximum load smoothly and observe the switching waveforms.

- 10. Compare these results with those presented in this design guide.

#### 3.2.2 **Test Results**

#### 3.2.2.1 Efficiency Performance

表 4 through 表 11 list the efficiency data of the different voltages.

表 4.5 V at 115-V AC, 60 Hz

| OUTPUT VOLTAGE (V) | OUTPUT CURRENT (A) | INPUT POWER (W) | EFFICIENCY (%) |

|--------------------|--------------------|-----------------|----------------|

| 5.03               | 0.5                | 3.03            | 83.00          |

| 5.014              | 1                  | 5.94            | 84.41          |

| 5.013              | 1.25               | 7.2             | 87.03          |

| 5.014              | 1.5                | 8.5             | 88.48          |

| 5.014              | 2                  | 11.2            | 89.54          |

| 5.014              | 2.5                | 13.8            | 90.83          |

| 5                  | 3                  | 16.6            | 90.36          |

| 5                  | 3.5                | 19.4            | 90.21          |

| 5                  | 3.75               | 20.8            | 90.14          |

| 5                  | 4                  | 22.2            | 90.09          |

| 5                  | 4.5                | 25.1            | 89.64          |

| 5                  | 5                  | 27.9            | 89.61          |

表 5. 5 V at 230-V AC, 50 Hz

| OUTPUT VOLTAGE (V) | OUTPUT CURRENT (A) | INPUT POWER (W) | EFFICIENCY (%) |

|--------------------|--------------------|-----------------|----------------|

| 5.03               | 0.5                | 3.6             | 69.86          |

| 5.014              | 1                  | 6.6             | 75.97          |

| 5.013              | 1.25               | 7.9             | 79.32          |

| 5.005              | 1.5                | 9.2             | 81.6           |

| 5.005              | 2                  | 11.4            | 87.81          |

| 5.005              | 2.5                | 14.1            | 88.74          |

| 4.99               | 3                  | 16.7            | 89.64          |

| 4.99               | 3.5                | 19.4            | 90.03          |

| 4.99               | 3.75               | 20.8            | 89.96          |

| 4.99               | 4                  | 22.1            | 90.32          |

| 4.99               | 4.5                | 24.9            | 90.18          |

| 4.99               | 5                  | 27.7            | 90.07          |

### 表 6.9 V at 115-V AC, 60 Hz

| OUTPUT VOLTAGE (V) | OUTPUT CURRENT (A) | INPUT POWER (W) | EFFICIENCY (%) |

|--------------------|--------------------|-----------------|----------------|

| 9.06               | 0.5                | 5.55            | 81.62          |

| 9.06               | 1                  | 10.5            | 86.29          |

| 9.06               | 1.25               | 12.9            | 87.79          |

| 9.06               | 1.5                | 15.3            | 88.82          |

| 9.06               | 2                  | 20              | 90.60          |

| 9.06               | 2.5                | 24.8            | 91.33          |

| 9.06               | 3                  | 29.7            | 91.52          |

| 9.06               | 3.5                | 34.6            | 91.65          |

| 9.06               | 3.75               | 37              | 91.82          |

| 9.06               | 4                  | 39.5            | 91.75          |

| 9.06               | 4.5                | 44.5            | 91.62          |

| 9.06               | 5                  | 49.5            | 91.52          |

表 7.9 V at 230-V AC, 50 Hz

| OUTPUT VOLTAGE (V) | OUTPUT CURRENT (A) | INPUT POWER (W) | EFFICIENCY (%) |

|--------------------|--------------------|-----------------|----------------|

| 9.04               | 0.5                | 6               | 75.33          |

| 9.06               | 1                  | 10.9            | 83.12          |

| 9.05               | 1.25               | 13.3            | 85.06          |

| 9.05               | 1.5                | 15.6            | 87.02          |

| 9.05               | 2                  | 20.3            | 89.16          |

| 9.05               | 2.5                | 25              | 90.50          |

| 9.05               | 3                  | 29.7            | 91.41          |

| 9.05               | 3.5                | 34.5            | 91.81          |

| 9.05               | 3.75               | 36.9            | 91.97          |

| 9.05               | 4                  | 39.3            | 92.11          |

| 9.05               | 4.5                | 44.2            | 92.14          |

| 9.05               | 5                  | 49              | 92.35          |

### 表 8. 15 V at 115-V AC, 60 Hz

| OUTPUT VOLTAGE (V) | OUTPUT CURRENT (A) | INPUT POWER (W) | EFFICIENCY (%) |

|--------------------|--------------------|-----------------|----------------|

| 14.99              | 0.5                | 10.08           | 74.36          |

| 14.97              | 1                  | 18.29           | 81.85          |

| 14.96              | 1.24               | 22.54           | 82.30          |

| 14.95              | 1.5                | 26.68           | 84.05          |

| 14.94              | 2                  | 34.04           | 87.78          |

| 14.93              | 2.5                | 41.93           | 89.02          |

| 14.93              | 3                  | 49.68           | 90.16          |

| 14.93              | 3.5                | 57.5            | 90.88          |

| 14.92              | 3.75               | 61.4            | 91.12          |

| 14.92              | 4                  | 65.32           | 91.37          |

| 14.91              | 4.5                | 73.22           | 91.63          |

| 14.92              | 5                  | 81.24           | 91.83          |

表 9. 15 V at 230-V AC, 50 Hz

| OUTPUT VOLTAGE (V) | OUTPUT CURRENT (A) | INPUT POWER (W) | EFFICIENCY (%) |

|--------------------|--------------------|-----------------|----------------|

| 14.98              | 0.5                | 9.98            | 75.05          |

| 14.97              | 1                  | 18.16           | 82.43          |

| 14.96              | 1.24               | 22.34           | 83.04          |

| 14.95              | 1.5                | 26.42           | 84.88          |

| 14.94              | 2                  | 33.32           | 89.68          |

| 14.93              | 2.5                | 41.54           | 89.85          |

| 14.93              | 3                  | 49.4            | 90.67          |

| 14.93              | 3.5                | 57.1            | 91.51          |

| 14.92              | 3.75               | 61              | 91.72          |

| 14.92              | 4                  | 64.9            | 91.96          |

| 14.92              | 4.5                | 72.7            | 92.35          |

| 14.92              | 5                  | 80.6            | 92.56          |

### 表 10. 20 V at 115-V AC, 60 HZ

| OUTPUT VOLTAGE (V) | OUTPUT CURRENT (A) | INPUT POWER (W) | EFFICIENCY (%) |

|--------------------|--------------------|-----------------|----------------|

| 19.95              | 0.5                | 12.81           | 77.87          |

| 19.89              | 1                  | 23.92           | 83.15          |

| 19.87              | 1.25               | 29.46           | 84.31          |

| 19.84              | 1.5                | 34.68           | 85.81          |

| 19.78              | 2                  | 44.8            | 88.30          |

| 19.78              | 2.5                | 55.12           | 89.71          |

| 19.79              | 3                  | 65.47           | 90.68          |

| 19.79              | 3.5                | 75.89           | 91.27          |

| 19.79              | 3.75               | 81.06           | 91.55          |

| 19.79              | 4                  | 86.3            | 91.73          |

| 19.79              | 4.5                | 96.8            | 92.00          |

| 19.79              | 5                  | 107.4           | 92.13          |

表 11. 20 V at 230-V AC, 50 Hz

| OUTPUT VOLTAGE (V) | OUTPUT CURRENT (A) | INPUT POWER (W) | EFFICIENCY (%) |

|--------------------|--------------------|-----------------|----------------|

| 19.95              | 0.5                | 12.65           | 78.85          |

| 19.89              | 1                  | 23.71           | 83.89          |

| 19.87              | 1.25               | 29.16           | 85.18          |

| 19.83              | 1.5                | 33.9            | 87.74          |

| 19.77              | 2                  | 44.4            | 89.05          |

| 19.79              | 2.5                | 54.7            | 90.45          |

| 19.79              | 3                  | 65              | 91.34          |

| 19.79              | 3.5                | 75.3            | 91.99          |

| 19.79              | 3.75               | 80.45           | 92.25          |

| 19.78              | 4                  | 85.6            | 92.43          |

| 19.78              | 4.5                | 95.9            | 92.82          |

| 19.78              | 5                  | 106.2           | 93.13          |

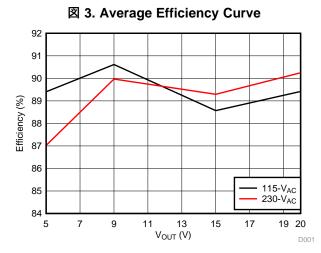

3 shows the efficiency curves.

#### 3.2.2.2 Load Regulation

**Output Voltage Transitions**

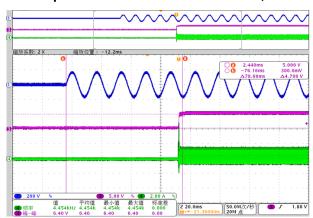

#### 3.2.2.3.1 Start-up

3.2.2.3

注: CH1: Input Voltage; CH3: Output Voltage; CH4: Transformer Primary Current

図 5. Start-up Waveform at 115-V AC and 5-V, 5-A Output

#### 3.2.2.3.2 Internal Waveform

#### 3.2.2.3.2.1 PFC Stage Switching Waveforms

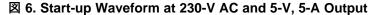

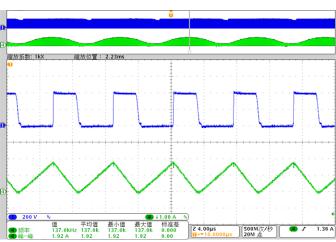

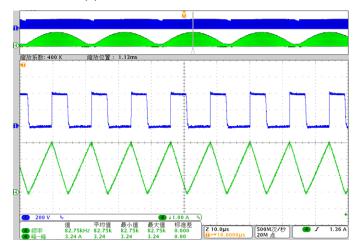

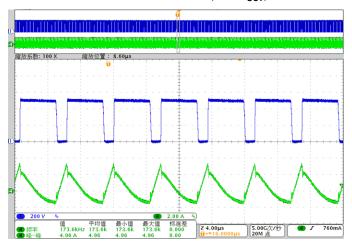

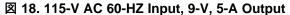

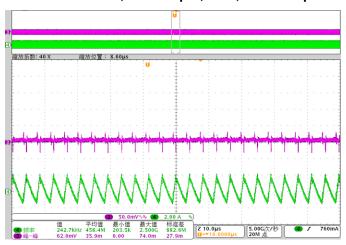

This section shows the PFC stage switching waveforms at input voltage 115 VAC and 230 VAC at different load conditions

注: CH1: PFC Switch Node Voltage; CH4: PFC Inductor Current

図 8. PFC-115 VAC at Full-load

#### 図 9. SW-PFC-230 VAC at Half-load

#### 図 10. SW-PFC-230 VAC at Full-load

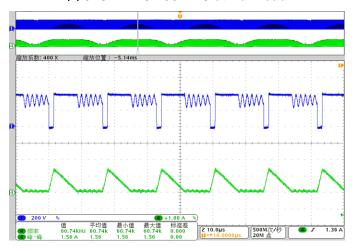

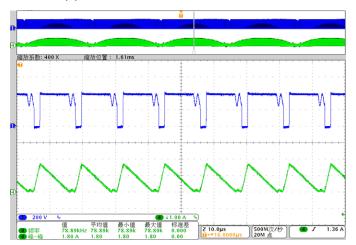

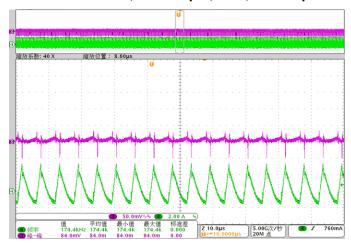

#### 3.2.2.3.2.2 ACF Stage Switching Waveforms

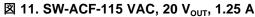

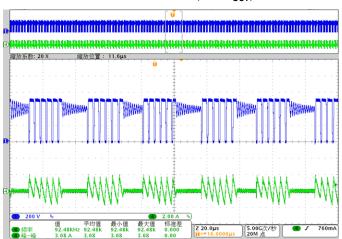

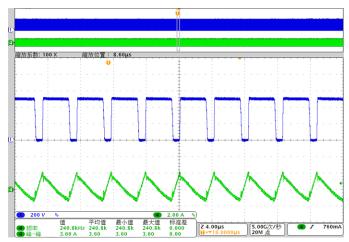

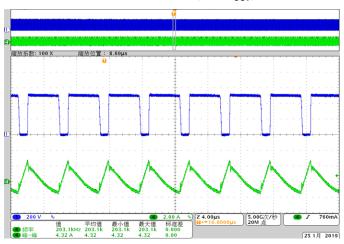

This section shows the ACF stage switching waveforms at an input voltage of 115 VAC and 20  $V_{OUT}$  at different load conditions.

注: CH1: ACF Switching Node Voltage; CH4: ACF Transformer Primary Current

図 12. SW-ACF-115 VAC, 20 V<sub>OUT</sub>, 2.5 A

### 図 13. SW-ACF-115 VAC, 20 V<sub>OUT</sub>, 3.75 A

図 14. SW-ACF-115 VAC, 20 V<sub>OUT</sub>, 5 A

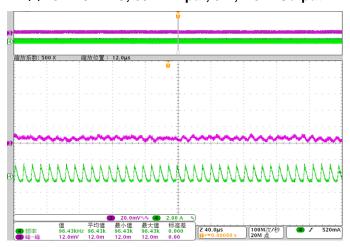

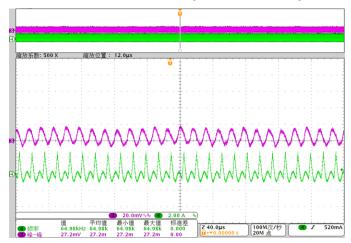

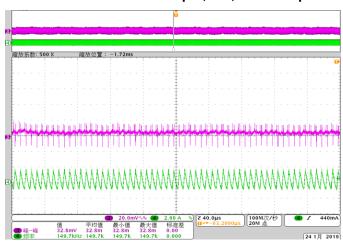

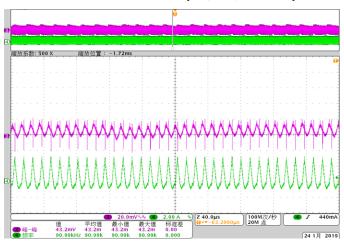

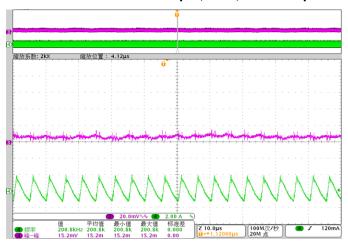

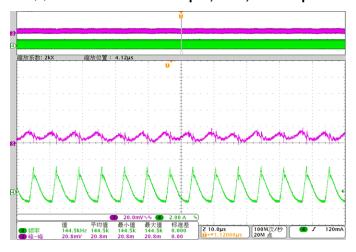

#### 3.2.2.4 Output Voltage Ripple

注: CH3: Output Voltage; CH4: Transformer Primary Current

図 15. 115-V AC, 60-Hz Input, 5-V, 2.5-A Output

図 16. 115-V AC, 60-Hz Input, 5-V, 5-A Output

図 17. 115-V AC 60-HZ Input, 9-V, 2.5-A Output

図 19. 115-V AC 60-HZ Input, 15-V, 2.5-A Output

図 20. 115-V AC 60-HZ Input, 15-V, 5-A Output

図 21. 115-V AC, 60-Hz Input, 20-V, 2.5-A Output

図 22. 115-V AC, 60-Hz Input, 20-V, 5-A Output

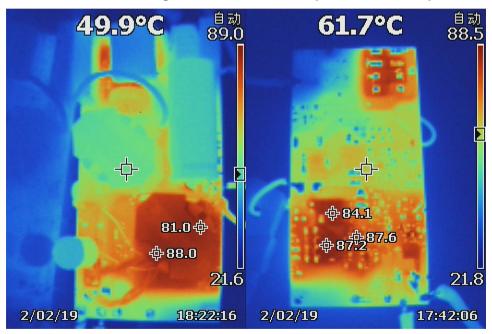

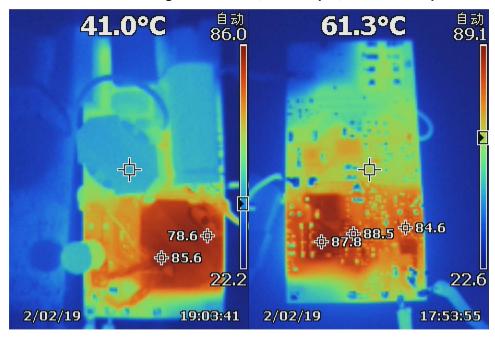

#### 3.2.2.5 Thermal Image

図 23. Thermal Image at 115-V AC, 60-Hz Input, 20-V, 5-A Output

図 24. Thermal Image at 230-V AC, 50-Hz Input, 20-V, 5-A Output

www.tij.co.jp Design Files

#### 4 Design Files

#### 4.1 Schematics

To download the schematics, see the design files at TIDA-010047.

#### 4.2 Bill of Materials

To download the bill of materials (BOM), see the design files at TIDA-010047.

#### 4.3 PCB Layout Recommendations

#### 4.3.1 Layout Prints

To download the layer plots, see the design files at TIDA-010047.

#### 4.4 Altium Project

To download the Altium Designer® project files, see the design files at TIDA-010047.

#### 4.5 Gerber Files

To download the Gerber files, see the design files at TIDA-010047.

#### 4.6 Assembly Drawings

To download the assembly drawings, see the design files at TIDA-010047.

#### 5 Related Documentation

- 1. Texas Instruments, UCC28056 6-pin single-phase transition-mode PFC controller data sheet

- 2. Texas Instruments, UCC28780 high-frequency active clamp flyback controller data sheet

- 3. Texas Instruments, UCC24612 high-frequency synchronous rectifier controller data sheet

- 4. Texas Instruments, 30-W/in³, 94% efficiency, 65-W USB Type-C™ PD AC/DC adapter reference design

- 5. Texas Instruments, 30-W/in3, 93.4% efficiency, 100-W AC/DC adapter reference design

#### 5.1 商標

E2E is a trademark of Texas Instruments.

Altium Designer is a registered trademark of Altium LLC or its affiliated companies. USB Type-C is a registered trademark of USB Implementers Forum.

すべての商標および登録商標はそれぞれの所有者に帰属します。

#### 5.2 Third-Party Products Disclaimer

TI'S PUBLICATION OF INFORMATION REGARDING THIRD-PARTY PRODUCTS OR SERVICES DOES NOT CONSTITUTE AN ENDORSEMENT REGARDING THE SUITABILITY OF SUCH PRODUCTS OR SERVICES OR A WARRANTY, REPRESENTATION OR ENDORSEMENT OF SUCH PRODUCTS OR SERVICES, EITHER ALONE OR IN COMBINATION WITH ANY TI PRODUCT OR SERVICE.

#### 重要なお知らせと免責事項

TI は、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス・デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の黙示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または黙示的にかかわらず拒否します。

これらのリソースは、TI製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した TI製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、TI の販売条件、または ti.com やかかる TI 製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、TIはそれらに異議を唱え、拒否します。

郵送先住所:Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022, Texas Instruments Incorporated