Texas Instruments Robotics System Learning Kit

## Module 10

**Quiz: Debugging Real-time Systems**

### **Quiz: Debugging Real-time Systems**

#### **Q1** Debugging Dump

```

There are two 8-bit arrays.

#define SIZE 1000

uint8_t P2buf[SIZE];

uint8 t P3buf[SIZE];

```

Write C code that dumps one instance of Port 2 input and Port 3 output into these arrays. Stop recording when the buffers are full. You can use pointer or index access to the arrays. The initialization need not fill the arrays; just initialize the index/pointers. The following are the prototypes of the functions you need to write.

```

void Debug_Init(void);

void Debug_Dump(void);

```

#### Q2 Intrusiveness

Consider the following compiler generated output for **Buffer[I]=x**;

```

ldr r0, [pc, #0x5c] ;r0=>I

000004bc:

4817

000004be:

4A18

ldr r2, [pc, #0x60] ;r2=>buffer

000004c0:

9900

ldr r1, [sp]

; r1=x

000004c2:

6800

ldr r0, [r0]

;r0=I

F8421020

str r1, [r2, r0, 1s1 #2]

000004c4:

Consider the following compiler generated output for *pt=x;

000004e4:

490F

ldr r1, [pc, #0x3c] ;r1=>pt

000004e6:

9800

ldr r0, [sp]

; r0=x

000004e8:

6809

ldr r1, [r1]

;r1=pt

000004ea:

6008

str r0, [r1]

```

Both pieces of C code store one 32-bit data into the buffer. Considering just this part of the code, which approach is less intrusive? Why?

#### **Qu3** Interrupts

List all the conditions that must be true for a SysTick interrupt to be generated? Does it matter the order in which these conditions occur?

#### **Q4** Interrupts

List the steps in order occurring in the context switch as the processor suspends the main program and launches an ISR. Include all steps after the completion of the instruction in the main, and prior to the execution of the first instruction of the ISR.

#### **Q5** Priority

Assume there are two interrupts running on the system. The SysTick interrupt has priority 2 and the Timer32 interrupt has priority 3.

- a) What happens if the two requests occur at the same time?

- b) What happens if SysTick occurs first, and while running the SysTick ISR, the Timer32 is triggered?

- What happens if Timer32 occurs first, and while running the Timer32 ISR, the SysTick is triggered?

#### Q6 SysTick

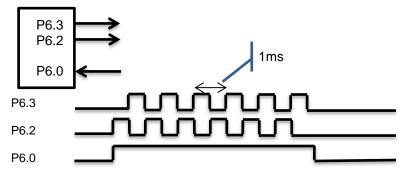

Make MSP432 Port 6 pins 3, 2 be output and make pin 0 be input. Design a software system that creates squarewaves out of P6.3 and P6.2 at 1 kHz if P6.0 is high. When oscillating, make P6.3 out of phase with P6.2. If P6.0 is low, clear both P6.3 and P6.2 low. You must use SysTick interrupts at priority 0. Assume the microcontroller is running at 3 MHz. The main program initializes the port and SysTick, but the main loop of the system is free to do other unrelated tasks.

#### Q7 Flash

For each of the following operations, specify whether the operation is *fast* (on the order of 10ns), *medium* (on the order of 100 $\mu$ s), or *slow* (on the order of 10s). Choose the closest answer for each

- a) Erasing Flash ROM

- b) Programming, writing bits to 0

- c) Reading bits that are 0

- d) Reading bits that are 1

# ti.com/rslk

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale (<a href="www.ti.com/legal/termsofsale.html">www.ti.com/legal/termsofsale.html</a>) or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2019, Texas Instruments Incorporated