## Using a Single-Output Gate-Driver for High-Side or Low-Side Drive

John Stevens

High Performance Isolated Power

#### **ABSTRACT**

In many isolated power-supply applications, power MOSFETs are often arranged in some form of bridge configuration for optimization of the power switches and power transformer for greater efficiency. These bridge configurations create two classifications of switches: high-side (HS) and low-side (LS). Dedicated HS and LS gate-driver ICs, such as the UCC277xx, UCC272xx and LM510x families, offer an output for HS switches as well as an output for LS switches in a single IC.

In contrast, some applications see great benefit from using single-output gate drivers such as the UCC2753x or the isolated UCC53xx families instead of combining HS and LS into one half bridge driver. Single output drivers can be located closer to the power switches, enabling greater layout flexibility and fewer parasitics, leading to optimal switching performance.

#### **Table of Contents**

| 1 Introduction                                                                             |                |

|--------------------------------------------------------------------------------------------|----------------|

| 2 Methods For High-Side Drive                                                              | 3              |

| 2.1 Gate-Drive Transformer Solution                                                        |                |

| 2.2 Bootstrap Bias Supply with Capacitive Signal Isolation Solution                        |                |

| 2.3 Isolated Bias Supply With Isolated High-Side Gate-Driver Solution                      |                |

| 2.4 Bootstrap Bias Supply with Isolated High/Low side Gate-Driver Solution                 |                |

| 2.5 Gate-Drive Transformer Solution                                                        | 7              |

| 3 Conclusion                                                                               |                |

| 4 Revision History                                                                         | 8              |

| ·                                                                                          |                |

| List of Figures                                                                            |                |

| Figure 1-1. Full-Bridge Powerstage With both High-Side and Low-Side Primary MOSFETsMOSFETs | 2              |

| Figure 2-1. High-Side Gate-Drive Transformer                                               |                |

| Figure 2-2. High-Side Bootstrap Circuit Using Capacitor-Based Signal Isolation             | 4              |

| Figure 2-3. High-Side Isolated Driver and Bias Supply                                      | 5              |

| Figure 2-4. Isolated Drivers Using High-Side Bootstrap Circuit                             | 6              |

| Figure 2-5. Isolated Drivers Using Isolated Bias Supply                                    | <mark>7</mark> |

### **Trademarks**

All trademarks are the property of their respective owners.

Introduction Www.ti.com

#### 1 Introduction

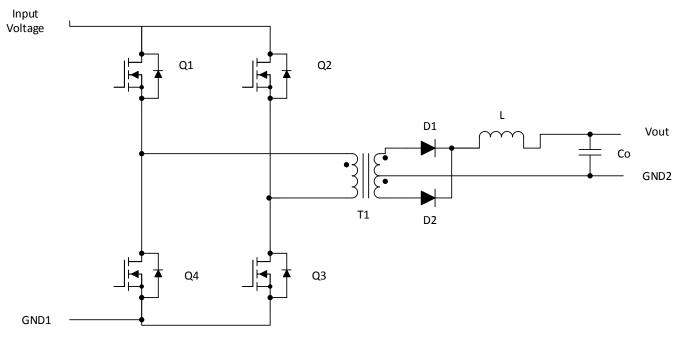

HS switches refer to Q1 and Q2 in Figure 1-1. These switches have a source connection that is floating and the voltage on this reference changes during the switching cycle. Q3 and Q4 are considered LS switches as their source reference connection is tied to input ground and does not change voltage during the switching period. Power is delivered to Vout when Q1 and Q3 are on at once, or when Q2 and Q4 are on together. For our circuit examples in Section 2, we will focus only on the bridge portion using Q1 and Q3.

Figure 1-1. Full-Bridge Powerstage With both High-Side and Low-Side Primary MOSFETs

To properly turn-on these switches in high-power applications, gate-drive ICs are often required. To properly drive a LS power switch, it is usually simple enough in that the output of the gate driver can be tied directly to the gate of the switch with the GND of the Driver IC tied to the source of the switch. To drive a HS switch, however, a few more considerations must be made:

- 1. For the gate driver output signal itself, a level-shifter or isolated signal transceiver such as a digital isolator is needed to ensure the gate maintains the proper voltage above the source to properly turn-on the HS switch. As the source of Q1 (GND of gate driver) rises during Q1 turn-on, the driver needs its reference voltage to follow the Q1 source closely and maintain the difference between the signal voltage and the reference. Further, the GND of this driver needs to be isolated from the controller ground because the Q1 source moves between 0 V and some higher voltage such as 400 V.

- 2. The HS gate driver also needs some sort of **bias supply** that can float and maintain the proper turn-on bias when the source rises to the input voltage. Otherwise, the gate driver would shutdown when the Q1 source voltage increases. This is usually accomplished by using a bootstrap circuit, an isolated bias supply, or using gate-drive transformers to isolate the gate driver from the switch-node reference.

## 2 Methods For High-Side Drive

#### 2.1 Gate-Drive Transformer Solution

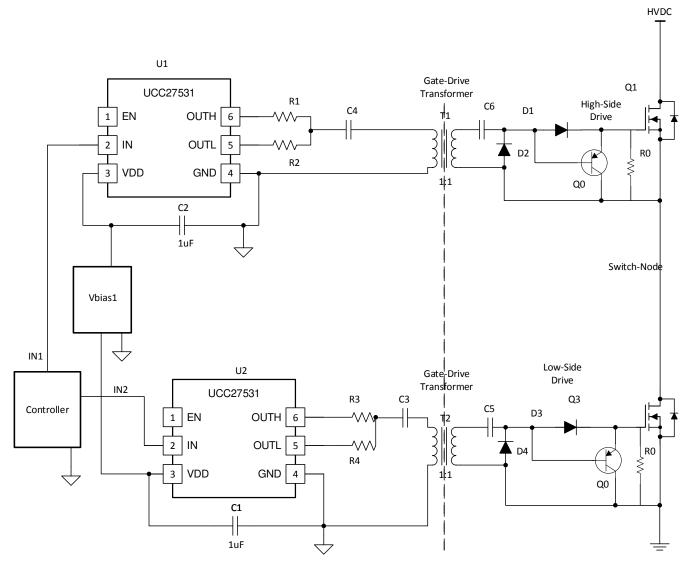

Figure 2-1. High-Side Gate-Drive Transformer

#### **Signal Isolation**

The output signals of U1 are isolated in Figure 2-1 with the use of T1. The transformer allows the gate signal to Q1 to have a floating reference that can move as the switch-node moves in voltage. DC blocking capacitors like C4 and C6 are added, as well as rectifier D1, and D2 to add offset to C6 preventing imbalance in the transformer. Q0 and R0 are used for turning off the power switch.

#### **High-Side Bias**

In Figure 2-1, an isolated or bootstrap supply is not needed. In this configuration the gate drivers are referenced to the same ground as the controller and Vbias1. Therefore, bias voltage can be directly supplied by Vbias1.

# 2.2 Bootstrap Bias Supply with Capacitive Signal Isolation Solution Signal Isolation

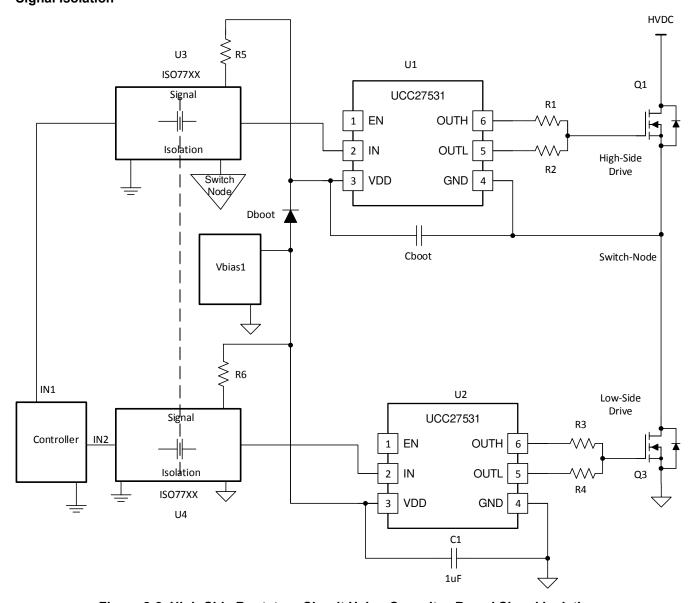

Figure 2-2. High-Side Bootstrap Circuit Using Capacitor-Based Signal Isolation

In Figure 2-2, the input to U1 is isolated using U3. U3 is capacitive signal isolator ISO77xx. Capacitive-based isolators can signal properly even with large common-mode ground slew-rates, they are more stable over life and temperature compared to optocouplers, and they do not have the duty cycle limitations of gate-drive transformers.

#### **High-Side Bias**

In Figure 2-2, Dboot and Cboot are used as a bootstrap circuit to bias U1 properly when Q1 is turned on. When Q1 is off, Dboot is forward biased and U1 is supplied directly from Vbias1 while Cboot is charged. When Q1 turns on, the switch-node voltage increases to HVDC, Dboot is reverse-biased and protecting Vbias1, and U1 is powered as Cboot empties its charge into the VDD pin of U1. This charge from Cboot must be adequate to keep U1 on throughout the entire time that Q1 is on. Sizing of Dboot and Cboot are beyond the scope of this article. In the UCC27712 datasheet, refer to for selecting Cboot and for selecting Dboot.

## 2.3 Isolated Bias Supply With Isolated High-Side Gate-Driver Solution

Figure 2-3. High-Side Isolated Driver and Bias Supply

#### Signal Isolation

In Figure 2-3, the input signals are isolated using an isolated gate driver for the high side and ISO77xx for the low side.

## **High-Side Bias**

In Figure 2-3, U1, Isolated gate driver, UCC53xx is used as a high-side driver, and is supplied using an isolated bias supply on the power side and VCC from the signal side. The supply Vbias1 is referenced to the GND pin or power ground of a non-isolated UCC27531 and also supplies the floating bias for the high-side. This is similar to the configuration in the UCC27531EVM-184 or UCC5390SCDEVM-010, where non-regulated, isolated supplies such as SN650x are used.

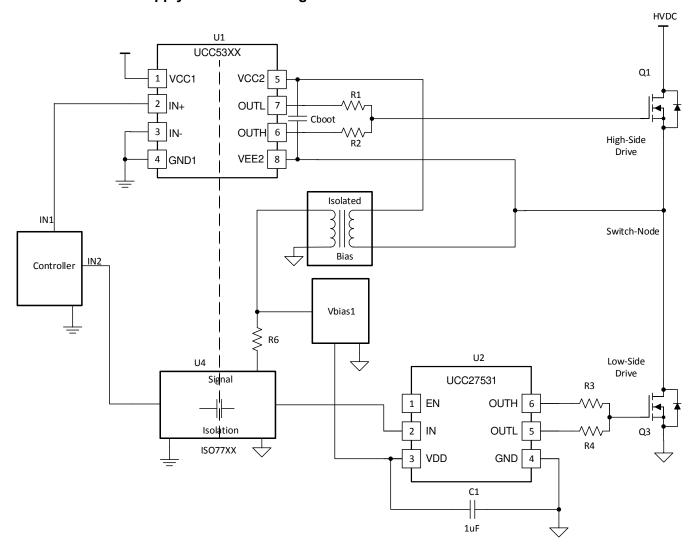

## 2.4 Bootstrap Bias Supply with Isolated High/Low side Gate-Driver Solution

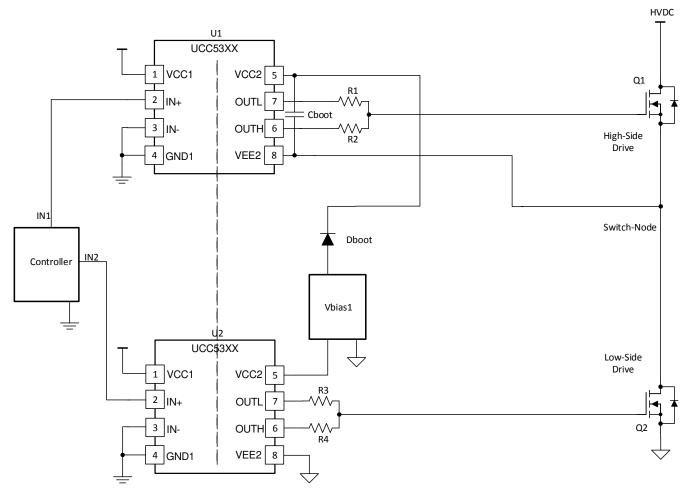

Figure 2-4. Isolated Drivers Using High-Side Bootstrap Circuit

#### Signal Isolation

The input signals of U1 are isolated in Figure 2-4, with the isolated gate driver, UCC53xx. This allows the signal to operate properly, even as the signal reference (switch-node) changes voltage throughout the switching period. It also isolates the controller ground from the switch-node and power ground.

#### **High-Side Bias**

In Figure 2-4, Dboot and Cboot are used as a bootstrap circuit to bias U1 properly. In the UCC27712 datasheet, refer to for selecting Cboot and for selecting Dboot.

#### 2.5 Gate-Drive Transformer Solution

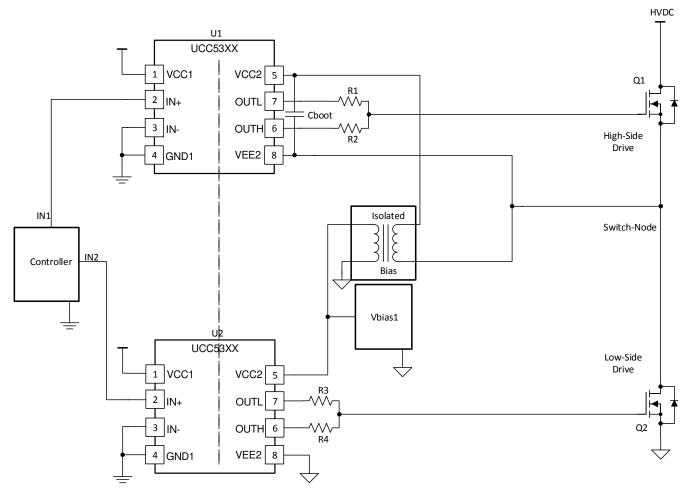

Figure 2-5. Isolated Drivers Using Isolated Bias Supply

#### **Signal Isolation**

The input signals of U1 are isolated in Figure 2-5, with the isolated gate driver, UCC53xx. The isolated bias, a transformer, allows the gate signal to Q1 to have a floating reference that can move as the switch-node moves in voltage.

#### **High-Side Bias**

In Figure 2-5, signal isolation is not needed because the gate drivers provide this internally. In this configuration, a bootstrap supply is not needed because of the isolated bias. Vbias1, referenced to power ground, supplies the floating bias for the high-side.

Conclusion Www.ti.com

## 3 Conclusion

Driving the gates of LS power switches is fairly simple in terms of signal path and proper biasing. Driving floating-source switches such as HS MOSFETs in bridge configurations, however, presents some challenges in terms of both signal path and bias for the HS gate driver. This paper has presented numerous circuit examples that have shown different methods of achieving HS gate driving using a single-output gate driver.

## **4 Revision History**

| Changes from Revision A (June 2018) to Revision B (September 2023)                                                                                                        | Page |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Updated the numbering format for tables, figures, and cross-references throughout the document                                                                            | 1    |

| Changes from Revision * (March 2013) to Revision A (June 2018)                                                                                                            | Page |

| Changed Figure 2 to include PNP turn off method.      Added highside isolated gate driver to Figure 4                                                                     |      |

| <ul> <li>Added highside and lowside isolated gate driver to Figure 5.</li> <li>Added highside and lowside isolated gate driver with isolated bias to Figure 5.</li> </ul> | 6    |

|                                                                                                                                                                           |      |

## IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2023, Texas Instruments Incorporated