### SCANSTA101,SCANSTA111,SCANSTA112, SCANSTA476

JTAG Advanced Capabilities and System Design

Literature Number: SNLA211

# SIGNAL PATH designer®

Tips, tricks, and techniques from the analog signal-path experts

| N | _ | -1 | 1 | 7 |

|---|---|----|---|---|

| Feature I | Article  |      | 1-6 |

|-----------|----------|------|-----|

| Comme /   | Innlicat | ione | 2   |

# JTAG Advanced Capabilities and System Design

— By David Morrill, Principal Applications Engineer

he JTAG bus, originally intended for board-level manufacturing test, has evolved into a multipurpose bus also used for In-System Programming (ISP) of FPGAs, FLASH, and processor emulation. This article's intent is to provide a brief overview of JTAG. Several system-level design options will be proposed, from the simplest board-level JTAG chain through a complex embedded multidrop system. Finally, an appendix is included that contains some useful definitions.

#### Overview: What is JTAG?

The Joint Test Action Group (JTAG) is an industry group formed in 1985 to develop a method to test populated circuit boards after manufacture. The group's work resulted in the IEEE 1149.1 standard entitled Standard Test Access Port and Boundary-Scan Architecture. The terms 1149.1, JTAG, "dot 1", and SCAN all refer to the same thing, the IEEE 1149.1 Standard for Boundary Scan Test.

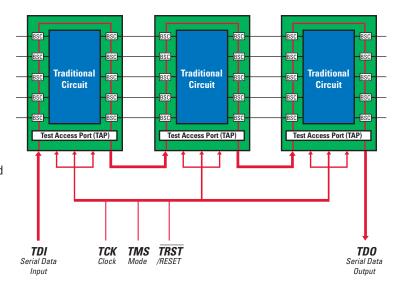

What is JTAG and what does it do?

- 1) It is a serial test bus.

- 2) It adds a Test Access Port (TAP) consisting of four pins to an IC (five with optional RESET) as shown in *Figure 1*.

- TDI (Test Data In)

- TDO (Test Data Out)

- TCK (Test Clock)

- TMS (Test Mode Select)

- TRST (Test Reset)

JTAG provides access to interconnected digital cells on an IC:

- 1) with a method of access for test and diagnostics and the

- ability to do factory and remote testing and diagnostics,

- ability to perform software debug, and

- reduce "No-Fault-Found" problems

- 2) with a method for in-circuit upgrades and the

- ability to remotely perform system-wide firmware upgrades

## **High Efficiency. Low Power.**

#### **Energy-Efficient Solutions for Communications Infrastructure**

National's communications infrastructure solutions and subsystems are designed to meet the needs of wired data center, wireless base station, and merchant power systems.

- ✓ Maximum performance with minimal heat

- ✓ System monitoring for increased system reliability

- ✓ Reference designs and online tools

#### Wired and Data Center Applications

PowerWise® Adaptive Voltage Scaling (AVS), a closed-loop voltage optimization technology, reduces both active and standby energy consumption in digital subsystems.

#### Wireless Base Station Applications

National's high dynamic range receiver subsystems enable multi-carrier and multi-standard radios.

#### Merchant and Point of Load Power Solutions

National's end-to-end power management solutions maximize power density and thermal dissipation.

## SIGNAL PATH designer

#### JTAG Advanced Capabilities and System Design

- Serial data in/out make one big loop through all chips

- Clock, mode, and reset signals shared by all all chips

Figure 1. Basic JTAG Chain Interconnect

All chips are driven by one TMS, TCLK, and  $\overline{TRST}$  signal from the test device. The TDI and TDO signals are daisy-chained together serially as shown in *Figure 1* and below:

```

Test device → Chip 1 TDI

Chip 1 TDO → Chip 2 TDI

Chip 2 TDO → Chip 3 TDI

...

Chip n-1 TDO → Chip n TDI

Chip n TDO → Test device

```

#### **Basic JTAG Application**

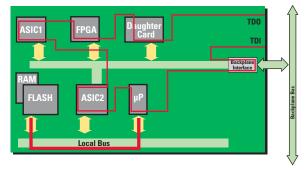

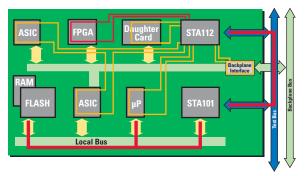

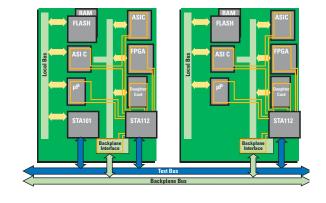

Figure 2 shows a basic JTAG chain consisting of JTAG-enabled devices connected in series through TDI and TDO. TCK, TMS, and  $\overline{TRST}$  are common to each device and are not shown. This chain is very simple and relatively easy to implement, but it is slow and does not provide focused testing. For example to access ASIC2, data must be serially shifted through the backplane interface, microprocessor ( $\mu$ P), ASIC2, ASIC1, FPGA, and the daughter card. In this simple example five devices can be seen on a chain. On a typical card, there can be dozens of devices. FLASH can also be programmed via the JTAG chain.

Figure 2. Basic Board with JTAG

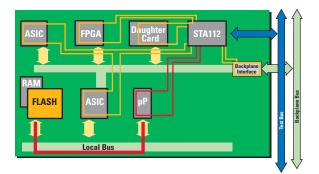

Figure 3 shows how a JTAG chain can be partitioned to increase speed, access, and flexibility. The SCANSTA111/112 is an addressable JTAG port (also known as "bridge") that allows the JTAG bus to be partitioned onto local scan ports (LSP) to reduce the size of the individual JTAG chains. This means the JTAG master can select one or more of these chains via LSP for focused testing or, in the case of FPGAs and FLASH memory, (re)programming. This is necessary for multi-board testing and highly desirable for FPGA programming. Breaking one long JTAG chain into smaller chains also can improve access/test time significantly. The LSPs can

## SIGNAL PATH designer

#### **JTAG Advanced Capabilities and System Design**

be accessed in parallel via an address mask for bulk programming/testing. The SCANSTA111 can be used for up to three partitions; the SCANSTA112 up to seven. The devices also can be cascaded; for example, a STA112 connected to a LSP of another STA112.

Figure 3. Board with Partitioned JTAG

Chains using SCANSTA112

#### **Embedded JTAG Master**

Assuming board-level or system-level JTAG test capability exists, the next level of capability is to develop an embedded JTAG system. Embedded JTAG provides a means to implement self diagnostics and reconfiguration, system-level test, and remote test/upgrades. This can be done with the on-host processor. However, this process is not automated and requires custom and costly development effort. This is a tedious task that is difficult to both debug and ensure full test coverage.

In contrast, the SCANSTA101-embedded JTAG test master enables system designers to embed their test vectors easily from their automatic test pattern generator (ATPG) tools into the production system. National Semiconductor provides a free SCANEASE conversion utility to port the ATPG vectors directly to the SCANSTA101. As shown in *Figure 4*, the SCANSTA101 interfaces between the host processor and the serial JTAG bus. It offloads this work from the host processor and drives the JTAG bus with test vectors.

Figure 4. Board with SCANSTA101-Embedded Master and Partitioned JTAG Chains using SCANSTA112

#### **Multidrop JTAG**

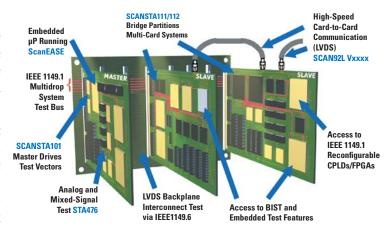

Next, the multidrop system will be discussed. This multidrop system consists of a backplane and test bus with several add-in cards as shown in *Figure 5*. The cards contain partitioned chains and, if needed, a STA101 master. A configuration of this type allows access and testing of the interconnect, ASICs, FLASH/RAM (via the local bus), FPGAs, daughter cards, the backplane interface, and the local buses of all boards on the backplane bus. The STA111/112's address masks allow all boards to be accessed in parallel if desired, which greatly increases speed. A STA101 could be added to the second board for redundancy.

Figure 5. Multidrop System with SCANSTA101-Embedded Master and Partitioned JTAG Chains using SCANSTA112

# SIGNAL PATH | designer

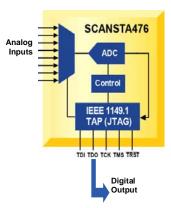

Figure 6. Block Diagram of SCANSTA476

#### **Analog Monitoring via JTAG**

It would be useful to have voltage measurement capability during board/system testing through IEEE1149.1. For example, it may be necessary to measure critical power supplies during development and factory test. Access to analog nodes that don't have physical access, or even require online voltage testing for health monitoring and prognostics may be required. The SCANSTA476 is an analog voltage monitor that has eight inputs that are fed to an

analog-to-digital converter (ADC). The digital result is stored in a JTAG register, all accessible via a fully 1149.1-compliant digital TAP. *Figure 6* shows a block diagram of the SCANSTA476. Having the ability to add voltage measurement capability to a system through a JTAG chain is a powerful tool for the system designer.

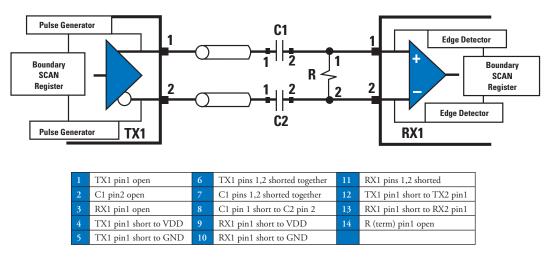

#### **Differential Signals, AC Coupling, and JTAG**

Most modern systems use high-speed, AC-coupled differential pairs. While 1149.1 is an excellent tool for testing and diagnosing digital systems, it was designed for DC-coupled, TTL-level nets. AC coupling and differential signals are not compatible with 1149.1. An IEEE working group studied the problem and developed a solution that became IEEE1149.6.

The solution required edge detectors to be added to both polarities of the differential pair receiver as shown in *Figure 7*. During a JTAG test, the 1149.6-enabled transmitter produces pulses under the control of the Boundary Scan Register (BSR) instead of static DC levels (as was done in 1149.1).

Figure 7. Schematic Showing Potential Defects Detectable by an 1149.6-Enabled Device for an AC-Coupled Differential Transmission Line

# SIGNAL PATH | designer

#### **JTAG Advanced Capabilities and System Design**

These pulses pass through the AC-coupling capacitor resulting in an edge at the receiver. The receiver detects these edges and passes this information to the BSR which can be read to determine if a defect is present.

A very important consideration is that IEEE1149.6 uses the identical protocol and TAP as IEEE1149.1, making it compatible with existing JTAG systems. National offers an entire array of 1149.6 products including cross points, mux buffers, and SerDes.

#### **Putting It All Together**

Figure 8 provides an example of how a typical highperformance telecom or datacom system might look. Much of the design and component selection has been driven by the requirements of the market place such as high performance, flexibility, and very high availability. Thus, there are many components with JTAG and built-in-test features as well as dense FPGAs for quick turn and flexibility. These test features and the ability to reconfigure components during manufacturing and in the field provide a cost-effective solution to the demanding requirements of deployed systems.

The JTAG test bus is used to access the test features on each board. The STA101 interfaces to the processor bus and drives the JTAG bus with ATPG vectors. The STA111/112 bridge is used to convert the IEEE JTAG test bus to a multidrop addressable environment and adds partitioning capabilities for JTAG path management. JTAG is used to access CPLDs for reconfiguration/programming, BIST features, and embedded test features for other complex devices. Card-to-card, AC-coupled differential interconnects are tested with 1149.6 enabled devices, and analog nodes are sampled with the STA476.

Figure 8. Total System

#### **Conclusion**

System-level JTAG can be a powerful tool, allowing manufacturing, remote test, diagnostics, and re-configuration. The system designer should pay careful attention to the level of access and speed required when designing a system, and use the proposed architectures as a starting point when beginning a design. National provides products, software, and support for simple through complex embedded JTAG systems and can provide access and interconnect test to digital, analog, and differential nets.

#### **Appendix: Useful Definitions**

- JTAG -Joint Test Action Group

- ISP In-System Programming

- TAP Test Access Port

- BSDL -Boundary Scan Description Language

- BSR Boundary Scan Register

- ATPG -Automated Test Program Generation

- BIST -Built-In Self Test

- SCANEASE -National Semiconductor's SVF Converter

- SVF Serial Vector Format

- LSP Local Scan Port

national.com/spdesigner

### **Design Tools**

#### WEBENCH® Signal Path Designer® Tools

Design, simulate, and optimize amplifier circuits in this FREE online design and prototyping environment allowing you to:

- Synthesize an anti-alias filter

- Select the best amplifier/ADC combo for your system specs

- Make trade-offs based on SNR, SFDR, supply voltage

- Simulate real-world operating conditions using SPICE

- Receive samples in 24 hours

national.com/webench

#### **WaveVision 4.1 Evaluation Board**

Test and evaluate A/D converters with National's easy-to use WaveVision 4.1 evaluation board. Each evaluation board comes complete with USB cable and support software.

#### Features and benefits:

- Plug-n-play ADC evaluation board

- USB 2.0 interface to PC

- PC-based data capture

- Easy data capture and evaluation

- Highlighted harmonic and SFDR frequencies

- Easy waveform examination

- Produces and displays FFT plots

- Dynamic performance parameter readout with FFT

- Produces and displays histograms

#### National Semiconductor

2900 Semiconductor Drive Santa Clara, CA 95051 1 800 272 9959

#### **Mailing address:**

PO Box 58090 Santa Clara, CA 95052

#### Visit our website at:

www.national.com

For more information, send email to:

new.feedback@nsc.com

## Don't miss a single issue!

Subscribe now to receive email alerts when new issues of Signal Path Designer® are available: national.com/spdesigner

Also, be sure to check out our Power Designer! View online today at: national.com/powerdesigner

#### IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

#### Products Applications

Audio www.ti.com/audio Communications and Telecom www.ti.com/communications **Amplifiers** amplifier.ti.com Computers and Peripherals www.ti.com/computers dataconverter.ti.com Consumer Electronics www.ti.com/consumer-apps **Data Converters DLP® Products** www.dlp.com **Energy and Lighting** www.ti.com/energy DSP dsp.ti.com Industrial www.ti.com/industrial Clocks and Timers www.ti.com/clocks Medical www.ti.com/medical

Interface

interface.ti.com

Security

www.ti.com/security

Logic

logic.ti.com

Space, Avionics and Defense

www.ti.com/space-avionics-defense

Power Mgmt power.ti.com Transportation and Automotive www.ti.com/automotive

Microcontrollers microcontroller.ti.com Video and Imaging www.ti.com/video

RFID <u>www.ti-rfid.com</u>

OMAP Mobile Processors www.ti.com/omap

Wireless Connectivity www.ti.com/wirelessconnectivity

TI E2E Community Home Page <u>e2e.ti.com</u>

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2011, Texas Instruments Incorporated