# DM816x Easy CYG Package PCB Escape Routing

#### ABSTRACT

The DM816x CYG package is designed with a new technology called a Via Channel<sup>™</sup> array. This technology allows for easy routing of the device in two signal and two power layers using large throughhole via diameters and standard trace widths; it is cost and time effective. Where more than four printed circuit board (PCB) layers are used, the routing is much more open and flexible than a regular BGA. This application report shows how to route the entire package by showing each quadrant up close and explaining the PCB feature sizes used. For this document, the Allegro<sup>®</sup> layout tool was used, although any PCB layout tool can be used.

|    | Contents                                                    |    |

|----|-------------------------------------------------------------|----|

| 1  | DM816x PCB Layout Technology                                | 2  |

| 2  | DM816x PCB Routing Detail                                   | 4  |

|    | List of Figures                                             |    |

| 1  | DM816x Footprint With Via Channel Array                     | 2  |

| 2  | First Quadrant (Upper Left) Routing (top and bottom layers) | 4  |

| 3  | First Quadrant Top Layer                                    | 5  |

| 4  | First Quadrant Bottom Layer                                 | 6  |

| 5  | Second Quadrant Routing (top and bottom layers)             | 7  |

| 6  | Second Quadrant Top Layer                                   | 8  |

| 7  | Second Quadrant Bottom Layer                                | 9  |

| 8  | Third Quadrant Routing (top and bottom layers)              | 10 |

| 9  | Third Quadrant Top Layer                                    | 11 |

| 10 | Third Quadrant Bottom Layer                                 |    |

| 11 | Fourth Quadrant Routing (top and bottom layers)             | 13 |

| 12 | Fourth Quadrant Top Layer                                   | 14 |

| 13 | Fourth Quadrant Bottom Layer                                |    |

Via Channel is a trademark of Texas Instruments. Allegro is a registered trademark of Cadence Design Systems. All other trademarks are the property of their respective owners.

### 1 DM816x PCB Layout Technology

#### 1.1 Via Channel Layout Advantages

Via Channel technology is a way of depopulating balls on the BGA chip package in a shape that makes it possible to have the vias concentrated in channels. This allows two important advantages.

- The via outside diameter (also known as the annular ring) can be larger than it normally would be if it

had to be placed in between the balls, since all of the vias are placed in special areas called via

channels. This makes manufacturing the PCB less expensive because 20/10 vias (vias with an outside

diameter of 20 mils and a finished hole size of 10 mils) are possible. Smaller vias can also be used,

but are not required.

- The vias are grouped in a radial pattern instead of a series of concentric rings around the middle of the chip, which is the case with normal BGA array PCB routing. The traces are more easily routed out of the inner parts of the chip because they are not restricted to the narrow paths in between many rows of through-hole vias. This allows reduced PCB layers because of the increased routing efficiency (more traces for every PCB layer). In the case of this chip, a four layer design is possible for all systems if PCB size is not crucial.

Figure 1 shows the resulting DM816x footprint. This shape has been separated down into quadrants. A quadrant is defined as one of four equal size squares making up the whole. The upper left square is called quadrant 1 and so on.

|        |     | _ | _ | _ | _          | _ | _ | _          |    |            | _      | _      | _          | -      |   | _ |   | -  | _ |   | _ | _ |            | _ |   | _  | _ |            |   | _ | _          |   |   |   |   | _     |

|--------|-----|---|---|---|------------|---|---|------------|----|------------|--------|--------|------------|--------|---|---|---|----|---|---|---|---|------------|---|---|----|---|------------|---|---|------------|---|---|---|---|-------|

| 0      | 0   | 0 | 0 | 0 | 0          | 0 | 0 | 0          | 0  | 0          | 0      | 0      | 0          | 0      | 0 | 0 | 0 | С  | 0 | 0 | 0 | 0 | 0          | 0 | 0 | 0  | 0 | 0          | 0 | 0 | 0          | 0 | 0 | 0 | 0 | 0     |

| 0      | 0   | 0 | 0 | 0 | 0          | 0 | 0 | $^{\circ}$ | 0  | $^{\circ}$ | 0      | 0      | $^{\circ}$ | 0      | 0 | 0 | 0 | С  | 0 | 0 | 0 | 0 | $^{\circ}$ | 0 | 0 | 0  | 0 | $^{\circ}$ | 0 | 0 | $^{\circ}$ | 0 | 0 | 0 | 0 | 0     |

| 0      | 0   |   |   | 0 | 0          |   | 0 | 0          |    | 0          |        | 0      | 0          | 0      |   | ٥ | 0 | C  | 0 | 0 |   | 0 | 0          | 0 |   | 0  |   | 0          | 0 |   | 0          | 0 |   |   | 0 | 0     |

| 0      | 0   |   |   |   | 0          | 0 | 0 | 0          |    |            |        | 0      | 0          | 0      |   | 0 |   | С  | 0 | 0 |   | 0 | 0          | 0 |   |    |   | 0          | 0 | 0 | $^{\circ}$ |   |   |   | 0 | 0     |

| 0      | 0   | 0 |   |   |            | 0 | 0 | 0          |    | $^{\circ}$ |        | 0      | 0          | 0      |   | 0 | 0 | С  | 0 |   |   | 0 | $^{\circ}$ | 0 |   | 0  |   | $^{\circ}$ | 0 | 0 |            |   |   | 0 | 0 | 0     |

| 0      | 0   | 0 | ٥ |   |            | ٥ | 0 | 0          |    |            |        | 0      | 0          | 0      | 0 | 0 | 0 | C  | 0 | 0 | ٥ | 0 | 0          | ٥ |   |    |   | 0          | 0 | 0 |            |   | 0 | ٥ | 0 | 0     |

| 0      | 0   |   | 0 | 0 | 0          | 0 |   | 0          | 0  |            |        | 0      | 0          | 0      | 0 | 0 | 0 | С  | 0 | 0 | 0 | 0 | $^{\circ}$ | 0 |   |    | 0 | $^{\circ}$ |   | 0 | $^{\circ}$ | 0 | 0 |   | 0 | 0     |

| 0      | 0   | 0 | 0 | 0 | 0          |   |   |            | Q. | $^{\circ}$ |        | 0      | 0          | 0      | 0 | 0 | 0 | C  | 0 | 0 | ٥ | 0 |            | 0 |   | 0  | ò |            |   |   | 0          | 0 | 0 | 0 | 0 | 0     |

| õ      | 0   | 0 | 0 | 0 | 0          | 0 |   |            | 1  | $^{\circ}$ |        | 0      | $^{\circ}$ | 0      | 0 | 0 | 0 | С  | 0 | 0 | 0 | 0 | $^{\circ}$ | 0 |   | ୀ  |   |            |   | 0 | $^{\circ}$ | 0 | 0 | 0 | 0 | 0     |

| 0      |     |   |   |   |            |   |   |            |    |            |        |        | 0          | 0      | 0 | 0 | 0 | С  | 0 | 0 | 0 | 0 | 0          | 0 |   |    |   |            | 0 |   |            |   |   |   |   | 0     |

| 0      | 0   | 0 |   | 0 |            |   | 0 | 0          | A. | _          | 0      | 0      | 0          | 0      | 0 | 0 | 0 |    |   | 0 | ٥ | 0 | 0          | ٥ | 0 | -  |   | 9          | 0 |   |            | 0 |   | 0 | 0 | 0     |

| 0      | 0   |   |   |   |            |   |   |            |    | 0          |        |        |            |        |   |   |   |    |   |   |   |   |            |   |   | 0  |   |            |   |   |            |   |   |   | 0 | 0     |

| 0      | 0   | 0 | 0 | 0 | 0          | 0 | 0 | 0          | 0  | $^{\circ}$ |        | 0      | 0          | 0      | 0 | 0 | 0 | С  | 0 | 0 | 0 | 0 | $^{\circ}$ | 0 |   | 0  | 0 | $^{\circ}$ | 0 | 0 | $^{\circ}$ | 0 | 0 | 0 | 0 | 0     |

| 0      | 0   | 0 | 0 | 0 | $^{\circ}$ | 0 | 0 | $^{\circ}$ | 0  | $^{\circ}$ |        | 0      | $^{\circ}$ | 0      | 0 | 0 | 0 | С  | 0 | 0 | 0 | 0 | $^{\circ}$ | 0 |   | 0  | 0 | $^{\circ}$ | 0 | 0 | $^{\circ}$ | 0 | 0 | 0 | 0 | 0     |

| 0      | 0   | 0 | 0 | 0 | 0          | 0 | 0 | $^{\circ}$ | 0  | $^{\circ}$ |        | 0      | $^{\circ}$ | 0      | 0 | 0 | 0 | С  | 0 | 0 | 0 | 0 | $^{\circ}$ | 0 |   | 0  | 0 | $^{\circ}$ | 0 | 0 | $^{\circ}$ | 0 | 0 | 0 | 0 | 0     |

| 0      | 0   | 0 | ٥ | 0 | 0          | ٥ | 0 | 0          | ٥  | 0          |        | 0      | 0          | 0      | 0 | 0 | 0 | C  | 0 | 0 | ٥ | 0 | 0          | ٥ |   | ٥  | 0 | 0          | ٥ | ٥ | 0          |   |   |   | 0 | 0     |

|        |     |   |   |   |            |   |   |            |    |            |        | 0      | 0          | 0      | 0 | 0 | 0 | С  | 0 | 0 | 0 | 0 | $^{\circ}$ | 0 |   | 0  | 0 | $^{\circ}$ | 0 | 0 | $^{\circ}$ | 0 | 0 | 0 | 0 | 0     |

| 0      | 0   |   | 0 | 0 | 0          | 0 | 0 | 0          | 0  | $^{\circ}$ |        | 0      | 0          | 0      | 0 | 0 | 0 | С  | 0 | 0 | 0 | 0 | 0          | 0 |   |    | 0 | 0          | 0 | 0 | $^{\circ}$ | 0 | 0 | 0 | 0 | 0     |

|        |     | 0 |   |   |            |   |   |            |    |            |        | 0      | 0          | 0      | 0 | 0 | 0 | С  | 0 | 0 | 0 | 0 | 0          | - |   |    |   |            |   |   | 0          |   |   |   |   |       |

| 0      | 0   | 0 | 0 | 0 | 0          | 0 | 0 | 0          | 0  | 0          |        | 0      | 0          | 0      | 0 | 0 | 0 | С  | 0 | 0 | 0 | 0 | 0          | 0 |   |    | 0 | 0          | 0 | 0 | $^{\circ}$ | 0 | 0 | 0 | 0 | 0     |

|        |     |   |   | 0 |            |   |   |            |    |            |        | 0      | 0          | 0      | 0 | 0 | 0 | C  | 0 | 0 | ٥ | 0 | 0          | ٥ |   | ٥  | 0 | 0          | ٥ | 0 | 0          | 0 | 0 | 0 | 0 | 0     |

| 0      | 0   | 0 | 0 | 0 | 0          | 0 | 0 | 0          | 0  | 0          |        | 0      | 0          | 0      | 0 | 0 | 0 | С  | 0 | 0 | 0 | 0 | 0          | 0 |   | 0  | 0 | 0          | 0 | 0 | 0          |   |   |   | 0 | 0     |

| 0      | 0   | 0 | 0 | 0 | 0          | 0 | 0 | 0          | 0  | 0          |        | 0      | 0          | 0      | 0 | 0 | 0 | С  | 0 | 0 | 0 | 0 | 0          | 0 |   | 0  | 0 | 0          | 0 | 0 | 0          | 0 | 0 | 0 | 0 | 0     |

| 0      | 0   | 0 | ٥ | 0 | 0          | ٥ | 0 | 0          | 0  | 0          |        | 0      | 0          | 0      | 0 | 0 | 0 | C  | 0 | 0 | ٥ | 0 | 0          | 0 |   | 0  | 0 | 0          | 0 | 0 | 0          | 0 | 0 | 0 | 0 | 0     |

| 0      | 0   | 0 | 0 | 0 | 0          | 0 | 0 | 0          | 0  | 0          |        | 0      | 0          | 0      | 0 | 0 | 0 | С  | 0 | 0 | 0 | 0 | 0          | 0 |   | 0  | 0 | 0          | 0 | 0 | 0          | 0 | 0 | 0 |   |       |

| 0      | -   |   |   |   |            |   |   |            |    | 0          |        |        |            |        |   |   |   |    |   |   |   |   |            |   |   | 0  |   |            |   |   |            |   |   |   |   | 0     |

| 0      | 0   | 0 |   |   |            |   |   |            |    |            |        |        |            |        |   |   |   |    |   |   |   |   |            |   |   |    |   | 0          | 0 |   |            | 0 |   | 0 | 0 |       |

| 0      | -   |   |   |   |            |   |   |            | 1  | 7          |        |        |            |        |   | 0 |   |    |   |   |   |   |            |   |   |    | Λ |            | 0 | 0 |            |   |   |   | 0 |       |

| 0      | 0   | 0 | 0 | 0 | 0          | 0 |   |            |    | 9          |        | ¢      | 0          | 0      | 0 | 0 | 0 | C  | 0 | 0 | 0 | 0 | 0          |   |   | ۰, |   |            |   |   | 0          |   |   |   |   | · · I |

| 0      |     | 0 |   |   |            |   |   |            | 0  | े          | )      |        |            |        |   | 0 |   |    |   |   |   |   |            | 0 |   | O, | v | r          |   |   | 0<br>0     | 0 | 0 | 0 | 0 | 0     |

| 0      | -   |   |   |   |            |   |   |            | 0  |            |        |        |            |        |   | 0 |   |    |   |   |   |   |            | 0 |   |    | 0 | 0          |   | 0 | 0          | 0 | 0 |   | 0 | 0     |

| 0      |     |   |   |   |            |   |   |            |    |            |        | 0      | 0          | 0      | 0 | 0 | 0 |    |   | 0 |   |   |            | 0 |   |    |   | Q          | 0 | 0 |            |   | 0 | 0 | 0 |       |

| 0      | -   |   |   |   |            |   |   |            |    | 0          |        |        |            |        |   |   |   |    |   |   |   |   |            |   |   | 0  |   |            |   |   |            |   |   |   |   |       |

| 0      |     |   |   |   | 0          |   |   |            |    |            |        |        | -          |        |   | 0 | • |    |   |   |   | • | 0          | 0 |   |    |   | -          |   |   | 0          |   |   |   |   | - 1   |

|        | 0   |   |   | 0 | 0          |   |   | 0          |    | 0          |        |        | 0          |        |   |   | 0 |    |   |   |   |   | 0          |   |   | 0  |   |            | 0 |   |            |   |   |   |   |       |

| Υ Υ    | Ÿ., |   |   |   |            |   |   |            | -  | ~          | $\sim$ | $\sim$ | $\sim$     | $\sim$ | 0 | 0 | 0 | C. | 0 | 0 | 0 | 0 | 0          | 0 | 0 | 0  | 0 | 0          | 0 | 0 | 0          | 0 | 0 | 0 | 0 | 0     |

| o<br>o | 0   |   |   |   |            |   |   |            |    |            |        |        |            |        |   |   |   |    |   |   |   |   |            |   |   |    |   |            |   |   |            |   |   |   |   |       |

Figure 1. DM816x Footprint With Via Channel Array

**NOTE:** The finished routing from the EVM (as shown) is available on the TI website (in the DaVinci SoC Products) located at:

http://www.ti.com/lsds/ti/dsp/video\_processors/dm81x/products.page in Allegro format. This layout is a six layer PCB due to time constraints, but uses only two signal layers as shown here.

## 1.2 DM816x PCB Layout Feature Sizes and Constraints

The overall PCB layout rules for routing this footprint (and the sizes used in this document) are as follows:

- 0.3mm BGA pad (as suggested by IPC standard 7351A and TI reliability studies)

- 4 mil (0.1mm) minimum trace size

- 4 mil (0.1mm) minimum clearance between traces and vias

- 20 mil (0.50mm) minimum via diameter

- 10 mil (0.25mm) minimum finished hole diameter

If done correctly, the results will be:

- No blind, stacked, buried, or micro vias necessary

- Only two signal layers required

This application report shows one example of a DM816x routing. There are many ways to route the same chip. Feel free to use this example in any way that is helpful.

The following illustrations show the EVM layout on the only two signal layers (top and bottom).

**NOTE:** It is helpful to do all routing using a metric measurement system on the CAD software. Using standard measurements (mils) with successive copy commands will compound rounding errors and can result in design rule violations.

## 2 DM816x PCB Routing Detail

### 2.1 Package Quadrant Pictures

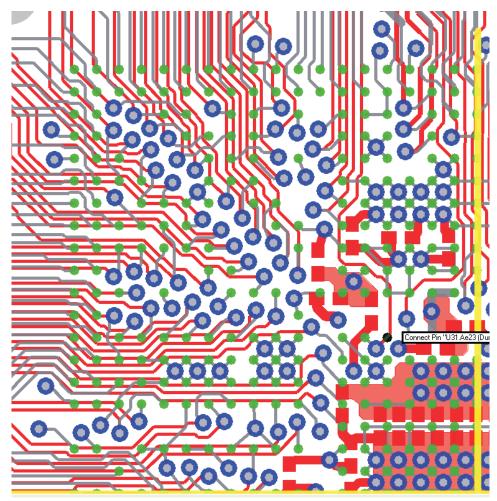

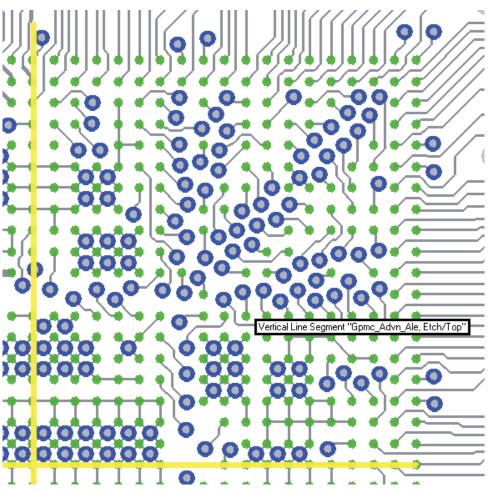

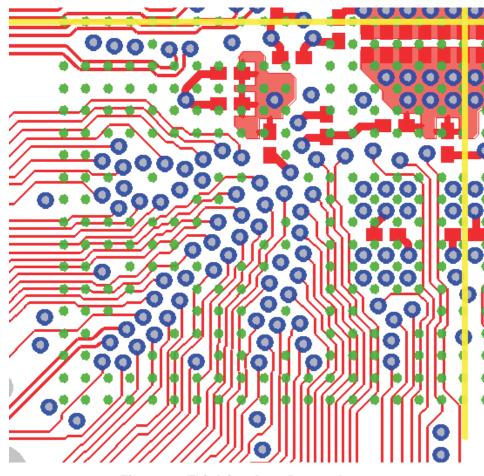

Figure 2 shows the overall routing of the first quadrant. In the following pages it will be broken up into simpler parts.

Figure 2. First Quadrant (Upper Left) Routing (top and bottom layers)

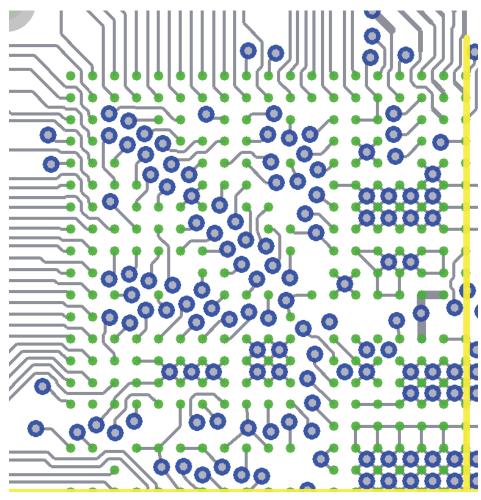

Figure 3. First Quadrant Top Layer

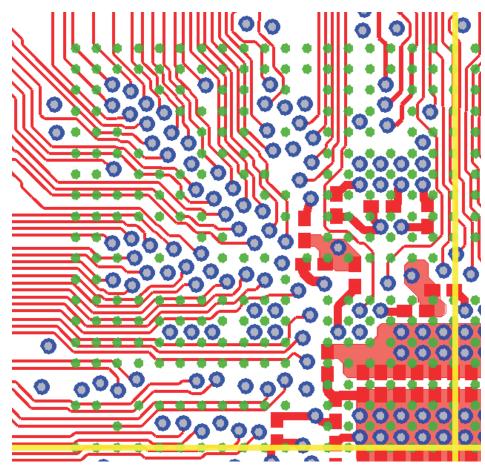

Figure 4. First Quadrant Bottom Layer

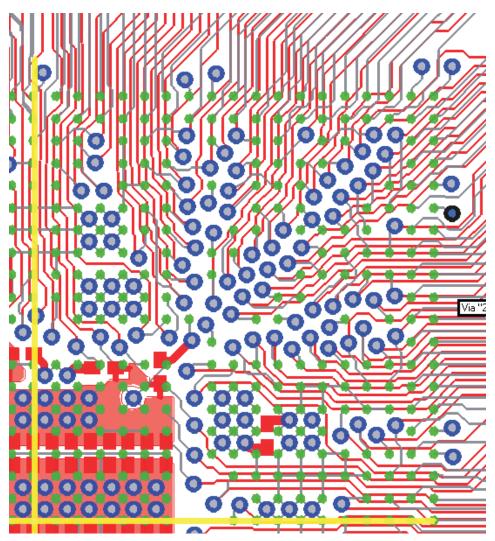

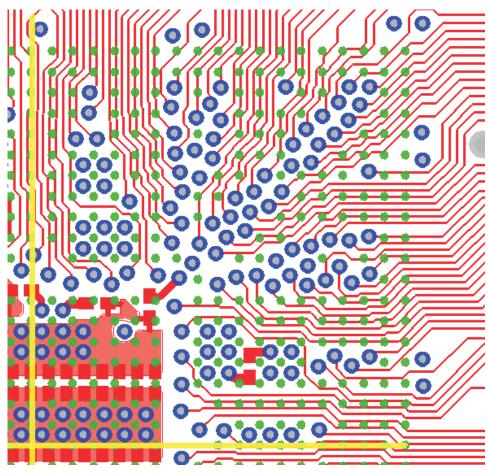

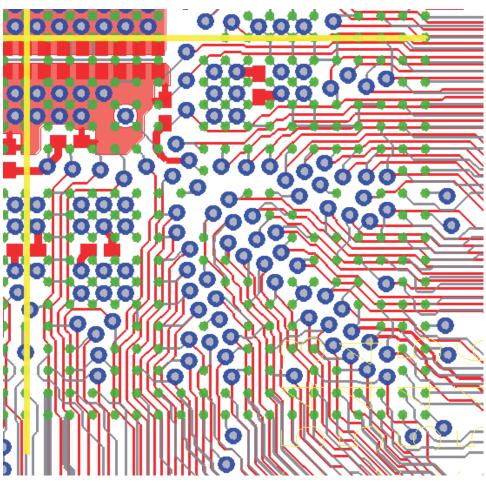

Figure 5. Second Quadrant Routing (top and bottom layers)

DM816x PCB Routing Detail

Figure 6. Second Quadrant Top Layer

Figure 7. Second Quadrant Bottom Layer

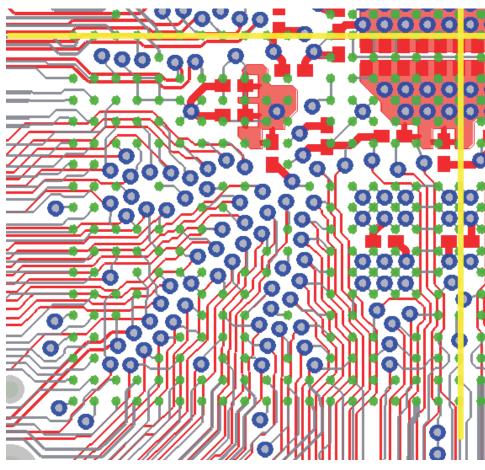

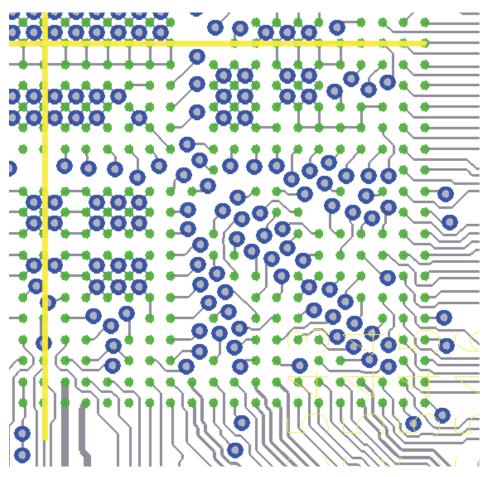

Figure 8. Third Quadrant Routing (top and bottom layers)

Figure 9. Third Quadrant Top Layer

Figure 10. Third Quadrant Bottom Layer

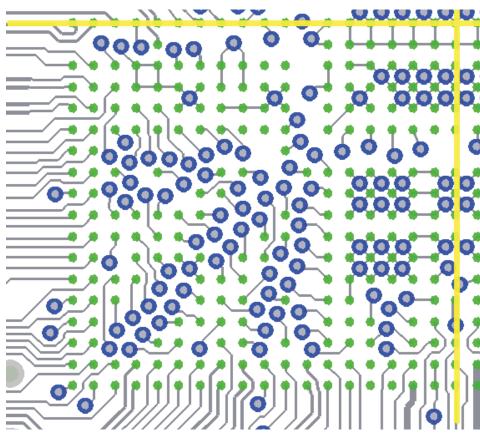

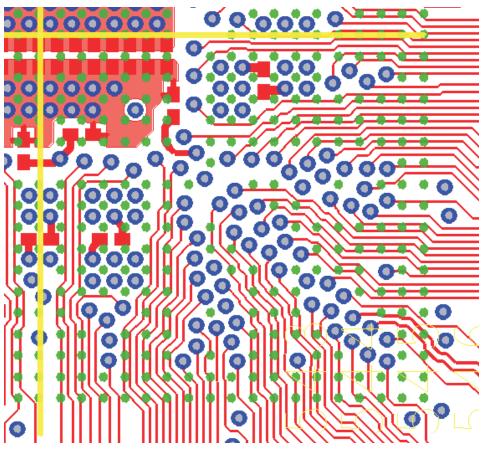

Figure 11. Fourth Quadrant Routing (top and bottom layers)

Figure 12. Fourth Quadrant Top Layer

Figure 13. Fourth Quadrant Bottom Layer

#### 2.2 Special Vias in Power/Gnd Area

Shown here in the center of the chip are vias placed between balls. These vias are only used in the power/ground area between balls of the same net.

It is possible to put vias with a large diameter pad in between four balls of the same net in the power and ground area since the copper pour of this area will take the place of the upper pad. Putting vias with a 20 mil (0.5 mm) pad in between four 0.3 mm ball pads of a 0.65 mm pitch part would normally cause design rule check (DRC) errors because there isn't 0.1 mm of room on all sides for a pad this size. However, since the copper pour of the area takes the place of the pad on the top layer anyway, the size of the top layer pad is not important.

There are several options to avoid an intentional DRC in these cases:

- Turn off the minimum clearance between nets of the same name (Allegro and probably many other CAD tools can do this). This will ignore what would otherwise be clearance violations between two PCB features on the same net. This is suggested as the best option since it doesn't require altering the PCB.

- Define and use a special via in these areas (only in between four balls of the same net) with this stackup:

| Top layer:     | $\rightarrow$ | 16 mil (0.4 mm) diameter via pad                     |

|----------------|---------------|------------------------------------------------------|

| Middle layers: | $\rightarrow$ | 20 mil (0.5 mm) or 18 mil (0.45 mm) diameter via pad |

| Bottom layer:  | $\rightarrow$ | 20 mil (0.5 mm) or 18 mil (0.45 mm) diameter via pad |

| Hole size:     | $\rightarrow$ | 10 mil (0.25 mm) finished hole                       |

A 16 mil (0.4 mm) top layer pad diameter will fit in between four ball pads without a DRC on a 4 mil (0.1 mm) clearance and 20 mil (0.5 mm) lower and bottom layer pad diameters with a 10 mil (0.25 mm) finished hole size. This should not violate most board shop's rules, however, it may be necessary to explain to the board shop that you are not actually designing a 16 mil via pad with a 10 mil hole since the upper pad size does not affect the copper pour.

By doing one of the above it is possible to put in extra power and ground vias to more closely couple the power and ground voltages on the top and power and ground layers.

Now, you are done and ready to route the rest of your design!

## **Revision History**

| Ch | nanges from Original (August 2011) to A Revision P | Page |

|----|----------------------------------------------------|------|

| •  | Update was made in Section 2.2.                    | 16   |

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

| Products                     |                          | Applications                  |                                   |

|------------------------------|--------------------------|-------------------------------|-----------------------------------|

| Audio                        | www.ti.com/audio         | Automotive and Transportation | www.ti.com/automotive             |

| Amplifiers                   | amplifier.ti.com         | Communications and Telecom    | www.ti.com/communications         |

| Data Converters              | dataconverter.ti.com     | Computers and Peripherals     | www.ti.com/computers              |

| DLP® Products                | www.dlp.com              | Consumer Electronics          | www.ti.com/consumer-apps          |

| DSP                          | dsp.ti.com               | Energy and Lighting           | www.ti.com/energy                 |

| Clocks and Timers            | www.ti.com/clocks        | Industrial                    | www.ti.com/industrial             |

| Interface                    | interface.ti.com         | Medical                       | www.ti.com/medical                |

| Logic                        | logic.ti.com             | Security                      | www.ti.com/security               |

| Power Mgmt                   | power.ti.com             | Space, Avionics and Defense   | www.ti.com/space-avionics-defense |

| Microcontrollers             | microcontroller.ti.com   | Video and Imaging             | www.ti.com/video                  |

| RFID                         | www.ti-rfid.com          |                               |                                   |

| OMAP Applications Processors | www.ti.com/omap          | TI E2E Community              | e2e.ti.com                        |

| Wireless Connectivity        | www.ti.com/wirelessconne | ctivity                       |                                   |

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2015, Texas Instruments Incorporated