# TCI6630K2L SoC

High performance, low power solution for indoor enterprise PoE+ small cells and outdoor pico deployments

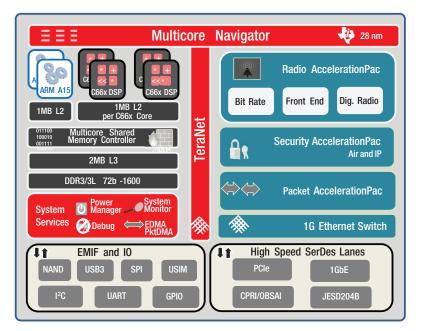

Based on TI's high-throughput KeyStone II architecture, the new TCI6630K2L system-on-chip (SoC) is a scalable low-power baseband solution with an integrated digital radio front end (DRFE) that meets the more stringent power, size and bill of materials (BOM) cost requirements of small cell wireless base stations. In enterprise and pico base stations, the device's dual ARM®/quad DSP cores deliver the processing power that TI's wireless infrastructure solutions are known for and combines this with design innovations that pinpoint the specific set of requirements that small cell base stations present to designers.

To ensure an engaging user experience with their subscribers, wireless service operators are faced with transitioning their infrastructures to more effective heterogeneous networks where 3G/4G and LTE/W-CDMA must seamlessly coexist. Cost-effective and

operationally efficient indoor and outdoor small cells will be a key service delivery layer between the larger macro or metro cells and the much more limited residential or femto cells. Indoor enterprise and outdoor pico cells will play a strategic role in bridging the gap between wide-area and residential service footprints.

# Scalable high-performance small cells

The TCl6630K2L takes the technology break-throughs achieved by the previous generations of TI's wireless infrastructure SoCs and scales them to the special set of requirements of small cell base stations. At the same time, the KeyStone II architecture gives the TCl6630K2L a high degree of scalability within the range of small cells of use cases, from indoor enterprise to outdoor pico cells. The KeyStone II architec-

ture affords the device a powerful framework that ensures the responsiveness that wireless users expect and which they will demand for years to come. At the same time, the scalability, flexibility and versatility of the KeyStone II architecture lends itself to higher levels of integration and system design innovations.

A critical aspect of the scalability of the TCl6630K2L is the consistent and continuous software track that is essential to all of Tl's base station SoCs. In addition to the hardware compatibilities of the KeyStone II architecture, software developed for any KeyStone-based device is scalable upward or downward to other KeyStone SoCs, which include SoCs that support metro and micro base stations. As a result, system providers can reduce software development costs considerably by re-using code across multiple infrastructure systems that target the various segments of the marketplace.

## Key Features

- Highly flexible and scalable from indoor enterprise to outdoor pico base stations

- Low power Meets Power over Ethernet Plus (PoE+) budget in many applications

- Supported by the same continuous software track from enterprise/pico to metro and micro base stations

- Integrated digital radio technology (Crest Factor Reduction, Digital Pre-Distortion) allows for more efficient and cost-effective power amplifiers

- Supports heterogeneous networks with carrier aggregation and dual-mode functionality

- Highly integrated to reduce BOM costs, system size, power consumption

- Targeted at small cells without sacrificing powerful processing cores

- Two ARM<sup>®</sup> Cortex<sup>™</sup>-A15 RISC cores

- Four TMS320C66x DSP cores with fixed- and floating-point processing

- KeyStone II architecture with extremely high throughput speeds optimizes processing cores

- High-speed JESD204B chip-to-chip interface optimizes board layout (fewer lanes, fewer pins) and reduces power consumption

- Advanced integrated network coprocessor offloads ARM/DSP cores, allowing greater system differentiation

# Integrated digital radio front end

To date, base station architectures have mostly featured discrete implementations of the DRFE, which has often been deployed in multiple discrete devices or even in an enclosure separate from the baseband processing block. Moving forward, small cell designs will require compact low-power enclosures with limited, if any, airflow. Simpler board designs with greater integration of components will be needed to achieve both the lower capital expenditure (capex) and operational expenditure (opex) goals dictated by the introduction of many new small cells into networks long dominated by macro-size cells.

In response to these requirements, the TCl6630K2L is the first wireless infrastructure SoC to integrate the functionality of a DRFE

on-chip. By taking this approach, as well as by developing additional innovations involving a new more efficient chip-to-chip interface, advanced coprocessor capabilities and others, the TCl6630K2L SoC is able to meet the low power, lower cost and simpler design requirements of small cells.

By integrating the DRFE, the TCl6630K2L SoC combines all the high-throughput digital processing into one optimized processing unit, including control, baseband and DRFE. As a result, the SoC is able to perform a variety of functions on-chip, such as the fundamental signal-processing functions like channelization and re-sampling, as well as channel aggregation and distribution, which are essential to heterogeneous networks and dual-mode operations.

Combining many of the DRFE functions with the baseband processing allows for the data conversion and RF up/down conversion processing to be integrated into another radio SoC that is fabricated with a process node more compatible with performance analog and RF operations. In addition, the DRFE capabilities on the TCl6630K2L SoC have been augmented with advanced analog/RF impairment correction algorithms that can interface with analog radio processing and improve the efficiencies and cost-effectiveness of the particular power amplifier (PA) deployed in a small cell design. The two most RF critical impairment correction algorithms are crest factor reduction (CFR) and digital pre-distortion (DPD).

#### • Crest Factor Reduction (CFR)

CFR is a signal-processing algorithm that affects a signal's peak-to-average ratio (PAR). Since selection of the system's PA must accommodate the greatest PAR expected, reducing the PAR can decrease the size and improve the power efficiency of the system's PA by as much as 400 percent, reducing the overall power consumption of the system and the cost of the PA significantly. The CFR algorithm reduces the PAR by introducing noise into the signals within certain limits. The TCI6630K2L's CFR module includes advanced features like multiple stages of peak cancellation with provisions to estimate fractional peaks and limit over

▲ KeyStone II-based SoC with integrated digital radio functionality

cancellation, automatic estimation of the CFR cancellation pulse shapes based on signal spectral content monitoring, dynamic threshold adjustments and automatic gain control loops.

## • Digital Pre-Distortion (DPD)

DPD is a way to coax more linear performance from the system's PA. The power efficiency of PAs decrease or drift away from an ideal linear performance line as the device approaches its peak drive point (also known as its saturation point). When the PA is not operating efficiently, it wastes power – increasing the overall power consumption of the system - and generates excessive heat, which in turn complicates the thermal management issues for the system designer. DPD allows the PA to operate more efficiently longer along a more linear performance path as it approaches its peak drive point. This opens up a wider array of PAs for the small cell system designer to choose from, including more cost-effective devices which reduce the system's BOM. At the same time, more than adequate margin is provided for system performance.

# Simplifying small cell designs

The sheer number of small cells needed in a seamless heterogeneous network will necessitate simple, very cost-effective system designs. In addition to greater integration at

the silicon level, circuit board design and layoutcan be simplified to reduce BOM and board production costs. A new serial communications link interface, which conforms to the JESD204B standard from JEDEC, achieves this simplification.

JESD204B provides for a high-throughput, low-pin-count serial link between analog-todigital (ADC) and digital-to-analog (DAC) converters, and on-board logic devices such as field programmable gate arrays (FPGA), digital signal processors (DSPs), SoCs, application specific integrated circuits (ASIC) and others. By embedding the clock in the data stream and including certain embedded algorithms to optimize the sampling of data bits, JESD204B is able to simplify routing between devices because significantly fewer lanes are needed on the board. To achieve the same throughput as JESD204B, for example, the more prominent SerDes interfaces, such as PCI Express (PCIe) and the Common Public Radio Interface (CPRI), would require more lanes on the board. This reduces the number of input/output (I/O) channels on devices, reducing pin counts and enabling smaller packages. In addition to simplifying system design, JESD204B shortens circuit board bring-up by reducing the setup/ hold times that are usually performed across the many more lanes typically employed by other SerDes interfaces like PCle and CPRI that are based on low-voltage differential signaling (LVDS) pairs. JESD204B is a flexible and scalable serial link interface that can accommodate a wide range of data transfer speeds and configurations, such as multiple ADCs or DACs on one JESD differential pair.

Other capabilities of the TCl6630K2L SoC that can have a profound effect on simplifying small cell designs are the coprocessors which can offload much of the processing load from the ARM and DSP cores, or eliminate the need for additional external processors without increasing the complexity of the system. For example, adding a discrete network processor to the system would mean adding the device itself as well as its associated memory, clock and power management functionality.

The TCl6630K2L SoC's integrated Network Coprocessor (NCP) can perform all of the transport network termination, and packet and security processing of a traditional network processor as well as all operations and management functions. The NCP includes a packet accelerator as well as extensive security accelerators supporting both the IPSec encryption algorithm for wireline connections and various wireless protocol encryption packages. Additionally, the TCl6630K2L SoC's NCP has been enhanced with the integration of an Ethernet switching element on-chip, eliminating the need for an external and costly switching device.

# Integrated digital radio front end

Various aspects of the TCl6630K2L SoC not only make it a low-power device, but its various capabilities such as the integrated DRFE reduce the overall power consumption of the entire small cell system. As a result, single-carrier dual-band or dual-mode system configurations based on the TCl6630K2L SoC will meet the power budget of Power over Ethernet Plus (PoE+), an important consideration in some use cases such as enterprise applications where a small cell base station may be deployed inside a building and connected to the facility's Ethernet network. With PoE. the small cell can be powered by and have wide area access to the Internet via one Ethernet cable, simplifying deployment and installation issues. At the same time, the TCl6630K2L SoC is a scalable solution, capable of supporting architectures beyond single-carrier systems. In fact, the advanced features of the TCl6630K2L SoC will support carrier aggregation where two channels of a certain carrier like LTE are

combined in the same bandwidth or dual mode where LTE and WDMA channels can be combined in the same bandwidth. In both cases network capacity is efficiently maximized.

TCl6630K2L SoC is the latest in TI's long line of the industry's lowest-power wireless base station and infrastructure SoCs. Similar to the devices before it, the TCl6630K2L SoC has achieved its exceedingly low power consumption through a combination of process technologies, TI's SmartReflex™ low-power technology and innovative power management techniques, such as dynamic voltage, frequency scaling, memory retention until access, power and clock gating, and others.

# Scalable solutions based on KeyStone II

The KeyStone II architecture on which the TCI6630K2L SoC is based affords the SoC considerable scalability and flexibility within the device itself, but sharing the same base architecture with other communications infrastructure SoCs enables scalability beyond the TCI6630K2L SoC to larger, more powerful SoCs such as the TCI6636 SoC for metro and micro small cells.

The key objective behind the KeyStone II architecture is to provide more than enough throughput and on-chip resources such that the processing cores will be able to reach their optimum processing performance without constraints. Referred to as multicore "entitlement", this empowering of the processing cores is ensured by the architecture's ability to provide non-blocking access to all processing cores, peripherals, coprocessors and I/O channels. Some of the key aspects of the KeyStone architecture are its Multicore Navigator, TeraNet, Multicore Shared Memory Controller and HyperLink.

The **Multicore Navigator** controls and abstracts the connections among the various subsystems that make up the KeyStone architecture and the particular SoC. This innovative packet-based manager has a unified interface for communications, data transfers and job management. While delivering higher system performance, it ensures fewer interrupts and reduces the complexity of software because of its "fire-and-forget" action model.

**TeraNet** – a hierarchal switch fabric –

delivers more than two terabits of data bandwidth within the TCl6630K2L SoC. This virtually guarantees that the cores and coprocessors are never idle because of data communication latencies. As a result, each processing element is able to operate at its optimum rate. Since theTeraNet switch fabric is hierarchical instead of a flat crossbar, overall power consumption is much lower in idle states and systems latency is minimized. Low latency is a key requirement of next-generation base stations, large and small.

With the **Multicore Shared Memory Controller (MSMC)** cores can directly access shared memory without adding traffic to the TeraNet. Instead, MSMC eliminates memory contention by arbitrating accesses to shared memory among the cores and other processing elements. Highly effective pre-fetch mechanisms for code and data make accesses to shared memory nearly the same in latency as accesses to local L2 memory.

The **DDR3 external memory interface (EMIF)** on the TCl6630K2L SoC is made up of one 1,600-MHz, 72-bit buses supporting as much as 8 GB of addressable memory space. With its direct connection to the MSMC, the DDR3 EMIF is able to reduce any latency associated with external memory fetches and provide the speed needed for large data transfers, which is essential for advanced 3G and 4G base stations.

Enabling an extensible and scalable system architecture, the TCl6630K2L SoC has two **HyperLink** interfaces for high-speed communication with other KeyStone devices. Each HyperLink supports a bandwidth of up to 100 Gbps with low protocol overhead. HyperLink functions in conjunction with the Multicore Navigator, dispatching processing tasks to any available device transparently, so that the task executes as if it were running on local resources.

# **Powerful core performance**

The KeyStone II architecture leverages advanced 28-nm technology for improved cost efficiency through the integration of multiple RISC cores and DSP cores and lower system power consumption.

The two ARM® Cortex<sup>™</sup>-A15 RISC cores provide high-performance RISC processing at ultra-low power consumption levels. The four

TMS320C66x DSP cores integrated into the TCl6630K2L SoC provide programmable performance supported by a variety of co-processors specializing in packet, symbol and bit-rate processing so that base station manufacturers can easily support a mix of W-CDMA and LTE users in heterogeneous networks.

Because the C66x DSP cores are capable of both fixed- and floating-point capabilities, each core can perform up to five times faster than a traditional floating-point core. In addition, the development and debugging cycle time for complex algorithms is significantly reduced from a multiple-month cycle to just a few days. The C66x DSP cores include 90 instructions targeted for floating-point and vector-math-oriented processing.

# **Complete tools and support**

TI has developed a range of tools and support capabilities that save base station suppliers time, resources and development budget so that these resources can be allocated to

developing differentiating capabilities in their own systems. A prime example of this is the complete Physical layer (PHY) for single- and dual-mode LTE and W-CDMA small cells that is included in TI's Base Station SoftwarePac. The availability of a production-ready PHY eliminates one of the most complex tasks of base station design. To facilitate seamless integration with a complete LTE or W-CDMA stack the interface to the SoftwarePac's PHY software is compliant with the Femto Application Platform Interface (FAPI), as defined by the Small Cell Forum. In addition, the design of the PHY is modular and open so customers can differentiate within the PHY by incorporating proprietary algorithms that may be critical to product differentiation. As a result of the PHY's flexible design, base station manufacturers can easily customize their products to meet the needs of different network operators.

Other development tools include TI's well known Code Composer Studio™ (CCStudio)

integrated development environment (IDE). a full suite of best-in-class Eclipse-based development and debugging tools. CCStudio IDE features a C compiler, Assembly optimizer to simplify programming and scheduling and a Windows® debugger for visibility into source code execution. The compiler generates highly efficient code that is first-pass efficient, reducing the need to optimize code. The debugging tools help designers get products to market faster while saving development resources by visualizing problems and finding solutions guickly. In addition, an evaluation module (EVM) is available to facilitate rapid development of prototypes. All of these tools integrate with the ARM® RISC cores as well so that designers can guickly and efficiently develop code for all subsystems within a single IDE platform.

## For more information

To learn more about the TCl6630K2L SoC visit www.ti.com/multicore.

# TI Worldwide Technical Support

### Internet

TI Semiconductor Product Information Center Home Page support.ti.com

TI E2E™ Community Home Page

e2e.ti.com

#### **Product Information Centers**

**Americas** Phone +1(512) 434-1560 Brazil Phone 0800-891-2616 Mexico Phone 0800-670-7544 Fax +1(972) 927-6377

Internet/Email support.ti.com/sc/pic/americas.htm

### Europe, Middle East, and Africa

00800-ASK-TEXAS European Free Call (00800 275 83927) International +49 (0) 8161 80 2121 +7 (4) 95 98 10 701 Russian Support

Note: The European Free Call (Toll Free) number is not active in all countries. If you have technical difficulty calling the free call number, please use the international number above.

+(49) (0) 8161 80 2045 Fax Internet www.ti.com/asktexas Direct Email asktexas@ti.com

Japan

Phone Domestic 0120-92-3326 Fax International +81-3-3344-5317 Domestic 0120-81-0036 Internet/Fmail International support.ti.com/sc/pic/japan.htm Domestic www.tij.co.jp/pic

## Asia

Phone International +91-80-41381665 Domestic Toll-Free Number Note: Toll-free numbers do not support

mobile and IP phones

1-800-999-084 Australia China 800-820-8682 800-96-5941 Hong Kong India 1-800-425-7888 Indonesia 001-803-8861-1006 Korea 080-551-2804 Malaysia 1-800-80-3973 New Zealand 0800-446-934 **Philippines** 1-800-765-7404 800-886-1028 Singapore Taiwan 0800-006800 001-800-886-0010 Thailand

Fax +8621-23073686 Email tiasia@ti.com or ti-china@ti.com Internet support.ti.com/sc/pic/asia.htm

**Important Notice:** The products and services of Texas Instruments Incorporated and its subsidiaries described herein are sold subject to TI's standard terms and conditions of sale. Customers are advised to obtain the most current and complete information about TI products and services before placing orders. TI assumes no liability for applications assistance, customer's applications or product designs, software performance, or infringement of patents. The publication of information regarding any other company's products or services does not constitute TI's approval. warranty or endorsement thereof.

B090712

The platform bar and E2E are trademarks of Texas Instruments. All other trademarks are the property of their respective owners.

#### IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

Products Applications

Audio www.ti.com/audio Automotive and Transportation www.ti.com/automotive Communications and Telecom **Amplifiers** amplifier.ti.com www.ti.com/communications **Data Converters** dataconverter.ti.com Computers and Peripherals www.ti.com/computers **DLP® Products** www.dlp.com Consumer Electronics www.ti.com/consumer-apps

DSP **Energy and Lighting** dsp.ti.com www.ti.com/energy Clocks and Timers www.ti.com/clocks Industrial www.ti.com/industrial Interface interface.ti.com Medical www.ti.com/medical logic.ti.com Logic Security www.ti.com/security

Power Mgmt power.ti.com Space, Avionics and Defense www.ti.com/space-avionics-defense

Microcontrollers <u>microcontroller.ti.com</u> Video and Imaging <u>www.ti.com/video</u>

RFID www.ti-rfid.com

OMAP Applications Processors <a href="www.ti.com/omap">www.ti.com/omap</a> TI E2E Community <a href="e2e.ti.com">e2e.ti.com</a>

Wireless Connectivity <u>www.ti.com/wirelessconnectivity</u>