## **CC2533 Silicon Errata**

# **Errata**

Literature Number: SWRZ034A June 2010–Revised October 2014

### **Contents**

| 1     | Introduction |                                                  | 4 |

|-------|--------------|--------------------------------------------------|---|

|       | 1.1          | Device and Development Support Tool Nomenclature | 4 |

|       | 1.2          | Device Markings                                  | 4 |

| 2     | Known        | Design Exceptions to Functional Specifications   | 5 |

| Revis | sion Hist    | ory                                              | 8 |

#### www.ti.com

### List of Figures

| 1              | Example of Device Markings     | 4 |  |

|----------------|--------------------------------|---|--|

| 2              | Example of Device Nomenclature | 5 |  |

| List of Tables |                                |   |  |

| 1              | Advisory List                  | 5 |  |

## CC2533 Silicon Errata

#### 1 Introduction

This document describes the known exceptions to functional specifications of the indicated devices.

The advisory numbers in this document may not be sequential. Some advisories may not be numbered. Some advisories may be moved to the next revision and others may have been removed and documented in the data sheet. When items are moved or deleted, the remaining numbers remain the same and are not resequenced.

#### 1.1 Device and Development Support Tool Nomenclature

To designate the stages in the product development cycle, TI assigns prefixes to the part numbers. These prefixes represent evolutionary stages of product development from engineering prototypes through fully qualified production devices

| X    | Experimental, preproduction, sample or prototype device. Device may not meet<br>all product qualification conditions and may not fully comply with TI<br>specifications. Experimental/Prototype devices are shipped against the<br>following disclaimer: "This product is still in development and is intended for<br>internal evaluation purposes." Notwithstanding any provision to the contrary, TI<br>makes no warranty expressed, implied, or statutory, including any implied<br>warranty of merchantability of fitness for a specific purpose, of this device. |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| null | Device is qualified and released to production. TI 's standard warranty applies to production devices.                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

#### 1.2 Device Markings

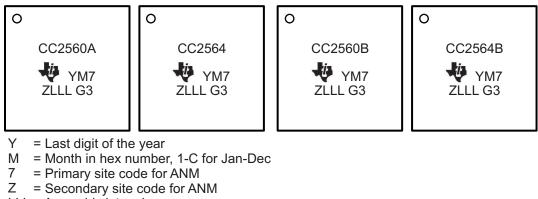

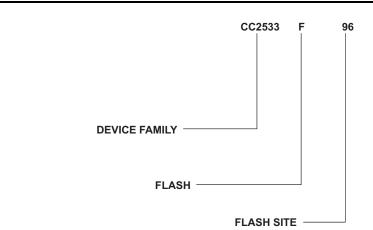

Figure 1 provides an example of the Concerto device markings and defines each of the markings. The device revision can be determined by the symbols marked on the top of the package as shown in Figure 1. Some prototype devices may have markings different from those illustrated. Figure 2 shows an example of the device nomenclature.

- LLL = Assembly lot code

- O = Pin 1 indicator

#### Figure 1. Example of Device Markings

All trademarks are the property of their respective owners.

A The additional 256KB is added to the Cortex<sup>™</sup>-M3 core (Connectivity Devices) or to the C28x<sup>™</sup> core (Base Devices).

#### Figure 2. Example of Device Nomenclature

#### 2 Known Design Exceptions to Functional Specifications Table 1. Advisory List

Issue 1 DMA Variable Transfer Length with Length 0 or 1 All revisions affected **Revision(s)** Affected Details Depending on which VLEN mode is used, attempting a variable length transfer with length 0 or 1 can lead to erroneous behavior by the DMA. The failing conditions will not occur naturally in an application as they do not transfer useful data, but may occur as the result of an error condition at the source of the DMA transfer. The DMA is generally set up with variable transfer length to transfer packets that come in over USART or RF. If there is an error in the medium, these packets may be malformatted. If they for example contain a length byte of 0, using the DMA to transfer those packets automatically without taking the described precautions may lead to a buffer overrun. The two VLEN modes that are affected are VLEN values 001 and 010. VLEN values 000, 011 and 100 work without restrictions. In VLEN modes VLEN = 001 and VLEN = 010, the DMA transfers a number of bytes/words based on the value of the first byte/word it reads from the source (the length byte/word). In the event that a transfer is started with a length byte/word of 0 or 1, the wrong number of bytes will be transferred and the DMA interrupt may be lost. The failure mode depends on whether byte or word mode is selected for the transfer as described in

| -    |                                                                                                        |                                                                                                              |                                                                                                                                                                                                                                                                                                                                 |

|------|--------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VLEN | Byte Mode                                                                                              | Word Mode                                                                                                    | Comment                                                                                                                                                                                                                                                                                                                         |

| 000  | ОК                                                                                                     | OK                                                                                                           |                                                                                                                                                                                                                                                                                                                                 |

| 001  | Two bytes transferred when length byte is<br>0                                                         | Two words<br>transferred when<br>length word is 0                                                            | Can be used if contents of length<br>byte/word in source buffer can be<br>checked not to be 0 or 1 before DMA is<br>triggered, or if an extra transfer to<br>destination is acceptable.                                                                                                                                         |

| 010  | Excessive number of bytes transferred<br>when length byte is 0 Extra transfer when<br>length byte is 1 | Two transfers<br>executed when<br>length word is 0 or 1<br>Interrupt not raised<br>when length word is<br>0. | Byte mode can be used if contents of<br>length byte in source buffer can be<br>checked not to be 0 or 1 before DMA is<br>triggered.Word mode can be used if<br>contents of length word in source buffer<br>can be checked not to be 0 or 1 before<br>DMA is triggered, or if an extra transfer to<br>destination is acceptable. |

| 011  | ОК                                                                                                     | OK                                                                                                           |                                                                                                                                                                                                                                                                                                                                 |

| 100  | ОК                                                                                                     | OK                                                                                                           |                                                                                                                                                                                                                                                                                                                                 |

#### **DMA Variable Lenght Restrictions**

DMA Variable Lenght Restrictions .

Workaround(s) Please observe the comments for each of the affected modes in order to use them without issues. Alternatively, any of the unaffected VLEN modes can be used if the buffer sizes are adjusted accordingly.

Issue 2 Timer 2 (MAC Timer) Read Latching

Revision(s) Affected All revisions affected

Details In Timer 2, the value of T2M1 is latched when T2M0 is read, and the values of T2MOVF1 and T2MOVF2 are latched when T2MOVF0 is read. This does not work as expected when the least significant byte read is 0xFF. When the timer is read on the cycle where the least significant byte is about to wrap around, the latched values are captured one cycle later. This means that the latched registers are incremented while the register that was read first (T2M0 or T2M0VF0) is not.

**Workaround(s)** To read Timer 2 overflow: Use T2CTRL.LATCH\_MODE = 1 and read T2M0 to trigger latching. Then read the overflow counter and ignore the result of the T2M0 read. To read Timer 2 counter: Read T2M0 first. If T2M0 == 0xFF, read timer once more to confirm its state.

| www.ti.com           | Known Design Exceptions to Functional Specifications                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Issue 3              | Watchdog Timer Counts Too Fast when System Clock Division is Enabled                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| Revision(s) Affected | All revisions affected                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| Details              | If system clock division is used (CLKCONCMD.CLKSPD $\neq$ CLKCONCMD.OSC) the Watchdog timer will count too fast. If clock division is used, for each 32 kHz clock cycle, the Watchdog timer will count more than one period. The number of periods counted is proportional to the amount of division.                                                                                                                                           |  |  |  |

| Workaround(s)        | If clock division is used, a proportionally larger WDT timeout should be used if possible.                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| Issue 4              | Leaving PM2/3 can produce glitches on the SCL and SDA pins                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| Revision(s) Affected | All revisions affected                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| Details              | Glitches can occur on the SCL and SDA pins when leaving PM2/3.The I2C pins SCL<br>and SDA should be high impedance with pull-up when not transmitting on the I2C bus.<br>This issue can cause a low pulse for approximately 250 ns when going from PM2/3 to<br>Active Mode. This is due to an insufficient reset of the I2C module when exiting PM2/3.                                                                                          |  |  |  |

| Workaround(s)        | To prevent these glitches, the I2C pin override bit (I2CWC.OVR) can be set before<br>entering PM2. This bit overrides the I2C module's control of the I/O lines and sets them<br>to the state defined in I2CWC. They should then be left in the reset state for I2CWC<br>which is input with pull-up enabled. The I2CWC.OVR bit can be cleared just after<br>returning to Active mode. This prevents any glitches from propagating to the pins. |  |  |  |

**Revision History**

www.ti.com

#### **Revision History**

| Cł | Changes from June 1, 2014 to October 3, 2014 Page                         |     |  |  |

|----|---------------------------------------------------------------------------|-----|--|--|

| •  | Added Updated to new standards                                            | . 7 |  |  |

| •  | Added Issue 4, Leaving PM2/3 can produce glitches on the SCL and SDA pins | . 7 |  |  |

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

| Products                     |                          | Applications                  |                                   |

|------------------------------|--------------------------|-------------------------------|-----------------------------------|

| Audio                        | www.ti.com/audio         | Automotive and Transportation | www.ti.com/automotive             |

| Amplifiers                   | amplifier.ti.com         | Communications and Telecom    | www.ti.com/communications         |

| Data Converters              | dataconverter.ti.com     | Computers and Peripherals     | www.ti.com/computers              |

| DLP® Products                | www.dlp.com              | Consumer Electronics          | www.ti.com/consumer-apps          |

| DSP                          | dsp.ti.com               | Energy and Lighting           | www.ti.com/energy                 |

| Clocks and Timers            | www.ti.com/clocks        | Industrial                    | www.ti.com/industrial             |

| Interface                    | interface.ti.com         | Medical                       | www.ti.com/medical                |

| Logic                        | logic.ti.com             | Security                      | www.ti.com/security               |

| Power Mgmt                   | power.ti.com             | Space, Avionics and Defense   | www.ti.com/space-avionics-defense |

| Microcontrollers             | microcontroller.ti.com   | Video and Imaging             | www.ti.com/video                  |

| RFID                         | www.ti-rfid.com          |                               |                                   |

| OMAP Applications Processors | www.ti.com/omap          | TI E2E Community              | e2e.ti.com                        |

| Wireless Connectivity        | www.ti.com/wirelessconne | ctivity                       |                                   |

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2014, Texas Instruments Incorporated