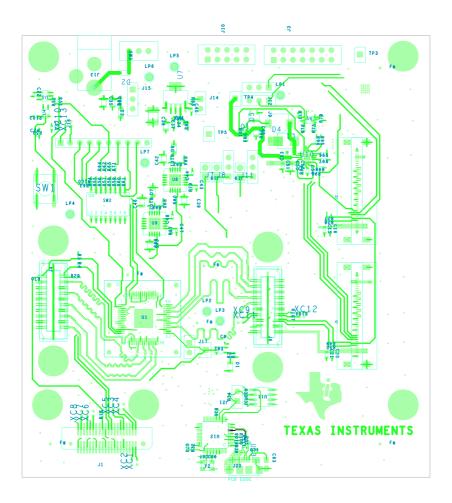

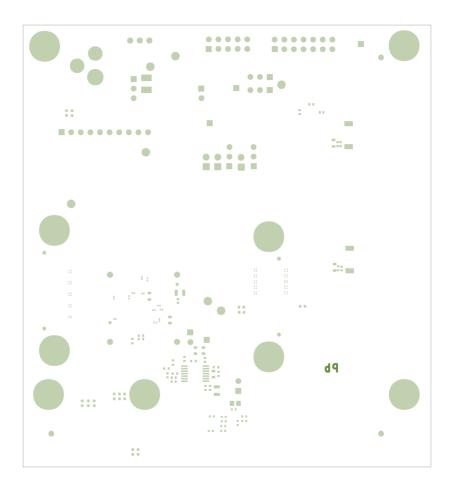

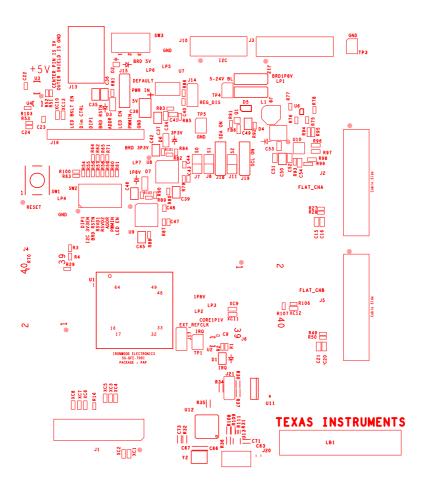

ART FILM - BOTTOM\_SILK

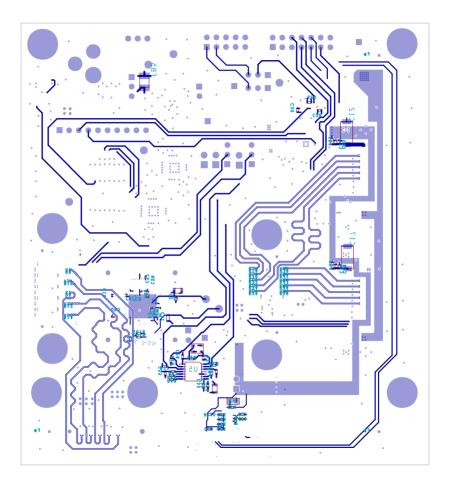

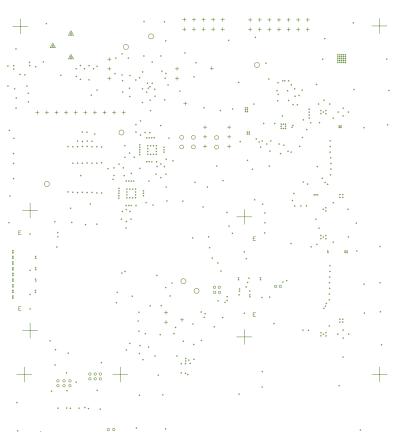

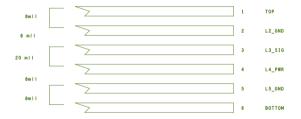

|        | DRILL CH/ | ART: TOP to BOT   | ТОМ          |     |

|--------|-----------|-------------------|--------------|-----|

|        | ALL UN    | ITS ARE IN MILS   | )            |     |

| FIGURE | SIZE      | TOLERANCE         | PLATED       | QTY |

|        | 5.0       | + 3 . 0 / - 3 . 0 | PLATED       | 55  |

|        | 6.0       | + 3 . 0 / - 3 . 0 | PLATED       | 60  |

|        | 8.0       | + 3 . 0 / - 3 . 0 | PLATED       | 501 |

| o      | 16.0      | + 3 . 0 / - 3 . 0 | PLATED       | 26  |

| +      | 38.0      | + 3 . 0 / - 3 . 0 | PLATED       | 51  |

| 0      | 40.0      | + 3 . 0 / - 3 . 0 | PLATED       | 6   |

| 0      | 43.0      | + 3 . 0 / - 3 . 0 | PLATED       | 3   |

| 0      | 52.0      | + 3 . 0 / - 3 . 0 | PLATED       | 7   |

| *      | 120.0     | + 3 . 0 / - 3 . 0 | PLATED       | 2   |

| ۵      | 140.0     | + 3 . 0 / - 3 . 0 | PLATED       | 1   |

| +      | 160.0     | + 3 . 0 / - 3 . 0 | PLATED       | 9   |

|        | 33.465    | + 3 . 0 / - 3 . 0 | NON - PLATED | 2   |

|        | 39.37     | + 3 . 0 / - 3 . 0 | NON - PLATED | 1   |

| E      | 40.0      | + 3 . 0 / - 3 . 0 | NON - PLATED | 4   |

|        | 51.181    | + 3 . 0 / - 3 . 0 | NON - PLATED | 1   |

|        | 63.386    | + 3 . 0 / - 3 . 0 | NON-PLATED   | 4   |

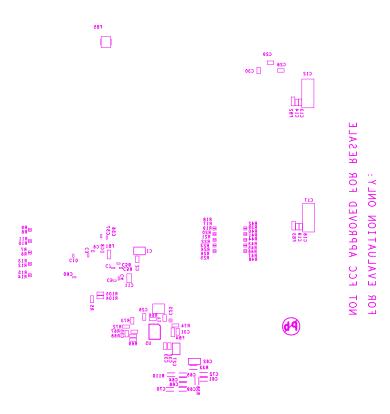

ART FILM - NOTES

ART FILM - NOTES

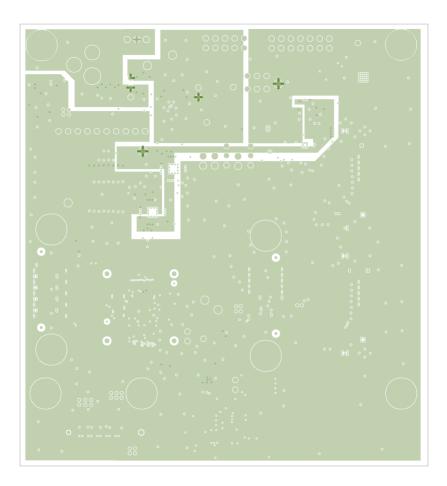

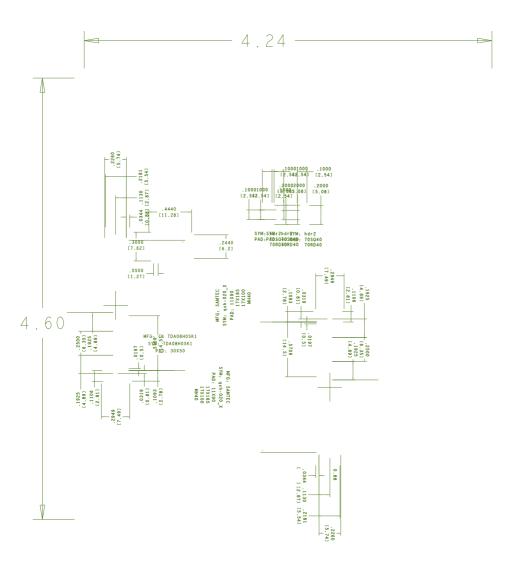

ART FILM - OUTLINE

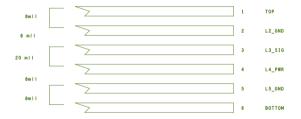

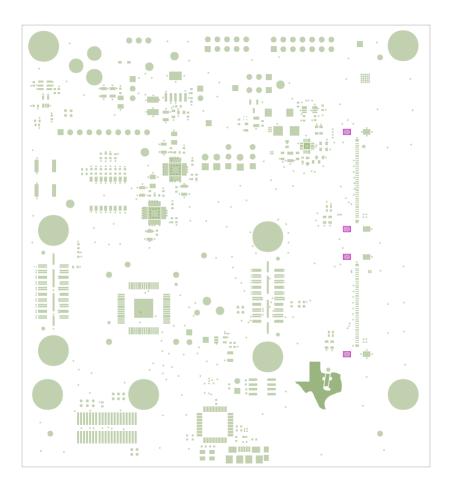

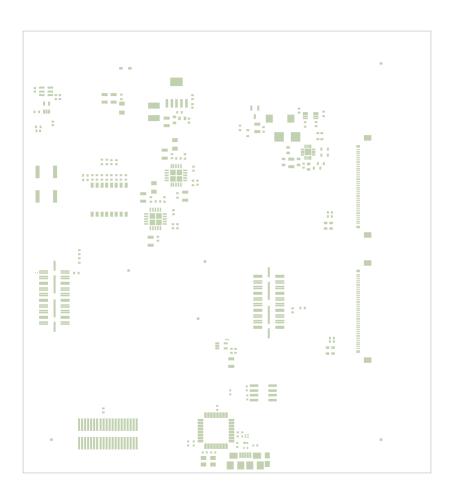

## ALL FABRICATION ITEMS MUST MEET OR EXCEED BEST INDUSTRY PRACTICE : IPC-A-600C (Commercial std.) LAMINATE MATERIAL : FR4 POLYCLAD 370 or EQUIVALENT COPPER WEIGHT : 10Z START INTERNAL, 1/20Z START EXTERNAL FINISHED BOARD THICKNESS : .062 +/- 10% MAXIMUM WARP AND TWIST TO BE : .005 INCH PER INCH MINIMUM COPPER WALL THICKNESS OF PLATED-THRU HOLES TO BE .001 INCH. THERE MUST BE 1MIL OR GREATER PLATING ON EACH SIDE OF THE BARREL WHEN VIEWED IN THE CROSS SECTION MINIMUM ANNULAR RING OF PLATED-THRU HOLES TO BE .002 INCH 1. 2.3. 4. 6. MINIMUM ANNULAR RING OF PLATED-THRU HOLES TO BE .002 INCH MINIMUM ALLOWABLE LINE REDUCTION TO BE 20% OR .002 WHICHEVER IS GREATER 0.003 AND 0.005 SIGNAL LINES ON LAYER 1 & 3 & 6 TO BE IMPEDANCE CONTROLLED 100 OHMS DIFFERENTIAL \*7- 10% 0.014 SIGNAL LINES ON LAYER 1 & 3 & 6 TO BE IMPEDANCE CONTROLLED 50 OHMS \*7- 10% 0.014 SIGNAL LINES ON LAYER 1 & 3 & 6 TO BE IMPEDANCE CONTROLLED 50 OHMS \*7- 10% 11. DIELECTRIC CONSTANTS ARE PREPREG : 4.1 12. Via's in SMT device pads to be filled with Non Conductive Epoxy. ANY VOID IN THE FILL MATERIAL MUST NOT BE GREATER THAN 25% OF THE FINISHED HOLE DIAMETER 13. A CROSS SECTION MOUNT AND DIGITAL PHOTO'S OF VIA'S TO BE PROVIDED 14. USE THE (DRPP) DUTCH REVERSE PLATING PROCESS 7. 15. VIAS will be tented. 16. ALL BOARDS MUST MEET OR EXCEED UL94-VO REQUIREMENTS. PCB MUST BEAR THE UL94V-0 UL REGISTERED MATERIALID NUMBER. PROCESS NOTES 1. CIRCUITRY ON OUTER LAYERS TO BE PLATED WITH : NICKEL GOLD 2. SOLDERMASK BOTH SIDES PER ARTWORK : BLUE LPI 3. SILKSCREEN BOTH SIDES PER ARTWORK : COLOR = WHITE Layout Notes 1. For all differential pairs(DSI and LVDS) in this design follow the guidelines decribed below Route together with controlled differential 100ohm impedance and controlled single 50ohm impedance. Keep away from other high speed signals especially all FlatA/FlatB\* signals. Keep lengths within 5mil of each other. Keep traces on layers adjacent to the ground plane. Keep number of VIAS to minimum. If VIAS used make it symetrical through all signals. Keep diff pairs separated at least by x3 of the trace width NO STUBS on the signal path, components should be placed such that the signals can routed in pass-thru manner 2. Bypass caps (C1 to C8 and C56 to C60 ) and FB1 should be placed close to U1 (SN65DSI85) 3. Place R105 and R104 as near as possible to REFCLK terninal on U1 4. R104 and R105 have a shared footprint node. 5. Bypass caps (C12 to C16) and FB2 should be placed close to J2 6. Bypass caps (C17 to C21) and FB3 should be placed close to J5 7. Caps C22 and C23 should be placed close to U3 8. R67 to R693 should be placed close to U5 9. Caps C28, C29 and C30 should be placed close to U6

GENERAL NOTES. UNLESS OTHERWISE SPECIFIED

10. Place TP3. TP5, LP4, LP5 as convenient for oscilloscope probe grounds

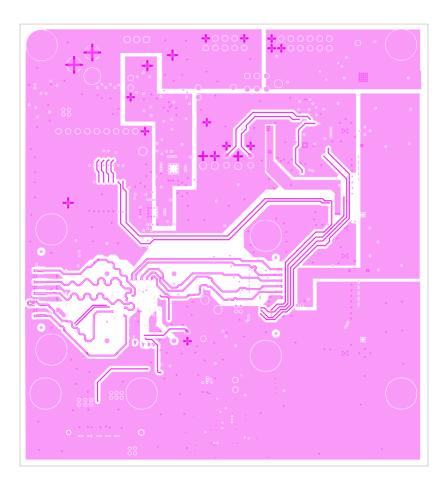

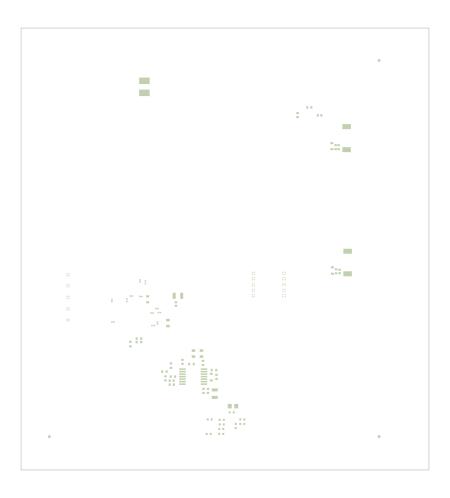

ART FILM - TOP\_PASTE

ART FILM - TOP\_PASTE

ART FILM - TOP\_SILK

## ART FILM - anotation

ART FILM - anotation

## IMPORTANT NOTICE FOR TI DESIGN INFORMATION AND RESOURCES

Texas Instruments Incorporated ('TI") technical, application or other design advice, services or information, including, but not limited to, reference designs and materials relating to evaluation modules, (collectively, "TI Resources") are intended to assist designers who are developing applications that incorporate TI products; by downloading, accessing or using any particular TI Resource in any way, you (individually or, if you are acting on behalf of a company, your company) agree to use it solely for this purpose and subject to the terms of this Notice.

TI's provision of TI Resources does not expand or otherwise alter TI's applicable published warranties or warranty disclaimers for TI products, and no additional obligations or liabilities arise from TI providing such TI Resources. TI reserves the right to make corrections, enhancements, improvements and other changes to its TI Resources.

You understand and agree that you remain responsible for using your independent analysis, evaluation and judgment in designing your applications and that you have full and exclusive responsibility to assure the safety of your applications and compliance of your applications (and of all TI products used in or for your applications) with all applicable regulations, laws and other applicable requirements. You represent that, with respect to your applications, you have all the necessary expertise to create and implement safeguards that (1) anticipate dangerous consequences of failures, (2) monitor failures and their consequences, and (3) lessen the likelihood of failures that might cause harm and take appropriate actions. You agree that prior to using or distributing any applications. TI has not conducted any testing other than that specifically described in the published documentation for a particular TI Resource.

You are authorized to use, copy and modify any individual TI Resource only in connection with the development of applications that include the TI product(s) identified in such TI Resource. NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT OF TI OR ANY THIRD PARTY IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information regarding or referencing third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of TI Resources may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

TI RESOURCES ARE PROVIDED "AS IS" AND WITH ALL FAULTS. TI DISCLAIMS ALL OTHER WARRANTIES OR REPRESENTATIONS, EXPRESS OR IMPLIED, REGARDING TI RESOURCES OR USE THEREOF, INCLUDING BUT NOT LIMITED TO ACCURACY OR COMPLETENESS, TITLE, ANY EPIDEMIC FAILURE WARRANTY AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY YOU AGAINST ANY CLAIM, INCLUDING BUT NOT LIMITED TO ANY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON ANY COMBINATION OF PRODUCTS EVEN IF DESCRIBED IN TI RESOURCES OR OTHERWISE. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, DIRECT, SPECIAL, COLLATERAL, INDIRECT, PUNITIVE, INCIDENTAL, CONSEQUENTIAL OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF TI RESOURCES OR USE THEREOF, AND REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

You agree to fully indemnify TI and its representatives against any damages, costs, losses, and/or liabilities arising out of your noncompliance with the terms and provisions of this Notice.

This Notice applies to TI Resources. Additional terms apply to the use and purchase of certain types of materials, TI products and services. These include; without limitation, TI's standard terms for semiconductor products <a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation modules, and samples (<a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2018, Texas Instruments Incorporated