## TI Designs LDO Parallel Solution Reference Design With TPS7B4253-Q1

# TEXAS INSTRUMENTS

#### **TI Designs**

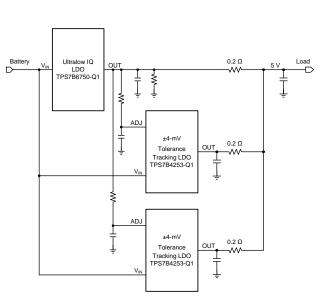

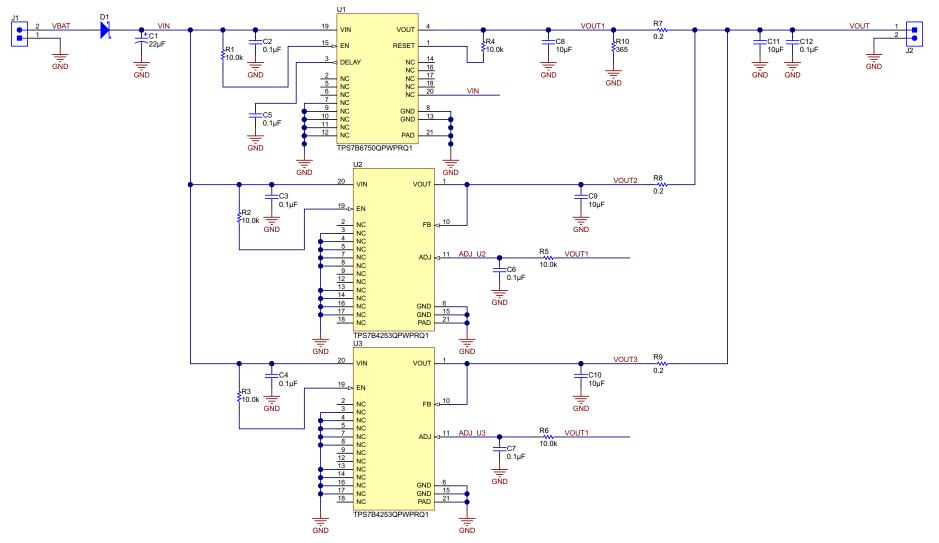

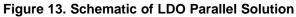

This TI Design uses a very low-tolerance, voltagetracking LDO TPS7B4253-Q1 to demonstrate the implementation of LDO parallel solution for high output current and low quiescent current (IQ) requirements. In this design, TPS7B6750-Q1 regulates 5-V output voltage and two TPS7B4253-Q1 devices expand the output current and realize the current sharing of each channel.

#### **Design Resources**

#### TIDA-00863 TPS7B4253-Q1 TPS7B6750-Q1

Design Folder Product Folder Product Folder

ASK Our E2E Experts

#### **Design Features**

- Expanded Output Current, Up to 900 mA

- Good Thermal Performance Under Large Load Conditions

- 4- to 40-V Wide Input Voltage Range

- Wide Range of Output Capacitor Selection

- Stable With 10- to 500-µF Ceramic Output Capacitor

- ESR Range From 0.001  $\Omega$  to 20  $\Omega$

#### **Featured Applications**

- Cluster

- HVAC

- Body Control Modules

- Shift-by-Wire

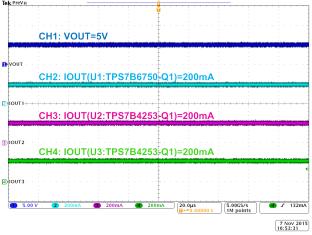

#### **Current Sharing of Each Channel**

#### Key System Specification

2

An IMPORTANT NOTICE at the end of this TI reference design addresses authorized use, intellectual property matters and other important disclaimers and information.

#### 1 **Key System Specification**

#### **Table 1. Key System Specifications**

| PARAMETER                | SPECIFICATION  |  |  |

|--------------------------|----------------|--|--|

| Input voltage            | 6- to 40-V DC  |  |  |

| Regulated output voltage | 5 V            |  |  |

| Output current range     | 900 mA maximum |  |  |

| Operating temperature    | –40°C to 125°C |  |  |

#### 2 System Description

The TIDA-00863 reference design provides a linear regulator parallel solution for the large output current requirement of linear regulators. A first-stage power supply in automotive applications, where both large current and low-quiescent current ( $I_{Q}$ ) are required, is one use of this design.

In this TIDA-00863 reference design, TPS7B6750-Q1 regulates 5-V output voltage and TPS7B4253-Q1 expands the output current and realizes the current sharing of each channel.

The TIDA-00863 reference design is primarily focused in the linear regulator parallel section and provides test data, schematic, and Gerber files.

Block Diagram

4

www.ti.com

### 3 Block Diagram

Figure 1. Block Diagram

#### 3.1 Highlighted Products

The TIDA-00863 reference design features the following TI regulators:

- TPS7B6750-Q1: 450-mA high-voltage ultralow-I<sub>o</sub>, low-dropout regulator

- TPS7B4253-Q1: 300-mA low-dropout, voltage-tracking LDO

Key features for selecting the devices for this reference design are provided in the following sections. See the respective product folders at <u>www.ti.com</u> for complete details of these devices.

#### 3.1.1 TPS7B6750-Q1

The TPS7B6750-Q1 device is one low-dropout linear regulator designed for up to 40-V VIN operations. With only 15- $\mu$ A I<sub>o</sub> at a light load, this device increases the endurance time of automotive batteries.

The TPS7B6750-Q1 device drives loads up to 450 mA and is suitable for many automotive applications, especially when used as a power supply of an infotainment system, body control module, and always-on battery applications.

In the TIDA-00863 design, TPS7B6750-Q1 regulates 5-V voltage at the output. This 5-V voltage is the reference voltage (ADJ) for TPS7B4253-Q1.

#### 3.1.2 TPS7B4253-Q1

The TPS7B4253-Q1 device is designed for automotive applications with a 45-V load dump. The device offers a 4-mV ultralow-tracking tolerance between the ADJ and FB pins across a temperature range of -40°C to 125°C. The reference voltage at the ADJ pin accurately regulates the output of the device.

The TPS7B4253-Q1 device can either be used as one tracking low-dropout regulator, or as a voltage tracker to build one closed-power loop for off-board sensors with an onboard mains supply. In the TIDA-00863 design, TPS7B4253-Q1 is used to expand the total output current up to 600 mA.

#### 4 System Design Theory

The TIDA-00863 reference design uses the voltage-tracking LDO TPS7B453-Q1 and the  $I_{Q}$  LDO TPS7B6750-Q1 to demonstrate the LDO parallel solution for large output current and low  $I_{Q}$  demands.

The TPS7B6750-Q1 is a 5-V fixed version, low dropout regulator in the TPS7B67xx-Q1 family. When powered up with input voltage higher than 5.5 V, the TPS7B6750-Q1 regulator regulates a 5-V output voltage within  $\pm 2\%$  accuracy. In this reference design, this 5-V voltage is directly the ADJ of the TPS7B4253-Q1 device. A voltage-tracking LDO with ultralow-tracking tolerance, the TPS7B4253-Q1 follows the reference voltage within  $\pm 4$  mV. The voltage difference between the three LDOs measures  $\pm 4$  mV only (maximum).

The TPS7B6750-Q1 can output current up to 450 mA and the TPS7B4253-Q1 can output current up to 300 mA. Using one TPS7B6750-Q1 LDO with two TPS7B4253-Q1 LDOs in parallel can expand output current to 1050 mA. This large output current is theoretical; the maximum value is determined by the working conditions of this TI Design. The following sections discuss the design theory based on a test case from three aspects:

- Thermal design

- Current sharing

- Loop stability

#### 4.1 Thermal Design Considerations

In the circuit design of linear regulators, thermal designs are important. Avoid device junction temperatures exceeding 150°C to ensure the stability of the three LDOs.

The following is a design example to illustrate this concept:

#### Table 2. Design Example

| PARAMETER                                            | DESIGN SPECIFICATION      |

|------------------------------------------------------|---------------------------|

| Input voltage, V <sub>IN</sub>                       | 12 V                      |

| Output voltage, V <sub>OUT</sub>                     | 5 V                       |

| Ambient temperature, T <sub>A</sub>                  | 85°C                      |

| PCB parameters                                       | four layer, 1 oz          |

| θJA(TPS7B4253-Q1, HTSSOP-20)                         | 45°C per W <sup>(1)</sup> |

| θJA(TPS7B6750-Q1, HTSSOP-20)                         | 45°C per W(t)             |

| Operating junction temperature range, T <sub>J</sub> | -40°C to 150°C            |

<sup>(1)</sup> Thermal impedance data is measured on the PCB in this reference design

Calculate the maximum power dissipation of the devices with Equation 1 and Equation 2

$$P_{D_{MAX}} = \frac{\Delta T}{\theta_{JA}} = \frac{T_{J} - T_{A}}{\theta_{JA}} = \frac{150^{\circ}C - 85^{\circ}C}{45^{\circ}C / W} = 1.444 \text{ W}$$

(1)

Calculate the maximum current of the devices:

$$I_{MAX} = \frac{P_{D_{MAX}}}{V_{IN} - V_{OUT}} = \frac{1.444 \text{ W}}{12 \text{ V} - 5 \text{ V}} = 0.206 \text{ A}$$

(2)

Maximum current of each device is approximately 200 mA, therefore the total maximum current is 600 mA.

#### 4.2 Current Sharing Considerations

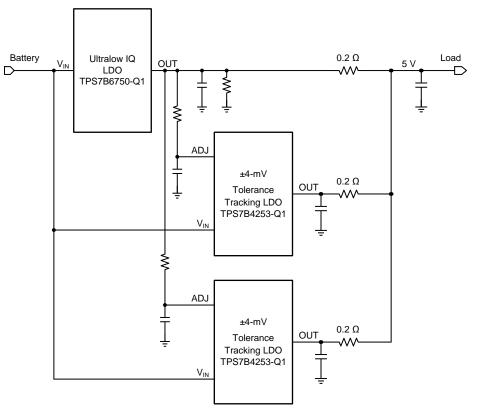

As the TPS7B4253-Q1 is a voltage-tracking LDO with ultralow-tracking tolerance, the maximum voltage difference between the outputs of three LDOs is small (±4 mV) across all conditions. This small voltage difference results in unbalanced current sharing if three outputs are connected directly (otherwise, system instability may occur).

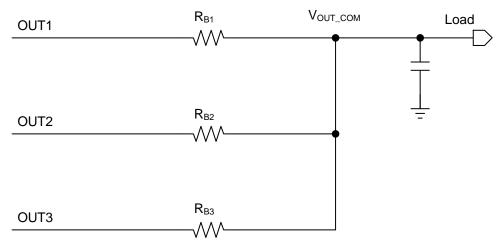

Figure 2. Current Balancing With Ballasting Resistor

Solve this problem by inserting the ballasting resistor  $R_B$  at each output of the three LDOs, as shown in Figure 2. Choose three identical resistors to ensure the current flow through the three channels are close under a heavy load.

In addition, compensate for the  $\pm$  4-mV voltage difference through the current difference between each channel. Equation 3 calculates the maximum current difference.

$$\Delta I_{MAX} = \frac{\Delta V_{MAX}}{R_B} = \frac{\pm 4 \text{ mV}}{R_B}$$

(3)

Under a heavy load, like 600 mA, the same current flows through each channel, and Equation 4 calculates this current value:

$$I_{OUTx} = \frac{I_{LOAD}}{3}$$

(4)

Equation 5 calculates the voltage drop across the ballasting resistor.

$$\Delta V_{\text{DROP}} = \frac{I_{\text{LOAD}}}{3} \times R_{\text{B}} = \frac{600 \text{ mA}}{3} \times R_{\text{B}}$$

(5)

The previous equations show a trade-off between the voltage drop and the current difference. A larger  $R_B$  produces a smaller current difference but a larger voltage drop. A smaller  $R_B$  produces a smaller voltage drop but a higher current difference. In this reference design, choose 0.2- $\Omega$  resistors.

See the previous equations and calculate the output voltage of this LDO parallel solution using Equation 6.

$$V_{OUT} = V_{OUT\_TPS7B6750-Q1} - \frac{I_{LOAD}}{3} \times R_{S} = 5 \text{ V} - \frac{600 \text{ mA}}{3} \times 0.2 \Omega = 4.96 \text{ V}$$

(6)

System Design Theory

#### 4.3 Loop Stability Consideration

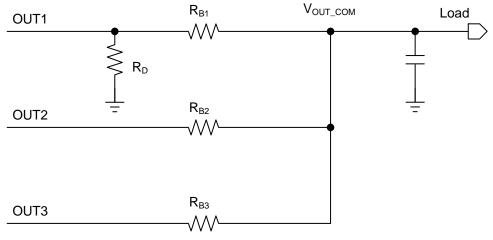

System instability occurs when the common node has no load, or either  $V_{OUT2}$  or  $V_{OUT3}$  measures 4 mV higher than  $V_{OUT1}$ . In this instance, the only current path travels from OUT2 or OUT3 to OUT1, causing system instability.

To maintain system stability, disable the other two TPS7B4253-Q1 LDOs by pulling EN down or connect a dummy load at OUT1 (as shown in Figure 3).

Figure 3. Dummy Load

Calculate the minimum dummy load with Equation 7.

$$I_{\text{DUMMY}} = \frac{4 \text{ mV}}{R_{\text{B1}} + \frac{R_{\text{B2}} \times R_{\text{B3}}}{R_{\text{B2}} + R_{\text{B3}}}} = \frac{4 \text{ mV}}{0.2 \ \Omega + \frac{0.2 \ \Omega \times 0.2 \ \Omega}{0.2 \ \Omega + 0.2 \ \Omega}} = 13.3 \text{ mA}$$

(7)

Calculate the maximum resistor  $R_D$  with Equation 8.

$$R_{\rm D} = \frac{V_{\rm OUT1}}{I_{\rm DUMMY}} = \frac{5 \text{ V}}{13.3 \text{ mA}} = 375 \Omega$$

(8)

Select 365  $\Omega$  for this reference design.

#### Getting Started

#### 5 Getting Started

Implement this design based on the previous LDO parallel specifications in this section.

#### 5.1 Input Capacitor

The TIDA-00863 reference design requires an input bypass capacitor, the value of which depends on the application. The typical recommended value for the bypass capacitor is 22  $\mu$ F. The voltage rating must be greater than the maximum input voltage.

#### 5.2 Output Capacitor

To ensure the stability and proper loop operation of device TPS7B4253-Q1 and device TPS7B6750-Q1, this design requires an output capacitor with a value between 10  $\mu$ F to 500  $\mu$ F and an ESR range from 0.001  $\Omega$  to 20  $\Omega$  at the output of each device and at the common node.

TI recommends the X7R ceramic capacitor with low ESR to improve the load transient response.

When multiple capacitors (two or more) are connected in parallel at the OUT pin, the ESR range of each output capacitor must be from 0.001  $\Omega$  to 3  $\Omega$  for loop stability.

Test Data

#### 6 Test Data

The test data in this section applies to the parameters mentioned in this TI Design. For alternative configurations, see the respective data sheets of the devices.

NOTE: All of the measurements in this section were measured with calibrated lab equipment.

#### 6.1 Test Equipment

The following Table 3 shows the test equipment used in these sections.

#### Table 3. Test Equipment

| TEST EQUIPMENT | MODEL             |

|----------------|-------------------|

| Power supply   | Agilent E3634A    |

| Oscilloscope   | Tektronix DPO4104 |

| Multimeter     | Agilent E34401A   |

| Loads          | Power resistors   |

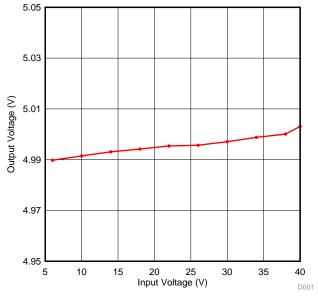

#### 6.2 Line Regulation

10

Figure 4 shows the line regulation with different supply voltages.

Figure 4. Line Regulation (Load = 300 mA)

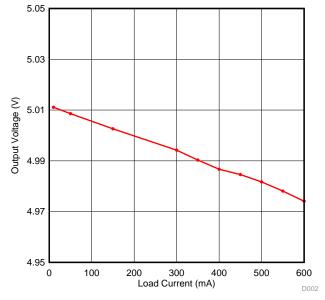

#### 6.3 Load Regulation

Figure 5 shows the device line transient response under different load conditions.

Figure 5. Load Regulation ( $V_{IN} = 14 V$ )

#### Test Data

#### 6.4 Line Transient

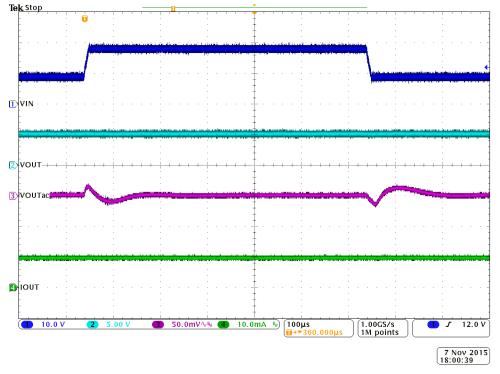

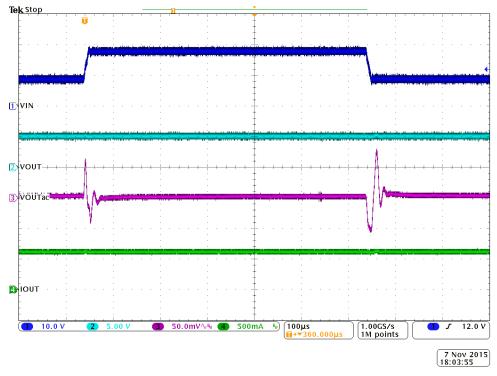

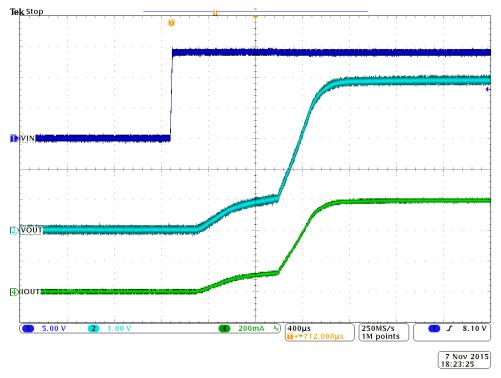

Figure 6 and Figure 7 show the device line transient response under different load conditions.

Figure 6. Line Transient From 9 V to 18 V (1 V/ $\mu$ s) With 10-mA Load

Figure 7. Line Transient From 9 V to 18 V (1 V/ $\!\mu s$ ) With 600-mA Load

13

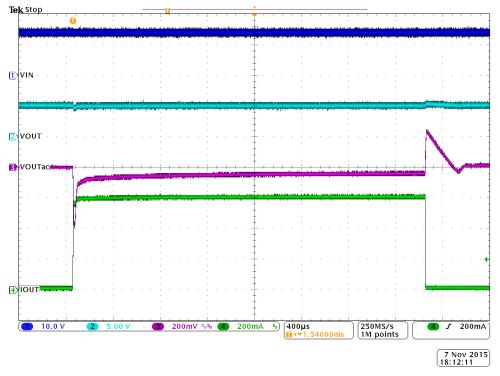

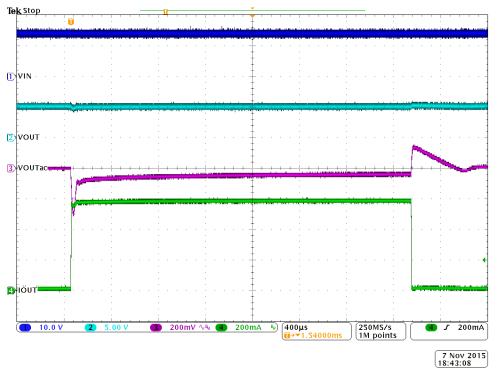

#### 6.5 Load Transient

Figure 8 shows the device load transient response with a 14-V input voltage.

Figure 8. Load Transient From 10 mA to 600 mA

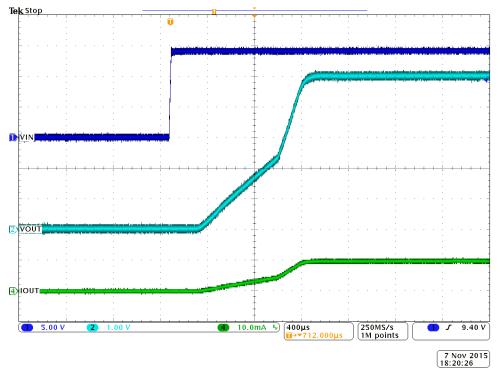

#### 6.6 Power Up

Figure 9 and Figure 10 show the device output response during power up under different load conditions.

Figure 9. Power-up From 0 V to 14 V With 10-mA Load

Figure 10. Power-up From 0 V to 14 V With 600-mA Load

#### 6.7 Load Transient Improvement

In the default setup, the output capacitors are 10-µF ceramic capacitors. To improve load transient response, use larger output capacitors.

Figure 11 shows the device load transient response by increasing output capacitors to 22 µF with the same test conditions and 100 mV of lower undershot (for which overshot voltage is achieved).

Figure 11. Improved Load Transient From 10 mA to 600 mA

#### Test Data

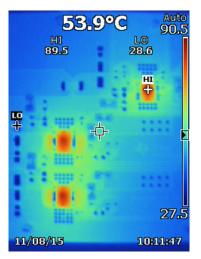

#### 6.8 **Thermal Performance**

Figure 12 shows the device thermal performance with the condition of  $V_{IN}$  = 12 V and load = 600 mA under room temperature ( $T_A = 25^{\circ}C$ ).

The highest temperature in the figure is 89.5°C, concentrated on the three LDO devices and the temperature rise is consistent with calculations Equation 1 and Equation 2 in Section 4.1. When the ambient temperature reaches 85°C, the device temperature remains lower than 150°C to prevent the device from thermal shutdown.

Figure 12. Thermal Performance at V<sub>IN</sub> = 12 V; Load = 600 mA; 25°C

#### 7 Design Files

#### 7.1 Schematics

To download the schematics for each board, see the design files at TIDA-00863

#### Design Files

### 7.2 Bill of Materials

To download the bill of materials (BOM), see the design files at TIDA-00863.

| DESIGNATOR                  | QUANTITY | VALUE  | DESCRIPTION                                                          | PACKAGE<br>REFERENCE | PART NUMBER        | MANUFACTURER        |

|-----------------------------|----------|--------|----------------------------------------------------------------------|----------------------|--------------------|---------------------|

| !PCB1                       | 1        |        | Printed Circuit Board                                                |                      | TPS7B4253          | Any                 |

| C1                          | 1        | 22 µF  | CAP, AL, 22 μF, 50 V, ±20%, 0.88 Ω, SMD                              | SMT Radial D         | EEE-FK1H220P       | Panasonic           |

| C2, C3, C4, C5, C6, C7, C12 | 7        | 0.1 µF | CAP, CERM, 0.1 µF, 50 V, ±10%, X7R, 0603                             | 603                  | GCM188R71H104KA57D | MuRata              |

| C8, C9, C10, C11            | 4        | 10 µF  | CAP, CERM, 10 μF, 16 V, ±10%, X7R, AEC-Q200<br>Grade 1, 1206_190     | 1206_190             | GCM31CR71C106KA64L | MuRata              |

| D1                          | 1        | 60 V   | Diode, Schottky, 60 V, 2 A, SMA                                      | SMA                  | B260A-13-F         | Diodes Inc.         |

| FID1, FID2, FID3            | 3        |        | Fiducial mark. There is nothing to buy or mount.                     | Fiducial             | N/A                | N/A                 |

| J1, J2                      | 2        |        | Terminal Block, 6A, 3.5-mm Pitch, 2-Pos, TH                          | 7.0 × 8.2 × 6.5 mm   | ED555/2DS          | On-Shore Technology |

| R1, R2, R3, R4, R5, R6      | 6        | 10.0k  | RES, 10.0k, 1%, 0.1 W, 0603                                          | 603                  | CRCW060310K0FKEA   | Vishay-Dale         |

| R7, R8, R9                  | 3        | 0.2    | RES, 0.2, 1%, 1 W, 2512                                              | 2512                 | WSL2512R2000FEA    | Vishay-Dale         |

| R10                         | 1        | 365    | RES, 365, 1%, 0.125 W, 0805                                          | 805                  | CRCW0805365RFKEA   | Vishay-Dale         |

| U1                          | 1        |        | 450-mA High-Voltage, Ultralow-IQ, Low-Dropout<br>Regulator, PWP0020D | PWP0020D             | TPS7B6750QPWPRQ1   | ті                  |

| U2, U3                      | 2        |        | 300mA Low-Dropout Voltage Tracking LDO,<br>PWP0020D                  | PWP0020D             | TPS7B4253QPWPRQ1   | ті                  |

#### Table 4. Bill of Materials

#### 7.3 PCB Layout Recommendations

For the LDO-power supply, especially high voltage and large current ones, layout is important. If not carefully designed, the regulator cannot deliver enough output current because of thermal limitations.

To improve the thermal performance of the device and maximize the current output at high-ambient temperature, use four-layer planes in PCB design, spread the thermal pad as wide as possible, and use plenty of thermal vias on and around the thermal pad.

#### 7.3.1 Layer Prints

To download the layer plots, see the design files at TIDA-00863.

#### 7.4 Altium Project

To download the Altium project files, see the design files at TIDA-00863.

#### 7.5 Gerber Files

To download the Gerber files, see the design files at TIDA-00863

#### 7.6 Assembly Drawings

To download the assembly drawings, see the design files at TIDA-00863

#### 8 References

- 1. TPS7B4253-Q1 300-mA 40-V Low-Dropout Voltage-Tracking LDO With 4-mV Tracking Tolerance (SLVSCP3)

- 2. TPS7B6750-Q1 450-mA High-Voltage Ultra-Low IQ Low-Dropout Regulator (SLVSCB2)

#### 9 About the Author

**JASON LIU** is the applications engineer at TI, where he manages the linear regulators applications support in the AVL product line of mixed signal automotive (MSA).

**DAVID XU** is the systems engineer at TI, where he managesr the linear regulators system and roadmap definition in the AVL product line of MSA.

Revision History A

www.ti.com

### **Revision History A**

| Changes from Original (November 2015) to A Revision |                                            |   |  |

|-----------------------------------------------------|--------------------------------------------|---|--|

| •                                                   | Changed block diagram to an updated figure | 4 |  |

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

#### **IMPORTANT NOTICE FOR TI REFERENCE DESIGNS**

Texas Instruments Incorporated ("TI") reference designs are solely intended to assist designers ("Buyers") who are developing systems that incorporate TI semiconductor products (also referred to herein as "components"). Buyer understands and agrees that Buyer remains responsible for using its independent analysis, evaluation and judgment in designing Buyer's systems and products.

TI reference designs have been created using standard laboratory conditions and engineering practices. **TI has not conducted any testing other than that specifically described in the published documentation for a particular reference design.** TI may make corrections, enhancements, improvements and other changes to its reference designs.

Buyers are authorized to use TI reference designs with the TI component(s) identified in each particular reference design and to modify the reference design in the development of their end products. HOWEVER, NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY THIRD PARTY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT, IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

TI REFERENCE DESIGNS ARE PROVIDED "AS IS". TI MAKES NO WARRANTIES OR REPRESENTATIONS WITH REGARD TO THE REFERENCE DESIGNS OR USE OF THE REFERENCE DESIGNS, EXPRESS, IMPLIED OR STATUTORY, INCLUDING ACCURACY OR COMPLETENESS. TI DISCLAIMS ANY WARRANTY OF TITLE AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, QUIET ENJOYMENT, QUIET POSSESSION, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS WITH REGARD TO TI REFERENCE DESIGNS OR USE THEREOF. TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY BUYERS AGAINST ANY THIRD PARTY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON A COMBINATION OF COMPONENTS PROVIDED IN A TI REFERENCE DESIGN. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, SPECIAL, INCIDENTAL, CONSEQUENTIAL OR INDIRECT DAMAGES, HOWEVER CAUSED, ON ANY THEORY OF LIABILITY AND WHETHER OR NOT TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES, ARISING IN ANY WAY OUT OF TI REFERENCE DESIGNS OR BUYER'S USE OF TI REFERENCE DESIGNS.

TI reserves the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques for TI components are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

Reproduction of significant portions of TI information in TI data books, data sheets or reference designs is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards that anticipate dangerous failures, monitor failures and their consequences, lessen the likelihood of dangerous failures and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in Buyer's safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed an agreement specifically governing such use.

Only those TI components that TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components that have **not** been so designated is solely at Buyer's risk, and Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2016, Texas Instruments Incorporated