# TI Designs G3-PLC (FCC Band) Data Concentrator Reference Design

*i* Texas Instruments

## **TI Designs**

The reference design for the G3-FCC Data Concentrator is an evaluation and development platform for data concentrator designs based on the AM335x ARM® Cortex®-A8 microprocessor family of devices. The design provides developers the ultimate level of flexibility and scalability with numerous performance, cost, and connectivity options for their data concentrator designs. It operates in the 157- to 487-KHz band defined by the FCC for Smart Grid Communications. It includes advanced hardware and software that reduce development time by up to nine months while still supporting connectivity to more than 1,000 smart meters. Developers can easily plug in different connectivity modules, including Sub-1GHz (LPRF), general packet radio service (GPRS), near field communication (NFC), and TI's power line communication (PLC) system-on-module (SOM) with G3-FCC support.

#### **Design Resources**

| TIDEP0058     | Tool Folder Containing Design Files |

|---------------|-------------------------------------|

| AM3359        | Product Folder                      |

| TMS320F28375S | Product Folder                      |

| AFE032        | Product Folder                      |

#### **Design Features**

- AM335x ARM Cortex-A8 Processor-Based Design Reduces Development Time by up to Nine Months

- Integrated Communication Interfaces Include Two Ethernet (MAC) Ports, a USB, and up to Eight UARTs for Easy Connectivity to Other Systems on the Smart Grid

- PLC Stacks for MAC and PHY Layers Let Developers Create Designs That Support G3-FCC

- IPv4, IPv6, and 6LoWPAN Protocols Allow Developers to Connect Their Data Concentrator Products to a Wide Range of Home and Building Automation Applications

- PLC SOM for Narrowband PLC in FCC Frequency Band

#### **Featured Applications**

- Grid Communication Infrastructure—Data Concentrator

- Grid Communication Module—PLC

53

An IMPORTANT NOTICE at the end of this TI reference design addresses authorized use, intellectual property matters and other important disclaimers and information.

All trademarks are the property of their respective owners.

#### 1 System Description

This TI Design is an evaluation and development platform for data concentrator designs based on the AM335x ARM Cortex-A8 microprocessor family of devices. The board can interface with multiple nodes (electricity meter) through PLC, low-power RF, or serially using RS-485. All of the board design information is freely available and can be used as the starting point for an AM335x-based data concentrator product. For more hardware details of hardware, see the *Smart Data Concentrator EVM (TMDSDC3359) Hardware Manual* [1].

Data concentrators play a key role in Advanced Metering Infrastructure (AMI) networks as they are the point of interaction between the utility's central operations and individual end points. The data concentrator nodes securely aggregate data from a network of meters over the power line and send it to utility servers.

Data concentrator software architecture separates the real-time functions into the TMS320F28375S MCU while keeping the upper levels of the stack on the AM335x host MPU running Linux.

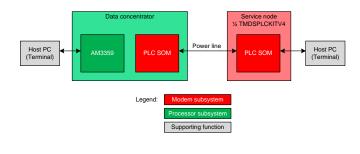

## 2 Block Diagram

Figure 1. System Block Diagram

The Data Concentrator EVM comes with a full variety of onboard devices that suit multiple application environments. Key features include:

- An AM3359 ARM Cortex-A8 microprocessor (MPU) running at 300 MHz

- Support for three-phase PLC

- Support for lower-power 2.4-GHz and sub-1GHz RF communication

- 2 Gb of DDR2 SDRAM memory

- 2 Gb of NAND flash memory, 64-Mb of SPI flash, and a 256-kb I<sup>2</sup>C EEPROM

- Three RS-485 ports, 2 RS-232 ports

- Two 1-Gb Ethernet interfaces

- One SD/MMC connector

- Two USB ports

- Temperature sensor

- Four user LEDs

- Onboard 120-/240-V AC/DC supply (12-V external DC supply also supported)

#### 3 System Design Theory

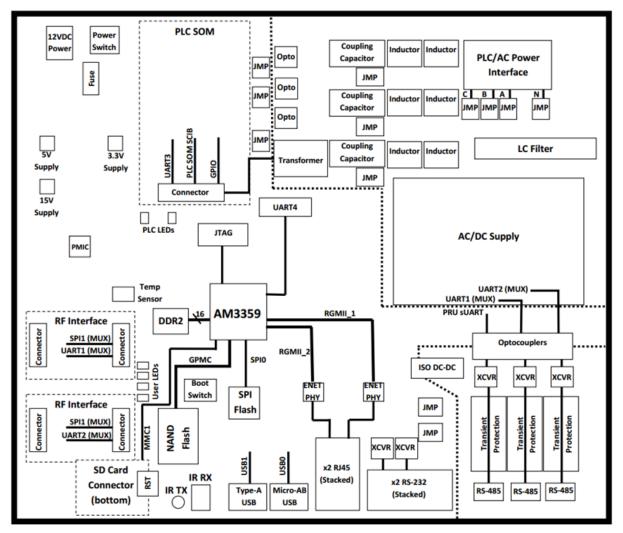

The Data Concentrator EVM consists of one main PCB assembly housing the AM3359 Cortex-A8 processor, DDR2 memory, NAND flash, and other peripherals. The AM3359 processor interfaces to the onboard peripherals through its integrated device interfaces. The processor's DDR 16-bit bus connects directly to the DDR2 memory while the GPMC bus is connected to the NAND flash.

With the addition of a PLC SOM, the EVM can communicate with other devices using PLC on a single- or three-phase system. All three phases are capacitively coupled into a single input which is fed to the PLC SOM connector (P2). The AM3359 processor communicates with the PLC SOM using a UART interface. The PLC section is electrically isolated from the rest of the board.

The EVM supports two low-power RF wireless daughter cards for 2.4-GHz and sub-1-GHz communication. The AM3359 processor can communicate with the RF daughtercards using either a UART interface or SPI.

The EVM supports two RS-232 ports and three RS-485 ports. One RS-232 ports is reserved for Linux kernel debugging while the second RS-232 port can be used for other user-defined purposes. Both RS-232 ports are connected to UART interfaces on the AM3359 processor. Two RS-485 ports are connected to UART interfaces; the third port requires a programmable real-time unit (PRU) software UART. All RS-485 ports are electrically isolated from the rest of the board.

The two USB ports on the processor are connected to a microUSB AB connector and a standard A connector to connect the peripheral and USB OTG devices. Additionally, the EVM includes an SD card, which can be used for booting files and application storage.

The EVM includes four user LEDs to provide visual feedback. Two additional LEDs are reserved for PLC SOM use. The user LEDs connect directly to the AM3359 processor for ease of use. The board can be powered through either a 12-V DC external supply or directly from a 120-/240-V AC power source. Onboard switching regulators and power management IC (PMIC) provide the necessary voltage rails to power the processor, memory, and onboard peripherals. The processor is held in reset until all voltage rails are within operating specifications.

Texas Instruments' Code Composer Studio<sup>™</sup> can debug code running on the EVM. Code Composer Studio communicates with the board through an external JTAG emulator. There is no onboard emulation on the EVM.

## 4 Test Setup

#### 4.1 Hardware

- Data Concentrator EVM (TIDEP0006)

- Two PLC SOM modules (<u>TIDM-SOMPLC-FCC</u>): One for the Data Concentrator EVM, and one for the SOM for PLC motherboard with AC power line coupling

- One PLC motherboard with AC power line coupling (TIDA-00192)

#### 4.2 Setup Description

- 1. Plug in the PLC SOM onto the Data Concentrator EVM and power the board. For more details on Data Concentrator Hardware, see the *Smart Data Concentrator EVM (TMDSDC3359) Hardware Manual* [1].

- 2. Connect the Data Concentrator EVM to the PC through RS-232 to connector P8 (lower port of P8) and Ethernet cable to connector P7 (upper port of stack connector).

- 3. Open Tera Term on the PC, select the Serial option, and set Serial Baud Rate to 115200 as shown in Figure 2 to obtain the IP address.

| Tera Term: Serial port setu                                 | at a state of the |  |  |  |

|-------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| <u>P</u> ort:                                               | СОМ12 - ОК                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| <u>B</u> aud rate:                                          | 115200 -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| <u>D</u> ata:                                               | 8 bit 🔹 Cancel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| P <u>a</u> rity:                                            | none 🔹                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| <u>S</u> top:                                               | 1 bit ▼ <u>H</u> elp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| Elow control:                                               | none 🔹                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| Transmit delay<br>O msec <u>/c</u> har O msec <u>/l</u> ine |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

Figure 2. Tera Term Serial Port Setup

Test Setup

With the IP address determined in <u>Step 3</u>, return to the Tera Term: New connection window and enter the IP address as shown in Figure 3.

| Tera Term: New cor | nnection                                                                                | ×                                                             |

|--------------------|-----------------------------------------------------------------------------------------|---------------------------------------------------------------|

| ⊚ ТСР <u>/І</u> Р  | Hos <u>t</u> : 156.117.97.<br>V Hist <u>o</u> ry<br>Service: O Telnet<br>SSH<br>O Other | 218<br>TCP port#: 23<br>SSH version: SSH2<br>Protocol: UNSPEC |

| © S <u>e</u> rial  | Port: COM6: ATE                                                                         | N USB to Serial Bridge (CC 👻                                  |

Figure 3. Tera Term: New Connection Setup—TCP/IP

- 5. Log in as "root" with password "root".

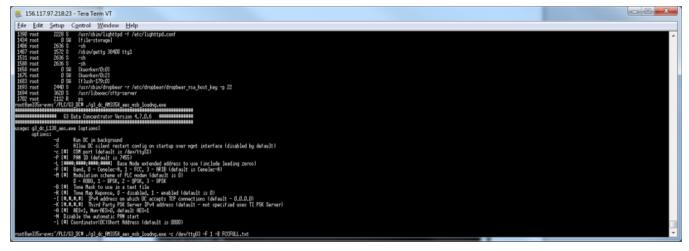

- 6. Start the G3 DC application by executing the following command in the terminal window of the host machine: >./g3\_dc\_AM335X\_aes\_msb\_loading.exe -c/dev/ttyO3

Figure 4. Tera Term VT – DC FCC Setup

Find more options in the user guide in the software package (http://www.ti.com/tool/ti-plc-g3-dc).

- Now a service node can join the network using another PLC modem with service node software installed. Plug in the PLC SOM onto PLC motherboard with AC power line coupling to complete the service node setup.

- (a) Connect the service node to the host PC and open Intermediate GUI installed on the PC. See the *Test Setup* section of the TIDM-SOMPLC-FCC reference guide (<u>TIDU812</u>) for details on connecting the service node to the PC.

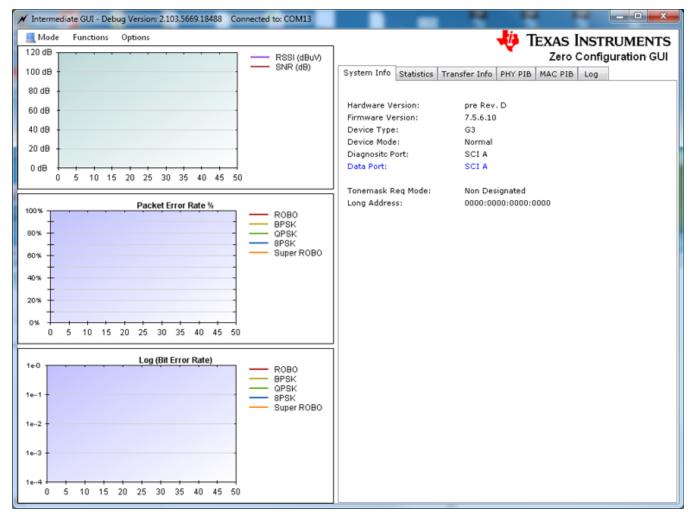

(b) Open Intermediate GUI on the PC (see Figure 5).

Figure 5. Intermediate GUI

Test Setup

www.ti.com

| (C) | Select ( | Options $\rightarrow$ | PHY | Parameters | and | ensure | FCC | band is | selected. |

|-----|----------|-----------------------|-----|------------|-----|--------|-----|---------|-----------|

|-----|----------|-----------------------|-----|------------|-----|--------|-----|---------|-----------|

| G3 PHY Parar                       |                    | l.0.16.57              | - COM           |            |

|------------------------------------|--------------------|------------------------|-----------------|------------|

| - Transmit PHY I<br>Modulation     | Parameters<br>ROBO | •                      |                 | тмв 🔲      |

| Level                              | 21 •               |                        | Coherent Mo     |            |

| Band FCC                           |                    | Maak                   | FCC Full Ban    |            |

| Banu rcc                           | •                  | MIGSK                  | recruitban      | <b>u v</b> |

| - PHY Transmit 1                   | lest               |                        |                 |            |

| 📃 Enable TX                        | Test Mode          | PPDU Paj               | yload (bytes)   | 0          |

| Sweep M(                           | CS                 | Inter-PPDI             | U Time (10 us)  | 0          |

| Sweep PF                           | DU Len             | Number of              | FPPDU / settir  | ng O       |

| Continuou                          | S                  | Data Patte             | ern Ramp Da     | ata 👻      |

| Tone Map (he                       | x) 0x00FFFFF       | F                      | Byte (hex)      | 0x00       |

| 📃 Enable Ze                        | ro Crossing        | Zero Cros:             | sing Delay (ms) | 0          |

| Receive PHY I<br>V AGC<br>Band FCC |                    |                        | àain Value 4    | v<br>d v   |

| - Receive PHY<br>Enable R>         | (Test Mode         | Data Patt<br>yte (hex) | ern Ramp D      | ata 💌      |

| OK                                 | Apply              | P                      | lefresh         | Cancel     |

Figure 6. G3 PHY Parameters Configuration

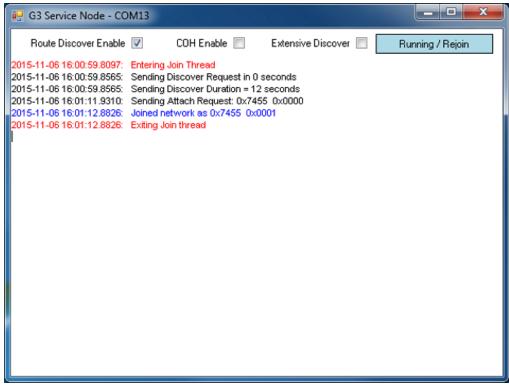

(d) Select Function → Service Node to start the service node and wait until it joins the Data Concentrator.

| G3 Service Node - COM13 |              | Particular Income    |       |

|-------------------------|--------------|----------------------|-------|

| Route Discover Enable 🔍 | COH Enable 📃 | Extensive Discover 📃 | Start |

|                         |              |                      |       |

|                         |              |                      |       |

|                         |              |                      |       |

|                         |              |                      |       |

|                         |              |                      |       |

|                         |              |                      |       |

|                         |              |                      |       |

|                         |              |                      |       |

|                         |              |                      |       |

|                         |              |                      |       |

|                         |              |                      |       |

|                         |              |                      |       |

Figure 7. G3 Service Node

See Figure 8 for an example of successfully joining the service node to the Data Concentrator.

Test Data

- www.ti.com

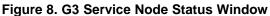

- 8. Once the service node has joined, trigger a simple data transfer by using application "Application udpIPv6App\_AM335X > ./udpIPv6App\_AM335x -I 100 -s 0x1".

The packet length is 100 and the short address is 0x1.

Find more options in the user guide in the software package (http://www.ti.com/tool/ti-plc-g3-dc).

#### 5 Test Data

Once the service node has joined over the network, the user can trigger a simple data transfer over the network by using the application "Application udpIPv6App\_AM335X > ./udpIPv6App\_AM335x –I 100 –s 0x1".

With data transfer initiated, the round trip time to send data from the Data Concentrator to the service node is displayed in milliseconds as shown in Figure 9.

Figure 9. Test Data

#### 6 Design Files

#### 6.1 Schematics

To download the schematics, see the design files at <u>TIDEP0058</u>.

## 6.2 Bill of Materials

To download the bill of materials (BOM), see the design files at TIDEP0058.

## 6.3 Layout Prints

To download the layer plots, see the design files at <u>TIDEP0058</u>.

## 6.4 Gerber Files

To download the Gerber files, see the design files at <u>TIDEP0058</u>.

## 6.5 Assembly Drawings

To download the assembly drawings, see the design files at <u>TIDEP0058</u>.

## 7 Software Files

To download the software files, see the design files at TIDEP0058.

#### 8 References

Texas Instruments, Smart Data Concentrator EVM (TMDSDC3359) Hardware Manual, TMDSDC3359 Wiki (http://processors.wiki.ti.com/index.php/Smart\_Data\_Concentrator\_EVM\_(TMDSDC3359)\_Hardware\_ Manual)

#### 9 About the Author

**NAVEEN KALA** is a system applications engineer at Texas Instruments, where he is responsible for providing technical support and training on Smart Grid solutions and driving solutions for Smart Grid/Metering, and working on defining future requirements in roadmap. He received the M.Eng. degree in electrical and computer engineering from University of Iowa.

**Revision History**

www.ti.com

## **Revision History**

| Cł | nanges from Original (December 2015) to A Revision | Page |

|----|----------------------------------------------------|------|

| •  | Changed from preview page                          | 1    |

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

#### **IMPORTANT NOTICE FOR TI REFERENCE DESIGNS**

Texas Instruments Incorporated ("TI") reference designs are solely intended to assist designers ("Buyers") who are developing systems that incorporate TI semiconductor products (also referred to herein as "components"). Buyer understands and agrees that Buyer remains responsible for using its independent analysis, evaluation and judgment in designing Buyer's systems and products.

TI reference designs have been created using standard laboratory conditions and engineering practices. **TI has not conducted any testing other than that specifically described in the published documentation for a particular reference design.** TI may make corrections, enhancements, improvements and other changes to its reference designs.

Buyers are authorized to use TI reference designs with the TI component(s) identified in each particular reference design and to modify the reference design in the development of their end products. HOWEVER, NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY THIRD PARTY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT, IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

TI REFERENCE DESIGNS ARE PROVIDED "AS IS". TI MAKES NO WARRANTIES OR REPRESENTATIONS WITH REGARD TO THE REFERENCE DESIGNS OR USE OF THE REFERENCE DESIGNS, EXPRESS, IMPLIED OR STATUTORY, INCLUDING ACCURACY OR COMPLETENESS. TI DISCLAIMS ANY WARRANTY OF TITLE AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, QUIET ENJOYMENT, QUIET POSSESSION, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS WITH REGARD TO TI REFERENCE DESIGNS OR USE THEREOF. TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY BUYERS AGAINST ANY THIRD PARTY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON A COMBINATION OF COMPONENTS PROVIDED IN A TI REFERENCE DESIGN. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, SPECIAL, INCIDENTAL, CONSEQUENTIAL OR INDIRECT DAMAGES, HOWEVER CAUSED, ON ANY THEORY OF LIABILITY AND WHETHER OR NOT TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES, ARISING IN ANY WAY OUT OF TI REFERENCE DESIGNS OR BUYER'S USE OF TI REFERENCE DESIGNS.

TI reserves the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques for TI components are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

Reproduction of significant portions of TI information in TI data books, data sheets or reference designs is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards that anticipate dangerous failures, monitor failures and their consequences, lessen the likelihood of dangerous failures and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in Buyer's safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed an agreement specifically governing such use.

Only those TI components that TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components that have **not** been so designated is solely at Buyer's risk, and Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2015, Texas Instruments Incorporated