TPS55289-Q1 SLVSGT5 - DECEMBER 2023

# TPS55289-Q1 36V, 8A Buck-Boost Converter with I<sup>2</sup>C Interface

#### 1 Features

- AEC-Q100 qualified:

- Device temperature grade 1: –40°C to +125°C ambient operating temperature range

- Functional Safety-Capable

- Documentation available to aid functional safety system design

- Programmable power supply (PPS) support for USB power delivery (USB PD)

- Wide input voltage range: 3.0V to 36V

- Programmable output voltage range: 0.8V to 22V with 10mV step

- ±1% reference voltage accuracy

- Adjustable output voltage compensation for voltage droop over the cable

- Programmable output current limit up to 6.35A with 50mA step

- ±5% accurate output current monitoring

- I<sup>2</sup>C interface

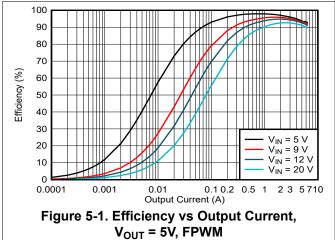

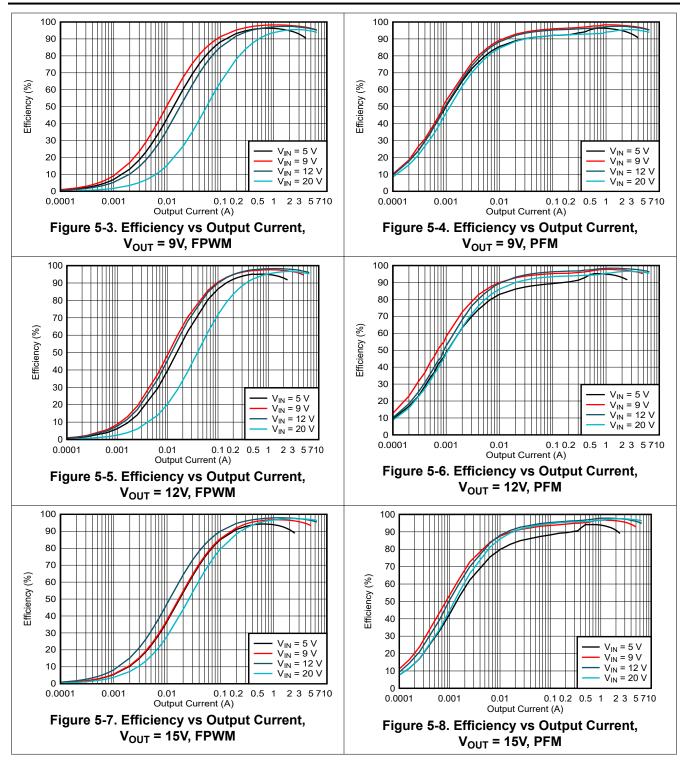

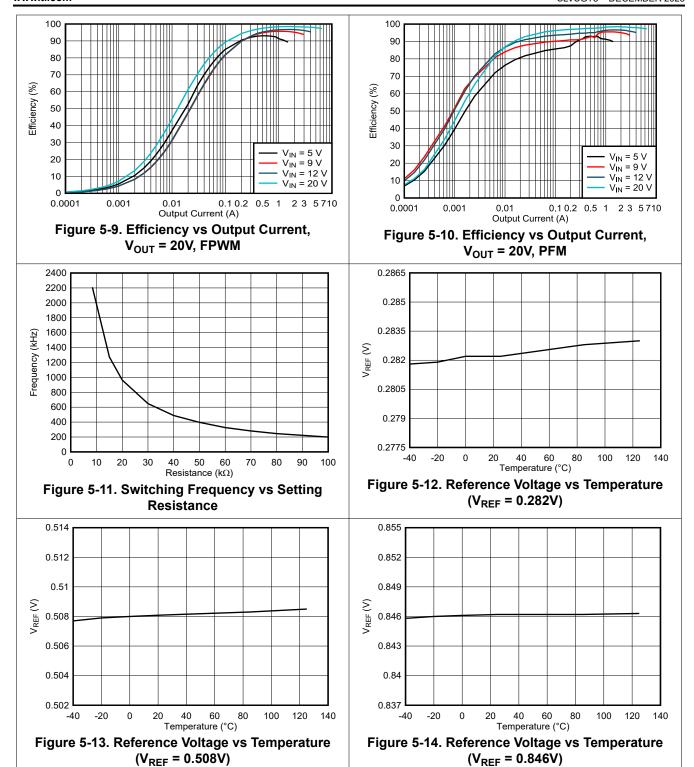

- High efficiency over entire load range

- 96% efficiency at  $V_{IN}$  = 12V,  $V_{OUT}$  = 20V and  $I_{OUT} = 3A$

- Programmable PFM and FPWM mode at light

- Avoid frequency interference and crosstalk

- Optional clock synchronization

- Programmable switching frequency from 200kHz to 2.2MHz

- EMI mitigation

- Optional programmable spread spectrum

- Lead-less package

- Rich protection features

- Output overvoltage protection

- Hiccup mode for output short-circuit protection

- Thermal shutdown protection

- 8A average inductor current limit

- Small solution size

- Maximum switching frequency up to 2.2MHz

- 3.0mm × 5.0mm HotRod™ QFN package

#### 2 Applications

- Car charger

- USB PD

- Wireless charger

- Automotive infotainment and cluster

- Automotive rear lighting

- Advanced driver-assistance system (ADAS)

## 3 Description

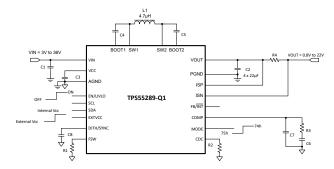

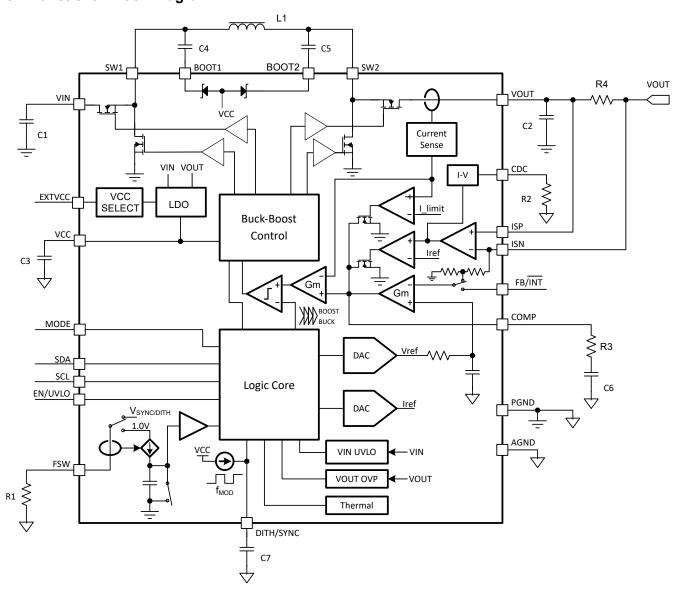

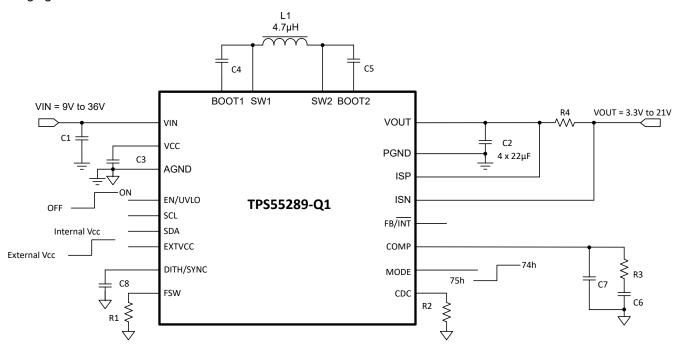

The TPS55289-Q1 is a synchronous buck-boost converter that is optimized for converting battery voltage or adapter voltage into power supply rails. The TPS55289-Q1 integrates four MOSFET switches providing a compact solution for USB Power Delivery (USB PD) application.

The TPS55289-Q1 has up to 36V input voltage capability. Through the I<sup>2</sup>C interface, the output voltage of the TPS55289-Q1 can be programmed from 0.8V to 22V with 10mV step. When working in boost mode, it can deliver 60W from a 12V input voltage. It is capable of delivering 45W from 9V input voltage.

The TPS55289-Q1 employs an average currentmode control scheme. The switching frequency is programmable from 200kHz to 2.2MHz by an external resistor and can be synchronized to an external clock. The TPS55289-Q1 also provides optional spread spectrum to minimize peak EMI.

TPS55289-Q1 offers output over-voltage protection, average inductor current limit, cycle-bycycle peak current limit and output short circuit protection. The TPS55289-Q1 also ensures safe operating with optional output current limit and hiccupmode protection in sustained overload conditions.

The TPS55289-Q1 can use a small inductor and small capacitors with high switching frequency. It is available in a 3.0mm × 5.0mm QFN package.

### **Device Information**

| PART NUMBER | PACKAGE <sup>(1)</sup> | BODY SIZE     |

|-------------|------------------------|---------------|

| TPS55289-Q1 | VQFN-HR                | 3.0mm × 5.0mm |

For all available packages, see the orderable addendum at the end of the data sheet.

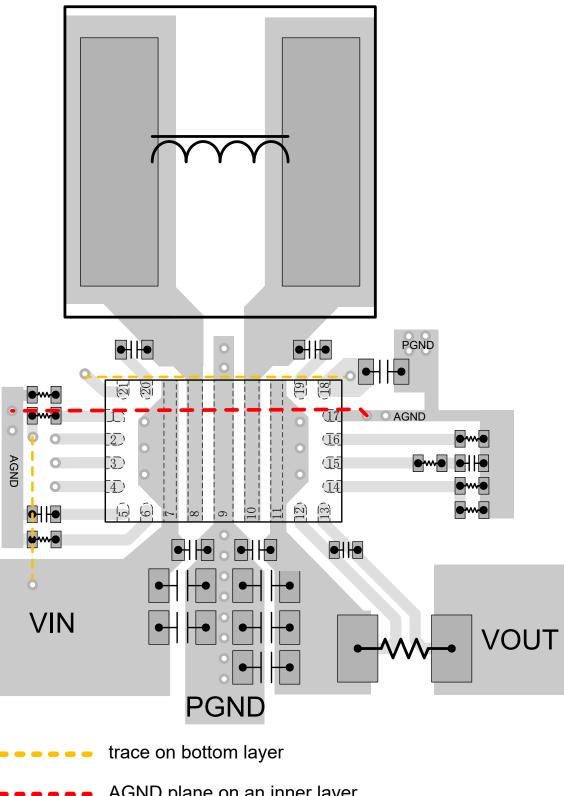

**Typical Application Circuit**

## **Table of Contents**

| 1 Features1                                     |

|-------------------------------------------------|

| 2 Applications                                  |

| 3 Description                                   |

| 4 Pin Configuration and Functions3              |

| 5 Specifications                                |

| 5.1 Absolute Maximum Ratings5                   |

| 5.2 ESD Ratings5                                |

| 5.3 Recommended Operating Conditions5           |

| 5.4 Thermal Information6                        |

| 5.5 Electrical Characteristics6                 |

| 5.6 I <sup>2</sup> C Timing Characteristics9    |

| 5.7 Typical Characteristics9                    |

| 6 Detailed Description13                        |

| 6.1 Overview13                                  |

| 6.2 Functional Block Diagram14                  |

| 6.3 Feature Description15                       |

| 6.4 Device Functional Modes23                   |

| 6.5 Programming23                               |

| 7 Register Maps27                               |

| 7.1 REF Register (Address = 0h, 1h) [reset =    |

| 10100100b, 00000001b]28                         |

| 7.2 IOUT_LIMIT Register (Address = 2h) [reset = |

| 11100100b]29                                    |

| 7.3 VOUT_SR Register (Address = 3h) [reset =    |

| 00000001b]30                                    |

| 7.4 VOUT_F5 Register (Address = 4n) [reset =         |      |

|------------------------------------------------------|------|

| 00000011b]                                           | 31   |

| 7.5 CDC Register (Address = 5h) [reset = 11100000b]. | 32   |

| 7.6 MODE Register (Address = 6h) [reset =            |      |

| 00100000b]                                           | . 33 |

| 7.7 STATUS Register (Address = 7h) [reset =          |      |

| 00000011b]                                           | 34   |

| 7.8 Register Summary                                 | .35  |

| 8 Application and Implementation                     | 36   |

| 8.1 Application Information                          | . 36 |

| 8.2 Typical Application                              |      |

| 8.3 Power Supply Recommendations                     | 44   |

| 8.4 Layout                                           | . 44 |

| 9 Device and Documentation Support                   | 46   |

| 9.1 Device Support                                   | . 46 |

| 9.2 Receiving Notification of Documentation Updates  | 46   |

| 9.3 Support Resources                                | . 46 |

| 9.4 Trademarks                                       | 46   |

| 9.5 Electrostatic Discharge Caution                  | 46   |

| 9.6 Glossary                                         | 46   |

| 10 Revision History                                  | . 46 |

| 11 Mechanical, Packaging, and Orderable              |      |

| Information                                          | . 46 |

|                                                      |      |

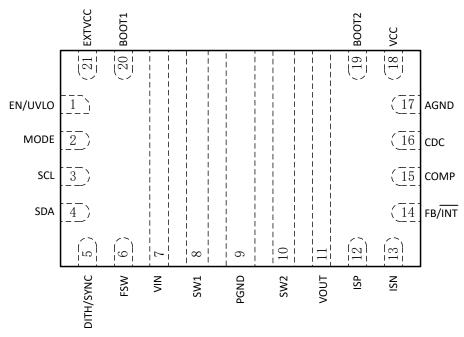

## **4 Pin Configuration and Functions**

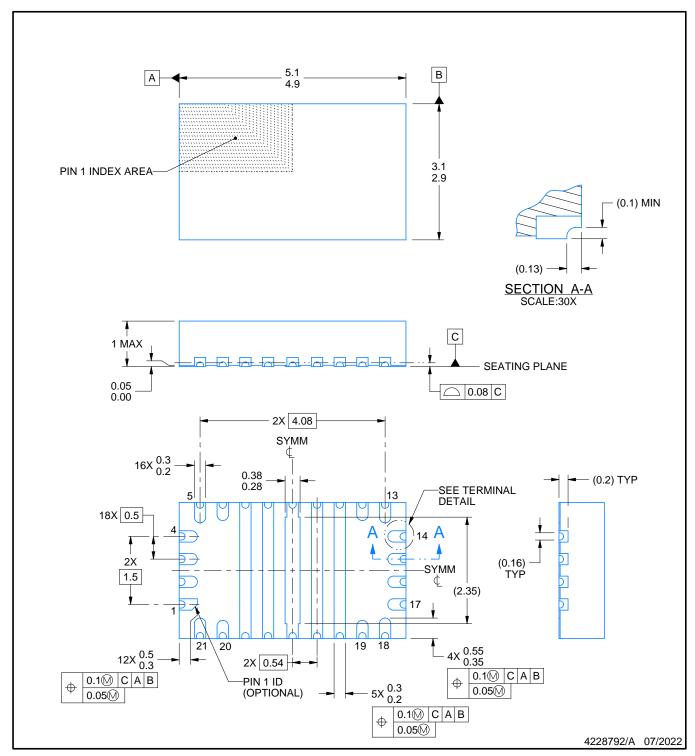

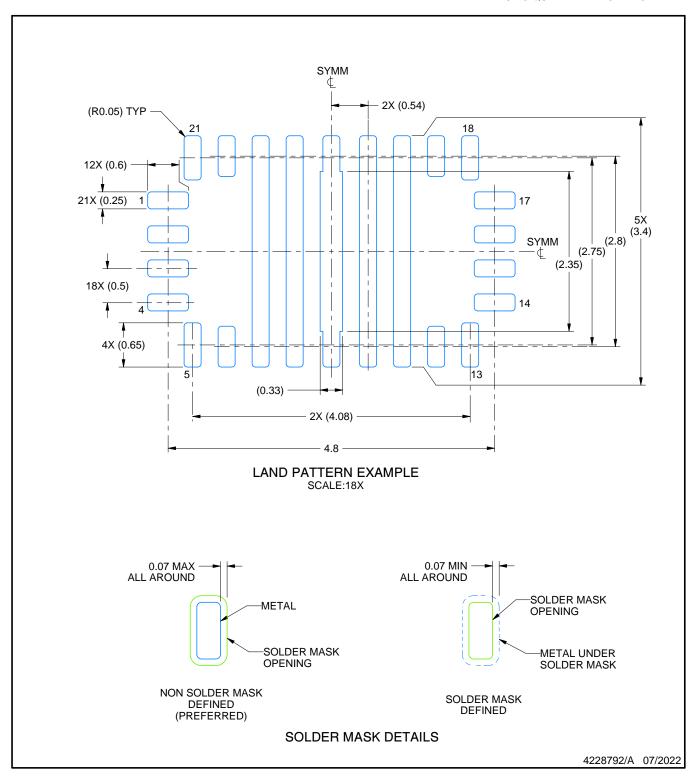

Figure 4-1. 21-pin VQFN-HR, RYQ Package (Transparent Top View)

**Table 4-1. Pin Functions**

|     | PIN       | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-----|-----------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO. | NAME      | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

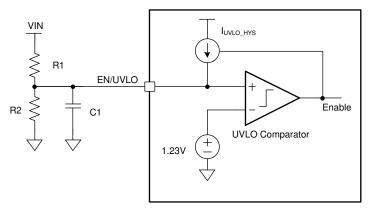

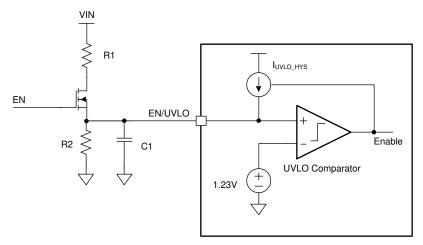

| 1   | EN/UVLO   | ı   | Enable logic input and programmable input voltage undervoltage lockout (UVLO) input. Logic high level enables the device. Logic low level disables the device and turns it into shutdown mode. After the voltage at the EN/UVLO pin is above the logic high voltage of 1.15V, this pin acts as programmable UVLO input with 1.23V internal reference.                                                                                                                                                               |

| 2   | MODE      | I   | I <sup>2</sup> C target address selection. When it is connected to logic high voltage, the I <sup>2</sup> C target address is 74H. When it is connected to logic low voltage, I <sup>2</sup> C target address is 75H.                                                                                                                                                                                                                                                                                               |

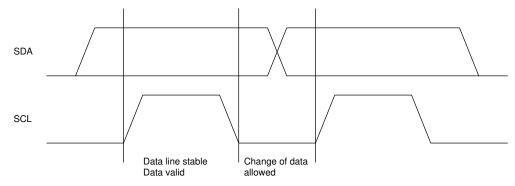

| 3   | SCL       | ļ   | Clock of I <sup>2</sup> C interface.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 4   | SDA       | I/O | Data of I <sup>2</sup> C interface.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

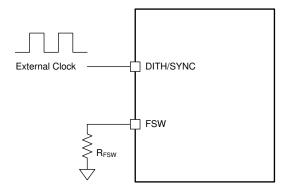

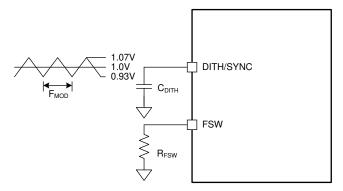

| 5   | DITH/SYNC | I   | Dithering frequency setting and synchronous clock input. Use a capacitor between this pin and ground to set the dithering frequency. When this pin is short to ground or pulled above 1.2V, there is no dithering function. An external clock can be applied at this pin to synchronize the switching frequency.                                                                                                                                                                                                    |

| 6   | FSW       | I   | The switching frequency is programmed by a resistor between this pin and the AGND pin.                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 7   | VIN       | PWR | Input of the buck-boost conveter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 8   | SW1       | PWR | The switching node pin of the buck side. It is connected to the drain of the internal buck low-side power MOSFET and the source of internal buck high-side power MOSFET.                                                                                                                                                                                                                                                                                                                                            |

| 9   | PGND      | PWR | Power ground of the device.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 10  | SW2       | PWR | The switching node pin of the boost side. It is connected to the drain of the internal boost low-side power MOSFET and the source of internal boost high-side power MOSFET.                                                                                                                                                                                                                                                                                                                                         |

| 11  | VOUT      | PWR | Output of the buck-boost converter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

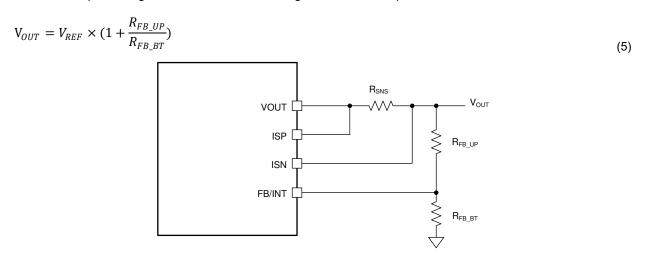

| 12  | ISP       | I   | Positive input of the current sense amplifier. An optional current sense resistor connected between the ISP pin and the ISN pin can limit the output current. If the sensed voltage reaches the current limit setting value in the register, a slow constant current control loop becomes active and starts to regulate the voltage between the ISP pin and the ISN pin. Connecting the ISP pin and the ISN pin together with the VOUT pin can disable the output current limit function. It must not be left open. |

## **Table 4-1. Pin Functions (continued)**

|     | PIN    | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-----|--------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO. | NAME   | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 13  | ISN    | I   | Negative input of the current sense amplifier. An optional current sense resistor connected between the ISP pin and the ISN pin can limit the output current. If the sensed voltage reaches the current limit setting value in the register, a slow constant current control loop becomes active and starts to regulate the voltage between the ISP pin and the ISN pin. Connecting the ISP pin and the ISN pin together with the VOUT pin can disable the output current limit function. It must not be left open. |

| 14  | FB/ĪNT | I/O | When the device is set to use external output voltage feedback, connect to the center tap of a resistor divider to program the output voltage. When the device is set to use internal feedback, this pin is a fault indicator open-drain output. When there is an internal fault happening, this pin outputs logic low level.                                                                                                                                                                                       |

| 15  | COMP   | 0   | Output of the internal error amplifier. Connect the loop compensation network between this pin and the AGND pin.                                                                                                                                                                                                                                                                                                                                                                                                    |

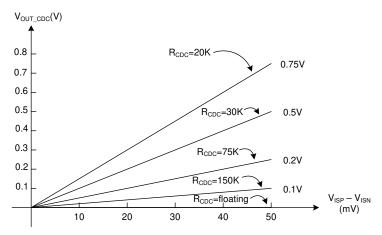

| 16  | CDC    | 0   | Voltage output proportional to the sensed voltage between the ISP pin and the ISN pin. Use a resistor between this pin and AGND to increase the output voltage to compensate voltage droop across the cable caused by the cable resistance. This pin can be left open if using internal cable voltage droop compensation.                                                                                                                                                                                           |

| 17  | AGND   | -   | Signal ground of the device.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 18  | VCC    | 0   | Output of the internal regulator. A ceramic capacitor of more than 4.7µF is required between this pin and the AGND pin.                                                                                                                                                                                                                                                                                                                                                                                             |

| 19  | BOOT2  | 0   | Power supply for high-side MOSFET gate driver in boost side. A ceramic capacitor of 0.1µF must be connected between this pin and the SW2 pin.                                                                                                                                                                                                                                                                                                                                                                       |

| 20  | BOOT1  | 0   | Power supply for high-side MOSFET gate driver in buck side. A ceramic capacitor of 0.1µF must be connected between this pin and the SW1 pin.                                                                                                                                                                                                                                                                                                                                                                        |

| 21  | EXTVCC | I   | Select the internal LDO or external 5V for VCC. When it is connected to VCC pin, logic high voltage or is left floating, select the internal LDO. When it is connected to logic low voltage, select the external 5V for VCC.                                                                                                                                                                                                                                                                                        |

## **5 Specifications**

### 5.1 Absolute Maximum Ratings

over the recommended operating junction temperature range (unless otherwise noted)(1)

|                                   |                                                                | MIN     | MAX     | UNIT |

|-----------------------------------|----------------------------------------------------------------|---------|---------|------|

| Voltage range<br>at terminals (2) | VIN, SW1                                                       | -0.3    | 42      | V    |

|                                   | BOOT1                                                          | SW1-0.3 | SW1+6   | V    |

|                                   | VCC, SCL, SDA, FSW, COMP, FB/INT, MODE, CDC, DITH/SYNC, EXTVCC | -0.3    | 6       | V    |

|                                   | VOUT, SW2, ISP, ISN                                            | -0.3    | 25      | V    |

|                                   | EN                                                             | -0.3    | 20      | V    |

|                                   | BOOT2                                                          | SW2-0.3 | SW2+6   | V    |

|                                   | SCL, SDA, FSW, COMP, FB/INT, MODE, CDC, DITH/SYNC, EXTVCC      | -0.3    | VCC+0.3 | V    |

| T <sub>J</sub>                    | Operating Junction, T <sub>J</sub> <sup>(3)</sup>              | -40     | 150     | °C   |

| T <sub>stg</sub>                  | Storage temperature                                            | -65     | 150     | °C   |

<sup>(1)</sup> Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

### 5.2 ESD Ratings

|                    |                         |                                                                          | VALUE | UNIT |

|--------------------|-------------------------|--------------------------------------------------------------------------|-------|------|

| V                  | Electrostatic discharge | Human body model (HBM), per AEC Q100-002 <sup>(1)</sup>                  | ±2000 | V    |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged device model (CDM), per AEC Q100-011, all pins <sup>(2)</sup>    | ±500  | V    |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged device model (CDM), per AEC Q100-011, corner pins <sup>(2)</sup> | ±750  | V    |

<sup>(1)</sup> Level listed above is the passing level per ANSI, ESDA, and JEDEC JS-001. JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process. Manufacturing with less than 500-V HBM is possible with the necessary precautions.

#### 5.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                  | <u> </u>                                      | MIN | NOM | MAX  | UNIT |

|------------------|-----------------------------------------------|-----|-----|------|------|

| V <sub>IN</sub>  | Input voltage range                           | 3.0 |     | 36   | V    |

| V <sub>OUT</sub> | Output voltage range                          | 0.8 |     | 22   | V    |

| L                | Effective inductance range                    | 1   | 4.7 | 10   | μH   |

| C <sub>IN</sub>  | Effective input capacitance range             | 4.7 | 22  |      | μF   |

| C <sub>OUT</sub> | Effective output capacitance range            | 10  | 100 | 1000 | μF   |

| TJ               | Operating junction temperature <sup>(1)</sup> | -40 |     | 150  | °C   |

<sup>(1)</sup> High junction temperatures degrade operating lifetimes. Operating lifetime is de-rated for junction temperatures greater than 125°C.

<sup>2)</sup> All voltage values are with respect to network ground terminal.

<sup>(3)</sup> High junction temperatures degrade operating lifetimes. Operating lifetime is de-rated for junction temperatures greater than 125°C.

<sup>(2)</sup> Level listed above is the passing level per EIA-JEDEC JESD22-C101. JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process. Manufacturing with less than 250-V CDM is possible with the necessary precautions.

#### **5.4 Thermal Information**

|                       |                                              | RYQ (VQFN) | RYQ (VQFN) |      |

|-----------------------|----------------------------------------------|------------|------------|------|

|                       | THERMAL METRIC(1)                            | 21 PINS    | 21 PINS    | UNIT |

|                       |                                              | Standard   | EVM (2)    |      |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance       | 43.4       | 27.5       | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 22.3       | N/A        | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 7.4        | N/A        | °C/W |

| $\Psi_{JT}$           | Junction-to-top characterization parameter   | 0.7        | 0.7        | °C/W |

| $Y_{JB}$              | Junction-to-board characterization parameter | 7.2        | 11.1       | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | N/A        | N/A        | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

#### **5.5 Electrical Characteristics**

$T_J$  = -40°C to 125°C,  $V_{IN}$  = 12 V and  $V_{OUT}$  = 20 V. Typical values are at  $T_J$  = 25°C, unless otherwise noted.

|                       | PARAMETER                                | TEST CONDITIONS                                                                                                                     | MIN  | TYP  | MAX  | UNIT |

|-----------------------|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| POWER SU              | PPLY                                     |                                                                                                                                     |      |      |      |      |

| V <sub>IN</sub>       | Input voltage range                      |                                                                                                                                     | 3.0  |      | 36   | V    |

| \ /                   |                                          | V <sub>IN</sub> rising                                                                                                              | 2.8  | 2.9  | 3.0  | V    |

| $V_{VIN\_UVLO}$       | Under voltage lockout threshold          | V <sub>IN</sub> falling                                                                                                             | 2.6  | 2.65 | 2.7  | V    |

|                       | Quiescent current into VIN pin           | IC enabled, no load, no switching. $V_{IN}$ = 3.0V to 24V, $V_{OUT}$ = 0.8V, $V_{FB}$ = $V_{REF}$ + 0.1V, $R_{FSW}$ = 100k $\Omega$ |      | 760  | 860  | μA   |

| l <sub>Q</sub>        | Quiescent current into VOUT pin          | IC enabled, no load, no switching. $V_{IN}$ = 3.0V, $V_{OUT}$ = 3V to 20V, $V_{FB}$ = $V_{REF}$ + 0.1V, $R_{FSW}$ = 100k $\Omega$   |      | 760  | 860  | μА   |

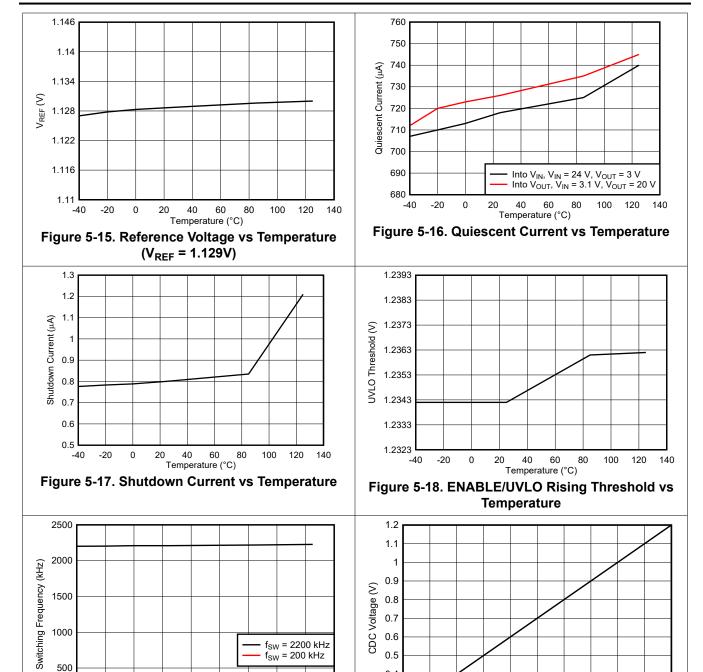

| I <sub>SD</sub>       | Shutdown current into VIN pin            | IC disabled, V <sub>IN</sub> = 3.0V to 14V, T <sub>J</sub> up to 125°C, EXTVCC pin floating                                         |      | 0.8  | 3    | μA   |

| V <sub>CC</sub>       | Internal regulator output                | I <sub>VCC</sub> = 50mA, V <sub>IN</sub> = 8V, V <sub>OUT</sub> = 20V                                                               | 5.0  | 5.2  | 5.4  | V    |

| EN/UVLO               |                                          |                                                                                                                                     |      |      |      |      |

| V <sub>EN_H</sub>     | EN Logic high threshold                  | V <sub>CC</sub> = 3.0V to 5.5V                                                                                                      |      |      | 1.15 | V    |

| V <sub>EN_L</sub>     | EN Logic low threshold                   | V <sub>CC</sub> = 3.0V to 5.5V                                                                                                      | 0.4  |      |      | V    |

| V <sub>EN_HYS</sub>   | Enable threshold hysteresis              | V <sub>CC</sub> = 3.0V to 5.5V                                                                                                      | 0.04 |      |      | V    |

| V <sub>UVLO</sub>     | UVLO rising threshold at the EN/UVLO pin | V <sub>CC</sub> = 3.0V to 5.5V                                                                                                      | 1.20 | 1.23 | 1.26 | V    |

| V <sub>UVLO_HYS</sub> | UVLO threshold hysteresis                | V <sub>CC</sub> = 3.0V to 5.5V                                                                                                      |      | 10   |      | mV   |

| I <sub>UVLO</sub>     | Sourcing current at the EN/UVLO pin      | V <sub>EN/UVLO</sub> = 1.3V                                                                                                         | 4.4  | 5    | 5.6  | μΑ   |

| OUTPUT                |                                          |                                                                                                                                     |      |      |      |      |

| V <sub>OUT</sub>      | Output voltage range                     |                                                                                                                                     | 0.8  |      | 22   | V    |

| V <sub>OVP</sub>      | Output overvoltage protection threshold  |                                                                                                                                     | 22.5 | 23.5 | 24.5 | V    |

| V <sub>OVP_HYS</sub>  | Overvoltage protection hysteresis        |                                                                                                                                     |      | 1    |      | V    |

| I <sub>FB_LKG</sub>   | Leakage current at FB pin                | T <sub>J</sub> up to 125°C                                                                                                          |      |      | 100  | nA   |

| VOUT_LKG              | Leakage current into VOUT pin            | IC disabled, V <sub>OUT</sub> = 20V, V <sub>SW2</sub> = 0V,<br>T <sub>J</sub> up to 125°C                                           |      | 1    | 20   | μΑ   |

|                       |                                          |                                                                                                                                     |      |      |      |      |

Product Folder Links: TPS55289-Q1

<sup>(2)</sup> Measured on TPS55289Q1EVM-011, 4-layer, 2-oz/1-oz/2-oz copper 91-mmx66-mm PCB.

$T_1 = -40$ °C to 125°C.  $V_{IN} = 12 \text{ V}$  and  $V_{OUT} = 20 \text{ V}$ . Typical values are at  $T_1 = 25$ °C. unless otherwise noted

|                       | PARAMETER                                      | TEST CONDITIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | MIN   | TYP   | MAX   | UNIT |

|-----------------------|------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|------|

|                       |                                                | VOUT_FS = 03h, REF = 0780h,<br>V <sub>REF</sub> = 1.129V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 19.7  | 20    | 20.3  | V    |

| ,                     | Output voltage when V <sub>REF</sub> is set to | VOUT_FS = 02h, REF = 0780h,<br>V <sub>REF</sub> = 1.129V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 14.78 | 15    | 15.22 | V    |

| V <sub>OUT_FULL</sub> | 1.129V                                         | VOUT_FS = 01h, REF = 0780h,<br>V <sub>REF</sub> = 1.129V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 9.85  | 10    | 10.15 | V    |

|                       |                                                | VOUT_FS = 00h, REF = 0780h,<br>V <sub>REF</sub> = 1.129V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 4.93  | 5     | 5.07  | V    |

|                       |                                                | VOUT_FS = 03h, REF = 0000h,<br>V <sub>REF</sub> = 45mV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0.74  | 0.8   | 0.86  | V    |

| /                     | Output voltage when V <sub>REF</sub> is set to | VOUT_FS = 02h, REF = 0000h,<br>V <sub>REF</sub> = 45mV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0.55  | 0.6   | 0.65  | V    |

| V <sub>OUT_ZERO</sub> | 45mV                                           | VOUT_FS = 01h, REF = 0000h,<br>V <sub>REF</sub> = 45mV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0.36  | 0.4   | 0.44  | V    |

|                       |                                                | VOUT_FS = 00h, REF = 0000h,<br>V <sub>REF</sub> = 45mV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0.18  | 0.2   | 0.22  | V    |

| REFERENCI             | E VOLTAGE                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |       |       |       |      |

|                       |                                                | External feedback with REF = 0780h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1.117 | 1.129 | 1.141 | V    |

| _                     | Reference voltage at the FB/INT pin            | External feedback with REF = 058Ch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0.837 | 0.846 | 0.855 | V    |

| $V_{REF}$             | when using external feedback                   | External feedback with REF = 0334h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0.502 | 0.508 | 0.514 | V    |

|                       |                                                | External feedback with REF = 01A4h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0.276 | 0.282 | 0.288 | V    |

| POWER SW              |                                                | External resultation with the second | 0.270 | 0.202 | 0.200 | •    |

| OWER SW               |                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |       |       |       |      |

|                       | Low-side MOSFET on resistance at buck side     | V <sub>OUT</sub> = 20V, V <sub>CC</sub> = 5.2V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       | 22    |       | mΩ   |

| R <sub>DS(on)</sub>   | High-side MOSFET on resistance at buck side    | V <sub>OUT</sub> = 20V, V <sub>CC</sub> = 5.2V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       | 14    |       | mΩ   |

| Bo(on)                | Low-side MOSFET on resistance at boost side    | V <sub>OUT</sub> = 20V, V <sub>CC</sub> = 5.2V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       | 11    |       | mΩ   |

|                       | High-side MOSFET on resistance at boost side   | V <sub>OUT</sub> = 20V, V <sub>CC</sub> = 5.2V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       | 11    |       | mΩ   |

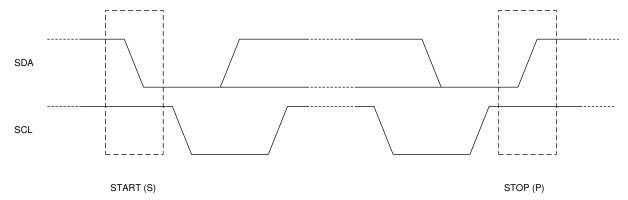

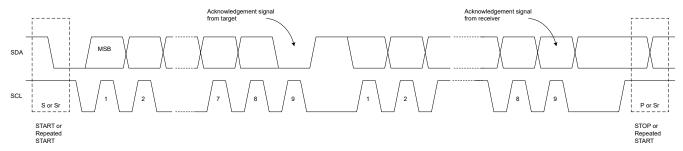

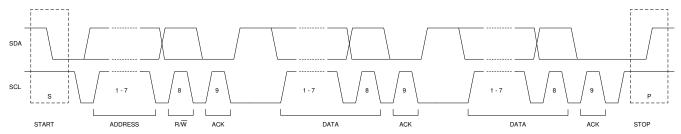

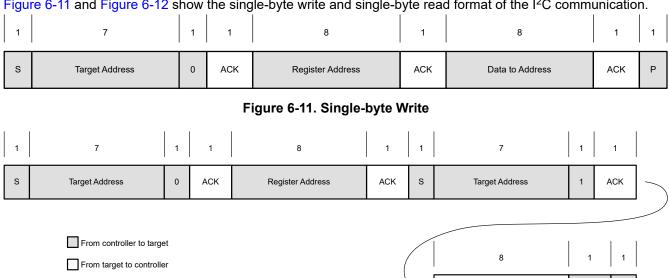

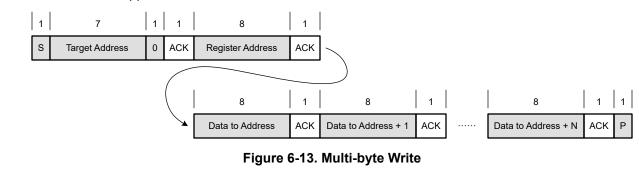

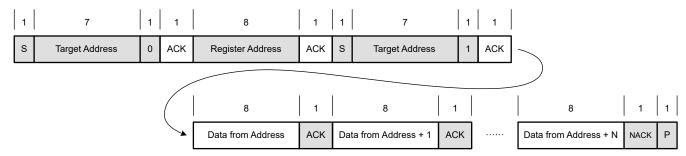

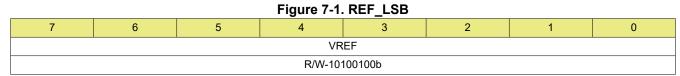

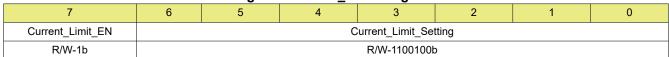

| NTERNAL (             | CLOCK                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |       |       |       |      |