### Improving Input Settling for Precision Data Converters

# 🔱 Texas Instruments

In high precision data acquisition applications the system's performance is susceptible to degradation from a variety of internal and external sources. For signal chains using a successive approximation register (SAR) analog to digital converter (ADC) such as those shown in Table 1, one noise source that can be easily overlooked is digital switching.

#### Table 1. Common Design Challenges with High-Speed, High-Resolution ADCs

| Challenges                                                                                       | Example System(s)                       | Solution                                                                                                                                  |

|--------------------------------------------------------------------------------------------------|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| Settled accuracy of high frequency signals                                                       | Motor and Servo<br>control and encoders | Wide Read<br>Cycle<br>decreases<br>required clock<br>rate, enabling a<br>longer quiet<br>window and<br>minimizes<br>ground plane<br>noise |

| System clock operates<br>at lower speeds to<br>conserve power                                    | Patient Monitoring<br>(ECG, EKG)        |                                                                                                                                           |

| Noisy ground causes<br>voltage reference to be<br>noisy and results in<br>inaccurate conversions | ADC with internal reference voltage     |                                                                                                                                           |

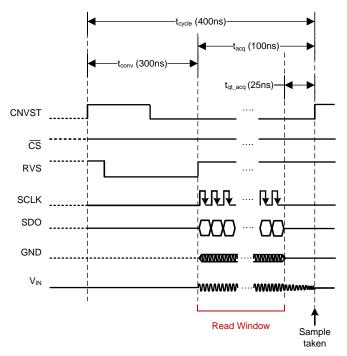

While communicating with the host processor, the ground plane can experience disturbances which couple into the analog input signal. However the impact of digital switching can be minimized by adjusting the period during which the conversion data is clocked out of the ADC. Transfer during this window of minimal interference is known as "Wide Read Cycle." A typical SAR ADC 'frame' is broken into two cycles: conversion ( $t_{conv}$ ) and acquisition ( $t_{acq}$ ), as shown in Figure 1.

During the acquisition cycle, an internal capacitor is being charged to the same voltage as the input signal. At the same time the ADC is clocking out the results of the previous conversion. It is recommended that a 'quiet time' be observed at the end of the acquisition cycle, during which no digital communication occurs. If digital switching occurs during this time, it is possible for disturbances in the ground plane to couple back onto the analog input as noise. During the conversion cycle, the ADC will compare the voltage on capacitor to a reference voltage to determine the value of the input signal.

## Figure 1. Conversion and Acquisition Cycle of a Typical SAR ADC

While the datasheet of a device specifies the minimum quiet time, some designs such as those with a sensitive ground layout will require a longer quiet period. In some cases, it is possible to increase the clock speed and read the data faster to create a longer quite time. For high-speed ( $\geq 1$  mega sample per second) and/or high-resolution ( $\geq 16$  bits) ADCs, this poses a challenge as the clock speed required may not be possible for the chosen host processor or would require a much more expensive one. For example, the ADS9120 is a 16-bit ADC with a cycle time of 400 ns ( $t_{cycle}$ ), a conversion time of approximately 300 ns ( $t_{conv}$ ) and a quiet time of 25 ns ( $t_{qt\_acq}$ ). The clock rate can be calculated with the following two equations, which at full throughput is 213.3 MHz.

$$t_{read} = t_{cycle} - t_{conv} - t_{qt_acq} = 75 ns$$

$$f_{sclk} = \frac{resolution}{t_{read}} = 213.3 \text{ MHz}$$

1

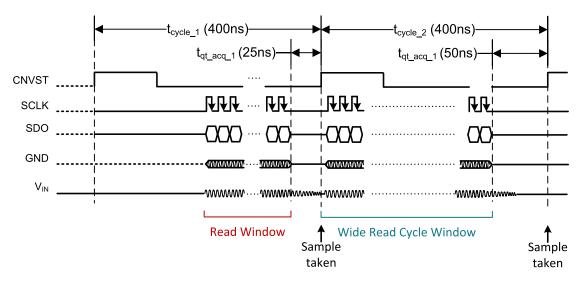

Not only is a 213.3 MHz clock beyond the capability of most SARs, including the ADS9120 which is limited to an SCLK speed of 75 MHz, it also requires an expensive host processor. However, ADCs enabled with Wide Read Cycle are capable of adjusting when the data is read and even the length of the read window. Specifically it can read the data during the conversion and/or acquisition cycles and change the length of the read window by adjusting the clock speed, as shown in Figure 2.

With Wide Read Cycle, it is possible to significantly increase the quiet time and decrease the clock speed. If the goal is to double the quiet time (50 ns) and decrease the clock speed as much as possible, then equation 1 is updated to equation 3 as  $t_{conv}$  is now a part of  $t_{read}$ :

$$t_{read} = t_{cycle} - t_{qt_acq} = 350 \text{ ns}$$

Solving 2 with the new  $t_{read}$  value results in a clock rate of 45.7 MHz which is well within the SPI clock speeds of a typical MCU or FPGA.

Although ground sensitivity does not always impact the performance of a data acquisition system, increasing the quiet time will help to ensure more accurate settling and thus better performance. By changing when the data is clocked out of the ADC, Wide Read Cycle enables a longer quiet time and a slower clock rate. This enables high-speed, high-resolution SAR ADCs to be used at full throughput with host processors that otherwise would be unable to provide a fast enough clock speed. To learn more about wide read zone, as well as other features that enable more robust designs with high performance SAR ADCs, be sure to check out the resources section.

### Resources

- More information on Wide Read Zone and Other Enhanced SPI Interface Features

- TI Precision Labs Comprehensive ADC Training

- Analog Engineer Calculator

Figure 2. Wide Read Cycle Window versus Traditional Data Read Window

| Device   | Description                                                                           | Full Throughput SCLK Speed<br>without Wide Read Cycle | Lowest SCLK Speed with Wide Read Cycle |

|----------|---------------------------------------------------------------------------------------|-------------------------------------------------------|----------------------------------------|

| ADS8900B | 20-Bit, 1-MSPS SAR ADC with Integrated<br>Reference Buffer and enhanced SPI interface | 75-MHz                                                | 21-MHz                                 |

| ADS8910B | 18-Bit, 1-MSPS SAR ADC with Integrated<br>Reference Buffer and enhanced SPI interface | 67-MHz                                                | 19-MHz                                 |

| ADS8920B | 16-Bit, 1-MSPS SAR ADC with Integrated<br>Reference Buffer and enhanced SPI interface | 60-MHz                                                | 17-MHz                                 |

| ADS9110  | 18-Bit, 2-MSPS SAR ADC with enhanced SPI interface                                    | 144-MHz                                               | 38-MHz                                 |

| ADS9120  | 16-Bit, 2.5-MSPS SAR ADC with enhanced SPI interface                                  | 214-MHz                                               | 43-MHz                                 |

#### IMPORTANT NOTICE FOR TI DESIGN INFORMATION AND RESOURCES

Texas Instruments Incorporated ('TI") technical, application or other design advice, services or information, including, but not limited to, reference designs and materials relating to evaluation modules, (collectively, "TI Resources") are intended to assist designers who are developing applications that incorporate TI products; by downloading, accessing or using any particular TI Resource in any way, you (individually or, if you are acting on behalf of a company, your company) agree to use it solely for this purpose and subject to the terms of this Notice.

TI's provision of TI Resources does not expand or otherwise alter TI's applicable published warranties or warranty disclaimers for TI products, and no additional obligations or liabilities arise from TI providing such TI Resources. TI reserves the right to make corrections, enhancements, improvements and other changes to its TI Resources.

You understand and agree that you remain responsible for using your independent analysis, evaluation and judgment in designing your applications and that you have full and exclusive responsibility to assure the safety of your applications and compliance of your applications (and of all TI products used in or for your applications) with all applicable regulations, laws and other applicable requirements. You represent that, with respect to your applications, you have all the necessary expertise to create and implement safeguards that (1) anticipate dangerous consequences of failures, (2) monitor failures and their consequences, and (3) lessen the likelihood of failures that might cause harm and take appropriate actions. You agree that prior to using or distributing any applications. TI has not conducted any testing other than that specifically described in the published documentation for a particular TI Resource.

You are authorized to use, copy and modify any individual TI Resource only in connection with the development of applications that include the TI product(s) identified in such TI Resource. NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT OF TI OR ANY THIRD PARTY IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information regarding or referencing third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of TI Resources may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

TI RESOURCES ARE PROVIDED "AS IS" AND WITH ALL FAULTS. TI DISCLAIMS ALL OTHER WARRANTIES OR REPRESENTATIONS, EXPRESS OR IMPLIED, REGARDING TI RESOURCES OR USE THEREOF, INCLUDING BUT NOT LIMITED TO ACCURACY OR COMPLETENESS, TITLE, ANY EPIDEMIC FAILURE WARRANTY AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY YOU AGAINST ANY CLAIM, INCLUDING BUT NOT LIMITED TO ANY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON ANY COMBINATION OF PRODUCTS EVEN IF DESCRIBED IN TI RESOURCES OR OTHERWISE. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, DIRECT, SPECIAL, COLLATERAL, INDIRECT, PUNITIVE, INCIDENTAL, CONSEQUENTIAL OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF TI RESOURCES OR USE THEREOF, AND REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

You agree to fully indemnify TI and its representatives against any damages, costs, losses, and/or liabilities arising out of your noncompliance with the terms and provisions of this Notice.

This Notice applies to TI Resources. Additional terms apply to the use and purchase of certain types of materials, TI products and services. These include; without limitation, TI's standard terms for semiconductor products <a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation modules, and samples (<a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2017, Texas Instruments Incorporated