Application Report

SLAA633-August 2014

# Interfacing to the ADS8363 Pseudo-Differential Operating Mode

Martin Li

Precision Analog - Engery Solutions Products

## ABSTRACT

This application note presents several methods for interfacing the ADS8363; a dual, 16-bit, 2x2 or 4x2 channel simultaneous sampling analog-to-digital converter (ADC). This application note focuses on interfacing to the pseudo differential operating mode ADS8363, employing both the Multichannel Buffered Serial Port (McBSP) port and a combination of Serial Peripheral Interface (SPI) and pulse width modulator (PWM) peripheral, in the C2000 DSP to highlight the compatibility of the interface. The TMS320F28377D experiment kit is used to provide the source code in this application note. Project collateral discussed in this application note can be downloaded from the following URL: <a href="http://www.ti.com/lit/zip/SLAA633">http://www.ti.com/lit/zip/SLAA633</a>.

### Contents

| 1 | Introdu | ction                          | 2              |

|---|---------|--------------------------------|----------------|

| 2 | Hardwa  | are Platform                   | 2              |

| 3 | Hardwa  | are Interfaces                 | 2              |

|   | 3.1     | Communication via McBSP        | 2              |

|   | 3.2     | Communication via SPI and ePWM | 5              |

| 4 | Softwa  | re Interface                   | 7              |

|   | 4.1     | McBSP Settings                 | 7              |

|   | 4.2     | SPI and ePWM Settings          | 8              |

|   | 4.3     | Software Flow                  |                |

| 5 | Refere  | nces                           | <mark>9</mark> |

### List of Figures

| 1 | Hardware Connections via McBSP                          | 3 |

|---|---------------------------------------------------------|---|

| 2 | Mode II Waveforms using McBSP                           | 4 |

| 3 | Expanded Mode II Waveform                               | 4 |

| 4 | Continuous Conversion in Mode II                        | 4 |

| 5 | Hardware Connections for Mode II via SPI and ePWM       | 5 |

| 6 | Mode II Waveforms using SPI and Epwm                    | 6 |

| 7 | Expanded First Conversion Cycle                         | 6 |

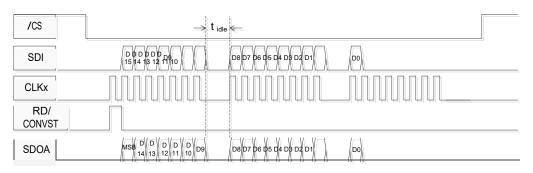

| 8 | Interfacing to ADS8363 with an 8-bit SPI without Buffer | 6 |

| 9 | Software Flow Chart                                     | 9 |

### List of Tables

| 1 | Channel Selection             | 2 |

|---|-------------------------------|---|

| 2 | Key Register Setting of McBSP | 7 |

| 3 | Key Register Setting o SPI    | 8 |

| 4 | Key Register Setting of ePWM  | 8 |

### 1 Introduction

The ADS8363 is a dual, 16-bit, 1MSPS SAR ADC with eight input channels, which is configurable as eight pseudo-differential inputs (4x2) or four fully differential inputs (2x2). The 8 input channels are grouped into two pairs, followed by two independent sample and hold circuits for simultaneous signal acquisition. Based on the MODE pin M0/M1 configuration, this part can be configured as any combination of manual or automatic sequencing channel selection with two serial data output or single serial data output, as shown in Table 1.

| MO | M1 | Channel Selection | Output Pin Used |

|----|----|-------------------|-----------------|

| 0  | 0  | Manual (via SDI)  | SDOA and SDOB   |

| 0  | 1  | Manual (via SDI)  | SDOA only       |

| 1  | 0  | Automatic         | SDOA and SDOB   |

| 1  | 1  | Automatic         | SDOA only       |

### **Table 1. Channel Selection**

The channel information bits (one bit of channel indicator, followed by one bit of ADC indicator before the most significant bit of conversion result) are only available in fully-differential operating mode. For the consideration of channel identification, manual channel selection mode should be used when ADS8363 is operating in pseudo-differential operating mode. Furthermore, for compatibility with most processors, single serial data output mode is selected in this application note, therefore, Mode II is mainly discussed in the following sections.

# 2 Hardware Platform

The ADS72-8363 EVM provides a platform to evaluate the functionality of the ADS7223/ADS8363 ADC. This EVM can be used to connect with various DSPs or micro controllers from TI, while allowing easy access to both analog and digital signals for customized end-user applications. More information about the EVM is available in the ADS7263/ADS8363EVM User Guide (SBAU185).

The *C2000 Experimenter Kits* from Texas Instruments are ideal products for initial device exploration and testing. The *DelfinoF28377D Experimenter Kit* has a docking station that features on-board USB JTAG emulation, and access to all control CARD signals, breadboard areas, and RS-232 and JTAG connectors. Refer to <a href="http://www.ti.com/tool/tmdxdock28377d">http://www.ti.com/tool/tmdxdock28377d</a> for more details about this kit.

The combination of the *DelfinoF28377D Experimenter Kit* and the *ADS72-8363 EVM* is a convenient way to experiment with interfacing the TMS320F28377D DSP to the ADS8363.

### **3 Hardware Interfaces**

The TMS320F28377D comes with McBSP and SPI for communication with serial devices such as the ADS8363. In addition, it inherently brings multi-channel enhanced pulse width modulator (ePWM) peripheral, which has the flexible capability of synchronization. Two methods for interfacing with the ADS8363 are presented in the following sections.

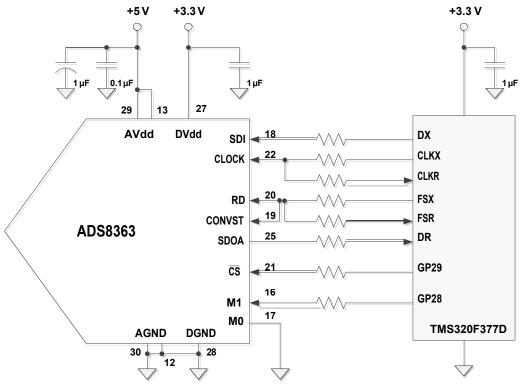

The resistor between the DSP and ADS8363 shown in the hardware connection (see Figure 1) is a reminder that high-speed digital signals can cause unwanted ringing in digital system which could ultimately degrade system performance. The requirement for the resistor depends on the clock speed, trace length and physical PCB layout in the end design.

# 3.1 Communication via McBSP

2

The McBSP consists of a data path and a control path to external devices. With the help of separated pins for transmission and reception, it supports full-duplex buffered data communication with a wide selection of data sizes: 8, 12, 16, 20, 24, and 32 bits. The McBSP also has four pins dedicated to the independent clocking and frame synchronizing for reception and transmission. More importantly, it integrates a programmable sample rate generator for internal generation and control of clock signals and frame synchronization signals. Because of these features, the McBSP easily communicates with different kinds of devices.

### 3.1.1 Using McBSP1

The 3.3-V compatible digital interface of the ADS8363 allows for a seamless connection between the TMS320F28377D Experiment Kit and the ADS72-8363 EVM. The hardware connections are shown in Figure 1. The chip select (CS) pin is controlled by the GPIO pin on the F28377D DSP to enable the ADS8363 before any operation, thus allowing multiple devices to share the McBSP peripheral. Configure the internal sample rate generator (SRG) in McBSP to generate the transmit clock signal (CLKX). The Frame Sync Transmit (FSX) pulse can be used as the data read (RD) signal, since it is synchronized to the CLKX signal and its width can be set as 1 CLKX cycle. CLKR and FSR in the McBSP are defined as clock and frame synchronization signals for reception. In order to minimize the phase shift between receive data (DR) and receive clock(CLKR), CLKR is connected to the CLKX at the point which is very close to the ADS8363. FSR is connected in the same way.

In Mode II, the ADS8363 needs 40 clock cycles to output the conversion result from both ADCs. If the start of the conversion (CONVST) signal is issued every 20 clock cycles (required for RD signal at that time) as in Mode I, every second pulse is ignored automatically, The CONVST signal can be connected to the FSX as well. To ensure proper functionality and avoid corruption of the output data, the FSX signal should not be longer than one clock cycle.

Figure 1. Hardware Connections via McBSP

As shown in Figure 1, the configuration command is sent through the DX pin of McBSP to the ADS8363 SDI pin, including the reference voltage configuration, power mode configuration, input mode configuration, input channel selection, and so forth. The conversion result of both ADCs is transmitted through SDOA to DR pin in Mode II, the SDOB pin is not used in this particular operation mode.

For Mode II operation, control the M1 with GPIO, while connecting the M0 to ground, so that the time of changing the operation mode from Mode I to Mode II is precisely controlled by processor. With this method, you can foresee the channel information of the serial output, thus minimizing the software overhead of identifying the channel information of the conversion result.

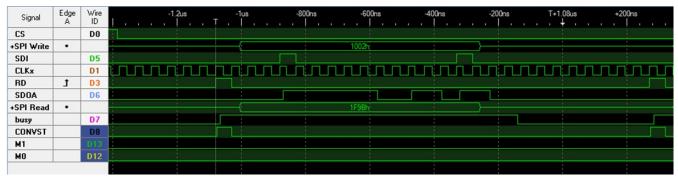

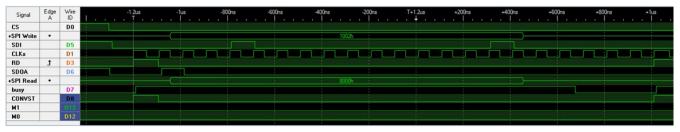

Figure 2 shows the initialization process for Mode II using the previously mentioned hardware setup. Figure 3 shows magnification to one conversion cycle. The rising edge of RD and CONVST signal is synchronized to the rising edge of conversion clock and the width is set to be one clock period, the entire cycle repeats every 27 clock periods.

| Signal     | Edge<br>A | Wire<br>ID | і. т          | -6us    |         | 5us     | -4us |          | 3us | -2us     |          | -1us | T+6.61us    |

|------------|-----------|------------|---------------|---------|---------|---------|------|----------|-----|----------|----------|------|-------------|

| CS         |           | DO         |               |         |         |         |      |          |     |          |          |      |             |

| +SPI Write | •         |            | +             | 1002h } | (       | 03FFh } |      | 1005h }- |     | 03FFh    | <u> </u> |      |             |

| SDI        |           | D5         | -             |         | - 16 m. |         | i i  |          | 1   |          |          |      |             |

| CLKx       |           | D1         | néonononitoro |         |         |         |      |          |     | nnnnnnkn |          |      | ANNANANAN A |

| RD         | t         | D3         |               |         |         |         |      |          |     |          |          |      |             |

| SDOA       |           | D6         |               |         |         |         |      |          |     |          |          |      |             |

| +SPI Read  | •         |            | C             | 1F9Bh   |         | 03F5h } |      | 07F4h }- |     | 07EDh    | <u> </u> |      |             |

| busy       |           | D7         |               |         |         |         |      |          |     |          |          |      |             |

| CONVST     |           | D8         | 1             |         |         |         | П    |          |     |          |          |      |             |

| M1         |           |            |               |         |         |         |      |          |     |          |          |      |             |

| MO         |           | D12        |               |         |         |         |      |          |     |          |          |      |             |

|            |           |            |               |         |         |         |      |          | 1   | 1        |          |      |             |

Figure 2. Mode II Waveforms using McBSP

Figure 3. Expanded Mode II Waveform

The previously introduced interface scheme can be used in fully-differential input mode too, the only thing that needs to be changed is the "PDE" bit, which needs to be cleared in the CONFIG register.

# 3.1.2 Channel Identification

The fixed output sequence of the serial port can be used to identify the channel information of conversion results. In Mode II operation, after selecting the conversion channels via SDI at the beginning, another conversion cycle in needed to convert the selected channels. The following two conversion cycles are used to output the conversion result. For continuous conversion with channel sweeping in this operation mode, the channel selection command needs to be sent at the read cycle when the BUSY signal is low, in which case, the CONVST signal is ignored.

To maximize the operation efficiency, it's suggested to set the M1 to high between the first two RD/CONVST signals shown as Figure 4, so that the first conversion cycle is used to set the channels which will be converted at the second conversion cycle, at which point the actual Mode II operation starts. The valid conversion result output starts with channel Ax ("x" depends on the channel configuration at the first conversion cycle, A0 in Figure 4) at the third conversion cycle.

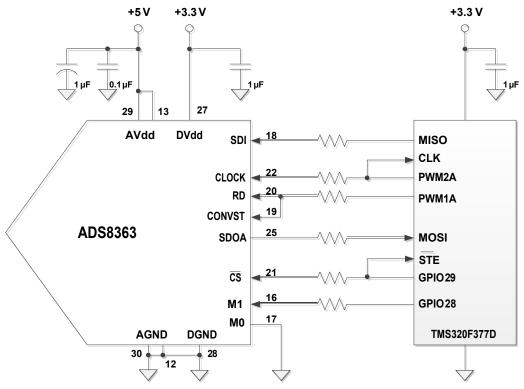

# 3.2 Communication via SPI and ePWM

For those processors which the McBSP peripheral is not available, it is possible to use the SPI and ePWM peripheral together to interface with the ADS8363. The ePWM peripheral used here needs to include at least two modules and have the capability of synchronizing to each other.

# 3.2.1 Using SPI and ePWM

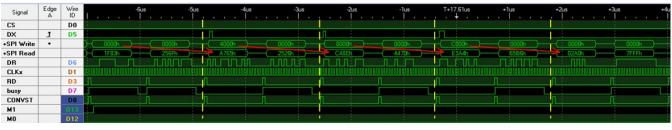

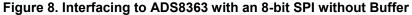

One SPI port and two ePWM modules are combined together to interface with the ADS8363 in this interfacing scheme, shown as Figure 5. The SPI port is configured as a slave device, the clock signal is provided from one of the ePWM modules, another ePWM module is used to control the RD and CONVST signal. These two ePWM modules are synchronized to each other with the time-base counter synchronization scheme.

Figure 5. Hardware Connections for Mode II via SPI and ePWM

As shown in Figure 5, The SDI and SDOA signal of ADS8363 are connected to the MISO and MOSI of the SPI port, respectively. Since the RD signal needs a falling clock edge to be validated, the transmitted data of the SPI port needs to be 1-bit right shifted. Detail of the software implementation is discussed in Section 4. Figure 6 shows one burst conversion series with eight conversion cycles and the corresponding six valid conversion results. The expanded first conversion cycle is shown in Figure 7.

| Signal     | Edge | Wire<br>ID | ÷       |       | -12us         |        | -10us  | 8us       |        | -6us  |               | -4us  |                 | -2us  |

|------------|------|------------|---------|-------|---------------|--------|--------|-----------|--------|-------|---------------|-------|-----------------|-------|

|            | A    |            |         |       |               |        |        | <br>      |        |       |               | •     | • •             | · · · |

| CS         |      | DO         |         |       |               |        |        | 11        |        |       |               | 11    |                 |       |

| +SPI Write | •    |            | <br>-   | 1002h | $\rightarrow$ |        | Fh 🔂 — | <br>ih )— | -      | 03FFh | )(            | 1060h | $\rightarrow$ — |       |

| SDI        |      | D5         |         |       | _1            |        |        | <br>      |        |       |               | ЛП    |                 |       |

| CLKx       |      | D1         |         |       |               |        |        |           | UUUUUU |       |               |       |                 |       |

| RD         | t    | D3         | _1      |       |               | Л      |        |           |        |       |               |       |                 | 1     |

| SDOA       |      | D6         | 1./     |       |               | $\Box$ |        |           |        |       | Π             |       |                 |       |

| +SPI Read  | •    |            | $+\Box$ | 8000h |               | -{ 035 | 7h     | <br>*     | -      | )7EDh | $\rightarrow$ | 07EAh | $\rightarrow$   |       |

| busy       |      | D7         |         |       |               |        |        |           |        |       |               |       |                 |       |

| CONVST     |      | D8         | _1      |       |               | Л      |        |           |        |       |               |       |                 | 1     |

| M1         |      |            |         |       |               |        |        |           |        |       |               |       |                 |       |

| MO         |      | D12        |         |       |               |        |        | 17        |        | 17    |               |       |                 |       |

Figure 6. Mode II Waveforms using SPI and Epwm

Figure 7. Expanded First Conversion Cycle

If there are two serial ports (McBSP + SPI or 2 SPI) available in the application, it is possible to communicate with the ADS8363 with both the SDOA and SDOB serial outputs. Details are found in chapter 3.2 of <u>SLAA167</u>.

# 3.2.2 SPI Peripheral Requirement

The ADS8363 needs at least 20 clock cycles to finish one conversion cycle. To ensure the conversion accuracy or maintain the constant conversion speed, it would be helpful if the SPI peripheral used here has the capability of handling at least 20 bits of data size or integrates with transmit and receive buffers. Otherwise, the software implementation should specify that the idle time between the two conversion portion,  $t_{idle}$ , is less than the maximum clock period (2 µs in the ADS8363 while operating at half-clock mode). Figure 8 shows the waveform using an 8-bit SPI without transmit and receive buffer interfacing to the ADS8363.

### 4 Software Interface

All of the software is written in C language and compiled with Code Composer Studio version 5.5. The following sections describe the setup of the McBSP port, as well as the setup of SPI and ePWM peripheral for interfacing with Mode II operation of the ADS8363. Both polling and interrupt methods for McBSP received data process are used in the source code.

# 4.1 McBSP Settings

The McBSP is programmed as a serial port with the internal sample rate generator (SRG) configured to generate the internal data clock (CLKG), which is used as internal transmit clock (CLKX). The transmitter and receiver are set as 16-bit operation with a one-bit delay after frame synchronization and before the transmission/reception of the first bit of the frame.

The transmit frame-synchronization pulse (FSX) is generated by the SRG, the width of the FSX should be set as one CLKX clock cycle. Depending on whether the polling or interrupt mechanism is used to process the transmission and reception data, the FSX needs to be set as: (1) generated when the transmit register is written or (2) periodically based on the setting of FPER bits in SRGR2 register. Table 2 lists the key register settings of McBSP interfacing with the ADS8363 using polling or interrupt methodology.

| Register         | Setting for Polling<br>Operation | Setting for Interrupt<br>Operation | Comments                                    |

|------------------|----------------------------------|------------------------------------|---------------------------------------------|

| SRGR2.bit.CLKSM  | 1                                | 1                                  | SRG use LSPCLK as input clock               |

| PCR.bit.SCLKME   | 0                                | 0                                  | - SKG use LSPCEK as input clock             |

| SRGR1.bit.CLKGDV | 9                                | 9                                  | Clock divider                               |

| PCR.bit.CLKXM    | 1                                | 1                                  | CLKX is driven by CLKG                      |

| RCR1.bit.RWDLEN1 | 2                                | 2                                  | Set as 16 hit operation                     |

| XCR1.bit.XWDLEN1 | 2                                | 2                                  | <ul> <li>Set as 16-bit operation</li> </ul> |

| RCR2.bit.RDATDLY | 1                                | 1                                  | one-bit delay on data receive and           |

| XCR2.bit.XDATDLY | 1                                | 1                                  | transmit                                    |

| PCR.bit.FSXM     | 1                                | 1                                  | FSX is driven by CLKG                       |

| SRGR1.bit.FWID   | 0                                | 0                                  | FSX is 1 CLKG cycle width                   |

| SRGR2.bit.FSGM   | 0                                | 0                                  | Different ways to generate FSX              |

| SRGR2.bit.FPER   | -                                | 21                                 | Period between two FSX signal               |

| MFFINT.bit.XINT  | -                                | 1                                  | Enable Ty/Dy interrupt                      |

| MFFINT.bit.RINT  | -                                | 1                                  | Enable Tx/Rx interrupt.                     |

Table 2. Key Register Setting of McBSP

In the sample code, the ADS8363 is running with a serial clock of 20 MHz, which is achieved by divide ten from low-speed peripheral clock (LSPCLK). The fixed data rate continuous conversion of ADS8363 is realized by using interrupt mechanism to process the data in McBSP, while the ADS8363 is configured using polling mechanism to process the data in McBSP, shown as the following lines of code.

```

for(loopcount = 0; loopcount<5; loopcount ++)

{

mcbsp_xmit(Txdata[Txcounter++],0);

while(McbspaRegs.SPCR1.bit.RRDY == 0) { ; } // Check for receive available?

Rxdata[Rxcounter++] = McbspaRegs.DRR1.all; // read out result.

while(McbspaRegs.SPCR2.bit.XRDY == 0) { ; } // Check for transmit ready?

}</pre>

```

### 4.2 SPI and ePWM Settings

TMS320F28377D integrates with high-speed synchronous SPI that allows a serial bit stream of programmed length (1 to 16 bits) to be shifted into and out of the device, furthermore, it supports a 16-level receive and transmit FIFO.

In this interfacing scheme, the SPI port is configured as a slave device with 4-wire mode operation. For compatibility with ADS8363 timing diagram, the SPI port is set to output data on rising edge and input data on falling edge with non-delayed clock.

In the source code, the character length of the SPI port is set as 11 bits, a buffer is employed in the transmission and reception, the next word in the buffer is transferred immediately upon completion of transmission of the previous one, thus combining two SPI transmissions into one ADS8363 conversion cycle; the following several lines of code shows the translation between them. Table 3 lists the key register settings of the SPI port previously described.

### Table 3. Key Register Setting o SPI

| Register                             | Setting | Comments                                                                                           |  |  |  |  |

|--------------------------------------|---------|----------------------------------------------------------------------------------------------------|--|--|--|--|

| SPICTL.all 0x0002 As a slave, normal |         | As a slave, normal SPI clocking scheme without delay                                               |  |  |  |  |

| SPIPRI.bit.TRIWIR<br>E               | 0       | Normal 4-wire SPI mode                                                                             |  |  |  |  |

| SPIFFCT                              | 0x0000  | The next word in buffer is transferred immediately upon completion of transmission of previous one |  |  |  |  |

| SPICCR.all                           | 0x008A  | 11 bits; data output on rising edge, input on falling edge                                         |  |  |  |  |

The two ePWM modules used is set to clock at the same rate and counter mode, with different counter period so that they could be used as RD/CONVST signal or clock signal. The counter value of ePWM2 module is synchronized to be zero when the counter value of ePWM1 module reaches to zero. Key register setting for ePWM module is shown in Table 4.

| Register            | ePWM1 Settings | PWM2 Settings | Comments                                        |  |  |

|---------------------|----------------|---------------|-------------------------------------------------|--|--|

| TBCTL.bit.HSPCLKDIV | 1              | 1             | Set the time base clock rate                    |  |  |

| TBCTL.bit.CLKDIV    | 1              | 1             |                                                 |  |  |

| TBCTL.bit.CTRMODE   | 0              | 0             | Set the counter mode as up-count mode           |  |  |

| TBPRD               | 219            | 9             | Set the period of the time-base counter         |  |  |

| AQCTLA.bit.ZRO      | 2              | 2             | Set the ePWM module output action               |  |  |

| AQCTLA.bit.CAU      | 1              | 1             |                                                 |  |  |

| CMPA.half.CMPA      | 10             | 5             | Set compare register to control duty cycle      |  |  |

| TBCTL.bit.PHSEN     | 0              | 1             | Synchronization control, ePWM1 as master, ePWM2 |  |  |

| TBCTL.bit.SYNCOSEL  | 1              | 0             | as slave                                        |  |  |

| TBPHS.half.TBPHS    | 0              | 0             | Set the counter value after synchronization     |  |  |

# 4.3 Software Flow

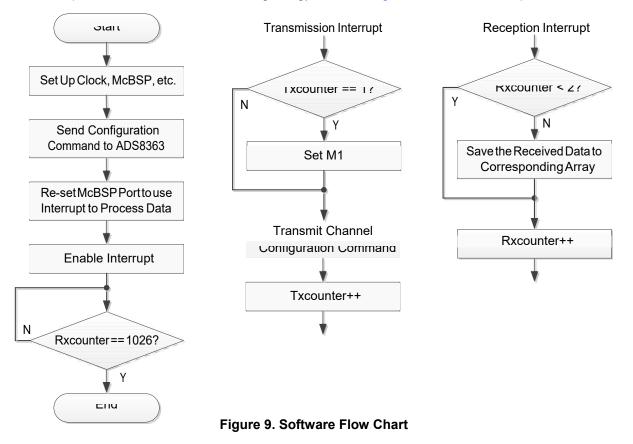

The sample code presented in this application report comes in two project files and two workspaces, corresponding to using the McBSP port or combining an SPI port with ePWM peripheral interfacing with the ADS8363.

Software Interface

In the program using McBSP port to interface with the ADS8363, the McBSP and other peripherals are configured appropriately once entering the main function. The configuration command for the ADS8363 is sent, after that, the McBSP port is reset to use interrupt instead of polling to process the transmission and reception data. At this time, the channel configuration command can be sent and the corresponding conversion result is retrieved via interrupt routine. The program ends with 1026 data (128 data per channel, plus with 2 invalid data at the beginning) received. Figure 9 shows the example flow chart.

# 5 References

- 1. ADS8363 data sheet (<u>SBAS523</u>B)

- 2. TMS320F2837xD Technical Reference Manual (SPRUHM8)

- 3. TMS320F28x Multichannel Buffered Serial Port (McBSP) Peripheral Reference Guide (SPRU061)

- 4. F2837xD Firmware Development Package User's Guide (F2837xD-FRM-EX-UG-100)

### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale (www.ti.com/legal/termsofsale.html) or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2019, Texas Instruments Incorporated