# Application Brief **ADS16axx Reference Options**

## Texas Instruments

Tom Hendrick

Precision Analog – Delta Sigma Converters

#### Introduction

The ADS1605, ADS1606 and ADS1625, ADS1626 can operate from an internal or external voltage reference. In either case, the reference voltage VREF is set by the differential voltage between VREFN and VREFP: VREF = (VREFP – VREFN). VREFP and VREFN each use two pins, which should be shorted together. VMID equals approximately 2.5 V and is used by the modulator. VCAP connects to an internal node and must also be bypassed with an external capacitor. For the best analog performance, it is recommended that an external reference voltage (VREF) of 3 V be used.

#### **Internal Reference**

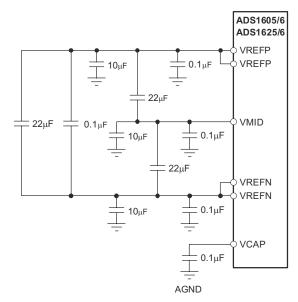

To use the internal reference, set the REFEN pin low. This activates the internal circuitry that generates the reference voltages. The internal reference voltages are applied to the pins. Good bypassing of the reference pins is critical to achieve optimum performance and is done by placing the bypass capacitors as close to the pins as possible. Figure 1 shows the recommended bypass capacitor values. Use high quality ceramic capacitors for the smaller values. Avoid loading the internal reference with external circuitry. If the ADS1605, ADS1606 or ADS1625, ADS1626 internal reference is to be used by other circuitry, buffer the reference voltages to prevent directly loading the reference pins.

Figure 1. Internal Reference Bypassing

1

#### **Internal Reference Start Up**

The internal band-gap reference has two start-up mechanisms. The first is a static mechanism that ensures some current is present in the output stage of the band gap. The second is a transient mechanism which ensures the proper output voltage. This dual start-up approach provides coverage across silicon process variations and is triggered at power-up of the DVDD supply or by toggling the power down (PD) pin.

When not in use, the ADS1605, ADS1606 and ADS1625, ADS1626 can be powered down by taking the  $\overline{PD}$  pin low. All circuitry will be shutdown, including the voltage reference. There is an internal pullup resistor of 170 k $\Omega$  on the  $\overline{PD}$  pin, but it is recommended that this pin be connected to a general purpose I/O pin to help ensure proper start-up of the reference when power cycling the device at cold temperatures.

When power cycling the ADS1605, ADS1606 and ADS1625, ADS1626 below  $-20^{\circ}$ C, it is recommended to allow the voltage present on the VCAP pin (pin 59) to drain completely to 0 V before the application of the analog supply voltage (AVDD) and the digital supply voltage (DVDD). If the reference voltage does not recover at power-up, toggling the  $\overline{PD}$  pin will allow the reference to recover. An alternate method to ensure proper reference recovery is to include a 50-k $\Omega$  resistor from VCAP (pin 59) to AVDD.

#### **External Reference**

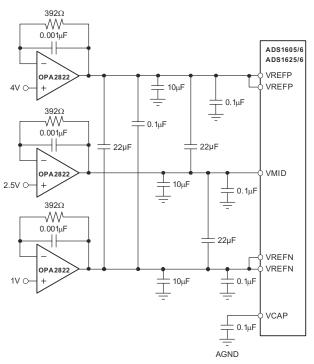

To use an external reference, set the REFEN pin high. This deactivates the internal generators for VREFP, VREFN and VMID, and saves approximately 25 mA of current on the analog supply (AVDD). The voltages applied to these pins must be within the values specified in the Electrical Characteristics table. Typically VREFP = 4 V, VMID = 2.5 V and VREFN = 1 V. The external circuitry must be capable of providing both a dc and a transient current.

Figure 2 shows the recommended circuitry for driving these reference inputs. Keep the resistances used in the buffer circuits low to prevent excessive thermal noise from degrading performance. Layout of these circuits is critical, make sure to follow good high-speed layout practices. Place the buffers and especially the bypass capacitors as close to the pins as possible. VCAP is unaffected by the setting on REFEN and must be bypassed when using the internal or an external reference.

Figure 2. Recommended External Reference Buffer Circuit

### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022, Texas Instruments Incorporated