# Programmable, two-stage, high-side current source circuit

Garrett Satterfield

## **Design Goals**

| Supply Voltage (V <sub>cc</sub> ) | DAC Output<br>Voltage | Output Current | Error   | Max Load<br>Resistance | Compliance<br>Voltage |

|-----------------------------------|-----------------------|----------------|---------|------------------------|-----------------------|

| 5V                                | 0V-2V                 | 0–100mA        | <1% FSR | 45Ω                    | 4.5V                  |

## **Design Description**

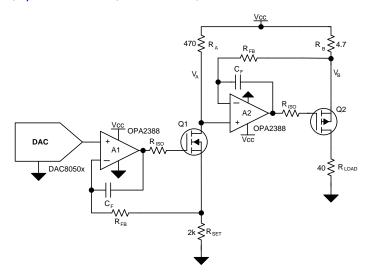

The programmable high-side current source supplies an adjustable current to a ground reference load. The first op amp stage sets a reference current based on the DAC output voltage. The second op amp stage acts as a current mirror that gains the reference current and regulates the current sourced from the output PMOS to the load.  $R_{\text{SET}}$ , RA, and RB set the output current based on the DAC voltage. Components  $C_{\text{COMP}}$ ,  $R_{\text{ISO}}$ , and  $R_{\text{FB}}$  provide compensation to ensure stability of the circuit. Common end equipment that utilize this circuit include *PLC Analog Output Modules*, *Field Transmitters*, *Digital Multimeters*, *Printers*, *Optical Modules*, *LED Drivers*, and *EPOS*.

## **Design Notes**

- 1. Choose a DAC with low offset, gain, and drift errors. RRIO op amps should be used to maintain low compliance voltage and op amps with low offset should be selected.

- 2. Minimize the current flow through R<sub>A</sub>, Q1, and R<sub>SET</sub>by selecting a large ratio of R<sub>A</sub>:R<sub>B</sub> to maximize efficiency while also minimizing heating and drift in the first stage.

- 3. Use high-precision, low-drift resistors for  $R_{\text{SET}}$ ,  $R_{\text{A}}$ , and  $R_{\text{B}}$  to minimize error caused by resistor mismatch and temperature drift.

- 4. Minimize the resistance of R<sub>B</sub> to maximize compliance voltage.

- 5. Avoid placing Q2 near thermally sensitive components in layout as the power dissipation causes heating.

## **Design Steps**

Set the reference current in the sink stage by selecting R<sub>SET</sub> based on V<sub>DAC</sub>. The reference current should be minimized as it flows directly to ground and reduced efficiency. Set the reference current to 1mA and calculate R<sub>SET</sub>.

$$R_{SET} = \frac{V_{DAC,max}}{I_{SET}} = \frac{2V}{1mA} = 2k\Omega$$

- 2. Select the required gain ratio based on the desired output current and  $I_{OUT}/I_{SET} = 100 \text{mA}/1 \text{mA} = 100$ , this is the required ratio of  $R_A:R_B$ .

- 3. Calculate the maximum value of R<sub>B</sub> from the maximum allowable voltage drop to drive the maximum current through the maximum load.

$$R_B < \frac{V_{CC} - I_{OUT,max} R_{LOAD,max}}{I_{OUT,max}} = \frac{5V - 0.1A*45\Omega}{0.1A} = 5\Omega$$

4. The voltage  $V_A$  is  $V_{CC} - I_{SET}xR_A$  which is equal to the voltage  $V_B$  due to the op amp feedback. Select  $R_A$  to achieve a voltage drop of <500mV to maintain the desired compliance voltage. A standard resistance of 4.7 $\Omega$  is chosen.

$$\begin{split} &V_A \,= V_B \\ &R_A \,= \frac{V_{CC} - V_A}{I_{SET}} = \frac{470 mV}{1mA} = 470 \Omega \end{split}$$

5. Calculate R<sub>B</sub> based on R<sub>A</sub> and the gain selected in step 2.

$$R_{B} = \frac{R_{A}}{100}$$

6. Verify the power dissipation of Q2. The power dissipation of Q2 based on the load is given by:

$$P_{Diss,Q2} = V_{CC} \times I_{OUT} - I_{OUT}^2 \times \left( R_{LOAD} + R_B \right) = 5V \times 0.1A - 0.1A^2 \times \left( 40\Omega + 4.7\Omega \right) = 0.053W$$

The maximum power dissipation of Q2 occurs when the load resistance is zero:

$$P_{Diss,Q2,max} = V_{CC} \times I_{OUT} - I_{OUT}^2 \times R_B = 5V \times 0.1A - 0.1A^2 \times 4.7 = 0.453W$$

Ensure Q2 is rated for this power dissipation.

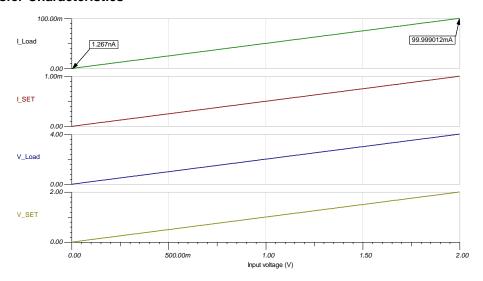

# **DC Transfer Characteristics**

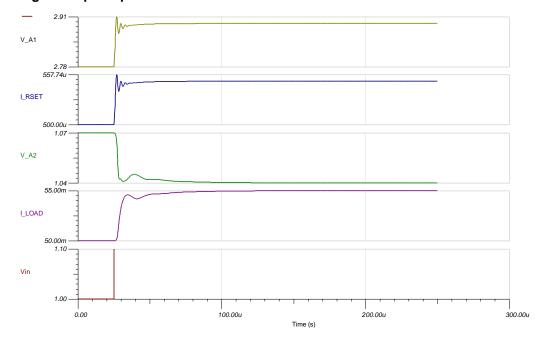

# **Small-Signal Step Response**

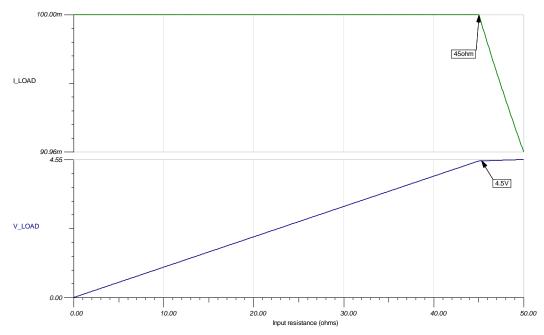

# **Compliance Voltage**

# **High Voltage Supply Modification**

This circuit design example uses a low voltage supply for  $V_{CC}$ . Some applications, such as 4–20mA current loops, require a high voltage supply to drive large resistive loads. To modify this current source for higher voltage supply, choose a high voltage, rail-to-rail input/output amplifier such as OPA192.

#### **Devices**

| Device     | Key Features                                                                                                 | Link                               | Other Possible Devices   |  |  |  |

|------------|--------------------------------------------------------------------------------------------------------------|------------------------------------|--------------------------|--|--|--|

| DACs       |                                                                                                              |                                    |                          |  |  |  |

| DAC80501   | 16-bit resolution, 1LSB INL, Single-Channel, Voltage Output DAC with 5ppm Internal Reference                 | http://www.ti.com/product/DAC80501 | http://www.ti.com/pdacs  |  |  |  |

| DAC80508   | 16-bit resolution, 1LSB INL, Octal-Channel, Voltage Output DAC with 5ppm Internal Reference                  | http://www.ti.com/product/DAC80508 | http://www.ti.com/pdacs  |  |  |  |

| DAC8775    | 16-bit resolution, Quad-Channel, ±10V, ±24mA Voltage and Current Output DAC, with Integrated DC/DC Converter | http://www.ti.com/product/DAC8775  | http://www.ti.com/pdacs  |  |  |  |

| Amplifiers |                                                                                                              |                                    |                          |  |  |  |

| OPA388     | Precision, Zero-Drift, Zero-Crossover, Rail-to-Rail Input/Output, 2.5-V to 5.5-V Supply                      | http://www.ti.com/product/OPA388   | http://www.ti.com/opamps |  |  |  |

| OPA192     | Precision, High-Voltage, Rail-to-Rail Input/Output, 4.5-V to 36-V Supply                                     | http://www.ti.com/product/OPA192   | http://www.ti.com/opamps |  |  |  |

| TLV170     | Cost Sensitive, Rail-to-Rail Output, 2.7-V to 36-V Supply                                                    | http://www.ti.com/product/TLV170   | http://www.ti.com/opamps |  |  |  |

# **Design References**

See Analog Engineer's Circuit Cookbooks for TI's comprehensive circuit library.

# Links to Key Files

TI Designs TIPD102, High-Side V-I Converter, 0-2V to 0-100mA, 1% Full Scale Error Reference Design

TI Designs TIPD215, Less Than 1-W, Quad-Channel, Analog Output Module With Adaptive Power Management Reference Design

TI Designs TIDA-01525, 8-channel, 16-bit, 200mA current output DAC reference design

Source Files for Programmable, Two-Stage, High-Side Current Source - http://ti.com/lit/zip/slac783.

## For direct support from TI Engineers use the E2E community:

e2e.ti.com

#### Other Links:

Precision DAC Learning Center

www.ti.com/pdac

# IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2021, Texas Instruments Incorporated