# **Comparing Bus Solutions**

Falk Alicke, Matthias Feulner, Frank Dehmelt, Ankur Verma, and G. Becke

Texas Instruments Incorported

#### **ABSTRACT**

The strong interest in this application report prompted this third edition. In addition to the changes and updates made throughout these sections, this edition also discusses Local Interconnect Network (LIN), USB-On-the-Go, DisplayPort, digital isolators, and more. This application report serves as a reference tool for finding the most appropriate data bus solution for today's advanced system architectures. It gives an overview of the different bus solutions available from Texas Instruments.

Designers can use many different solutions to solve the same problem. The task is to identify the optimum solution for their application. This application report makes it easier for designers to do this. It has sections on data transmission fundamentals, data line drivers and receivers, data links, and data signaling conditioners. Subsections discuss the electrical properties, applicability, and features of each product family.

#### **Contents**

| 1 | Overv  | iew                                                   | 4  |

|---|--------|-------------------------------------------------------|----|

|   | 1.1    | Single-Ended or Differential Transmission             | 4  |

|   | 1.2    | Modes of Operation                                    | 5  |

|   | 1.3    | Parallel or Serial Transmission                       | 6  |

|   | 1.4    | Data Transmission Speed                               | 7  |

|   | 1.5    | Standardized Interfaces                               | 7  |

| 2 | Data-  | Line Drivers and Receivers                            | 8  |

|   | 2.1    | Backplane Transceiver Logic (BTL)                     | 9  |

|   | 2.2    | Current-Mode Logic (CML)                              | 10 |

|   | 2.3    | Controller Area Network (CAN)                         | 11 |

|   | 2.4    | ControlNet                                            | 13 |

|   | 2.5    | Emitter-Coupled Logic (ECL) and Positive ECL (PECL)   | 14 |

|   | 2.6    | General-Purpose Interface Logic                       | 15 |

|   | 2.7    | Gunning Transceiver Logic (GTL)                       | 18 |

|   | 2.8    | Gunning Transceiver Logic Plus (GTLP)                 | 20 |

|   | 2.9    | IEEE1284-Compatible Devices                           | 22 |

|   | 2.10   | Local Interconnect Network (LIN)                      | 23 |

|   | 2.11   | Low-Voltage Differential-Multipoint (LVDM)            | 24 |

|   | 2.12   | Stub Series Terminated Logic (SSTL)                   | 26 |

|   | 2.13   | TIA-232 (RS-232)                                      | 28 |

|   | 2.14   | TIA/EIA-422 (RS-422)                                  | 29 |

|   | 2.15   | TIA-485 (RS-485)                                      | 30 |

|   | 2.16   | TIA-644 (LVDS)                                        | 30 |

|   | 2.17   | TIA-899 (M-LVDS)                                      | 32 |

|   | 2.18   | VMEbus                                                | 33 |

| 3 | Data I | Links                                                 | 34 |

|   | 3.1    | Digital Video                                         | 34 |

|   | 3.2    | General-Purpose Gigabit Transceivers                  | 46 |

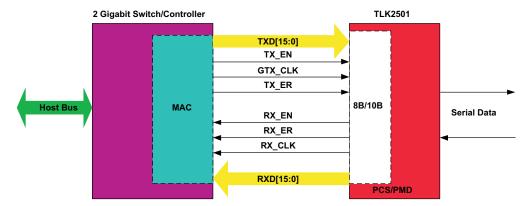

|   | 3.3    | Gigabit Ethernet and Fibre Channel Transceivers       | 48 |

|   | 3.4    | IEEE 1394 Cable and Backplane Applications (FireWire) |    |

|   | 3.5    | PCI/CompactPCI                                        | 54 |

|   | 3.6    | SONET/SDH Transceivers                                | 57 |

|          | 3.7 Universal Serial Bus                                                   |    |

|----------|----------------------------------------------------------------------------|----|

|          | 3.9 FPD-Link III                                                           |    |

| 4        | Data Signal Conditioners and Translators                                   |    |

|          | 4.1 Clock Distribution Circuits (CDC)                                      | 63 |

|          | 4.2 Digital Isolators                                                      | 68 |

| 5        | Summary                                                                    | 71 |

| 6        | References                                                                 | 71 |

| 7        | Glossary                                                                   | 72 |

|          | List of Figures                                                            |    |

| 1        | Single-Ended Transmission Circuit Model                                    |    |

| 2        | Differential Transmission Circuit Model                                    | 5  |

| 3        | Simplex Bus                                                                | 5  |

| 4        | Multidrop Bus                                                              | 6  |

| 5        | Half-Duplex Bus                                                            | 6  |

| 6        | Multipoint Bus                                                             | 6  |

| 7        | Principle of Parallel and Serial Transmission                              | 7  |

| 8        | Principle Setup of an Open-Collector Bus System Using BTL Devices          | 9  |

| 9        | ControlNet Applications                                                    | 13 |

| 10       | Point-to-Point Connection                                                  | 15 |

| 11       | Typical Backplane Application Using Several Plug-In Cards                  | 17 |

| 12       | Principle Setup of an Open-Collector Bus System Using GTL Devices          |    |

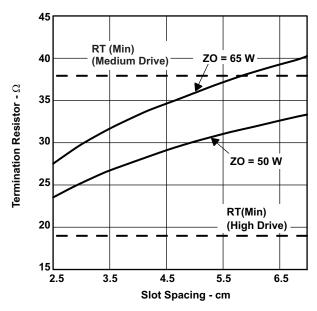

| 13       | R <sub>T</sub> Versus Slot Spacing With GTLP Medium and High Drive Devices |    |

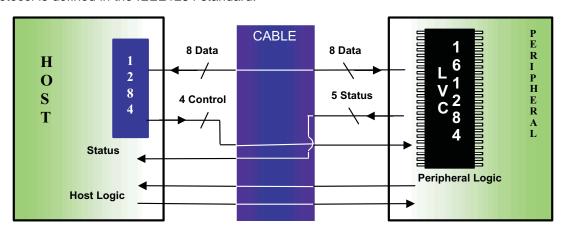

| 14       | Typical Application Showing a 1284 Interface                               |    |

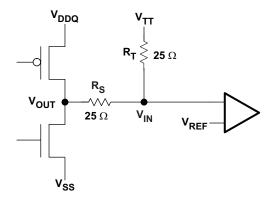

| 15       | Typical Output Buffer Environment, Class II of SSTL Standard               |    |

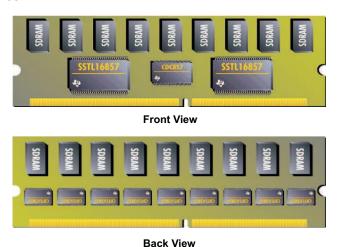

| 16       | DDR SDRAM Memory Interfacing Solution Using the SN74SSTL16857              |    |

| 17       | Null Modem Application Using RS232                                         |    |

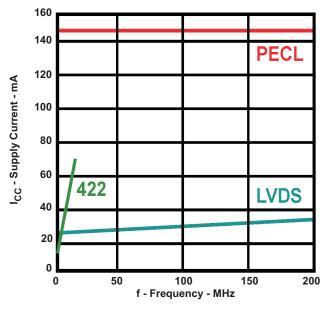

| 18       | Supply Current Versus Switching Frequency                                  |    |

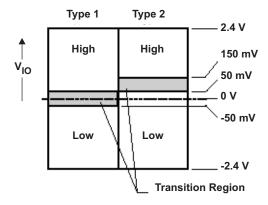

| 19       | Type 1 / Type 2 Switching Levels                                           |    |

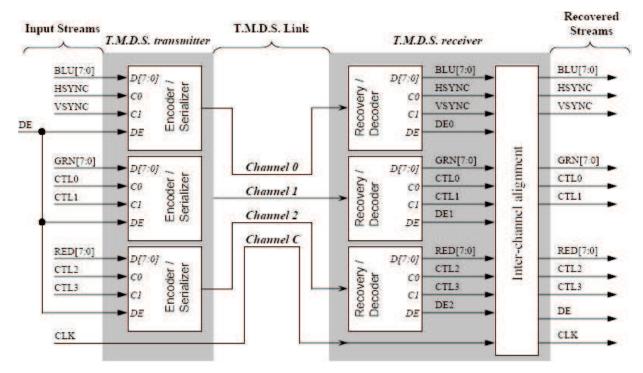

| 20       | TMDS Link Channel Map                                                      |    |

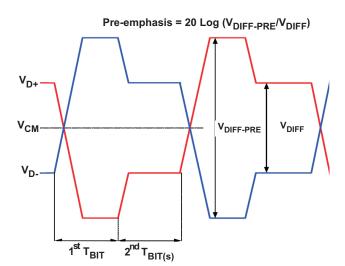

| 21       | DisplayPort Output Wave Shaping                                            |    |

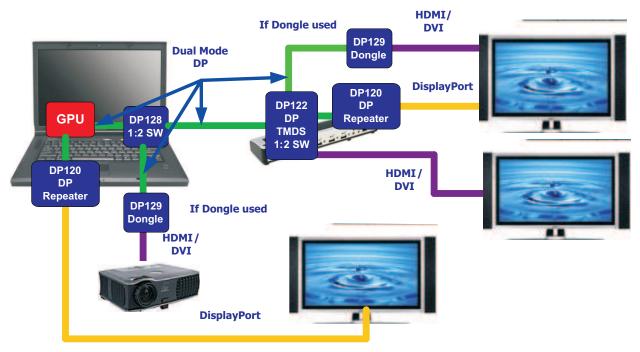

| 22       | Typical DisplayPort Application                                            |    |

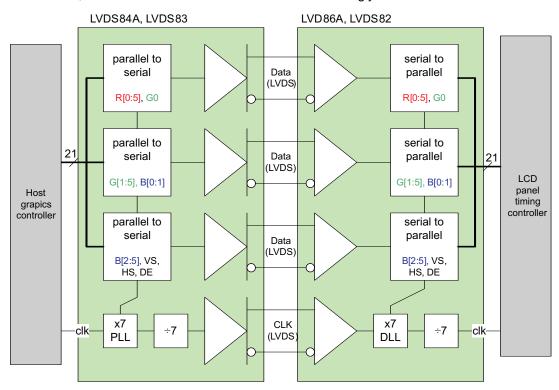

| 23       | Typical FlatLink™ Application                                              |    |

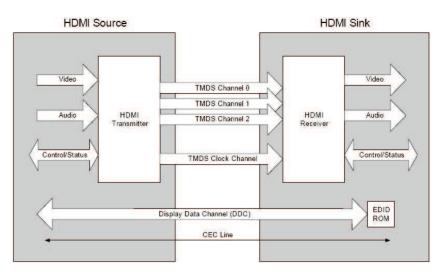

| 24       | HDMI Block Diagram                                                         |    |

| 25       | TMDS Electrical Schematic                                                  |    |

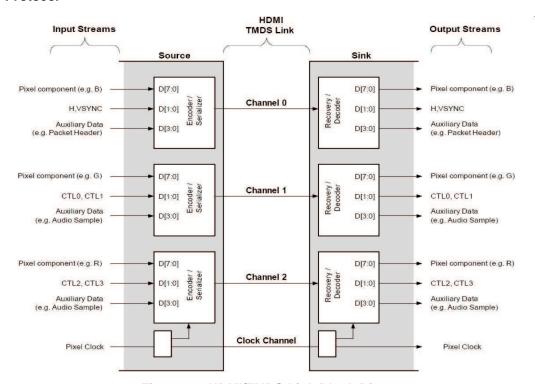

| 25<br>26 | HDMI/TMDS Link Block Diagram                                               |    |

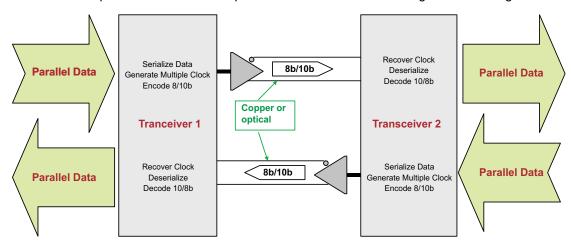

| 20<br>27 | SerDes Parallel Interface                                                  |    |

| 28       | SerDes Interface Using Two Transceivers.                                   |    |

|          | ·                                                                          |    |

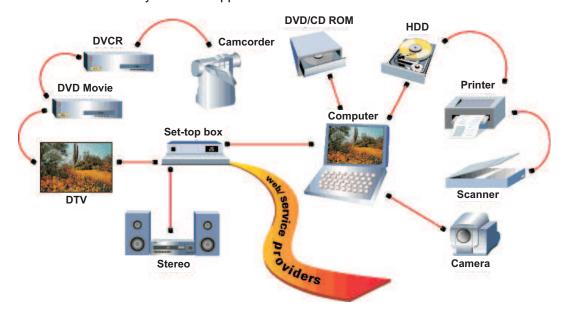

| 29<br>30 | Possible Interconnections Using 1394 as Interface                          |    |

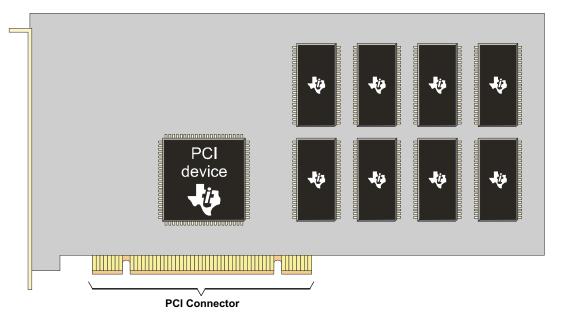

| 31       | PCI Card for Personal Computer                                             |    |

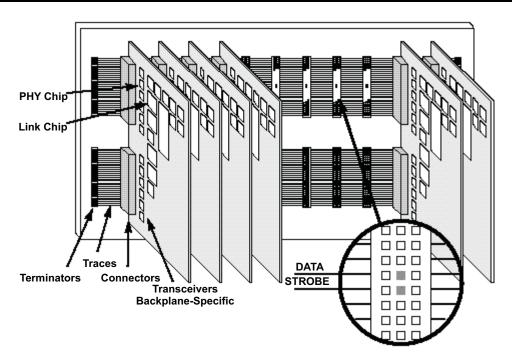

| 32       | CompactPCI Backplane                                                       |    |

|          |                                                                            |    |

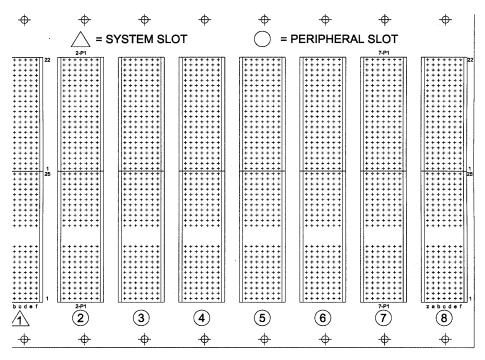

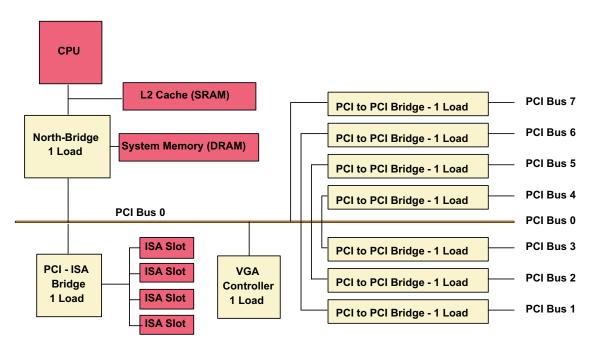

| 33       | PCI Bus System With 8 PCI Buses.                                           |    |

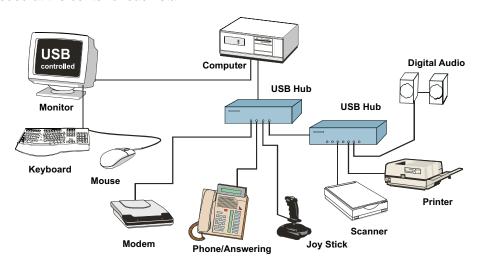

| 34       | USB – Tiered Star Topology.                                                |    |

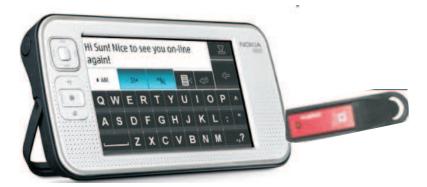

| 35<br>36 | Example of USB OTG Desktop-to-PDA Application                              |    |

| 36       | Example USB OTG PDA-to-Memory Application                                  |    |

| 37       | Example USB OTG PDA-to-PDA Application                                     |    |

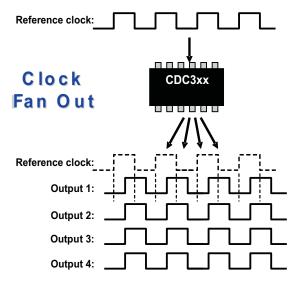

| 38       | Clock Buffer/Driver Diagram                                                |    |

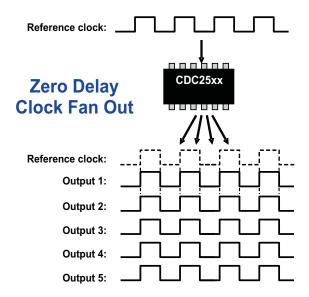

| 39       | Zero Delay Buffer Diagram                                                  | 64 |

| www. | .tı | LCOr | n |

|------|-----|------|---|

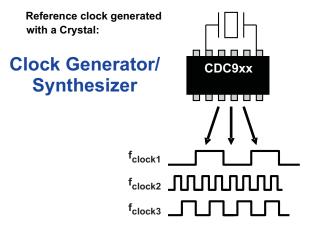

| 40 | Clock Generator Diagram                                                       |    |

|----|-------------------------------------------------------------------------------|----|

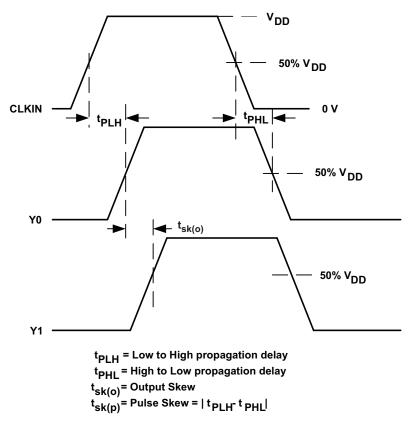

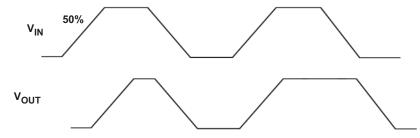

| 41 | Input and Outputs Waveforms                                                   |    |

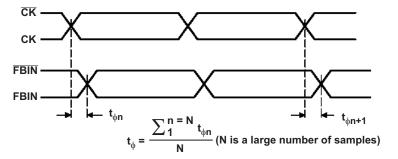

| 42 | Static phase offset                                                           | 65 |

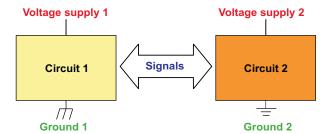

| 43 | Digital Isolators Let Signals Pass Through Between Circuit 1 and Circuit 2    |    |

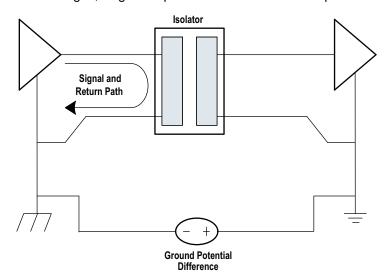

| 44 | Isolators Break Ground Loops                                                  |    |

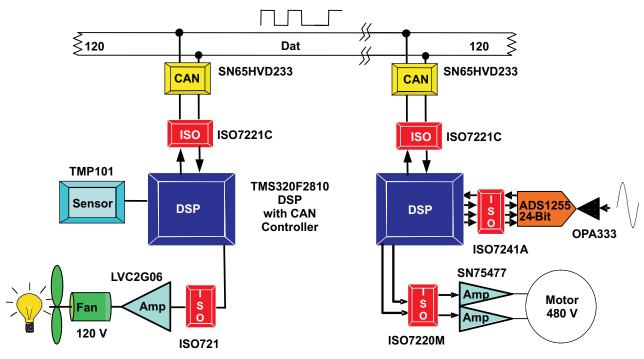

| 45 | A Typical Industrial FieldBus Application Using Digital Isolators             |    |

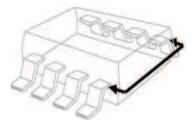

| 46 | Measuring the Creepage Distance for a Typical Digital Isolator IC             |    |

| 47 | Figure 48. Measuring the Clearance Distance for a Typical Digital Isolator IC |    |

| 48 | Pulse-Width Distortion                                                        | 70 |

|    | List of Tables                                                                |    |

| 1  | Electrical Data Interfaces                                                    |    |

| 2  | Top Device List – Backplane Transceiver Logic                                 |    |

| 3  | Top CAN Device List                                                           | 12 |

| 4  | Selected Characteristics for General-Purpose Logic Families                   | 16 |

| 5  | Top Feature List of Advanced System Logic by Logic Family                     | 17 |

| 6  | Top Device List GTL                                                           | 19 |

| 7  | Top Device List GTLP                                                          | 21 |

| 8  | Top Device List – IEEE 1284–Compatible Devices                                | 23 |

| 9  | LIN Device List                                                               | 24 |

| 10 | TOP LVDM Device List                                                          | 25 |

| 11 | Top Device List for Stub Series Termination Logic                             | 27 |

| 12 | Top TIA/EIA-232 Device List                                                   | 29 |

| 13 | Top RS-422 Device                                                             | 29 |

| 14 | Top RS-485 Device List                                                        | 30 |

| 15 | TOP LVDS Device List                                                          | 32 |

| 16 | Top M-LVDS Device List                                                        | 33 |

| 17 | Maximum Data Transfer Speeds                                                  | 33 |

| 18 | Top Device List VME                                                           | 34 |

| 19 | Data Links                                                                    | 34 |

| 20 | DVI Transmitter Device List                                                   | 36 |

| 21 | DVI Receiver Device List                                                      | 36 |

| 22 | EMI and Link Quality                                                          |    |

| 23 | DisplayPort Electrical Layer                                                  |    |

| 24 | DisplayPort Pre-Emphasis Levels (dB)                                          |    |

| 25 | DisplayPort Products                                                          |    |

| 26 | Multiplexing Ratios for LVDS SerDes and FlatLink™ Devices                     |    |

| 27 | LVDS SerDes Device List                                                       |    |

| 28 | HDMI Switch Device List                                                       |    |

| 29 | Next Generation HDMI Switch Device List                                       |    |

| 30 | Serial Gigabit Device List                                                    |    |

| 31 | Gigabit Ethernet/Fibre Channel Device List                                    |    |

| 32 | 1394 PMD Connection Matrix                                                    |    |

| 33 | Top IEEE 1394 Link Layer Device List (PC)                                     |    |

| 34 | Top IEEE 1394 Integrated Device List (PC)                                     |    |

| 35 | Top IEEE 1394 Integrated Device List (Non-PC)                                 |    |

| 36 | Top IEEE 1394 Link Layer Device List (Non-PC)                                 |    |

| 37 | Top IEEE 1394 Physical Layer Device List (Notifice)                           |    |

| 38 | Top Device List - PCI Products                                                |    |

| 50 |                                                                               | 91 |

Overview www.ti.com 39 40 41 42 43 Clock Drivers for Memory module 66 44 45 Adjustable-Delay Clock Drivers 67 46 Jitter Cleaners 67 47 48 49

### **Trademarks**

DOC, SCOPE, FlatLink, MicroStar Junior, OMAP are trademarks of Texas Instruments. Intel is a trademark of Intel Corporation.

All other trademarks are the property of their respective owners.

### 1 Overview

In today's information-hungry age, transmitting data several inches between computer memory and display screen is just as critical as sending it halfway around the globe. To meet these increasingly demanding data transmission needs, Texas Instruments has combined its expertise in high-speed digital and analog technologies to constantly extend the performance and capability of practically every data transmission standard.

This application report provides the reader with an overview of wired data-bus systems and provides insight into which standard or bus configuration best suits a designer's needs. Before discussing the prominent data transmission standards, their technical features, and the products that TI offers for each of these standard applications, the fundamental differences of the basic bus structures must be explained.

For the purposes of this report, products are divided into data line drivers and receivers, data links, and data signal conditioners or translators. Line drivers and receivers generate and receive the electrical signals over cables or board traces. Data link products arrange data for transmission and disassemble it for reception. Signal conditioners or translators modify data signals for particular application needs.

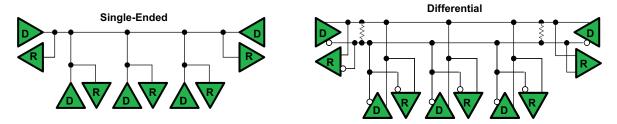

# 1.1 Single-Ended or Differential Transmission

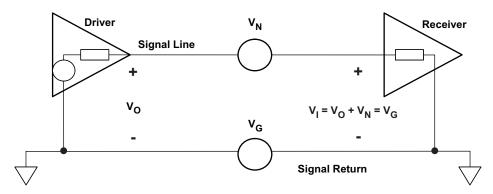

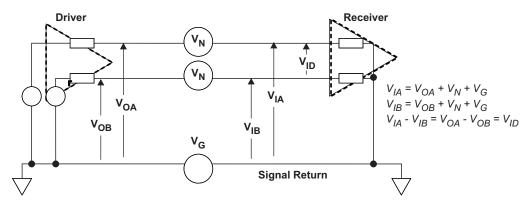

The two basic forms of data transmission circuits are single-ended and differential. In the single-ended or unbalanced circuit of Figure 1, the voltage difference between the signal line and common local ground determines the bus state. In the Figure 2 differential or balanced circuit, the voltage difference between two complementary signal lines determines the bus state. Each has advantages and disadvantages.

Figure 1 presents the electrical schematic diagram of a single-ended transmission circuit and the noise sources  $V_N$  and  $V_G$  that directly add to the signal voltage,  $V_O$ . This makes the single-ended circuit susceptible to external noise influences. Because no complementary signal (as in differential) cancels the fields created by the single-ended signal, it radiates much more noise than differential circuits. Electromagnetic noise susceptibility and emissions relegate single-ended interfaces to low signaling rates and short transmission lines. However, the single-ended interface line driver, receiver, and interconnection costs are often less than those of differential circuits.

www.ti.com Overview

Figure 1. Single-Ended Transmission Circuit Model

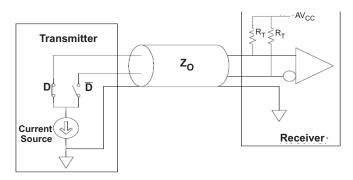

Figure 2 shows the electrical schematic diagram of a differential transmission circuit in which noise sources  $V_N$  and  $V_G$  add to each signal line and are common to both signals. The differential receiver measures the difference between the two lines and rejects the common voltage of the signals. If used with closely coupled lines, the complementary signals cancel each other's electromagnetic fields, resulting in high immunity and low noise emissions. This immunity to external noise influence and the low radiated emissions make differential signaling a good choice when relatively high signaling rates and long distance are required in electrically noisy, or noise-sensitive applications. Differential signaling comes with the additional cost of the line driver, receiver, and interconnection over the cost of single-ended transmission.

Figure 2. Differential Transmission Circuit Model

# 1.2 Modes of Operation

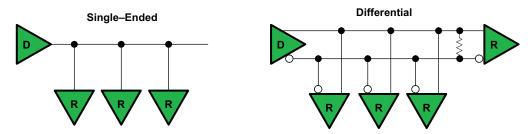

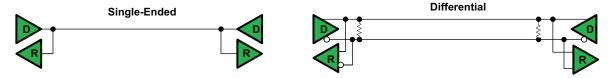

Modes of operation refer to the direction of data flow and affect the electrical requirements for line drivers and receivers. Figure 3 displays the simplex mode for the unidirectional (nonreversible) flow of data from a single line driver to a single line receiver.

Figure 3. Simplex Bus

The full-duplex mode consists of two simplex circuits transmitting simultaneously in opposite directions between ports.

The distributed simplex mode or differential multidrop mode is a single line driver transmitting unidirectional to more than one receiver. Figure 4 presents some examples.

Overview www.ti.com

Figure 4. Multidrop Bus

The half-duplex mode is a nonsimultaneous, two-way data flow between two line driver and receiver pairs or transceivers. Figure 5 illustrates this.

Figure 5. Half-Duplex Bus

The logical extension of the half-duplex mode is the multipoint bus. A multipoint bus is the nonsimultaneous, two-way data flow among three or more transceivers connected to the same physical transmission line, as illustrated in Figure 6. Multipoint line drivers and receivers have stringent electrical requirements and support all of the other modes of operation.

Figure 6. Multipoint Bus

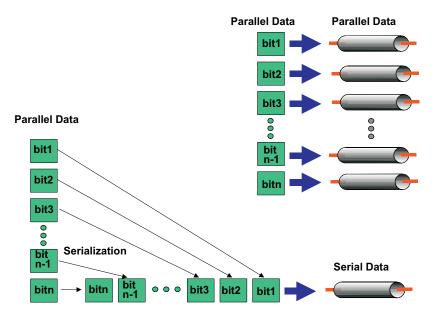

# 1.3 Parallel or Serial Transmission

Figure 7 illustrates the difference between parallel and serial data transmission. Parallel data buses transmit multiple bits at the same time over a signal line for each data bit. Serial data buses transmit one bit after another through a single line by serializing, then de-serializing back to parallel data. Although serial buses must transmit at a higher rate to achieve the same signaling rates as a parallel bus, both methods have advantages and disadvantages.

www.ti.com Overview

Figure 7. Principle of Parallel and Serial Transmission

Latency is typically referred to as the time from a data request to its receipt. Generally, latency is lower in parallel buses because the time to serialize and deserialize the data is not required. Operational software protocols are often implemented for a parallel bus interface by dedicating specific bits for the control of data transfer, thereby enabling higher signaling rates.

The interconnection cost advantage of the serial bus is from the single data path that results in less board area, fewer connector pins, and less transmission cable cost.

The signaling rate advantage goes to the parallel bus because the width of a bus has no limit. However, distance quickly become a critical factor as parallel fields interact with each other. High-quality, shielded, twisted-pair, parallel cable helps to slightly extend the parallel bus length, but not to the extreme lengths that can be attained on a single twisted-pair cable.

#### Data Transmission Speed 1.4

Many terms are used to describe the signaling rate or speed of data transfer, and the designer needs to understand the context when using signaling rate units. The minimum unit-interval or t<sub>III</sub> describes the minimum time duration of a single pulse of a bit sequence. Many standards define signal quality either in terms of signal rise and fall times or eye-pattern jitter as a percentage of the t<sub>III</sub>. The inverse of the t<sub>III</sub> is the signaling rate in units of bits per second such as kilobits per second (kbps) or megabits per second (Mbps). These parameters often define the basic bandwidth requirements of a data transmission circuit regardless of its form, mode, or other characteristic.

Some applications use the input clock frequency in Hertz to describe a data transfer rate. This is commonly used when comparing serializer and deserializer products with a known parallel bus width. The relation of Hertz to bits per second is that a single bit is typically considered to be a 180 degree unit – a 360 degree cycle is two bits. Therefore, 1 Hz is equal to 2 bits per second.

#### 1.5 Standardized Interfaces

The primary reason for standardizing a data interface is the economy of scale. The high number of manufacturers of standardized interchangeable products such as RS-485 transceivers, typically lowers the end cost to a user. To this purpose, governments and industry trade groups have published many data transmission standards. The Institute of Electrical and Electronic Engineers (IEEE), the Telecommunications Industry Association (TIA), and the International Standards Organization (ISO) are just a few examples.

Some standards are comprehensive and specify all of the necessary characteristics for successful interoperation of a data interface. Others focus on a subset of the requirements, such as the electrical layer, and are referenced by other standards. In some cases, first-to-market interface products such as emitter-coupled logic (ECL) have become a de facto standard electrical layer.

#### 2 Data-Line Drivers and Receivers

Line drivers and receivers are responsible for passing bits onto and receiving them from the connecting medium. They have no understanding of the meaning of the bits, but deal with the electrical characteristics of the signals and signaling methods. The signaling rate, mode of operation, and distance are the primary selection criteria.

Table 1 summarizes the Texas Instruments line drivers and receivers, which are discussed in the remainder of this section. The speed and distances listed are estimated maximums and simultaneous operation at both maximums may not be possible. As cable length increases, you must lower the signaling rate to keep the same bit-error rates. This, and the increased exposure to noise with distance, makes the analog characteristics of line drivers and receivers important and helps explain the number of different standards. It also complicates the selection process.

**Table 1. Electrical Data Interfaces**

| INTERFACE RATE                                                | SIGNALING  | DISTANCE | FORM                            | MODE(S)             | STANDARD                    | PRODUCT FAMILY(1)         |

|---------------------------------------------------------------|------------|----------|---------------------------------|---------------------|-----------------------------|---------------------------|

| Backplane Transceiver Logic (BTL)                             | < 50 Mbps  | < 1 m    | Single-ended                    | Multiplex           | IEEE896.1                   | Backplane Logic           |

| Controller Area Network (CAN)                                 | < 1 Mbps   | < 400 m  | Differential                    | Multiplex           | ISO 11898                   | CAN                       |

| Current-Mode Logic (CML)                                      | < 5 Gbps   | < 1 m    | Differential                    | Half Duplex         |                             | LVDS/M-<br>LVDS/ECL/CML   |

| Emitter-Coupled Logic (ECL)                                   | < 5 Gbps   | < 10 m   | Single-ended or<br>Differential | Distributed simplex |                             | LVDS/M-<br>LVDS/ECL/CML   |

| General-Purpose Interface Logic(GPL)                          |            |          |                                 |                     |                             |                           |

| Gunning Transceiver Logic (GTL)                               | <120 Mbps  | < 1 m    | Single-ended                    |                     | JESD8-3                     |                           |

| Gunning Transceiver Logic Plus (GTLP)                         | < 200 Mbps | < 1 m    | Single-ended                    |                     | JESD8-3                     |                           |

| IEEE 1284 Compatible Devices                                  |            |          |                                 |                     |                             |                           |

| Local Interconnection<br>Network (LIN)                        |            |          |                                 |                     |                             |                           |

| Low-Voltage Differential<br>Multipoint (LVDM)                 | < 1 Gbps   | < 10 m   | Differential                    | Half duplex         | None                        | M-LVDS PHYs<br>(<500Mbps) |

| Low-Voltage Differential<br>Signaling (LVDS)                  | < 2 Gbps   | < 10 m   | Differential                    | Distributed simplex | TIA/EIA-644                 | M-LVDS PHYs<br>(<800Mbps) |

| Multipoint-Low-Voltage<br>Differential Signaling (M-<br>LVDS) | <500 Mbps  | < 30 m   | Differential                    | Multiplex           | TIA/EIA-899                 | M-LVDS PHYs<br>(<500Mbps) |

| RS-232                                                        | < 250 kbps | < 20 m   | Single-ended                    | Simplex             | TIA/EIA-232                 | RS-232                    |

| RS-422 simplex                                                | < 40 Mbps  | < 1200 m | Differential                    | Distributed simplex | TIA/EIA-422                 | RS-422                    |

| RS-485                                                        | < 40 Mbps  | < 1200 m | Differential                    | Multiplex           | TIA/EIA-485                 | RS-485                    |

| Stub SeriesTerminated Logic (SSTL)                            | < 400 Mbps | < 1 m    | Single-ended                    |                     | EIA/JESD8-8,<br>EIA/JESD8-9 |                           |

| VMEbus                                                        | < 80 Mbps  | < 1 m    | Single-ended                    | Multiplex           | ANSI/VITA1-1991             |                           |

<sup>(1)</sup> For additional information on each Product Family, go to www.ti.com and enter the relevant product family name in the Search by Keyword box.

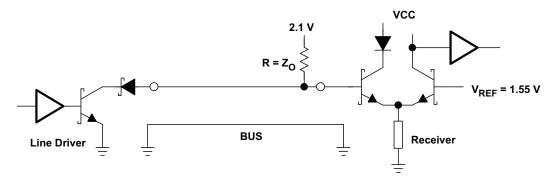

# 2.1 Backplane Transceiver Logic (BTL)

In the past, the standard solutions for driving bus lines on backplane systems were TTL or CMOS logic circuits. However, some issues result from the high voltage swing of 3.3 V up to 5 V: Correct termination for all load conditions is not possible and large drive capabilities are necessary to enable incident wave switching.

A bus system with reduced voltage swing solves a lot of problems. The BTL bus realizes a bus in open-collector mode, as shown Figure 8. In this case, the falling edge is actively generated from the driver. Only a low impedance driver can switch the bus with the incident wave.

Figure 8. Principle Setup of an Open-Collector Bus System Using BTL Devices

#### 2.1.1 Electrical

The physical layer of the Futurebus is called backplane transceiver logic (BTL) and works only with a voltage swing of 1.1 V, using an open-collector bus system. The saturation voltage of the pulldown transistor and the forward voltage of the serially connected diode generates the output low level voltage of 1 V. The high level of 2.1 V comes from the termination resistor connected to the termination voltage of 2.1 V. The value of the termination resistor is equal to the impedance of the bus-line and therefore the bus line is terminated correctly. For safe detection of the logic levels, the inputs are designed with differential amplifiers and a threshold at 1.55 V, exactly in the middle of the voltage swing.

To reduce ICC current spikes, the fall time is defined to be 2 ns or slower. The rise time is not generated by active electronics, but by the pullup resistor.

### 2.1.2 Applicability

Futurebus plus logical layer specification, according to the IEEE896.2 specification, describes the node management, live insertion, and profiles. However, the physical layer may also be used stand-alone without the logical layer.

The target area for BTL devices is the telecommunications sector, where live insertion capability is especially mandatory.

### 2.1.3 Features

- Reduced voltage swing:  $V_L = 1 \text{ V}$ ;  $V_H = 2.1 \text{ V}$  generates low switching noise 10  $\Omega$  or 20  $\Omega$  || 20- $\Omega$  line impedance

- Correct line termination by a pullup resistor at the line end avoids line reflections

- Decoupling diode reduces output capacitance to < 5 pF, increases line impedance</li>

- Maximum output edge rate 2 ns, trapezoidal waveform reduces system noise

- Supports live insertion/withdrawal

## Table 2. Top Device List - Backplane Transceiver Logic

| DEVICE      | SPECIFICATION | DESCRIPTION                                                                | PACKAGE      | STATUS    |

|-------------|---------------|----------------------------------------------------------------------------|--------------|-----------|

| SN74FB2033A | TTL /BTL      | 8-Bit TTL /BTL registered transceivers                                     | 52-pin PQFP  | Available |

| SN74FB1651  | TTL /BTL      | 17-Bit TTL /BTL universal storage transceivers with buffered clock times   | 100-pin SQFP | Available |

| SN74FB2031  | TTL /BTL      | 9-Bit TTL /BTL address/data transceivers                                   | 52-pin PQFP  | Available |

| SN74FB1653  | LVTTL /BTL    | 17-Bit LVTTL /BTL universal storage transceivers with buffered clock lines | 100-pin SQFP | Available |

| SN74FB2041A | TTL /BTL      | 7-Bit TTL /BTL transceivers                                                | 52-pin PQFP  | Available |

| SN74FB2040  | TTL /BTL      | 8-Bit TTL /BTL transceivers                                                | 52-pin PQFP  | Available |

# 2.2 Current-Mode Logic (CML)

#### 2.2.1 Electrical

Current-mode logic (CML) is used in point-to-point, high-speed, differential-data transfer applications. CML is typically used across a  $50-\Omega$  transmission medium, using a  $50-\Omega$  to VCC termination. Typical output voltage swings for CML are 600-mV peak or 1200-mV peak-to-peak, allowing for greater transmission distances, whereas the output common mode is typically VCC -300 mV.

### 2.2.2 Applicability

CML is a high-speed, differential-signal logic implementation. CML is typically used to implement high-speed I/O structures found in gigabit SerDes, high-speed clocking devices, and other high-speed digital communication links. CML technology is often used for implementing multi-gigabit links running from 3 Gbps to 10 Gbps (or equivalent clock frequencies) for applications such as gigabit Ethernet, 10G Ethernet, and Fibre Channel.

### 2.2.3 Features

The CML interface drivers provide several design features, including high-speed capabilities, adjustable logic output swing, level adjustment, and adjustable slew rate. CML can be used in both AC-coupled and DC-coupled environments (assuming proper pullup and termination schemes are implemented). In the case of extremely high data rates applications (6 Gbps to 10 Gbps), superior propagation delay characteristics and static current consumption enable lower power solutions.

See Interface Selection Guide for a list of top CML devices: www.ti.com/interface.

#### 2.3 Controller Area Network (CAN)

The Controller Area Network (CAN) is an International Standardization Organization (ISO)-defined, serial communications bus originally developed for the automotive industry to replace the complex wiring harness with a two-wire bus. The specification calls for signaling rates up to 1 Mbps, high immunity to electrical interference, and an ability to self-diagnose and repair data errors.

CAN is ideally suited in applications requiring a large number of small messages in a short time, with high reliability in rugged operating environments. Because CAN is message based and not address based, it is especially suited when data is needed by more than one location and system-wide data consistency is considered mandatory.

#### 2.3.1 **Electrical**

The CAN standard, ISO 11898:1993 defines half-duplex, differential transmission on cable lengths up to 40 m, a maximum stub length of 0.3 m, and a maximum of 30 nodes at signaling rates up to 1 Mbps. However, with careful design, much longer cables, longer stub lengths, and many more nodes can be added to a bus – always with a trade-off in signaling rate. For more information on the CAN physical layer, see the application report Controller Area Network Physical Layer Requirements (SLLA270).

A single, shielded or unshielded, twisted-pair cable with a 120-Ω characteristic impedance (Zo) is specified as the interconnect. This interconnecting cable is terminated at both ends with a resistor equal to the Zo of the line. Nodes are then connected to the bus with unterminated drop cables or stubs.

Data transmission circuits employing CAN are used in applications requiring a rugged interconnection with a wide common-mode voltage range. Therefore, shielded cable is recommended in these electronically harsh environments, and when coupled with the Standard's -2-V to 7-V common-mode range of tolerable ground noise, helps to ensure data integrity.

The CAN communications protocol, ISO 11898:1993, describes how information is passed between devices on a network, and conforms to the Open Systems Interconnection (OSI) model that is defined in terms of layers. ISO 11898 defines the functions of the lower layers of the OSI model that are performed within a CAN controller. These CAN controller functions are designed for interaction with a higher layer protocol such as CANopen to complete node communication relationships for bus operation. An abundance of plug-n-play CAN programming routines are available on the Internet from different vendors.

#### 2.3.2 **Applicability**

The robust features of CAN make it ideally suited for the many rugged applications to which the CAN protocol is being adapted. Among the applications finding solutions with CAN are automobiles, trucks, trains, buses, airplanes and aerospace, agriculture, construction, mining, and marine vehicles. CAN-based control systems are being used in factory and building automation and embedded control systems for machines, medical devices, domestic appliances, and many other applications.

#### 2.3.3 **Features**

- Established standard and standardized plug-n-play products

- Fault tolerant very high short-circuit protection

- Self-diagnosing error repair every bit checked 5 times for error

- Very robust interface for harsh electrical environments

- Wide common-mode operating range

# **Table 3. Top CAN Device List**

| DEVICE                                                              | FEATURES                                                                                                                                                     | POWER                                                   | PACKAGE                             |

|---------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|-------------------------------------|

| SN65HVD230, SN65HVD231, and<br>SN65HVD232 CAN Transceiver<br>Family | High-temperature range and short-circuit protection.<br>Low-power Standby and Sleep modes.<br>Wide Common mode. Low power.                                   | V <sub>CC</sub> : 3.3-V I/O:<br>(LV)TTL / CAN           | 8-pin SOIC                          |

| SN65HVD233, SN65HVD234, and<br>SN65HVD235 CAN Transceiver<br>Family | High-temperature range and short-circuit protection. Low-power Standby and Sleep modes. Wide Common mode. Low power. Auto-baud loopback diagnostic function. | V <sub>CC</sub> : 3.3-V I/O:<br>(LV)TTL / CAN           | 8-pin SOIC                          |

| SN65HVD251                                                          | High-temperature range and short-circuit protection. Low-power Standby. Wide Common mode. Low cost.                                                          | V <sub>CC</sub> : 5-V I/O:<br>5-V CMOS / CAN            | 8-pin SOIC                          |

| SN65HVD1040                                                         | Low-power, 5-µA bus monitor. Wide Common mode. High-ESD protection. Split pin bus stabilizing function. High-temperature range and short-circuit protection. | V <sub>CC</sub> : 5-V I/O: TTL / CAN                    | 8-pin SOIC                          |

| SN65HVD1050                                                         | High-temperature range and short-circuit protection. Low-power Standby. Wide Common mode. Low cost.                                                          | V <sub>CC</sub> : 5-V I/O: TTL / CAN                    | 8-pin SOIC                          |

| TMS320LF240x DSP Family                                             | Full CAN controller.<br>Low power.                                                                                                                           | V <sub>CC</sub> : 3.3 V I/O (LV)<br>TTL / CAN, SPI, SCI | 100-pin PZ,<br>144-pin PGE          |

| TMS320F28xx DSP Family                                              | Dual CAN controller versions.<br>Low power.                                                                                                                  | V <sub>CC</sub> : 3.3-V I/O (LV)<br>TTL / CAN, SPI, SCI | Multiple PGE, PZ, and LQFP packages |

| TMS470xxx                                                           | 16/32-bit RISC flash microcontroller Dual CAN controller versions. Low-power modes.                                                                          | V <sub>CC</sub> : 3.3-V ARM7, CAN, 2 SPI, 2 SCI, ADC    | Multiple PGE, PZ, and LQFP packages |

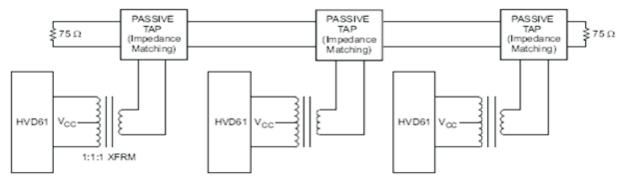

### 2.4 ControlNet

ControlNet is an open standard network that meets the demands of industrial applications requiring high speed (5 megabits per second) and high throughput with predictable and repeatable transfers of mission critical data.

#### 2.4.1 Electrical

ControlNet can be implemented on several different types of media, including copper coaxial cable, fiber-optic cable, and fiber ring, with variations for media redundancy and intrinsically safe applications. ControlNet supports a maximum of 99 nodes, with no minimum distance limitation between nodes. The most common media implementation uses transformer-coupled signals over coaxial cable. The 5-Mbps data is Manchester-encoded so that the bus levels change at 10 Mbps.

Texas Instruments supplies the only integrated ControlNet PHY (transceiver) available—the SN65HVD61.

### 2.4.2 Protocol

ControlNet is part of the Common Industrial Protocol (CIP) maintained jointly by ControlNet International and Open DeviceNet Vendors Association (ODVA). It offers high network efficiency with multicast of inputs and peer-to-peer data, using a Producer/Consumer communication model that allows the user to configure devices, control actions, and collect information over a single network.

# 2.4.3 Applicability

ControlNet meets the demands of real-time, high-speed applications at the automation and control layer for integration of complex control systems such as coordinated drive systems, weld control, motion control, vision systems, complex batch control systems, process control systems with large data requirements, and systems with multiple controllers and human-machine interfaces.

See the application report *ControlNet Applications with the SN65HVD61 PHY* (SLLA265) for further information.

Figure 9. ControlNet Applications

# 2.5 Emitter-Coupled Logic (ECL) and Positive ECL (PECL)

#### 2.5.1 Electrical

Emitter-coupled logic (ECL) is used in point-to-point, high-speed, differential-data transfer applications. A negative power scheme is used for ECL with VCC = 0 V and VEE = -5.2 V. ECL is typically used across a  $50-\Omega$  transmission medium using a  $50-\Omega$  to VEE termination. Typical output voltage swings for ECL are 800-mV peak or 1600-mV peak-to-peak allowing for greater transmission distances, whereas the output common mode is typically -1.3 V.

Positive/pseudo emitter-coupled logic (PECL) is used in point-to-point, high-speed, differential-data transfer applications. The opposite of ECL, PECL has a positive power supply scheme with VCC = 5 V and VEE = 0 V. PECL is typically used across a  $50-\Omega$  transmission medium using a  $50-\Omega$  to VCC-2-V termination. Typical output voltage swings for PECL are 800-mV peak or 1600-mV peak-to-peak allowing for greater transmission distances, whereas the output common mode is typically VCC -1.3 V.

Low voltage positive/pseudo emitter-coupled logic (LVPECL) is used in point-to-point, high-speed, differential-data transfer applications. LVPECL takes PECL and allows for lower power supply ranges. The typical power supply range for LVPECL is VCC = 3.3 V and VEE = 0 V. LVPECL is typically used across a 50- $\Omega$  transmission medium using a 50- $\Omega$  to VCC-2-V termination. Typical output voltage swings for LVPECL are 800-mV peak or 1600-mV peak-to-peak allowing for greater transmission distances, whereas the output common mode is typically VCC – 1.3 V.

# 2.5.2 Applicability

Emitter-coupled logic (ECL) and positive/pseudo emitter-coupled logic (PECL) have been traditionally considered high-speed logic families that are applicable for use in high-speed communications data and clock links. Also, many high-speed clock distribution devices use xECL as its logic type due to its noise performance as well as its universal familiarity among the engineering community at large.

### 2.5.3 Features

Emitter-coupled logic (ECL) uses negative power supply rail, which historically had the advantage of improved noise immunity. Because the implementation of positive-supply technologies such as TTL and CMOS, the older technologies no longer provide a benefit, as a system using them requires several power supplies including the –5.2 V or –4.5 V needed for ECL.

As a result, ECL migrated to PECL, which allowed designers to move away from this negative supply rail and simplify board layout. The principle behind PECL was simply to keep the same output swing of 800 mV, but shift it to a positive voltage by using a 5-V rail and ground. LVPECL is the same concept as PECL, but uses a 3.3-V supply rather that the 5-V one. This results in a power consumption reduction relative to PECL. One of the key benefits that made xECL popular was its constant current requirement mostly independent of the switching circuit. This results in less noise and relatively constant (predictable) power usage, which are especially important for high data rate applications.

See Interface Selection Guide for a list of top PECL devices: www.ti.com/interface

# 2.6 General-Purpose Interface Logic

For a long time TTL-buses have been the standard solution for backplane systems. Different logic families are available to fulfill the requirement for backplane buses. The choice for the appropriate logic strongly depends on physical characteristics of the bus. The main factor is the number of receiving and transmitting modules connected into that bus. The more cards on the backplane, the lower the impedance of the bus due to additional capacitive loading. This arises from the input/output capacitance of the transceivers, the capacitance layer of printed-circuit stub lines and the connectors, resulting in the need for a higher drive capability of the logic device.

Mature 5-V TTL and 5-V CMOS as well as 3.3-V CMOS technologies provide a drive capability of 24 mA and can only handle line impedance down to about 50  $\Omega$ . With the introduction of BiCMOS technologies, the drive has been enlarged to -32/64 mA and with so-called incident wave switching drivers (SN74ABT25xxx). It is even possible to drive bus lines with an impedance as low as 25  $\Omega$ . The enhanced transceiver logic (ETL) features improved noise margins, while maintaining compatible TTL switching levels and therefore enabling higher speed on the backplane.

**Backplane - Multipoint To Multipoint - Connection**

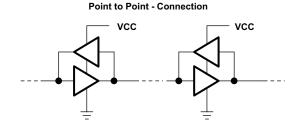

Figure 10. Point-to-Point Connection

Standard logic devices can be used for either point-to-point connections or to realize backplane buses, which consist of many drivers and receivers along the bus, as shown in Figure 10. Both solutions using standard logic devices are usually set up as parallel buses; up to 36 bits can be switched by one logic device. The operational frequency can be chosen within a range from a few MHz up to the clock frequency of about 50 MHz, such that the data throughput per device is in the range of 1 to 2 Gbps.

#### 2.6.1 Electrical

The electrical specification of LVTTL levels meets the TTL specification. The combination of 5-V TTL with LVTTL is possible without any additional effort. Five-volt CMOS levels are not compatible with LVTTL levels. Five-volt tolerance is mandatory for unidirectional, and the use of 5-V level shifters is required for bidirectional data transfer, when combining a 3.3-V system with a 5-V-supplied system part. Table 4 shows the key parameters for 5-V and 3.3-V advanced system logic families. Another important feature is the live insertion capability of a logic family, which enables the user to insert and remove modules during operation. The important parameters are IOFF, power up/down 3-state, and precharge functionality as shown in Table 17. For more information about this topic, see the application report *Live Insertion* (SDYA012).

**INTERFACING** LIVE INSERTION, REMOVAL **FAMILY** RECOMMENDED DRIVE (mA) **LEVELS** SUPPLY VOLTAGE TO (LV) TTL **HOT INSERTION** AHC/LV 5 V CMOS Use level shifter 5 V ±8 AC 5 V ±24 5 V CMOS Use level shifter I<sub>OFF</sub>, PU/D-3-state 5 V -32/ +64 ABT TTL Yes ABT25 5 V -80 (32)/+188 (64) **ABTE** 5 V -60 (12)/ +90 (12) **ETL** Yes I<sub>OFF</sub>, PU/D-3-state and precharge I<sub>OFF</sub>, (LVCZ: PU/D-3-state) LVC 3.3 V ±24 LVTTL Yes 3.3 V LVTTL **ALVC** ±24 Yes LVT 3.3 V -32/ +64 LVTTL Yes I<sub>OFF</sub>, PU/D-3-state **ALVT** 3.3 V -32/ +64 LVTTL Yes I<sub>OFF</sub>, PU/D-3-state AVC 2.5 V ±12 + DOC™ **2.5 CMOS** Yes I<sub>OFF</sub>, PU/D-3-state

Table 4. Selected Characteristics for General-Purpose Logic Families

A maximum bus length is not specified for backplanes; however, in practice, the bus length of parallel backplanes does not exceed about 50 cm.

**1.8 CMOS**

Yes

### 2.6.2 Applicability

AUC

1.8 V

The backplanes are not limited to any special domain. They are used in telecom, computer, and industry application, wherever several system parts are connected using a backplane or a memory bus. ABTE supports VME64.

### 2.6.3 Features

- 8-, 16-, and 32-bit devices enable parallel operation on the backplane/memory bus.

- Boundary scan devices (JTAG IEEE 1149.1) available in LVT and ABT enable easy testability during design and production.

- Bus-hold feature eliminates external pullup resistor.

+8

- Series damping resistors enable improved signal integrity in point-to-point buses.

- ABT, LVT, ALVT, and LVCZ incorporate power-up, 3-state outputs.

- ABTE supports precharge feature, enabling support hot swapping.

- LVC, ALVC are specified down to 1.8 V, further reducing power consumption.

I<sub>OFF</sub>, PU/D-3-state

# Table 5. Top Feature List of Advanced System Logic by Logic Family

| FUNCTION                             | AHC | AC  | ABT | ABTE | (A)LVC | LVT | ALVT | AVC  | AUC |

|--------------------------------------|-----|-----|-----|------|--------|-----|------|------|-----|

| Gates                                | n   | n   | n   | N/A  | n      | N/A | N/A  | N/A  | n   |

| Flip-flops                           | n   | n   | n   | N/A  | n      | n   | n    | N/A  | n   |

| Drivers                              | n   | n   | n   | n    | n      | n   | n    | n    | n   |

| Transceivers                         | n   | n   | n   | n    | n      | n   | n    | n    | n   |

| UBT <sup>TM(1)</sup>                 | N/A | N/A | n   | N/A  | n      | n   | n    | n    | n   |

| Bus hold <sup>(2)</sup>              | N/A | N/A | n   | n    | n      | n   | n    | n    | n   |

| 26-Ω series resistors <sup>(3)</sup> | n   | n   | n   | n    | n      | n   | n    | DOC™ | n   |

| SCOPE <sup>TM (4)</sup>              | N/A | N/A | n   | N/A  | N/A    | n   | N/A  | N/A  | N/A |

<sup>(1)</sup> The universal bus transceiver (UBTTM) combines D-type latches and D-type flip-flops for operation in transparent, latched or clocked mode.

<sup>(4)</sup> SCOPE™ products are compatible with the IEEE Standard 1149.1–1990 (JTAG) test access port and boundary scan architecture.

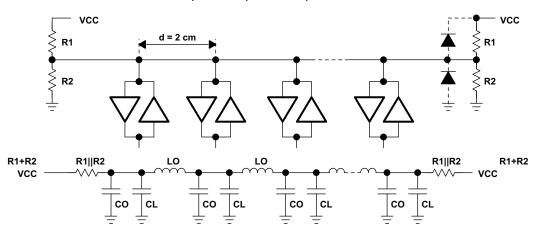

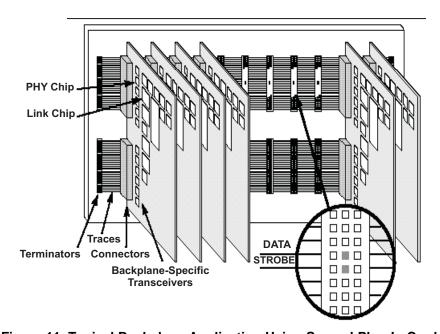

Figure 11. Typical Backplane Application Using Several Plug-In Cards

<sup>&</sup>lt;sup>(2)</sup> Bus hold on data inputs eliminates the need for external pullup resistors.

<sup>(3) 26-</sup>Ω series resistors are included in the output stages to match bus impedance and avoid external resistors.

# 2.7 Gunning Transceiver Logic (GTL)

The basic concept of a GTL bus is similar to a BTL system and is shown in Figure 12.

Figure 12. Principle Setup of an Open-Collector Bus System Using GTL Devices

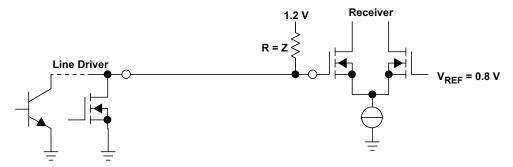

Because of the missing diode in the open-collector/drain outputs (compared to the BTL- solution), the low level is 0.4 V. With a chosen high level of 1.2 V, the voltage swing is reduced to 0.8 V only. Again, the threshold is in the middle of the voltage swing at 0.8 V.

With a drive capability of GTL outputs up to about 40 mA, the GTL devices are able to drive a termination resistor of 0.8 V/40 mA = 20  $\Omega$ . If the bus line is terminated correctly, the lowest impedance that can be driven by a GTL driver in the middle of a bus is 40  $\Omega$  (effectively the driver sees: 40  $\Omega$  || 40  $\Omega$  = 20  $\Omega$ ). As a result of the 0.8-V swing and the 40-mA IOL, the maximum power dissipation of one output is 16 mW. It is thus possible to integrate these low power drivers into ASICs.

# 2.7.1 Specialities of the GTL Device SN74GTL1655

With the SN74GTL1655, the benefits of the BTL family and GTL family are combined within one device. The drive capability of the SN74GTL1655 outputs now provides up to 100 mA, enabling the outputs to drive a termination resistor of 11  $\Omega$ .

With the GTL1655, even heavily loaded backplane buses can be served. For those buses, the line impedance can decrease down to  $22~\Omega$ .

All the features for live insertion and withdrawal have also been included in the GTL1655. The SN74GTL1655 further includes a selectable edge rate control (ERC) circuit for variable rise and fall rates so that the designers can fine-tune their circuits for maximum data throughput as system loading dynamically changes. The edge rate control minimizes bus-settling time.

## 2.7.2 Electrical

The gunning transceiver logic (GTL) devices support two different logic-level specifications: GTL (according EIA/JEDEC Standard EIA/JESD8-3) and the GTL + levels. The bus system is – similar to the BTL bus – realized as open-collector bus. No diode is included in the open-collector/drain output stage of the GTL-devices, such that the output low level can be reduced down to 0.4 V (GTL+: 0.55). With a chosen high level of 1.2 V for GTL (GTL+: 1.5 V), the voltage swing is reduced to 0.8 V (0.95 V) only. The threshold is in the middle of the voltage swing at 0.8 V (GTL+: 1 V).

GTL+ is becoming more and more a standard in the industry due to the enlarged noise margin of GTL+ levels. For example, GTL+ levels are being used on the Intel Pentium Pro (P6) processor to address this noise margin concern. By using GTL+ levels instead of GTL, the margin is increased about 16%.

# 2.7.3 Applicability

GTL was originally designed for a small bus on a board, for example, between a processor and its memory modules. Because the target application for GTL is not a backplane bus, but a bus on a board, no requirements for live insertion or withdrawal have been included in the specification.

With reduced output levels and state-of-the-art designs, the results are a reduction of power consumption, higher speeds, and improved signal integrity compared to the BTL bus, such that GTL+ backplane optimized-drivers are a premium solution for heavily loaded bus systems. Live insertion capabilities and an increased drive for low impedance backplanes are met with the GTL1655 device.

#### 2.7.4 Features

- Differential amplifier ensures stable threshold voltage of the receiver.

- Low voltage swing generates low switching noise.

- GTL:  $V_L = 0.4 \text{ V}$ ;  $V_H = 1.2 \text{ V}$

- GTL+:  $V_L = 0.55 \text{ V}$ ;  $V_H = 1.5 \text{ V}$

- High drive capable option available, enabling incident wave switching as low as 10  $\Omega$  or 20  $\Omega$  || 20- $\Omega$  line impedance

- GTL/GTL+: Low drive capability, I<sub>olmax</sub> = 40/50 mA

- GTL1655: High drive capability, I<sub>olmax</sub> = 100 mA

- Correct line termination using a pullup resistor at the line end avoids line reflections.

- Edge-rate-control-output circuit of GTL1655 enables variable output slew rate depending on load condition for maximum data throughput.

**Table 6. Top Device List GTL**

| DEVICE        | SPECIFICATION | DESCRIPTION                                                                                    | PACKAGE                     | STATUS    |

|---------------|---------------|------------------------------------------------------------------------------------------------|-----------------------------|-----------|

| SN74GTL16612  | LVTTL /GTL    | 18-bit LVTTL /GTL+ universal bus transceivers, like 16601 function                             | 56-pin SSOP<br>56-pin TSSOP | Available |

| SN74GTL1655   | LVTTL /GTL    | 17-bit LVTTL /GTL+ universal bus transceivers with live insertion, like 16501 function         | 64-pin TSSOP                | Available |

| SN74GTL16616  | LVTTL /GTL    | 16-bit LVTTL /GTL+ universal bus transceivers with buffered clock outputs, like 16601 function | 56-pin TSSOP<br>56-pin SSOP | Available |

| SN74GTL16622A | LVTTL /GTL    | 18-bit LVTTL /GTL+ bus transceivers, like 16601 function w/o LE and two CE                     | 64-pin TSSOP                | Available |

| SN74GTL16923  | LVTTL /GTL    | 18-bit LVTTL /GTL+ bus transceivers, like 16601 function w/o LE and two OE                     | 64-pin TSSOP                | Available |

# 2.8 Gunning Transceiver Logic Plus (GTLP)

GTLP devices are high-speed transceivers (LVTTL/card and GTLP/backplane) that operate like the GTL family with two major differences: they have been optimized for the distributed loads found in multislot backplanes, and they support live insertion with internal precharge circuitry. The GTLP reduced output swing (<1 V) and reduced input threshold levels allow higher backplane clock frequencies increasing the bandwidth for manufacturers developing next-generation telecommunication and data communication solutions. GTLP devices are backward-compatible with commonly used parallel backplane technologies such as ABT, FCT, LVT, ALVT, and FB+ and provide an alternative to more complex serial technologies.

GTLP offers two different drives, 50 mA and 100 mA at 0.55 V, to allow the designer flexibility in matching the device to backplane length, slot spacing, and termination resistor. The medium drive device can drive lines in point–to–point configurations down to 19  $\Omega$ . The lowest termination resistor that can be driven by the driver in the middle of a bus is 38  $\Omega$  (effectively the driver's load is 38  $\Omega$  || 38  $\Omega$  = 19  $\Omega$ ). The high drive devices can drive loads of 9.5  $\Omega$  (0.95 V/100 mA). Therefore, the minimum termination resistor for bus configuration is 19  $\Omega$ . It is important to pick a termination resistor that matches the backplane impedance for best signal integrity but is within the capacity of the driver. Impedance is a function of natural trace impedance ( $Z_0$ ), stub length, connector impedance, device impedance, and card spacing. Closer spacing reduces the effective impedance, which requires a smaller termination resistor as shown in Figure 13.

Figure 13. R<sub>T</sub> Versus Slot Spacing With GTLP Medium and High Drive Devices

To enhance the data throughput of a GTLP backplane a source synchronous clock layout is advised. Because the clock signal is sent from the same source, the flight time over the bus is eliminated in the timing budget. This roughly doubles the data throughput of the backplane. TI offers a special device, the GTLPH1627 and GTLPH16927, which has one bit integrated for the source synchronous clock. It also features a flexible set-up time adjustment (FSTA), which offers the designer an easy way to implement a source synchronous bus.

### 2.8.1 Electrical

Optimized for the GTLP signal level specifications, also operates at GTL (according JEDEC Standard JESD8–3) or GTL+ signal levels. The bus system, identical to the GTL bus, is realized as an open-drain bus. The GTLP voltage swing is from 1.5 V to 0.55 V with  $\pm 50$  mV around the  $V_{REF}$  threshold of 1 V.

# 2.8.2 Applicability

GTLP is used where the major concerns are higher data throughput, live insertion capability, or lower power consumption in parallel backplane architectures. GTLP offers up to four times the performance of TTL devices in backplane upgrade applications.

#### 2.8.3 Features

- 3.3-V operation with 5-V tolerant LVTTL inputs/outputs, which allow the devices to act as 5-V TTL to GTLP as well as 3.3-V LVTTL to GTLP translators

- Significantly improved output edge control (OEC) circuitry on the rising and falling edge of the GTLP outputs reduces line reflections, electromagnetic interference (EMI) and improves overall signal integrity allowing clock frequencies in excess of 80 MHz, with source synchronous clock layout even in excess of 120 MHz

- Fully supports live insertion with I<sub>off</sub>, PU3S and BIAS V<sub>CC</sub> circuitry

- Edge rate control (ERC) circuitry on high drive devices allows fast or slow edge rates.

- CMOS construction for 1/3 the static power consumption of BiCMOS logic devices

- A-port (LVTTL side) balanced drive of ±24 mA with optional bus-hold circuitry

**Table 7. Top Device List GTLP**

| DEVICE         | SPECIFICATION | DESCRIPTION                                                                            | PACKAGE                                                      | STATUS                          |

|----------------|---------------|----------------------------------------------------------------------------------------|--------------------------------------------------------------|---------------------------------|

| SN74GTLPH306   | LVTTL /GTLP   | 8-bit LVTTL /GTLP medium drive bus transceivers                                        | 24-pin SOIC<br>24-pin TSSOP<br>24-pin TVSOP                  | Available                       |

| SN74GTLP817    | LVTTL /GTLP   | GTLP/LVTTL medium drive with ERC 1:6 fan-out driver                                    | 24-pin SOIC<br>24-pin TSSOP<br>24-pin TVSOP                  | Available                       |

| SN74GTLP2033   | LVTTL /GTLP   | 8-bit Registered Transceiver with Split LVTTL Port and Feedback Path and ERC           | 48-pin TSSOP<br>48-pin TVSOP<br>56-ball VFBGA                | Available                       |

| SN74GTLP2034   | LVTTL /GTLP   | 8-bit Registered Transceiver with Split LVTTL Port and Feedback path and ERC           | 48-pin TSSOP<br>48-pin TVSOP<br>56-ball VFBGA                | Available                       |

| SN74GTLP21395  | LVTTL /GTLP   | Two 1-bit Transceiver with Split LVTTL Port, Feedback Path and Selectable Polarity     | 20-pin SOIC<br>20-pin TSSOP<br>20-pin TVSOP<br>20-ball VFBGA | Available                       |

| SN74GTLP22033  | LVTTL /GTLP   | 8-bit Registered Transceiver with Split LVTTL Port and Feedback path and ERC           | 48-pin TSSOP<br>48-pin TVSOP<br>56-ball VFBGA                | Available                       |

| SN74GTLP22034  | LVTTL /GTLP   | 8-bit Registered Transceiver with Split LVTTL Port and Feedback path and ERC           | 48-pin TSSOP<br>48-pin TVSOP<br>56-ball VFBGA                | Available                       |

| SN74GTLPH16912 | LVTTL /GTLP   | 18-bit LVTTL /GTLP medium drive universal bus transceivers                             | 56-pin TSSOP<br>56-pin TVSOP                                 | Product<br>Preview<br>available |

| SN74GTLPH16916 | LVTTL /GTLP   | 17-bit LVTTL /GTLP medium drive universal bus transceivers with Buffered Clock Outputs | 56-pin TSSOP<br>56-pin TVSOP                                 | Available                       |

| SN74GTLPH16927 | LVTTL /GTLP   | 18-bit LVTTL/GTLP medium drive transceiver with Source Synchronous Clock Outputs, FSTA | 56-pin TSSOP<br>56-pin TVSOP                                 | Product<br>Preview              |

| SN74GTLPH16945 | LVTTL /GTLP   | 16-bit LVTTL /GTLP medium drive bus transceivers                                       | 48-pin TSSOP<br>48-pin TVSOP                                 | Available                       |

| SN74GTLPH32912 | LVTTL /GTLP   | 36-bit LVTTL /GTLP medium drive universal bus transceivers                             | 114-ball LFBGA                                               | Available                       |

| SN74GTLPH32916 | LVTTL/GTLP    | 34-bit LVTTL /GTLP medium drive universal bus transceivers with Buffered Clock Outputs | 114-ball LFBGA                                               | Available                       |

| SN74GTLPH32945 | LVTTL /GTLP   | 32-bit LVTTL /GTLP medium drive universal bus transceivers                             | 96-ball LFBGA                                                | Available                       |

| SN74GTLP1394   | LVTTL /GTLP   | 2-bit LVTTL /GTLP high drive bus transceivers with ERC                                 | 16-pin SOIC<br>16-pin TSSOP<br>16-pin TVSOP                  | Available                       |

| SN74GTLP1395   | LVTTL /GTLP   | Two 1-bit LVTTL/ high drive bus transceivers with ERC                                  | 20-pin SOIC<br>20-pin TSSOP<br>20-pin TVSOP<br>20-ball VFBGA | Available                       |

| DEVICE         | SPECIFICATION | DESCRIPTION                                                                          | PACKAGE                                       | STATUS             |

|----------------|---------------|--------------------------------------------------------------------------------------|-----------------------------------------------|--------------------|

| SN74GTLPH1612  | LVTTL /GTLP   | 18-bit LVTTL /GTLP high drive universal bus transceivers with ERC                    | 64-pin TSSOP                                  | Available          |

| SN74GTLPH1616  | LVTTL/GTLP    | 17-bit LVTTL /GTLP high drive universal bus transceivers with Buffered Clock Outputs | 64-pin TSSOP                                  | Available          |

| SN74GTLPH1627  | LVTTL/GTLP    | 18-bit LVTTL/GTLP high drive transceiver with Source Synchronous Clock Outputs, FSTA | 56-pin TSSOP<br>56-pin TVSOP                  | Product<br>Preview |

| SN74GTLPH1645  | LVTTL /GTLP   | 16-bit LVTTL /GTLP high drive bus transceivers with ERC                              | 56-pin TSSOP<br>56-pin TVSOP<br>56-ball VFBGA | Available          |

| SN74GTLPH1655  | LVTTL /GTLP   | 16-bit LVTTL /GTLP high drive universal bus transceivers with ERC                    | 64-pin TSSOP                                  | Available          |

| SN74GTLPH3245  | LVTTL /GTLP   | 32-bit LVTTL /GTLP high drive bus transceivers with ERC                              | 114-pin LFBGA                                 | Available          |

| SN74GTLPH16612 | LVTTL /GTLP   | 18-bit LVTTL /GTLP medium drive universal bus transceivers                           | 56-pin SSOP<br>56-pin TSSOP                   | Available          |

Table 7. Top Device List GTLP (continued)

# 2.9 IEEE1284-Compatible Devices

The IEEE1284 standard provides an open path for communication between computers and intelligent printers and peripherals. The release of the standard signaling method for a bidirectional parallel peripheral interface for personal computers defines a common standard for bidirectional parallel communications between personal computers and peripherals. Preexisting methods used a wide variety of hardware and software products, each with unique and – in most cases – incompatible signaling schemes. An example is the Centronics printer port. An official standard for this printer port never existed. Therefore, problems in circuit designs occurred due to unknown hardware design elements, such as termination resistors or driver output impedance. For safe data transmission, only a short cable between host and peripheral (1 to 2 m) was acceptable. The release of the IEEE1284 standard answers the demand for an industry-wide, high-speed, high-integrity parallel port standard for a bidirectional peripheral interface. Texas Instruments offers three bus drivers. They support reliable data transfer through cables lengths up to 10 meters (30 feet) at a speed of 16 Mbps.

## 2.9.1 Electrical

The IEEE1284 specification defines the physical setup of the 1284 interface including wiring diagram, minimum drive capabilities, and termination considerations.

# 2.9.1.1 Applicability

The '1284-compatible devices are widely used from computer and peripheral manufacturers, because the '1284 standard can communicate more than 50 times faster than conventional parallel port interfaces. The protocol is defined in the IEEE1284 standard.

Figure 14. Typical Application Showing a 1284 Interface

#### 2.9.2 Features

- Designed for the IEEE Std 1284–I (Level 1 Type) and IEEE Std 1284–II (Level 2 Type) electrical specifications

- Adds bidirectional capabilities to the existing Centronics parallel interface

- Supports five modes of data transfer (Centronics; Nibble; Byte; EPP; ECP)

- Advanced operating mode can reach speeds of 16 to 32 Mbps

- New electrical interface, cabling, and connector for improved performance and reliability while retaining backward compatibility

- 50 to 100 times faster than the original parallel port (Centronics)

Table 8. Top Device List – IEEE 1284–Compatible Devices

| DEVICE          | SPECIFICATION | DESCRIPTION                                                           | PACKAGE                                                 | STATUS    |

|-----------------|---------------|-----------------------------------------------------------------------|---------------------------------------------------------|-----------|

| SN74ACT1284     | TTL           | 7-bit bus interface with 3-state outputs                              | 20-pin SOIC<br>20-pin SSOP<br>20-pin TSSOP<br>20-pin SO | Available |

| SN74LVC161284   | LVTTL         | 19-bit bus interface                                                  | 48-pin SSOP<br>48-pin TSSOP                             | Available |

| SN74LV161284    | LVTTL         | 19-bit bus interface                                                  | 48-pin SSOP<br>48-pin TSSOP                             | Available |

| SN74LVCZ161284A | LVTTL         | 19-bit bus interface with error free power-up                         | 48-pin TSSOP                                            | Available |

| SN74LVCE161284  | LVTTL         | 19-bit bus interface with error free power-up and 15KV ESD protection | 48-pin SSOP<br>48-pin TSSOP<br>48-pin TVSOP             | Available |

# 2.10 Local Interconnect Network (LIN)

The local interconnect network (LIN) was defined by a consortium of car makers, suppliers, and semiconductor companies. It is a concept for a low-cost automotive network that complements the existing portfolio of automotive multiplex networks by replacing complex power wiring harnesses with a bus and smart actuators and sensors. LIN is implemented as a sub-bus in a hierarchical vehicle network in order to provide quality enhancement and cost reduction in vehicles. The LIN standard includes the specification of the transmission protocol, the transmission medium (physical layer), the interface between development tools, and the interfaces for software programming. LIN promotes the interoperability of network nodes from the viewpoint of hardware and software and a predictable EMC behavior.

The specification calls for signaling rates up to 20 kbps using a single wire, high immunity to electrical interference, low electromagnetic emissions, and high ESD robustness. LIN is a single master with multiple slaves concept making it an ideal local sub-bus to the higher speed controller area network (CAN) typically used in the vehicle. The protocol may be implemented based on low-cost UART/SCI interface hardware, software equivalent, or as an embedded state machine. The LIN specification also provides a transport layer and diagnostic support.

LIN's simplicity and low-cost overhead makes it ideally suited in applications requiring a low number of small messages in a scheduled time with high reliability and low cost.

## 2.10.1 Electrical

The LIN standard defines half-duplex, single-ended transmission on cable lengths up to 40 meters with a maximum of 16 nodes at signaling rates up to 20 kbps. Additional nodes can be added but they lower bus impendence by approximately 3% per node. LIN is specified for reference to the vehicle battery voltage of 8 V to 18 V. However, with careful design, this can be extended to support commercial vehicles up to 27 V, but as always this involves a trade-off in signaling rate. A single cable with capacitance of 150 pF/m maximum is specified as the interconnect with a total bus capacitance of 10 nF. The bus is terminated at

the master node with a  $1-k\Omega$  pullup resistor and at each slave node with 30  $k\Omega$ . Nodes are connected to the bus through stubs. Data transmission circuits employing LIN are used in applications requiring a rugged interconnection, so robustness has been defined within the electrical layer and is designed into the physical layer transceivers. It withstands a wide input voltage range, has a wide short-circuit and transient voltage range, high ESD, and wide ground shifts to help ensure data integrity.

#### 2.10.2 Protocol

The LIN communications protocol describes how information is passed between devices on a network and conforms to the open systems interconnection (OSI) model that is defined in terms of layers. LIN 2.1 defines the functions of the lower layers of the OSI model that are performed within a LIN controller. An abundance of LIN programming routines is available from various vendors.

# 2.10.3 Applicability

The robust features of LIN make it ideally suited for the many rugged applications to which the LIN protocol is being adapted. Although it was developed within the automotive market, it is beginning to find additional uses in trucks, buses, agriculture, and marine vehicles. LIN-based control systems can be developed for other applications where low data rate, single wire, and low cost are key concerns.

### 2.10.4 Features

- Established standard and standardized products

- Fault tolerant high short-circuit protection

- · Robust interface for harsh electrical environments

Table 9. LIN Device List

| DEVICE                                 | FEATURES                                                                                                        | SUPPLY                                   | PACKAGE                                              |

|----------------------------------------|-----------------------------------------------------------------------------------------------------------------|------------------------------------------|------------------------------------------------------|

| TPIC1021x-Q1 LIN<br>Transceiver Family | High-temperature range and short-circuit protection. Low power sleep mode with wake up from LIN bus or HV input | VSUP: 7 V to 27 V<br>I/O: 3 V to 5.25 V  | 8-pin SOIC                                           |

| TMS470 MCU Family                      | Full LIN 2.0 controller. Low power modes                                                                        | Single 3.3 V or 3.3 V I/O and 1.8-V core | 80-, 100-, 144-pin LQFP                              |

| TMS570 MCU Family                      | Full LIN 2.0 controller. High performance.                                                                      | 3.3-V I/O and 1.5-V core                 | 128-, 144-, 176-pin LQFP<br>208-, 256-, 324-ball BGA |

# 2.11 Low-Voltage Differential-Multipoint (LVDM)

LVDM stands for LVDS-multipoint, enabling a half-duplex operation with LVDS voltage levels and speeds. It benefits from the same advantages as LVDS. Additionally, it allows bidirectional data transfer and the attachment of several drivers, receivers, and/or transceivers. LVDM is a LVDS-multipoint option exclusively available from TI. Meanwhile, a new standard has been released, following the industry demand for standardized multipoint-LVDS, including definitions such as bus contention-prevention, and so forth, which are of high importance when mixing devices of multiple suppliers. The next section addresses M-LVDS. As the devices following the new standard provide an higher output drive capability than LVDM, for some applications where power consumption and heat sinking is of concern, LVDM may still be an option versus M-LVDS. Existing products will remain available.

#### 2.11.1 Electrical

LVDM is LVDS with doubled driver output current. For bidirectional transfers, a termination is needed at each end of the line. The requirement of termination matching the line impedance remains. Therefore, both ends are terminated with  $100\text{-}\Omega$ . The effective termination resistance results in the parallel configuration of these two resistors, equaling half the impedance or twice the load. To ensure the same input voltage levels like with LVDS (that is, at a  $100\text{-}\Omega$  load), the output current is doubled to generate the required amplitude on just  $50~\Omega$ .

# 2.11.2 Applicability

LVDM can be used as a replacement for TIA/EIA–485 interconnections, especially for high-speed, low-power, and/or low EMI interfaces. As the physical parameters on the line are identical with LVDS, regular LVDS receivers may be used. This way, common-mode input range is between 0 V and 2.4 V, which limits the line length and the applicability in a electrically noisy environment. It is suited for backplane applications and cabled interfaces.

# 2.11.3 Features

- Drives double-terminated multipoint

- · Very high speed

- Very low power consumption

- Very low EMI

- Low cost

**Table 10. TOP LVDM Device List**

| DEVICE              | FEATURES                       | SUPPLY                         | PACKAGE      |

|---------------------|--------------------------------|--------------------------------|--------------|

| SN65LVDM176         | Single-Channel Transceiver     | VCC: 3.3 V<br>I/O: LVTTL /LVDM | 8-pin SOIC   |

| SN65LVDM1676 / 1677 | 16-Channel Transceiver         | VCC: 3.3 V<br>I/O: LVTTL /LVDM | 64-pin TSSOP |

| SN65LVDM050         | Dual-Channel Driver – Receiver | VCC: 3.3 V<br>I/O: LVTTL /LVDM | 16-pin SOIC  |

| SN65LVDM320         | Octal Latched Transceiver      | VCC: 3.3 V<br>I/O: LVTTL /LVDM | 64-pin TSSOP |

| SN65LVDM31          | Quad Driver                    | VCC: 3.3 V<br>I/O: LVTTL /LVDM | 16-pin SOIC  |

# 2.12 Stub Series Terminated Logic (SSTL)

Stub series terminated low-voltage logic (SN74SSTVxxx) designers are constantly trying to get the most out of their designs in the most cost-effective means. As faster versions of a particular CPU become available, the designer often tries to improve the throughput of an existing design simply by increasing the CPU clock frequency.

These issues resulted in JEDEC defining two SSTL switching standards (SSTL\_3, EIA/ JESD8–8, SSTL\_2, EIA/ JESD8-8). Both standards specify a particular termination scheme with appropriate values for the resistors and capacitors.

The SSTL interface standard is intended for high-speed memory interface applications and specifies switching characteristics such that operating frequencies up to 200 MHz are attainable. The primary application for SSTL devices is to interface with SDRAMs.

A two-resistor network is used to establish a voltage level such that differential voltage swings can be used and two different resistor value configurations can be acceptable.

Figure 15. Typical Output Buffer Environment, Class II of SSTL Standard