# High-Voltage Lifetime of the ISO72x Family of Digital Isolators

Ashish Gokhale and Gaddi Hasse

High-Performance Analog/Interface Products

# ABSTRACT

This application report examines the high-voltage lifetime characteristics of the isolation barrier in the ISO72x family of digital isolators. This provides the user with information regarding the long-term, high-voltage withstand capability of this family of products.

#### Contents

|   | Introduction                      |   |

|---|-----------------------------------|---|

| 2 | Insulation Properties and Ratings | 2 |

| 3 | ISO72x Device Description         | 2 |

| 4 | Modeling and Test Methodology     | 3 |

| 5 | Results                           | 4 |

| 6 | Conclusions                       | 5 |

| 7 | References                        | 6 |

|   |                                   |   |

#### List of Figures

| 1 | Isolation Barrier for ISO72x Family of Products | 2 |

|---|-------------------------------------------------|---|

| 2 | Test Setup for High-Voltage Lifetime            | 4 |

| 3 | High-Voltage Lifetime Using TDDB E Model        | 4 |

| 4 | High-Voltage Lifetime Based on Best Curve Fit   | 5 |

|   |                                                 |   |

## List of Tables

| 1 | Typical Data-Sheet Specifications of Insulation Characteristics | 2 |

|---|-----------------------------------------------------------------|---|

| 2 | High-Voltage Lifetime Predictions Based on TDDB E-Model         | 5 |

# Trademarks

All trademarks are the property of their respective owners.

# 1 Introduction

Industrial control systems often use digital isolators where downtime costs are high and reliability is a key concern for suppliers of equipment to this market. Data-sheet specifications adequately cover functional and parametric performance of the isolators, including maximum voltage capability of the isolation barrier for single-event, high-voltage transients. However, these specifications do not sufficiently address the behavior of the isolation properties under long-term application of a high voltage.

This application report provides a long-term prediction of the isolation properties of the ISO72x family of digital isolators when operated with a continuous input to output voltage of 560 V at a junction temperature of 150°C.

This report first defines insulation properties and ratings and then describes the ISO72x isolation barrier. It presents the time-dependent dielectric breakdown (TDDB) model and ISO72x test results.

## 2 Insulation Properties and Ratings

Dielectrics have intrinsic insulation properties determined by their physical and chemical composition, which includes impurities and imperfections (inclusions) that manufacturing may introduce. It is well understood that these inclusions cause the insulation properties to change over time and result in the eventual failure of the dielectric. These changes are accelerated by applying an electric field across the dielectric and/or by increasing its temperature.

Data-sheet specifications for most digital couplers only include initial ratings. For basic insulation applications, most of the commonly available (including ISO72x family) isolated couplers refer to a 4000-V ( $V_{IOTM}$ ) rating. Table 1 refers to typical data-sheet ratings provided by the manufacturer. By itself, this rating does not imply that the product can withstand 4000 V if applied for an indefinite time or at an arbitrarily high temperature. In fact, given only this rating, it is impossible to predict the voltage-withstand characteristics over time of such a product which may be subjected to repeated high-voltage strikes on a factory floor environment, for example.

#### Table 1. Typical Data-Sheet Specifications of Insulation Characteristics

| PARAMETER                          | SYMBOL                     | MAXIMUM                   | UNITS  |

|------------------------------------|----------------------------|---------------------------|--------|

| Maximum working insulation voltage | V <sub>IORM</sub>          | 560                       | V peak |

| Transient overvoltage              | V <sub>IOTM</sub>          | 4000                      | V peak |

| nout to output pools toot voltogo  | V <sub>PR</sub> , Method b | 1.875 × V <sub>IORM</sub> | V peak |

| Input-to-output peak test voltage  | V <sub>PR</sub> , Method a | $1.2 \times V_{IORM}$     | V peak |

| Insulation resistance              | R <sub>IO</sub>            | > 1E9                     | Ω      |

The other insulation rating that is of concern is the working voltage ( $V_{IORM}$ ), or continuous operating voltage. This voltage rating implies that the product retains its insulation properties over the lifetime of the product if it is operated at this voltage applied between the input and output. Usually, semiconductor products last for a minimum of 10 years.

## 3 ISO72x Device Description

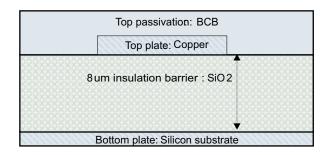

The ISO72x family of products consists of an input and an output semiconductor device separated by a high-impedance isolation barrier designed for the transfer of electrical signals across the barrier. The ISO72x uses capacitive coupling to transmit signals across the barrier while maintaining isolation of the output side with reference to input. The capacitor dielectric is semiconductor-grade silicon dioxide and is the isolation barrier. Figure 1 shows the capacitor is constructed from a top plate consisting of plated copper and a bottom plate made from doped silicon substrate. A BCB (benzocyclobutene) spin-on dielectric passivation over the top plate reinforces the insulation characteristics.

Figure 1. Isolation Barrier for ISO72x Family of Products

#### 4 Modeling and Test Methodology

#### 4.1 The TDDB E-Model for Dielectric Breakdown

Time-dependent dielectric breakdown (TDDB) is an important failure mode for dielectric materials like silicon dioxide (SiO<sub>2</sub>). The E-model <sup>(1)</sup> is the most widely accepted and used model for capacitor breakdown and can be applied to all dielectric thicknesses <sup>(2)</sup>. The E-model is not only phenomenological <sup>(3)</sup> but is also backed by a theoretical physical degradation mechanism <sup>(4)</sup>. The E-model is considered as the most conservative of all models in the literature (5). More complex systems, such as the one discussed in this document, may experience multiple failure modes, or degradation mechanisms; each of these modes can be modeled with its respective E-model. The sum of all these dielectric degradation rates would determine the overall time to failure.

A capacitor models the input to output of all isolated devices. The capacitor dielectric thickness and material type can vary from product to product. In the ISO72x family of products, this capacitor is part of the active circuit, as opposed to being part of the parasitic circuit in the case of optocouplers or inductive/magnetic-coupled devices.

The lifetime prediction is accomplished by a series of accelerated-stress TDDB testing. According to the E-model, the time to failure (TF) relates to the electric field as Equation 1 shows.

$$\ln(TF) \propto \frac{\Delta H_o}{k_b T} - \gamma Eox$$

(1)

where  $\Delta H_{o}$  is the enthalpy for oxide breakdown (referred to as activation energy),  $E_{ox}$  is the electric field across the isolation barrier, given by the ratio of applied-stress voltage ( $V_s$ ) to thickness of the insulation barrier,  $k_{\rm b}$  is Boltzmann's constant, and  $\gamma$  is the field acceleration parameter. The data was taken at 150°C, the worst-case operating condition, to avoid the need for temperature corrections. The only TF acceleration was through applying a higher voltage,  $V_s$ . Because  $V_s$  is proportional to  $E_{ox}$ , and temperature acceleration does not have to be accounted for, a simplified model can be used as is shown in Equation 2. (2)

$In(TF) \propto - MVs$

where M (voltage acceleration parameter) is a constant proportional to y. Thus, using Equation 2, the Emodel predicts that the relation is exponential, or, if TF is plotted on the y-axis using a log scale and V<sub>s</sub> on the x-axis using a linear scale, the relation looks linear on such a plot. In this case, M is the slope of this line.

This line is extrapolated to the operating voltage (V<sub>IORM</sub>) for lifetime prediction and will always be overly conservative. This is a result of accelerating the testing by applying voltages much higher than the operating voltage. The higher voltages activate additional dielectric-degradation modes leading to an apparent deviation from the E-model. The additional modes, which may not be active at lower voltages, tend to decrease the slope, which results in a lower projected TF.

#### 4.2 Test Methodology

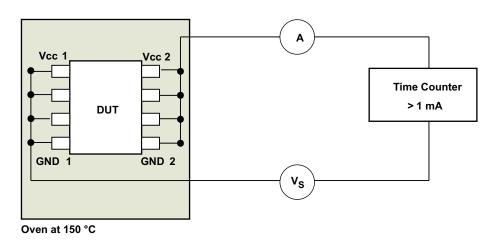

Normally, semiconductor lifetime is studied at the wafer level. However, due to the voltages involved and to get a more accurate analysis of the failure modes of the product, packaged units were used for testing in this application report. Through-hole, dual-in-line packages (DIP) generated artifact-free data in the test setup; therefore, DIP units generated the majority of the data points. Small-outline integrated circuit (SOIC) and DIP devices were tested and analyzed to confirm that the same failure modes were activated. Figure 2 shows the test setup for a device under test (DUT).

(3) See Reference 3.

<sup>(1)</sup> See Reference 1.

<sup>(2)</sup> See Reference 2.

<sup>(4)</sup> See References 4 and 5.

<sup>(5)</sup> See References 6 and 7.

Figure 2. Test Setup for High-Voltage Lifetime

The basic methodology was to apply a stress voltage from the input to the output of the DUT in a twoterminal configuration using a high-voltage source, while maintaining the still-air, ambient-air temperature at 150°C. The start of the test activated a timer; this timer stopped when the current in the circuit exceeded 1 mA, which meant that the dielectric had failed. The TF was noted for each applied test voltage. DUTs were tested independently of each other (one DUT per test) at each test voltage to get statistically valid results.

# 5 Results

# 5.1 TDDB E-Model Predictions

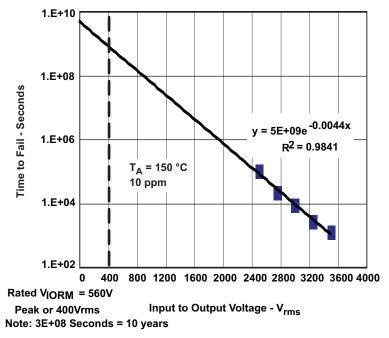

The raw data was statistically analyzed using a linearized Weibull <sup>(6)</sup> plot to determine the worst-case TF; this was extrapolated down to 10-ppm level at each test voltage. The extrapolated TF (10 ppm) is plotted against test voltage in Figure 3.

Figure 3. High-Voltage Lifetime Using TDDB E Model

<sup>(6)</sup> See Reference 12. Weibull plots are better suited for analyzing data such as capacitor breakdown.

Table 2 summarizes the lifetime predictions at different values of V<sub>IORM</sub> (Vpeak) using the TDDB E-model illustrated in Figure 3.

| V <sub>IORM</sub> , Vpeak | Lifetime per TDDB E-Model ( in<br>Years) |

|---------------------------|------------------------------------------|

| 200                       | 85                                       |

| 400                       | 46                                       |

| 560                       | 28                                       |

| 700                       | 18                                       |

| 800                       | 13                                       |

## Table 2. High-Voltage Lifetime Predictions Based on TDDB E-Model

# 5.2 Model Comparison

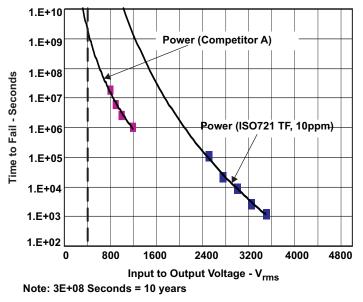

Unlike the use of the E-model, competitors often use an arbitrary fit to their data, that is not based on any physical dielectric degradation models. An example is a power fit shown in Figure 4. The same data used in Figure 3 was plotted here and a best-fit trend-line was generated using a power curve as shown in Figure 4. As can be seen, significantly longer lifetimes can be expected using such an approach. Published competitor data (also at 10-ppm levels) for inductive coupled devices are included for comparison. The competitor data was published using a time scale in years; therefore, in Figure 4, those units were converted from years to seconds for comparison. TI's preference for using the TDDB E-model is based on the fact that this model is conservative and should result in high-confidence predictions compared to any other models or a best data fit methodology.

Figure 4. High-Voltage Lifetime Based on Best Curve Fit

# 6 Conclusions

The ISO72x family of products can be safely operated for over 25 years at an operating voltage of 560 V. Results also show that the isolation barrier is robust and can withstand multiple instances of high-voltage spikes of up to 4000 Vpeak or 2828 Vrms, as specified by the  $V_{IOTM}$  rating

We currently recommend the ISO7710 from our newest ISO77xx family of digital isolators with improved isolation ratings.

5

Results

References

## 7 References

- Comparison of E and 1/E TDDB Models for SiO2 Under Long Term/Low Field Test Conditions, Joe McPherson, Vijay Reddy, Kaustav Banerjee, and Huy Le, Texas Instruments and University of California at Berkeley, IEDM 98-171-174

- 2. *Reliability Analysis Method for Low-k Interconnect Dielectrics Breakdown in Integrated Circuits*, G.S. Haase, E.T. Ogawa, and Joe McPherson, Journal of Applied Physics 98, 34503-34514 (2005

- 3. A. Berman, Proc. International Reliability Physics Symposium, IEEE 1981, page 204

- 4. Joe McPherson and D. Baglee, Proc. International Reliability Physics Symposium, IEEE 1985, page 1

- 5. Joe McPherson and H.C. Mogul, Journal of Applied Physics 84, 1513 (1984)

- 6. A Unified Gate Oxide Reliability Model, Chenming Hu and Qiang Lu, University of California, Berkeley; IEDM 99-445-448

- A Consistent Model for Time Dependent Dielectric Breakdown in Ukltrathin Silicon Dioxides, Kenji Okada and Kenji Yoneda, Matsushita Electronics Corporation; IEEE 99CH36296. 37th Annual International Reliability Physics Symposium, San Diego, CA 1999

- 8. HCPL-0721 Data Sheet, Avago Technologies

- 9. iCoupler Isolation Technology: Eliminate Those Optocoupler Headaches!, Analog Devices

- 10. ADuM1100 Datasheet Revision E, Analog Devices

- 11. Texas Instruments, ISO72x Single Channel High-Speed Digital Isolators data sheet

- 12. Probability and Statistics for Engineers, Third Edition, Irwin Miller, John E. Freund, Prentice Hall ISBN 0-13-711938-0

Page

# **Revision History**

# NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

# Changes from Original (January 2006) to A Revision

| • | Added reference to the ISO7710 device and ISO77xx family of digital isolators in the Conclusion | 5 |

|---|-------------------------------------------------------------------------------------------------|---|

|---|-------------------------------------------------------------------------------------------------|---|

#### IMPORTANT NOTICE FOR TI DESIGN INFORMATION AND RESOURCES

Texas Instruments Incorporated ('TI") technical, application or other design advice, services or information, including, but not limited to, reference designs and materials relating to evaluation modules, (collectively, "TI Resources") are intended to assist designers who are developing applications that incorporate TI products; by downloading, accessing or using any particular TI Resource in any way, you (individually or, if you are acting on behalf of a company, your company) agree to use it solely for this purpose and subject to the terms of this Notice.

TI's provision of TI Resources does not expand or otherwise alter TI's applicable published warranties or warranty disclaimers for TI products, and no additional obligations or liabilities arise from TI providing such TI Resources. TI reserves the right to make corrections, enhancements, improvements and other changes to its TI Resources.

You understand and agree that you remain responsible for using your independent analysis, evaluation and judgment in designing your applications and that you have full and exclusive responsibility to assure the safety of your applications and compliance of your applications (and of all TI products used in or for your applications) with all applicable regulations, laws and other applicable requirements. You represent that, with respect to your applications, you have all the necessary expertise to create and implement safeguards that (1) anticipate dangerous consequences of failures, (2) monitor failures and their consequences, and (3) lessen the likelihood of failures that might cause harm and take appropriate actions. You agree that prior to using or distributing any applications. TI has not conducted any testing other than that specifically described in the published documentation for a particular TI Resource.

You are authorized to use, copy and modify any individual TI Resource only in connection with the development of applications that include the TI product(s) identified in such TI Resource. NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT OF TI OR ANY THIRD PARTY IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information regarding or referencing third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of TI Resources may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

TI RESOURCES ARE PROVIDED "AS IS" AND WITH ALL FAULTS. TI DISCLAIMS ALL OTHER WARRANTIES OR REPRESENTATIONS, EXPRESS OR IMPLIED, REGARDING TI RESOURCES OR USE THEREOF, INCLUDING BUT NOT LIMITED TO ACCURACY OR COMPLETENESS, TITLE, ANY EPIDEMIC FAILURE WARRANTY AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY YOU AGAINST ANY CLAIM, INCLUDING BUT NOT LIMITED TO ANY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON ANY COMBINATION OF PRODUCTS EVEN IF DESCRIBED IN TI RESOURCES OR OTHERWISE. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, DIRECT, SPECIAL, COLLATERAL, INDIRECT, PUNITIVE, INCIDENTAL, CONSEQUENTIAL OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF TI RESOURCES OR USE THEREOF, AND REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

You agree to fully indemnify TI and its representatives against any damages, costs, losses, and/or liabilities arising out of your noncompliance with the terms and provisions of this Notice.

This Notice applies to TI Resources. Additional terms apply to the use and purchase of certain types of materials, TI products and services. These include; without limitation, TI's standard terms for semiconductor products <a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation modules, and samples (<a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2018, Texas Instruments Incorporated