# SN65DSI83, SN65DSI84, and SN65DSI85 Hardware Implementation Guide

Yoon Lee

Computer and Consumer Interface

#### ABSTRACT

This document includes guidelines and recommendations for implementing the SN65DSI83, SN65DSI84, or SN65DSI85 in system hardware. These recommendations are only guidelines and it is the designer's responsibility to consider all system characteristics and requirements. The engineers should refer to the datasheets for technical details such as device operation, terminal description, and so forth.

#### Contents

| 1 | Overview                           |                                              | 2 |

|---|------------------------------------|----------------------------------------------|---|

|   | 1.1                                | What are SN65DSI83, SN65DSI84 and SN65DSI85? | 2 |

| 2 | Hardware Implementation Guidelines |                                              |   |

|   |                                    | Layout Recommendation                        |   |

|   | 2.2                                | RESET Implementation                         |   |

|   | 2.3                                | ADDR                                         | 5 |

|   | 2.4                                | LVDS REVERSE Routing Option                  | 5 |

|   | 2.5                                | Unused DSI Channels or Lanes                 | 6 |

|   | 2.6                                | RSVD Pins                                    | 6 |

| 3 | References                         |                                              | 6 |

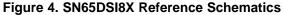

| 4 | Reference Schematics               |                                              |   |

#### List of Figures

| 1 | SN65DSI85 Layout Example                 | 4 |

|---|------------------------------------------|---|

| 2 | Cold Start Vcc Ramp Up to EN             | 5 |

| 3 | RESET or SHUTDOWN Timing When Vcc = HIGH | 5 |

| 4 | SN65DSI8X Reference Schematics           | 7 |

|   |                                          |   |

### List of Tables

| 1 | SN65DSI8X Features Summary       | 2 |

|---|----------------------------------|---|

| 2 | Channel A LVDS Reverse Pin Order | 6 |

| 3 | Channel B LVDS Reverse Pin Order | 6 |

Overview

2

#### 1 **Overview**

#### 1.1 What are SN65DSI83, SN65DSI84 and SN65DSI85?

The three devices: SN65DSI83, SN65DSI84 and SN65DSI85 will be referred to as SN65DSI8X in this document. SN65DSI8X is an MIPI DSI-to-LVDS bridge device that supports video modes in forward direction. The SN65DSI8X is primarily targeted for portable applications such as tablets and smart phones that utilize the MIPI DSI video format. The SN65DSI8X can be used between a GPU with DSI output and a video panel with LVDS inputs.

All three devices share the same pin out and package.

Table 1 lists a summary of the feature sets on these devices.

| Part Name | Description                                   | Max Resolution                                         |

|-----------|-----------------------------------------------|--------------------------------------------------------|

| SN65DSI83 | Single Channel DSI to Single-Link LVDS        | Suitable 1366x768/1280x800 60 fps at 24 bpp/18 bpp     |

| SN65DSI84 | Single Channel DSI to two Single-Link<br>LVDS | 1920x1200 60 fps at 24 bpp/18 bpp                      |

| SN65DSI85 | Dual Channel DSI to two Single-Link LVDS      | 2560x1600 60 fps, 1920x1080p 120 fps at 24 bpp /18 bpp |

### Table 1. SN65DSI8X Features Summary<sup>(1)</sup>

<sup>(1)</sup> Each DSI Channel has 4 DSI data lanes + 1 CLK lane. Each LVDS link has 4 data lanes + 1 CLK lane.

# 2 Hardware Implementation Guidelines

# 2.1 Layout Recommendation

### 2.1.1 Parts and Component Placement

### 2.1.1.1 VCORE Pin

This pin outputs 1.1 V from the internal voltage regulator. The pin MUST have a  $1-\mu F$  external capacitor to GND.

# 2.1.1.2 REFCLK

A series resistor is recommended near the RECLK source for EMI reduction purpose. If possible, bury the REFCLK trace in the inner layer, or minimize the trace length from the REFCLK terminal to the CLK source by placing the source near the SN65DSI8X REFCLK terminal, or do both.

### 2.1.1.3 Decoupling Capacitors

Decoupling capacitors should be placed near the power plane and power rails for the SN65DSI8X. The trace length between decoupling capacitors must be minimized to avoid large current loops and trace inductance. The use of four ceramic capacitors (two 0.1  $\mu$ F and two 0.01  $\mu$ F) near the SN65DSI8X is recommended.

# 2.1.2 Critical Routes

- DA\*P/N and DB\*P/N pairs should be routed together with controlled-differential 100-Ω impedance. Keep away from other high speed signals. Keep lengths within 5 mil of each other. Keep traces on layers adjacent to ground plane. The number of VIAS should be kept to a minimum. Each pair should be separated at least by 3 times the signal trace width. Route all differential pairs on the same group of layers (outer layers or inner layers) if not on the same layer.

- A\_Y\*P/N and B\_Y\*P/N pairs should be routed together with controlled differential 100-Ω impedance. Keep away from other high speed signals. Keep lengths within 5 mil of each other. Keep traces on layers adjacent to ground plane. The number of VIAS should be kept to a minimum. Each pair should be separated at least by 3 times the signal trace width. Route all differential pairs on the same group of layers (outer layers or inner layers) if not on the same layer.

- Ref CLK trace should be routed as short as possible.

# 2.1.3 Spread Spectrum CLK

The system is allowed to provide the center spread CLK input to the REFCLK or DSI CLK for EMI reduction purpose. The center spread CLK input to the REFCLK or DSI CLK is passed through to the LVDS CLK output A\_CLKP/N or B\_CLKP/N. The spread depth can be 0.5% to 2% with 30 Hz to 50 Hz of modulation frequency range.

3

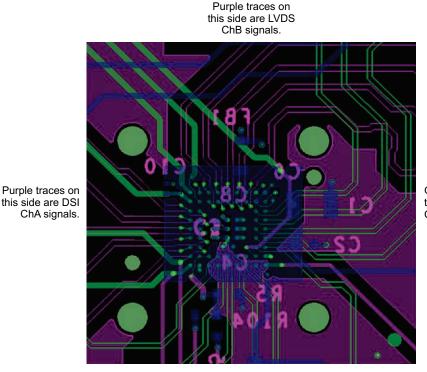

Green traces on this side are LVDS ChA signals.

Green traces on this side are LVDS ChB signals.

Green - TOP Layer, Purple - Layer 3, Blue - Bottom

# Figure 1. SN65DSI85 Layout Example

The layer stack up of the board in Figure 1 is as shown in the following:

\*6-layer PCB\* Layer 1: Top component side Layer 2: GND Layer 3: Signal Route Layer4: Power Layer 5: GND Layer 6: Bottom component side

# 2.2 **RESET** Implementation

The SN65DSI8X is reset by controlling the EN terminal (pin B1). The reset implementation defined in the datasheet should be followed for correct operation of the device after the reset.

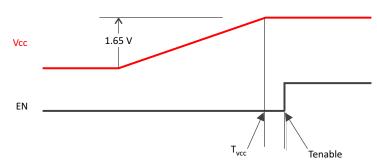

Figure 2 and Figure 3 depict the reset timing. User should refer to the datasheet for further details on reset operation.

Figure 2 shows the EN implementation during cold start when the device is first powered on.  $T_{enable}$  must be always greater than  $T_{vcc}$ . In case of using the passive reset circuitry, this timing must be insured by using the correct values of R and C which could vary depending on the ramp up time of the system. The internal R value on the EN is 200 k $\Omega$ .

Figure 2. Cold Start Vcc Ramp Up to EN

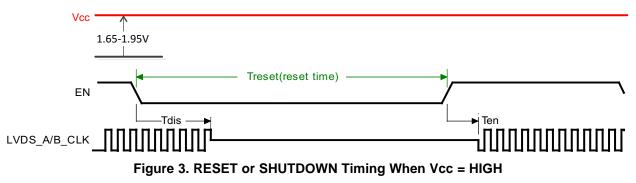

Figure 3 shows the EN implementation while the device is powered on. The following timing must be met when the SN65DSI8X transitions from a normal operation state to a RESET or SHUTDOWN state while Vcc remains high.

# 2.3 ADDR

The ADDR determines the least significant bit of the I<sup>2</sup>C ADDR for the SN65DSI8X. This bit should be pulled high or low through a resistor depending on the I<sup>2</sup>C address the system chooses to use for the SNDSI85. When this pin is pulled low, the device address is 0x2C, high 0x2D.

# 2.4 LVDS REVERSE Routing Option

The SN65DSI85 allows reversing or swapping the order of the LVDS pins via the register bit control at address 0x1A per the definitions below.

# 2.4.1 LVDS Even Odd Swap Option

By setting the 0x1A bit6 EVEN\_ODD\_SWAP bit in the CSR, the routing of even and odd pixels can be swapped. When this bit is set to 0 (default), odd pixels are routed to LVDS Channel A (A\_Y\*P/N) and even pixels routed to LVDS Channel B (B\_Y\*P/N). When this bit is set to 1, odd pixels are routed to LVDS Channel B (B\_Y\*P/N) and even pixels routed to LVDS Channel A (A\_Y\*P/N).

# 2.4.2 LVDS Reverse Pin Order Option

The order of the LVDS pins for LVDS Channel A or Channel B can be reversed by CSR configurations at the address 0x1A bits 5 CHA\_REVERSE\_LVDS and bit4 CHB\_REVERSE\_LVDS.

5

**NOTE:** When it is pulled high, it must be tied to the device Vcc such that this pin does not remain high when the device power is removed.

References

| Pin Number | CHA_REVERSE_LVDS=0 (Default) | CHA_REVERSE_LVDS=1 |

|------------|------------------------------|--------------------|

| C8         | A_Y0P                        | A_Y3P              |

| C9         | A_YON                        | A_Y3N              |

| D8         | A_Y1P                        | A_CLKP             |

| D9         | A_Y1N                        | A_CLKN             |

| E8         | A_Y2P                        | A_Y2P              |

| E9         | A_Y2N                        | A_Y2N              |

| F8         | A_CLKP                       | A_Y1P              |

| F9         | A_CLKN                       | A_Y1N              |

| G8         | A_Y3P                        | A_Y0P              |

| G9         | A_Y3N                        | A_Y0N              |

# Table 2. Channel A LVDS Reverse Pin Order

# Table 3. Channel B LVDS Reverse Pin Order

| Pin Number | CHB_REVERSE_LVDS=0 (Default) | CHB_REVERSE_LVDS=1 |

|------------|------------------------------|--------------------|

| B3         | B_Y0P                        | B_Y3P              |

| A3         | B_Y0N                        | B_Y3N              |

| B4         | B_Y1P                        | B_CLKP             |

| A4         | B_Y1N                        | B_CLKN             |

| B5         | B_Y2P                        | B_Y2P              |

| A5         | B_Y2N                        | B_Y2N              |

| B6         | B_CLKP                       | B_Y1P              |

| A6         | B_CLKN                       | B_Y1N              |

| B7         | B_Y3P                        | B_Y0P              |

| A7         | B_Y3N                        | B_Y0N              |

#### 2.5 **Unused DSI Channels or Lanes**

Unused DSI input terminals (DA\*N/P, DB\*N/P) should be left unconnected or driven to LP11 state.

#### 2.6 **RSVD** Pins

The RSVD1 and RSVD2 are reserved pins. Leave these unconnected for normal operation.

#### 3 References

SN65DSI8X Datasheets (SLLSEB9, SLLSEC1, SLLSEC2)

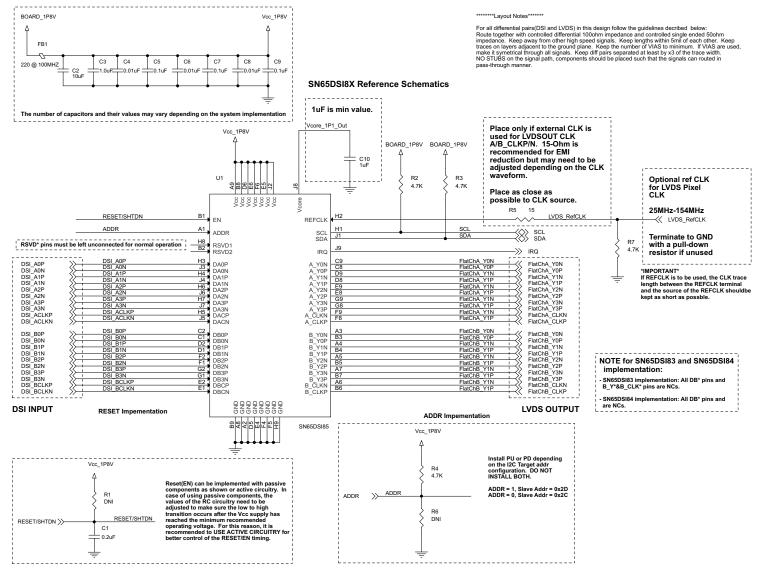

# 4 Reference Schematics

#### Figure 4 schematics for the SN65DSI8X reference design.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

| Products                     |                                 | Applications                  |                                   |

|------------------------------|---------------------------------|-------------------------------|-----------------------------------|

| Audio                        | www.ti.com/audio                | Automotive and Transportation | www.ti.com/automotive             |

| Amplifiers                   | amplifier.ti.com                | Communications and Telecom    | www.ti.com/communications         |

| Data Converters              | dataconverter.ti.com            | Computers and Peripherals     | www.ti.com/computers              |

| DLP® Products                | www.dlp.com                     | Consumer Electronics          | www.ti.com/consumer-apps          |

| DSP                          | dsp.ti.com                      | Energy and Lighting           | www.ti.com/energy                 |

| Clocks and Timers            | www.ti.com/clocks               | Industrial                    | www.ti.com/industrial             |

| Interface                    | interface.ti.com                | Medical                       | www.ti.com/medical                |

| Logic                        | logic.ti.com                    | Security                      | www.ti.com/security               |

| Power Mgmt                   | power.ti.com                    | Space, Avionics and Defense   | www.ti.com/space-avionics-defense |

| Microcontrollers             | microcontroller.ti.com          | Video and Imaging             | www.ti.com/video                  |

| RFID                         | www.ti-rfid.com                 |                               |                                   |

| OMAP Applications Processors | www.ti.com/omap                 | TI E2E Community              | e2e.ti.com                        |

| Wireless Connectivity        | www.ti.com/wirelessconnectivity |                               |                                   |

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2013, Texas Instruments Incorporated