# Using the SPI Interface With TRF7960

ShreHarsha Rao

#### ABSTRACT

One of the microcontroller interfacing options available for the TRF7960 is the SPI with SS\*. This is also known as 4-wire hardware SPI mode. The TRF7960 device acts as the slave device and the microcontroller or DSP is the master in this configuration.

#### Contents

| TRF79 | 960 - SPI With SS* Mode Errata                   | 2 |

|-------|--------------------------------------------------|---|

| 1.1   | SCLK Polarity Switch                             | 3 |

| 1.2   | IRQ Status Register Read                         | 4 |

|       | Direct Command Processing                        |   |

| 1.4   | Initialization of Derivative Registers           | 7 |

| 1.5   | Transmitting One Byte Through the FIFO           | 7 |

| 1.6   | Extra Dummy Bytes on RX                          | 8 |

| 1.7   | Timing Conditions for MOSI With Respect to S_CLK | 9 |

|       |                                                  |   |

#### Trademarks

1

Tag-it is a trademark of Texas Instruments. All other trademarks are the property of their respective owners.

#### 1 TRF7960 - SPI With SS\* Mode Errata

It is important to note that there are some nonstandard conditions when the TRF7960 is operated in the SPI mode. Table 1 lists these conditions and the software patches to work around them.

| Condition                                                                                                                                                      | Software Fix                                                                                                                                                                                  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SCLK clock polarity switch needed when read operation (single or continuous) is executed.                                                                      | Firmware fix to switch clock polarity between writes and reads (see Section 1.1).                                                                                                             |

| IRQ Status register is not automatically cleared after reading.                                                                                                | Dummy read is needed to clear the contents of IRQ status register<br>and hence drive the IRQ pin low (see Section 1.2).                                                                       |

| All stand-alone (single-byte) direct commands need additional clock cycle to work. An example is the slot markers (EOF) for ISO 15693 do not work in SPI mode. | All direct command functions need to have this additional SW fix.<br>Direct commands like "Transmit Next Slot" needs to have additional<br>SCLK cycle before SS* goes high (see Section 1.3). |

| Some of the registers (RX wait time, RX no response wait time) do not take default values when the appropriate protocol is chosen in the ISO control register. | Manually program these defaults again in the initialization routine (see Section 1.4).                                                                                                        |

| Transmitting one byte through the FIFO.                                                                                                                        | Split the command (See Section 1.5).                                                                                                                                                          |

#### **Table 1. Nonstandard Conditions**

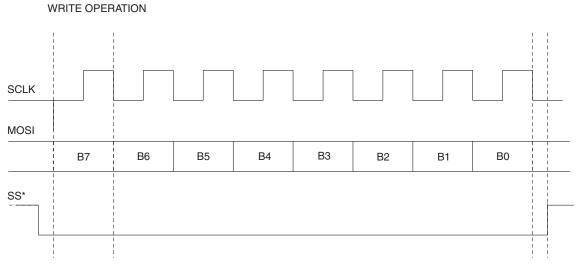

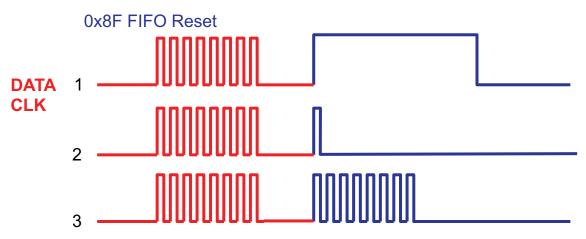

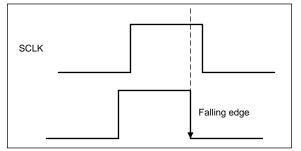

The serial interface is in reset while the SS\* signal is high. Serial Data-In (MOSI) changes on the falling edge, and are validated in the reader on the rising edge (see Figure 1). Communication is terminated when SS\* signal goes inactive (high). All words must be 8 bits long with the MSB transmitted first.

Figure 1. Serial - SPI Interface Communication (Write Mode)

### 1.1 SCLK Polarity Switch

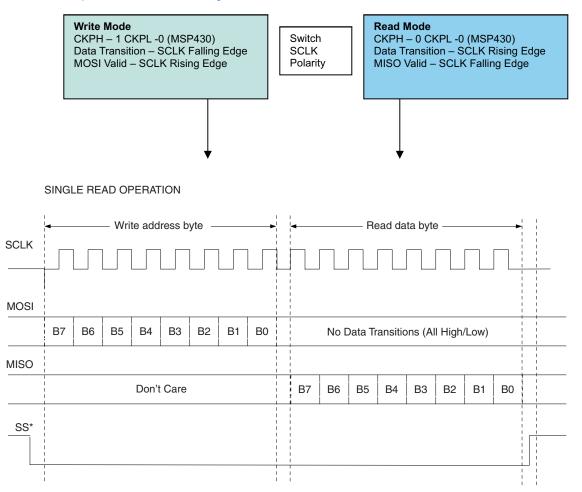

The SPI read operation is shown in Figure 2 below.

Figure 2. Serial - SPI Interface Communication (Read Mode)

The read command is sent out on the MOSI pin, MSB first in the first 8 clock cycles. MOSI data changes on the falling edge, and is validated in the reader on the rising edge (see Figure 2). During the write cycle the serial data out (MISO) is not valid. After the last read command bit (B0) is validated at the 8th rising edge of SCLK, after half a clock cycle, valid data can be read on the MISO pin at the falling edge of SCLK. It takes 8 clock edges to read out the full byte (MSB first).

**NOTE:** When using the hardware SPI (for example, a MSP430 hardware SPI) to implement the above feature, care must be taken to switch the SCLK polarity after write phase for proper read operation. The example clock polarity for the MSP430-specific environment is shown in the box above. Refer to the USARTSPI chapter for any specific microcontroller family for further information on the setting the appropriate clock polarity.

This clock polarity switch NEEDS to be done for all read (single, continuous) operations.

The MOSI (serial data out) should not have any transitions (all high or all low) during the read cycle. Also, the SS\* should be low during the whole write and read operation.

TRF7960 - SPI With SS\* Mode Errata

TRF7960 - SPI With SS\* Mode Errata

The clock polarity switch is illustrated by the following pseudo code. This code refers specifically to the MSP430 platform. See the data sheet of the relevant microcontroller for your design.

```

*pbuf = (0x40 | *pbuf);

// address, read, single

*pbuf = (0x5f &*pbuf);

// register address

while (!(IFG2 & UCBOTXIFG));

// USCI_B0 TX buffer ready?

UCB0TXBUF = *pbuf;

// Previous data to TX, RX

//while (!(IFG2 & UCB0RXIFG));

temp=UCB0RXBUF;

UCB0CTL1 = UCSWRST;

UCB0CTL0 &= ~UCCKPH;

// switch clock polarity for read

UCB0CTL1 &= ~UCSWRST;

SPIStartCondition();

// SCLK High/Low to complete the cycle

P3SEL |= BIT3;

// USCI_B0 TX buffer ready?

while (!(IFG2 & UCB0TXIFG));

UCB0TXBUF = 0 \times 00;

// Receive initiated by a dummy TX write???

while (!(IFG2 & UCBORXIFG));

_NOP();

_NOP();

*pbuf = UCB0RXBUF;

pbuf++;

lenght--;

UCB0CTL0 |= UCCKPH;

// revert to original clock polarity

```

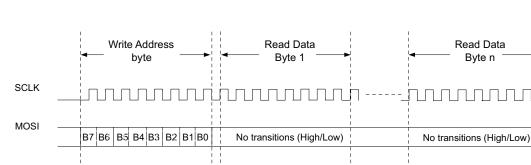

Figure 3 shows the continuous read operation.

Don't Care

#### **Continuous Read Operation**

B7 B6 B5 B4 B3 B2 B1 B0

#### 1.2 **IRQ Status Register Read**

MISO

SS\*

4

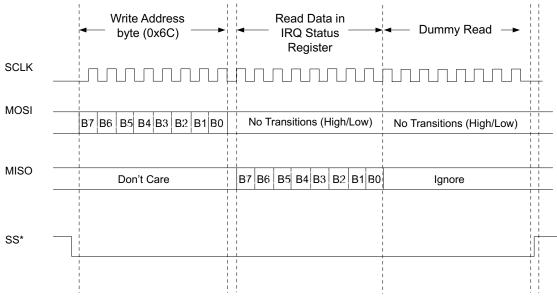

NOTE: Special steps are needed when you read the TRF796x IRQ status register (register address 0x0C) in SPI mode. The status of the bits in this register are cleared after a "dummy read". The following steps need to be followed when reading the IRQ status register.

Read Data

Byte n

B7 B6 B5 B4 B3 B2 B1 B0

- 1. Write in command 0x6C: read 'IRQ status' register in continuous mode (8 clocks).

- 2. Read out the data in register 0x0C (8 clocks).

- 3. Generate another 8 clocks (as you were reading the data in register 0x0D) but ignore the MISO data line.

This is shown in Figure 4.

# Special Case – IRQ Status Register Read

Figure 4. SPI Interface Communication (IRQ Status Register Read)

# 1.3 Direct Command Processing

Table 2 lists the direct commands supported by the TRF7960 and TRF7961.

#### Table 2. Command Codes

| Command Code (hex) | Command                                         | Comments                                        |

|--------------------|-------------------------------------------------|-------------------------------------------------|

| 00                 | Idle                                            |                                                 |

| 03                 | Software initialization                         | Software initialization, same as power on reset |

| 0F                 | Reset FIFO                                      |                                                 |

| 10                 | Transmission without CRC                        |                                                 |

| 11                 | Transmission wtih CRC                           |                                                 |

| 12                 | Delayed transmission without CRC                | EPC                                             |

| 13                 | Delayed transmission with CRC                   | EPC                                             |

| 14                 | Transmit next time slot                         | ISO15693, Tag-it™                               |

| 16                 | Block receiver                                  |                                                 |

| 17                 | Enable receiver                                 |                                                 |

| 18                 | Test internal RF (RSSI at RX input with TX off) |                                                 |

| 19                 | Test internal RF (RSSI at RX input with TX on)  |                                                 |

#### TRF7960 - SPI With SS\* Mode Errata

www.ti.com

Table 3 lists the direct commands that need the software fix when using SPI with SS\* mode. These are the direct commands that are executed stand-alone (direct commands with just one byte).

| Direct Command               | Command Code | Need Dummy Clock |

|------------------------------|--------------|------------------|

| Idle                         | 0x03         | Yes              |

| Software initialization      | 0x00         | Yes              |

| Reset FIFO                   | 0x0F         | Yes              |

| Transmit next time slot      | 0x14         | Yes              |

| Block receiver               | 0x16         | Yes              |

| Enable receiver              | 0x17         | Yes              |

| Test internal RF             | 0x18         | Yes              |

| Test external RF             | 0x19         | Yes              |

| Transmit without CRC         | 0x10         | No               |

| Transmit with CRC            | 0x11         | No               |

| Delayed transmit without CRC | 0x12         | No               |

| Delayed transmit with CRC    | 0x13         | No               |

#### **Table 3. Direct Commands**

It is recommended to have this software fix written as part of a direct command function. An example of a direct command is the slot markers (EOF) for ISO 15693. This will not work in SPI mode.

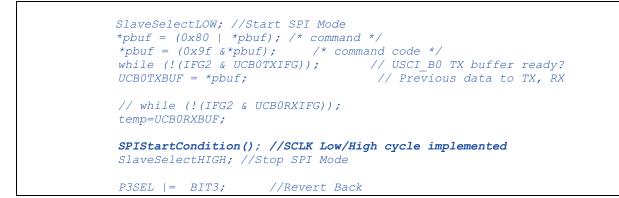

This is solved by a software fix by implementing the direct command (for example transmit next slot") in one of two ways:

- 1. Have an additional SCLK cycle (low/high) before SS\* goes high.

- or

- 2. Send a dummy TX write (8 SCLK cycles) before SS\* goes high.

This is shown in the diagram below.

Any one of the three dummy clock options work.

The pseudo code shown below in the DirectCommand function implements a SCLK low/high/low transition.

Texas

**STRUMENTS**

#### 1.4 Initialization of Derivative Registers

Some of the registers (RX wait time, RX no response wait time) do not take default values when the Tagit<sup>™</sup> protocol is chosen in the ISO control register. This is solved by manually programming the timing related registers in the Initialization routine as shown in the pseudo code of the TIInventoryRequest function below.

```

//added code

buf[0] = RXNoResponseWaitTime;

buf[1] = 0x14;

buf[2] = ModulatorControl;

buf[3] = 0x21;

WriteSingle(buf, 4);

//end added code

```

It is also recommended that the modulator and system clock register (register 0x09) be re-initialized when the inventory request (15693) or REQB (14443B) or REQA (14443A) is issued.

#### 1.5 Transmitting One Byte Through the FIFO

When transmitting one byte to the TRF7960 using SPI with SS\* mode, a special firmware fix is needed. This method involves splitting the writes into two operations as shown in the pseudo code below.

```

buf[0] = 0x8f;

buf[1] = 0x91;

buf[2] = 0x3d;

buf[3] = 0x00;

buf[4] = 0x10;

RAWwrite(&buf[0], 5);

buf[5] = 0x3F;

buf[6] = "one byte data to be transmitted";

buf[7] = 0x00;

RAWwrite(&buf[5], 3);

```

Each RAW Write function takes the SS low and high. Please refer to the TRF7960 firmware for definition of RAWwrite function. (file name parallel.c)

#### 1.6 Extra Dummy Bytes on RX

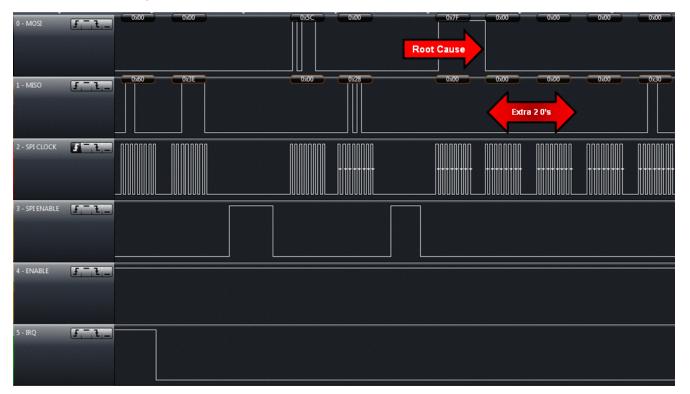

A specific condition can cause the TRF7960 to output two additional dummy bytes of data when reading the FIFO after an RX operation. This occurs when the MOSI line is left high after issuing the direct command to continuous read from the TRF7960 FIFO. The MOSI line can left high due to not properly resetting the SPI module while changing the SCLK polarity for the read operation. Figure 5 shows the root cause of this output.

Figure 5. Screenshot With Root Cause

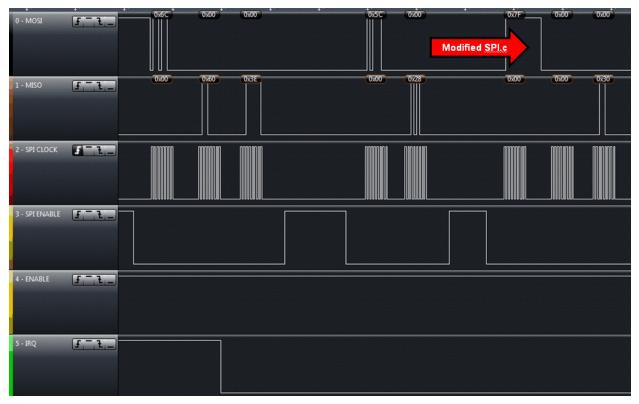

To fix this, ensure the SPI module is properly reset in the MCU when toggling the SCLK polarity between read and write operations. This should force the MOSI line back low and resolve the issue. Figure 6 shows the updated firmware, and Figure 7 shows the signals after correction.

| .84 <b>vo</b> : | id                                              |                                         |

|-----------------|-------------------------------------------------|-----------------------------------------|

| .85 <b>Sp</b> : | <pre>iReadCont(u08_t *pbuf, u08_t length)</pre> |                                         |

| .86 {           |                                                 |                                         |

| .87             | u08_t j = 0;                                    |                                         |

| .88<br>.89      | SLAVE SELECT LOW;                               | //Start SPI Mode                        |

| .90             | // Address/Command Word Bit Distribution        | //Start SPI Houe                        |

| .91             | *pbuf = (0x60   *pbuf);                         | <pre>// address, read, continuous</pre> |

| .92             | *pbuf = (0x7f &*pbuf);                          | // register address                     |

| .93             | while (!(IFG2 & UCB0TXIFG))                     | <pre>// USCI_B0 TX buffer ready?</pre>  |

| .94             | {                                               |                                         |

| .95             | }                                               |                                         |

| .96             | UCB0TXBUF = *pbuf;                              | <pre>// Previous data to TX, RX</pre>   |

| .97<br>.98      | while(UCB0STAT & UCBUSY)                        |                                         |

| .98             | s                                               |                                         |

| :00             | 1                                               |                                         |

| :01             | ,                                               |                                         |

| :02             | <pre>temp = UCB0RXBUF;</pre>                    |                                         |

| :03             |                                                 |                                         |

| :04             | UCB0CTL1  = UCSWRST;                            |                                         |

| :05             | UCB0CTL0 &= ~UCCKPH;                            |                                         |

| 106             | UCB0CTL1 &= ~UCSWRST;                           |                                         |

| 07              |                                                 |                                         |

#### Figure 6. Screenshot of Adjusted Firmware

Figure 7. Screenshot With Issue Fixed

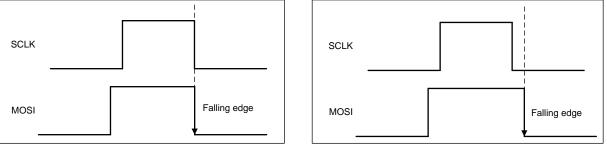

# 1.7 Timing Conditions for MOSI With Respect to S\_CLK

When in SPI mode, MOSI should be able to rise or fall independent of S\_CLK as long as SPI timing requirements are met. However, while in SPI mode, if MOSI has a falling edge before the end of a high period of S\_CLK, then the device treats it as a parallel mode stop condition and does not register the data.

This behavior occurs only when S\_CLK and MOSI are high and the state of MOSI changes from logic high to logic low before the state of S\_CLK change from logic high to logic low (see Figure 8).

#### TRF7960 - SPI With SS\* Mode Errata

#### Issue occurs

Communication is terminated by the parallel mode Stop condition when MOSI data changes during a high SCLK period.

#### Issue does not occur

Issue does not occur

#### Figure 8. Parallel Mode Stop Condition

In use cases where SPI is not naturally synchronized, the workaround is to add software guards to prevent MOSI from changing state before S\_CLK.

Page

# **Revision History**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| <b>O</b> I: | f    |     | 04  | 00471-  | NI       | 07  | 0040 |

|-------------|------|-----|-----|---------|----------|-----|------|

| Changes     | trom | way | 31, | 2017 to | November | 27, | 2018 |

| • | Added Section 1.7, Timing Conditions for MOSI With Respect to S_CLK | 9 |

|---|---------------------------------------------------------------------|---|

|---|---------------------------------------------------------------------|---|

# IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022, Texas Instruments Incorporated