# Application Report

# TRF7970A Firmware Design Hints

Josh Wyatt, Kostas Aslanidis, Juergen Mayer-Zintel

Texas Instruments Embedded RF

#### **ABSTRACT**

This application report is a reference for the firmware developer using TRF7970A in conjunction with a microcontroller (for example, an MSP430™ MCU or ARM®-based MCU).

|        | Contents                                                           |

|--------|--------------------------------------------------------------------|

| 1      | ISO15693 Only – Direct Command (0x14) EOF/TX Next Slot             |

| 2      | Missing IRQ                                                        |

| 3      | Lost IRQ                                                           |

| 4      | Wrong Data Due to Overshoots                                       |

| 5<br>6 | ISO14443A Decoder                                                  |

| 7      | TRF7960, TRF7961, TRF7960A, TRF7970A SPI With SS Special Handling  |

| 8      | TRF7970A MIFARE™ Compatibility                                     |

|        |                                                                    |

|        | List of Figures                                                    |

| 1      | Special Direct Mode (TX REQ1, 0x26, LSB First), RX Reply From Tag) |

| 2      | Entering Special Direct Mode                                       |

| 3      | TX Part (Detail)                                                   |

| 4      | End of TX (Detail)                                                 |

| 5      | RX Part (Entering Direct Mode 1 Detail)                            |

| 6      | RX Part (Detail)                                                   |

|        | List of Tables                                                     |

| 1      | Firmware Hints Reference                                           |

| 2      | Entering Special Direct Mode (Signals)                             |

| 3      | Entering Special Direct Mode (Steps)                               |

| 4      | TX Part (Steps Detail)                                             |

| 5      | End of TX (Steps Detail)                                           |

| 6      | RX Part (Entering Direct Mode 1 Detail Steps)                      |

| 7      | RX Part (Receiving Tag Reply Steps Detail)                         |

| 8      | Known Limitations With Specific Tags                               |

| 9      | TRF7960A Special Functions Register 0x10                           |

| 10     | TRF7970A Special Functions Register 0x10                           |

| 11     | TRF7970A Special Functions Register 0x11                           |

MSP430 is a trademark of Texas Instruments.

ARM is a registered trademark of ARM Ltd.

MIFARE, JCOP, DESFire are trademarks of NXP Semiconductors.

All other trademarks are the property of their respective owners.

### TRF7960, TRF7961, TRF7960A, TRF7970A Firmware Hints

Table 1 lists the firmware design hints that are described in this application report.

**Table 1. Firmware Hints Reference**

|               | Item                                                       | TRF7970A | TRF7960A | TRF7960 | TRF7961 |

|---------------|------------------------------------------------------------|----------|----------|---------|---------|

| 1             | ISO15693 only - Direct command (0x14) 'Transmit next slot' |          |          | ✓       | ✓       |

| 2 Missing IRQ |                                                            | ✓        | ✓        | ✓       | ✓       |

| 3             | Lost IRQ                                                   | ✓        | ✓        | ✓       | ✓       |

| 4             | Wrong data due to "overshoots"                             |          |          | ✓       |         |

| 5             | ISO14443A decoder                                          |          |          | ✓       |         |

| 6             | Tags that do not follow the ISO14443A Layer 4 framing      |          |          | ✓       |         |

| 7             | SPI with SS (see Section 7.5)                              |          | ✓        | ✓       | ✓       |

### 1 ISO15693 Only – Direct Command (0x14) EOF/TX Next Slot

### **Description**

Sending of 'Transmit next slot' direct command (0x14) can happen only once (ISO15693).

#### Workaround

Before sending the 'Transmit next slot' direct command, the 'Reset' direct command must be send. This is only used in ISO15693 Inventory command (with 16 time slots). ISO 15693 'Write Single Block' and 'Lock Block' commands are affected also if the 'Option' bit is set.

### 2 Missing IRQ

### Description

The device does not send (on pin 13) any interrupt requests on certain condition. The chip can go to a state in which the sending of additional interrupts during RX or TX is stopped. This happens when the Stop condition is exactly aligned with the byte boundary on TX data.

### Workaround

The loading and reading of the FIFO should be coded in such a way, that the Stop condition does not fall directly on the TX byte boundary.

#### 3 Lost IRQ

#### Description

Lost IRQ if the end of RX IRQ occurs at the same time that the IRQ register is being read (also see Section 6).

#### Workaround

Add additional checks to retrieve the RX data in case the IRQ is suppressed by a coinciding read operation.

#### 4 Wrong Data Due to Overshoots

### **Description**

The ISO14443A 106-kbps decoder gives wrong data in certain condition. When the analog front end filter overshoots, the digitizer might produce a rising edge on the subcarrier data. If this occurs within a small time-window the decoder will produce false data. This happens extremely rarely and is dependent on the antenna/filter characteristics.

#### Workaround

Switch to PM channel or adjust gain to avoid overshoots in the analog filter.

www.ti.com ISO14443A Decoder

### 5 ISO14443A Decoder

#### **Description**

ISO14443A subcarrier decoded incorrectly – "reading holes".

#### Workaround

Adjust gain setting of main RX channel; repeat reading until correct data results. (This might require additional time.)

### 6 Tags That Do Not Follow ISO14443A Layer 4 Framing

### **Description**

When a transmit frame starts with the code 0x93, 0x95 or 0x97, the reply will not be correctly framed. This happens because the TRF796x devices have an automatic anticollision broken byte framing system that is activated with the 0x93, 0x95 or 0x97 code.

#### Workaround

Use TRF7960 "Direct Mode".

### 7 TRF7960, TRF7961, TRF7960A, TRF7970A SPI With SS Special Handling

### 7.1 SPI With SS Pin Only – No High Impedance

#### Description

Serial interface with SS pin only - interface does not go to high impedance when SS is high. It is not possible to multiplex the serial port interface lines.

#### Workaround

An external 3-state buffer must be used if the chip is connected to a serial bus and the interface lines must be multiplexed.

### 7.2 SPI With SS Pin Only – Direct Commands

### **Description**

Serial interface with SS pin only - the direct commands are not executed if they are the last operation in the SPI communication. In the SPI interface with SS pin the Stop condition clock pulse is missing (compared to the parallel interface and SPI without SS pin). Some operations are relying on this clock and they do not work as expected.

#### Workaround

If a direct command is the last operation in the SPI communication, the SS pins goes high. An additional clock pulse must be sent after this happens.

### 7.3 SPI With SS Pin Only – IRQ Status Bit

#### Description

Serial interface with SS pin only - IRQ status bits are not cleared after the IRQ Status register (0x0C) is read.

#### Workaround

A dummy read must be made after reading the 'IRQ status' register (0x0C). This can be done in noncontinuous or continuous mode. In continuous mode only 8 clock pulses are needed. In noncontinuous mode 16 clock pulses are needed: 8 for address and 8 for data.

### 7.4 SPI With SS Pin Only – No TX if Single Bit in FIFO

### **Description**

Serial interface with SS pin only - the chip does not start with transmission if only 1 byte is loaded to the FIFO.

#### Workaround

The microcontroller has to load an additional byte to the FIFO. The chip will transmit only 1 byte on the TX if the "Number of complete bytes" in the registers 0x1D and 0x1E is 1.

### 7.5 SPI With SS Pin Only – Clock Polarity Change

### Description

DATA\_CLK clock polarity needs to be switched when FIFO read operation (single or continues) is executed. During SPI data transmission MOSI line is valid on rising edge; MISO line is valid on falling edge of data clock signal.

NOTE: Not needed for the TRF7970A

#### Workaround

Firmware must switch clock polarity between FIFO Write and Read.

### 7.6 SPI With SS Pin Only – IRQ Status Register Reset

### Description

The IRQ Status Register (0x0C) is not automatically cleared after reading.

#### Workaround

Dummy register read is required to clear the content of the IRQ Status Register and drive the IRQ line to low.

### 7.7 SPI With SS Pin Only – Single Byte Direct Commands

#### Description

All single byte direct commands need an additional CLK cycle to work.

#### Workaround

All direct Command functions need to have an additional DATA\_CLK cycle before Slave Select I line goes high.

### 7.8 SPI With SS Pin Only – Some Registers Do Not Take Default Values

#### Description

Some of the registers do not take the default values when the appropriate protocol is chosen in the ISO Control Register.

### Workaround

Manually program the default settings into the TRF796x during initialization.

### 8 TRF7970A MIFARE™ Compatibility

For communication with MIFARE tags special procedures have to be used. This is because the MIFARE protocol encrypts parity bits and the CRC bytes.

#### **Transmit**

For transmitting data from the TRF7970A to a MIFARE tag Special Direct Mode must be used.

When in Special Direct Mode the TRF7970A sends a data clock to the MCU on I/O\_5 (pin 22) and the Microcontroller controls the TRF7970A through I/O\_2 (TX enable) and I/O\_3 (data).

Detailed procedure is described below.

#### Receive

The TRF7970A can receive MIFARE coded data in two ways.

- By using Direct Mode 1 where the decoded data and bit clock are available directly on I/O\_6 and I/O\_5 pins. Detailed procedure is described below.

- By using normal receive through FIFO. In this case bit 7 in register 0x01 must be set to a 1 to disable CRC checking and bit 5 in register 0x10 must be set to a 1 to disable parity checking. The 2 bytes CRC are stored in the FIFO, the parity bits are discarded.

To enable receiving 4-bit long packets bit 2 in register 0x10 must be set to a 1 and bit 7 in register 0x01 must be set to a 1 to disable CRC checking.

### 8.1 TX in Special Direct Mode, RX in Direct Mode 1

### **Procedure**

- 1. Set TX\_Data (I/O\_3) low (required for sending correct SOF when entering SDM)

- 2. Write register 0x0D with 0x3E (Disable No Response IRQ)

- 3. Write register 0x01 with 0x08 (ISO14443A at 106 kbps)

- 4. Write register 0x00 with 0x21 (enable TX/RX)

- 5. Send command 0x16 to disable decoders (for TRF7970A, command is 0x96)

- 6. Read register 0x0C (to clear IRQ)

- 7. Write register 0x10 with 0x08 (enable Special Direct Mode)

- 8. Write register 0x00 with 0x61 (enter Special Direct Mode)

- 9. Send 8 clock cycles to enter Special Direct Mode, with no stop condition (SS pin stays low)

- 10. I/O\_2 goes high and enables TX, bit clock on I/O\_5, data sampled on I/O\_3 falling edge

- 11. I/O\_2 goes low and disables TX

- 12. Stop condition issued on SPI (SS line brought high)

- 13. Reply from tag received in Direct Mode 1.

### 8.2 Screen Shots

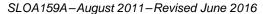

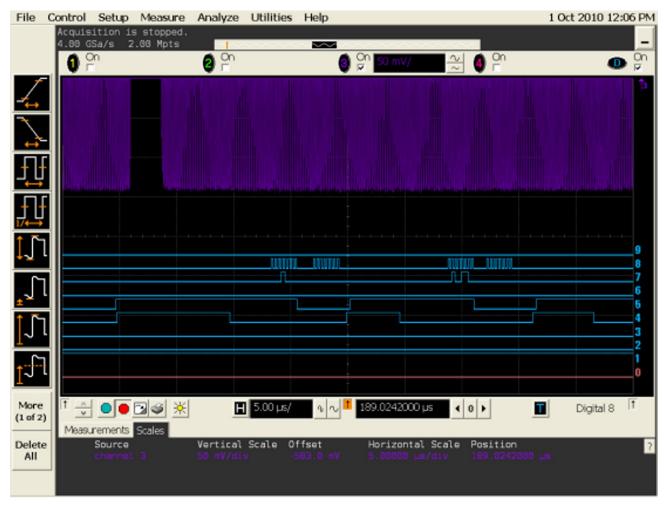

NOTE: In Figure 1, Special Direct Mode is called Direct Mode 2.

Table 2 shows the signals for Figure 1.

Figure 1. Special Direct Mode (TX REQ1, 0x26, LSB First), RX Reply From Tag)

**Table 2. Entering Special Direct Mode (Signals)**

| Test Point               | Signals                  |

|--------------------------|--------------------------|

| Channel 1 (Oscilloscope) | RF Field                 |

| D9                       | IRQ                      |

| D8                       | DATA_CLK                 |

| D7                       | I/O_7 (MOSI)             |

| D6                       | I/O_6 (MISO)             |

| D5                       | I/O_5 (bit clock)        |

| D4                       | I/O_4 (slave select, SS) |

| D3                       | I/O_3 (TX data)          |

| D2                       | I/O_2 (TX enable)        |

| D1                       | I/O_1                    |

| D0                       | I/O_0                    |

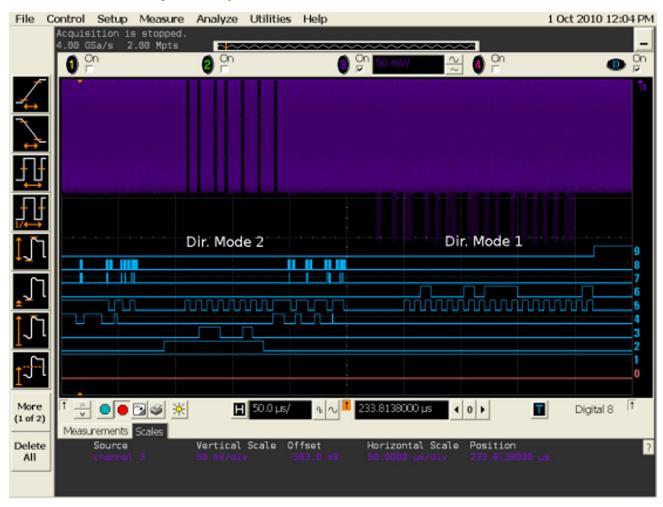

Table 3 shows the steps for Figure 2.

Table 3. Entering Special Direct Mode (Steps)

| Step Number | Instruction                                                                                                             |  |  |

|-------------|-------------------------------------------------------------------------------------------------------------------------|--|--|

| 1           | Read register 0x0C (to clear IRQ if necessary)                                                                          |  |  |

| 2           | Write register 0x10 with 0x08 (enable Special Direct Mode)                                                              |  |  |

| 3           | Write register 0x00 with 0x61 (enter Direct Mode)                                                                       |  |  |

| 4           | Send 8 clock cycles to enter Direct Mode, with no stop condition (SS pin stays low for duration of Special Direct Mode) |  |  |

Figure 2. Entering Special Direct Mode

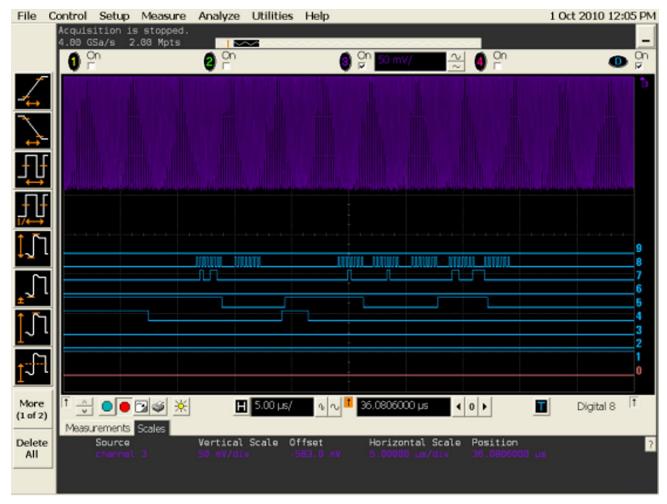

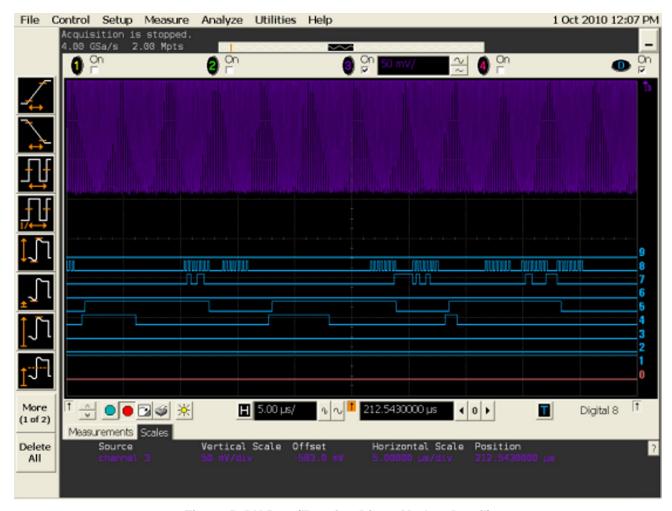

Table 4 shows the steps for Figure 3.

**Table 4. TX Part (Steps Detail)**

| Step Number | Instruction                                                                             |

|-------------|-----------------------------------------------------------------------------------------|

| 1           | I/O_2 goes high, enabling TX, bit clock on I/O_5, data on I/O_3 sampled on falling edge |

| 2           | I/O_2 goes low, disabling TX                                                            |

| 3           | Stop Condition (SS line brought high)                                                   |

Figure 3. TX Part (Detail)

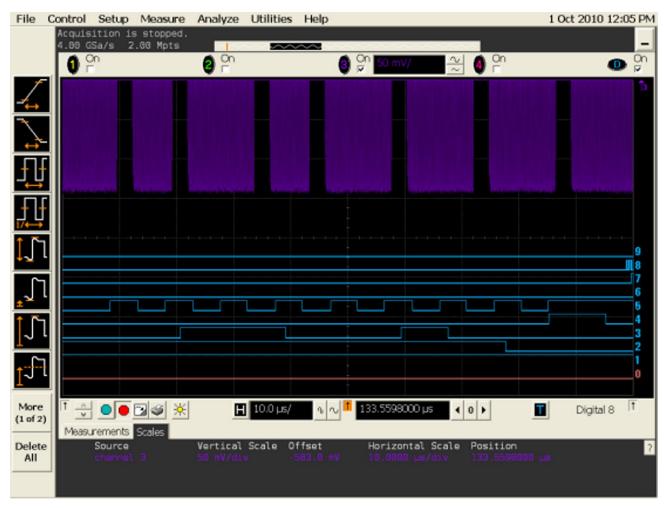

Table 5 shows the steps for Figure 4.

Table 5. End of TX (Steps Detail)

| Step Number | Instruction                                                  |  |

|-------------|--------------------------------------------------------------|--|

| 1           | Write register 0x10 with 0x00 (disables Special Direct Mode) |  |

| 2           | Read register 0x0C (clearing any IRQ)                        |  |

Figure 4. End of TX (Detail)

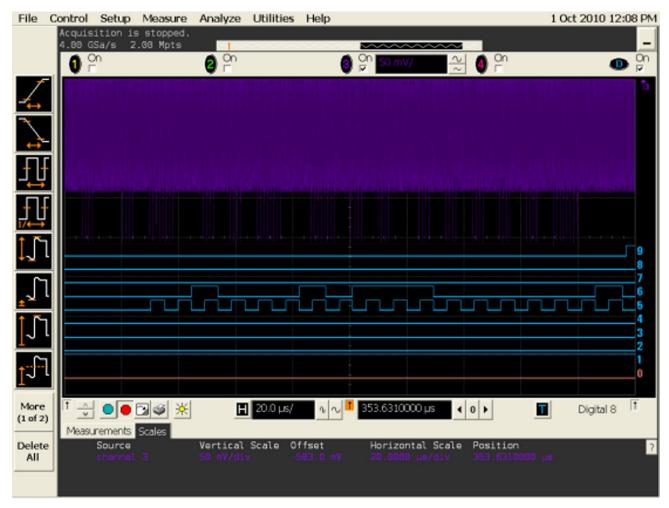

Table 6 shows the steps for Figure 5.

Table 6. RX Part (Entering Direct Mode 1 Detail Steps)

| Step Number | Instruction                                                                                                       |  |

|-------------|-------------------------------------------------------------------------------------------------------------------|--|

| 1           | Read register 0x0C (to clear IRQ if necessary)                                                                    |  |

| 2           | Write register 0x01 with 0x48 (enable Direct Mode 1)                                                              |  |

| 3           | Write register 0x00 with 0x61 (enter Direct Mode)                                                                 |  |

| 4           | Send 8 clock cycles to enter Direct Mode, with no stop condition (SS pin stays low for duration of Direct Mode 1) |  |

Figure 5. RX Part (Entering Direct Mode 1 Detail)

Table 7 shows the steps for Figure 6.

Table 7. RX Part (Receiving Tag Reply Steps Detail)

| Step Number | Instruction                          |

|-------------|--------------------------------------|

| 1           | Receiving tag reply in Direct Mode 1 |

| 2           | IRQ goes high at end of RX           |

Figure 6. RX Part (Detail)

# **Table 8. Known Limitations With Specific Tags**

| Tag | Tag Type                                              | Problem                                                                                                                                                                                                                                                | Workaround                                                                                                                                                                     |

|-----|-------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| T1  | MIFARE Ultralight                                     | The 4-bit ACK and NAK reply can not be decoded with the integrated decoder/framer system. The 4-bit ACK is not according the standard ISO 14443A, so the internal data framing reports an error and needs to be by-passed.                             | Direct mode                                                                                                                                                                    |

| T2  | MIFARE classic (standard)                             | The parity check fails with the encrypted frames as the MIFARE® standard encrypts also the parity bit.                                                                                                                                                 | Direct mode                                                                                                                                                                    |

| Т3  | Tags that do not follow the ISO14443A Layer 4 framing | When a transmit frame starts with the code 0x93, 0x95 or 0x97, the reply will not be correctly framed. This happens because the TRF796x devices have an automatic ANTICOLLISION broken byte framer that is activated with the 0x93, 0x95 or 0x97 code. | Direct mode                                                                                                                                                                    |

| T4  | Cryptographic cards (for example, JCOP™ and DESFire™) | Using a cryptographic card (JCOP or DESFire) at close proximity (<1 cm) can cause a wrong collision error detection.                                                                                                                                   | The reason is the 'calculation noise' emitted by the card, which can be suppressed if the gain is drastically reduced. Use additional gain reduction enabled by test register. |

| T5  | ISO 15693 cards requiring a slot delimiter (EOF)      | There are ISO15693 cads on the market requiring a slot delimiter (EOF).                                                                                                                                                                                | A dedicated MCU timer must be used to generate the 37.76-µs timing grid.                                                                                                       |

### Table 9. TRF7960A Special Functions Register 0x10

| Bit | Bit Name       | Function                                                                                                 | Comment                                                                              |

|-----|----------------|----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|

| B7  |                | Reserved                                                                                                 | Reserved                                                                             |

| B6  |                | Reserved                                                                                                 | Reserved                                                                             |

| B5  |                | Reserved                                                                                                 | Reserved                                                                             |

| B4  | next_slot_37us | Sets the time grid for next slot command in ISO15693                                                     | 0 = 18.88 μs<br>1 = 37.77 μ s                                                        |

| В3  |                | Reserved                                                                                                 | Reserved                                                                             |

| B2  | 4_bit_RX       | Enable 4-bit replay (ACK, NACK) used by some cards; for example, MIFARE Ultralight                       | 0 = normal receive<br>1 = 4-bit receive                                              |

| B1  | 14_anticoll    | Disable anticollision frames for ISO14443A (this bit should be set to 1 after anticollision is finished) | 0 = Anticollision framing (0x93, 0x95, 0x97)<br>1 = Normal framing (no broken bytes) |

| В0  | col_7_6        | Selects the number of subcarrier pulses that trigger a collision error in ISO14443A at 106 kbps          | 0 = 7 subcarrier pulses<br>1 = 6 subcarrier pulses                                   |

### Table 10. TRF7970A Special Functions Register 0x10

| Bit | Bit Name       | Function                                                                                                 | Comment                                                                                                                            |

|-----|----------------|----------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| B7  |                | Reserved                                                                                                 | Reserved                                                                                                                           |

| B6  |                | Reserved                                                                                                 | Reserved                                                                                                                           |

| B5  | par43          | Disables parity checking for ISO14443A                                                                   |                                                                                                                                    |

| B4  | next_slot_37us | Sets the time grid for next slot command in ISO15693                                                     | 0 = 18.88 μs<br>1 = 37.77 μs                                                                                                       |

| ВЗ  | dir_mode2      | Bit stream transmit for MIFARE at 106 kbps                                                               | Enables direct mode for transmitting ISO14443A data, bypassing the FIFO and feeding the data bit stream directly onto the encoder. |

| B2  | 4_bit_RX       | Enable 4-bit replay (ACK, NACK) used by some cards (for example, MIFARE Ultralight)                      | 0 = normal receive<br>1 = 4-bit receive                                                                                            |

| B1  | 14_anticoll    | Disable anticollision frames for ISO14443A (this bit should be set to 1 after anticollision is finished) | 0 = Anticollision framing (0x93, 0x95, 0x97)<br>1 = Normal framing (no broken bytes)                                               |

| В0  | col_7_6        | Selects the number of subcarrier pulses that trigger collision error in ISO14443A at 106 kbps            | 0 = 7 subcarrier pulses<br>1 = 6 subcarrier pulses                                                                                 |

# Table 11. TRF7970A Special Functions Register 0x11

| Bit | Bit Name | Function                                                              | Comment                                                                              |

|-----|----------|-----------------------------------------------------------------------|--------------------------------------------------------------------------------------|

| B7  |          | Reserved                                                              | Reserved                                                                             |

| B6  |          | Reserved                                                              | Reserved                                                                             |

| B5  |          | Reserved                                                              | Reserved                                                                             |

| B4  |          | Reserved                                                              | Reserved                                                                             |

| В3  |          | Reserved                                                              | Reserved                                                                             |

| B2  |          | Reserved                                                              | Reserved                                                                             |

| B1  |          | Reserved                                                              | Reserved                                                                             |

| В0  | irg_srx  | Copy of the RX start signal (Bit 6) of the IRQ Status Register (0x0C) | Signals the RX SOF was received and the RX is in progress. IRQ when RX is completed. |

Revision History www.ti.com

# **Revision History**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| Changes from August 4, 2011 to June 30, 2016 |                                                                                    |   |

|----------------------------------------------|------------------------------------------------------------------------------------|---|

| •                                            | Added steps 1 and 2 in Section 8.1, TX in Special Direct Mode, RX in Direct Mode 1 | 5 |

#### IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

| Products | Applications |

|----------|--------------|

| 1100000  | Applications |

Audio www.ti.com/audio Automotive and Transportation www.ti.com/automotive **Amplifiers** amplifier.ti.com Communications and Telecom www.ti.com/communications **Data Converters** dataconverter.ti.com Computers and Peripherals www.ti.com/computers **DLP® Products** www.dlp.com Consumer Electronics www.ti.com/consumer-apps DSP dsp.ti.com **Energy and Lighting** www.ti.com/energy Clocks and Timers www.ti.com/clocks Industrial www.ti.com/industrial Interface interface.ti.com Medical www.ti.com/medical Logic Security www.ti.com/security logic.ti.com

Power Mgmt power.ti.com Space, Avionics and Defense www.ti.com/space-avionics-defense

Microcontrollers microcontroller.ti.com Video and Imaging www.ti.com/video

RFID www.ti-rfid.com

OMAP Applications Processors www.ti.com/omap TI E2E Community e2e.ti.com

Wireless Connectivity www.ti.com/wirelessconnectivity