# **APPLICATION NOTE U-157**

Larry Spaziani Applications Engineer Unitrode Corporation

# FUELING THE MEGAPROCESSOR -A DC/DC CONVERTER DESIGN REVIEW FEATURING THE UC3886 AND UC3910

# FUELING THE MEGAPROCESSOR - A DC/DC CONVERTER DESIGN REVIEW FEATURING THE UC3886 AND UC3910

by Larry Spaziani Applications Engineer

# ABSTRACT

This application note provides a detailed account of design tradeoffs and procedures for the development of a Voltage Regulator Module (VRM) for the Intel Pentium<sup>®</sup>Pro processor. This voltage regulator features Unitrode's UC3886 Average Current Mode PWM Controller and UC3910 4-BIT DAC and Voltage Monitor ICs configured in a Buck Regulator. Test results and waveforms are provided which show how the VRM power supply meets stringent requirements imposed by Intel.

# INTRODUCTION

Intel's Pentium<sup>®</sup>Pro power system specification demonstrates the industry trend to operate at lower voltages and at higher currents, with tight regulation and fast transient response. Meeting these requirements demands the most of both the power stage and the control system of the power supply. Unitrode's UC3886 and UC3910 are specifically designed for optimizing the control loop, the dynamic response and the DC accuracy required by the Pentium<sup>®</sup>Pro. The power stage inductor and capacitors are critical as well in meeting the extremely tight voltage regulation during a Pentium<sup>®</sup>Pro load transient.

This application note will detail the design of a complete VRM power supply. This design review will detail the critical VRM specifications, power supply architecture tradeoffs, power stage design details and equations and finally design specifics used to configure the UC3886 and UC3910. The complete current and voltage loops will then be closed, and performance results of the power supply will be shown.

This design review will reveal the many advantages of using the UC3886 and UC3910, which include:

- Direct output NMOS drive, eliminating the need for creating high voltages and allowing the use of an efficient N-Channel MOSFET.

- High DC accuracy negates the need for voltage trimming and insures the overall regulation will be met.

- Direct interface with INTEL's PENTIUM<sup>™</sup> PRO VID programming codes.

- The UC3910's DAC and unique voltage monitoring architecture directly replaces discrete components including a precision reference, a DAC, complicated resistive networks, multiple window comparators and an SCR Driver.

- Accurate and true "square-knee" current limiting eliminates the need to over-design the power components for operation in an indefinite short circuit.

- Optimization of the loop performance due to large signal changes due to transient load-ing effects.

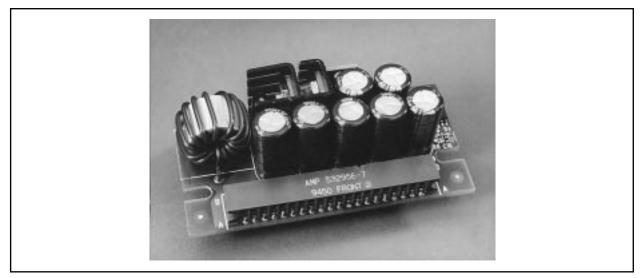

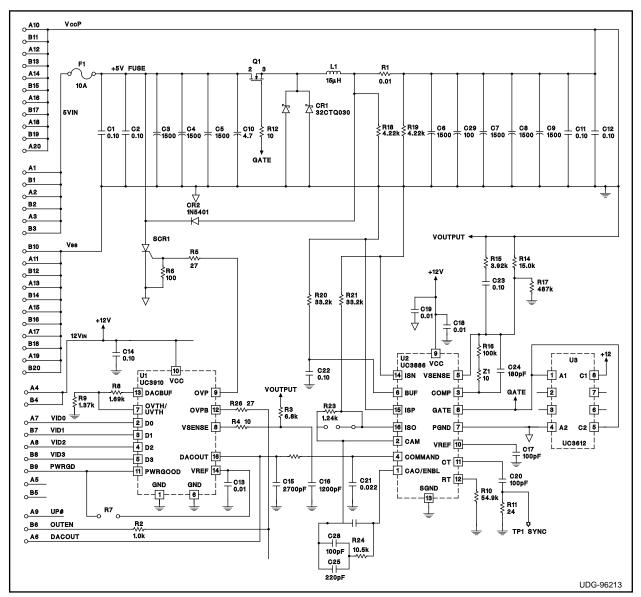

The Unitrode VRM demonstration kit is shown in Figure 1. The VRM's schematic is shown in Figure 2 and the parts are described in Table 1.

Figure 1. Unitrode's VRM Demonstration Kit

Figure 2. Schematic Diagram

# **APPLICATION NOTE**

Input Voltages:

Output Voltage:

Regulation:

Load Transient:

Minimum Current: 0.3A

Maximum Current: 11.2A

#### POWER SUPPLY SPECIFICATIONS

The requirements for the DC/DC converter which will provide power to Intel Pentium<sup>®</sup>Pro are contained in Intel's application note AP-523 [1], Section 10. These power supply requirements consist of required specifications, expected specifications and design guidelines, some of which are summarized below.

5.00V ±5%

12.00V ±5%

ripple/noise.

rate  $\leq$ 30.3A/µs.

Variable from 2.4V to 3.4V programmable per INTEL VID codes, 100mV increments.

±5% Including initial tolerance,

setpoints, drift, transients and

Minimum to maximum or maximum to minimum current at a

| Input Current Rate: ±0.1A/µs | maximum | during | а |

|------------------------------|---------|--------|---|

| load trans                   | ient.   |        |   |

| Power-Good:    | Open Collector output LOW signal when the output voltage is not within $\pm 10\%$ of nominal. |  |

|----------------|-----------------------------------------------------------------------------------------------|--|

| Output Enable: | Open Collector input signal with<br>a LOW state disabling the<br>DC/DC converter.             |  |

| Ripple/Noise:  | ±1% to 20MHz.                                                                                 |  |

| Overshoot:     | ≤10% above the initial setpoint<br>at application or removal of input<br>power.               |  |

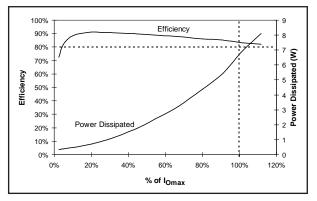

| Efficiency:    | ≥80% at maximum current,                                                                      |  |

cy: ≥80% at maximum current, ≥40% at minimum current

- Temperature:  $+10^{\circ}$ C to  $+60^{\circ}$ C,  $\geq 100$  LFM air cooling along connector axis.

- Over Voltage: Self shut down when the output exceeds 10% to 20% of nominal.

#### TABLE 1 - PENTIUM®PRO VRM DEMONSTRATION KIT BILL OF MATERIALS

| REF.DES. | UNITRODE PENTIUM®PRO VRM DEMONS                      | PACKAGE            | NOTES |

|----------|------------------------------------------------------|--------------------|-------|

| U1       | Unitrode UC3910DP 4-BIT DAC and Voltage Monitor      | SOIC-16            |       |

| U2       | Unitrode UC3886DP ACM PWM Controller                 | SOIC-16            |       |

| U3       | Unitrode UC3612DP Dual Schottky Diode                | SOIC-8             |       |

| C01      | 0.10µF Ceramic                                       | 1206 SMD           |       |

| C02      | 0.10µF Ceramic                                       | 1206 SMD           |       |

| C03      | Sanyo 6MV1500GX, 1500µF, 6.3V, Aluminum Electrolytic | 10x20mm Radial Can |       |

| C04      | Sanyo 6MV1500GX, 1500µF, 6.3V, Aluminum Electrolytic | 10x20mm Radial Can |       |

| C05      | Sanyo 6MV1500GX, 1500µF, 6.3V, Aluminum Electrolytic | 10x20mm Radial Can |       |

| C06      | Sanyo 6MV1500GX, 1500µF, 6.3V, Aluminum Electrolytic | 10x20mm Radial Can |       |

| C07      | Sanyo 6MV1500GX, 1500µF, 6.3V, Aluminum Electrolytic | 10x20mm Radial Can |       |

| C08      | Sanyo 6MV1500GX, 1500µF, 6.3V, Aluminum Electrolytic | 10x20mm Radial Can |       |

| C09      | Sanyo 6MV1500GX, 1500µF, 6.3V, Aluminum Electrolytic | 10x20mm Radial Can |       |

| C10      | Sprague/Vishay 595D475X0016A2B, 4.7µF 16V Tantalum   | SPRAGUE Size A     |       |

| C11      | 0.10µF Ceramic                                       | 1206 SMD           |       |

| C12      | 0.10µF Ceramic                                       | 1206 SMD           |       |

| C13      | 0.10µF Ceramic                                       | 1206 SMD           |       |

| C14      | 0.10µF Ceramic                                       | 1206 SMD           |       |

| C15      | 2700pF Ceramic                                       | 0603 SMD           |       |

| C16      | 1200pF Ceramic                                       | 0603 SMD           |       |

| C17      | 1000pF Ceramic                                       | 0603 SMD           |       |

| C18      | 0.01µF Ceramic                                       | 0603 SMD           |       |

| C19      | 0.10µF Ceramic                                       | 1206 SMD           |       |

| C20      | 100pF NPO Ceramic                                    | 0603 SMD           |       |

| C21      | 0.022uF Ceramic                                      | 0603 SMD           |       |

| C22      | 0.10µF Ceramic                                       | 1206 SMD           |       |

| C23      | 0.10µF Ceramic                                       | 1206 SMD           |       |

Short Circuit:

Continuous short circuit modewithout damage or overstress to the unit.

| REF.DES. | DESCRIPTION                                              | PACKAGE           | NOTES |

|----------|----------------------------------------------------------|-------------------|-------|

| C24      | 180pF NPO Ceramic                                        | 0603 SMD          |       |

| C25      | 220pF NPO Ceramic                                        | 0603 SMD          |       |

| C26      | NOT USED                                                 | 0603 SMD1         |       |

| C27      | 180pF NPO Ceramic                                        | 0603 SMD          |       |

| C28      | 1000pF NPO Ceramic                                       | 0805 SMD          |       |

| C29      | Sprague/Vishay 593D107X9010D2, 100µF, 6.3V Tantalum      | EIA Size D SMD    |       |

| SCR1     | Motorola MCR12D, 12A SCR                                 | TO-220AB          | 2     |

| CR1      | International Rectifier 32CTQ030 30V, 30A Schottky Diode | TO-220AB          |       |

| CR1-HS   | AAVID 577002 TO-220 Heat Sink                            |                   |       |

| CR2      | 1N5401CT, 3A 100V Diode                                  | DO-201AD          | 2     |

| F1       | Littlefuse R451010, 10A Fast Blow                        | SMD Square        | 2     |

| J1       | AMP 532956-7 40 Pin Connector                            | •                 |       |

| L1       | Coilcraft S6030-B, 10µH to 20µH                          | Radial Toroid     |       |

| Q1       | International Rectifier IRL3103, 30V, 56A                | TO-220AB          |       |

| Q1-HS    | AAVID 577202 TO-220 Heat Sink                            |                   |       |

| R01      | Dale/Vishay WSR-2 0.01W 1%                               | SMD Power Package | 3     |

| R02      | 1.00kW, 1%, 1/16 Watt                                    | 0603 SMD          |       |

| R03      | 6.8kW, 5%, 1/16 Watt                                     | 0603 SMD          |       |

| R04      | 10W, 5%, 1/16 Watt                                       | 0603 SMD          | 4     |

| R05      | 27W, 5%, 1/16 Watt                                       | 0603 SMD          | 2     |

| R06      | 100W, 5%, 1/16 Watt                                      | 0603 SMD          | 2     |

| R07      | NOT USED                                                 | 0603 SMD          | 5     |

| R08      | 1.69kW, 1%, 1/16 Watt                                    | 0603 SMD          |       |

| R09      | 1.37kW, 1%, 1/16 Watt                                    | 0603 SMD          |       |

| R10      | 54.9kW, 1%, 1/16 Watt                                    | 0603 SMD          |       |

| R11      | 24W, 5%, 1/16 Watt                                       | 0603 SMD          | 8     |

| R12      | 10W, 5%, 1/16 Watt                                       | 0603 SMD          |       |

| R13      | 10kW, 5%, 1/16 Watt                                      | 0603 SMD          |       |

| R14      | 15.0kW, 1%, 1/16 Watt                                    | 0603 SMD          |       |

| R15      | 3.92kW, 1%, 1/16 Watt                                    | 0603 SMD          |       |

| R16      | 100kW, 1%, 1/16 Watt                                     | 0603 SMD          |       |

| R17      | 487kW, 1%, 1/16 Watt                                     | 0603 SMD          |       |

| R18      | 4.22kW, 1%, 1/16 Watt                                    | 0603 SMD          |       |

| R19      | 4.22kW, 1%, 1/16 Watt                                    | 0603 SMD          |       |

| R20      | 33.2kW, 1%, 1/16 Watt                                    | 0603 SMD          |       |

| R21      | 33.2kW, 1%, 1/16 Watt                                    | 0603 SMD          |       |

| R22      | NOT USED                                                 | 0603 SMD          | 1     |

| R23      | 1.24kW, 1%, 1/16 Watt                                    | 0603 SMD          |       |

| R24      | 10.5kW, 1%, 1/16 Watt                                    | 0603 SMD          |       |

| R25      | NOT USED                                                 | 0603 SMD          |       |

| R26      | 27W, 5%, 1/16 Watt                                       | 0603 SMD          | 6     |

| Z1       | 10W, 5%, 1/16 Watt                                       | 0603 SMD          | 7     |

TABLE 1 - PENTIUM®PRO VRM DEMONSTRATION KIT BILL OF MATERIALS (cont.)

Notes: 1) R22 and C26 are not required. These parts can be used for alternative compensation schemes. 2) These parts are related to the overvoltage protection SCR firing circuit.

3) Simulate a "4 wire" connection using PCB etch for best results.

4) R04 used for debug purposes. R04 is not required in a production unit.

5) R07 can be used to pull up the PWRGOOD signal internally to the VRM

6) R26 is not required for proper operation. R26 is used as a "jumper".

7) Z1 used for debug purposes. Z1 can be used for alternative compensation, or shorted in a production unit.

8) R24 is not required for production unless synchronization is used.

# **POWER CONVERSION ARCHITECTURE**

### **Topology: Single Switch Buck Regulator**

Power conversion from either +5 volts or +12 volts to the lower voltages required by the Pentium<sup>®</sup>Pro can be accomplished by either a linear regulator or by a myriad of switching converter topologies. Linear regulation is not appropriate because of its inherently poor efficiency. Transformer coupled switching topologies are not required, and not desired, because of the common input and output grounding system. Either a single switch or a synchronous rectifier (two switch) buck regulator are the most appropriate choices for this application. Higher efficiency can be achieved with synchronous rectification, but is not required in this application because the efficiency goal is 80%. The added cost and complexity of a second N-MOSFET is therefore not justified.

# Input Voltage: +5 Volts Provides Power, +12 Volts provides Bias and Drive

Either the +5 volt or the +12 volt power bus can be used for this single switch Buck regulator. An Nchannel MOSFET is chosen as the switch because of the efficiency of low  $R_{DSon}$  N-MOSFETs. The +12 volt bus can be used to drive the N-MOSFET in a +5V input Buck regulator, whereas a +12V input Buck regulator would require a higher voltage (17-20 volts) to provide drive to the switch. Several other considerations are made in choosing the input voltage, including:

- +12V input would require a larger output inductor for a given ripple current.

- +5V input operates at higher duty cycles, reducing power in the freewheeling diode, whereas +12V input operates at lower duty cycles, reducing power in the MOSFET.

- The combined power dissipated of the freewheeling diode plus the MOSFET is less with a +5V input than with a +12V input.

- +5V typically has better power distribution on a motherboard, and within a system, even considering the higher DC currents involved when converting power from +5V.

- The input capacitors will see the same RMS switching current at either voltage.

- +5V has six dedicated input pins whereas +12V has only two. Using +5V as an input voltage will result in fewer amps/pin and a lower impedance path to the source.

- +12V busses can often withstand larger voltage deviations due to the loading effects of the Pentium<sup>®</sup>Pro.

# Control Method - Average Current Mode Control Using the UC3886

Average Current Mode control, as implemented with the UC3886, offers the advantages of optimization of the control loop, very fast amplifiers for a fast transient response, and accurate current limiting. Application Note U-140 [2] discusses the many advantages of Average Current Mode control over both Peak Current Mode control and Voltage Mode control.

# Switching Frequency - 200kHz

Several considerations in choosing 200kHz as the switching frequency are:

- 1. An upper bound on frequency is derived from the gain required by the UC3886 Average Current Mode control current sense amplifier. This upper bound will be shown to be 312kHz.

- 2. A high switching frequency is desired for

- Minimum output inductor size

- Maximum control loop bandwidth

- 3. A low switching frequency is desired for

- Keeping switching losses low, although switching losses in the semiconductors is not a significant factor in this application because the input voltage (+5V) is very low.

- Reducing noise when using a 2-layer printed circuit board.

- 4. The use of Aluminum Electrolytic capacitors is favored for both input and output capacitors in this application because of the height allowed, their high Capacitance-to-ESR and Capacitance-to-ESL ratios and their ripple current capabilities. Surveying several suppliers of Aluminum Electrolytic capacitors revealed that they have significantly low impedance and optimal ripple current handling at 100kHz to 200kHz, where ESR is minimal.

# POWER STAGE COMPONENT SELECTION

The power stage components consist of the input and output capacitors, switch, freewheeling diode, output inductor and sense resistor, and are chosen to be leaded devices for the most part because of the height allowed in this design. The semiconductors are first chosen to meet a full load efficiency goal of 80% and to provide reliable operation at full load. The output inductor is then chosen to provide low output current ripple into the capacitors and for continuous mode operation of the

# APPLICATION NOTE

Buck regulator. The output capacitors are chosen to provide an extremely low output impedance for low voltage ripple and low voltage droop during and output load transient. Finally, the input capacitors are chosen to handle the high level of ripple current demanded by the Buck regulator and to heavily filter the input voltage from both high and low load transients.

#### Efficiency/Power Dissipation Budget

The desired efficiency goal of  $\geq$ 80% at full load operation will govern how many of the power stage components are selected. Efficiency goals are set at a nominal input voltage of +5.00V, an output voltage of 3.1V, +25°C ambient temperature and at a maximum load current of 11.2A.

The nominal output power of the power supply is equal to  $3.1V \cdot 11.2A = 34.72$  Watts. From the desired efficiency, the input power at full load is

$$P_{IN} = \frac{P_{OUT}}{0.8} = \frac{34.72W}{0.8} = 43.4$$

Watts

The power dissipated is 8.68 Watts, at full load. An example efficiency budget is shown in Table 2.

#### **Power Stage Component Design Details**

#### Freewheeling Diode: CR1

International Rectifier 32CTQ030 or equivalent, 2 legs paralleled

$V_{F} \approx 0.35 V @ T_{J} = 115^{\circ}C$

$T_{Jmax} = 150^{\circ}C$

Heat Sink = AAVID P/N 577002 or equivalent

Low voltage schottky technology is chosen to maximize the efficiency of the power supply, based on its lower forward voltage and lack of reverse recovery losses.

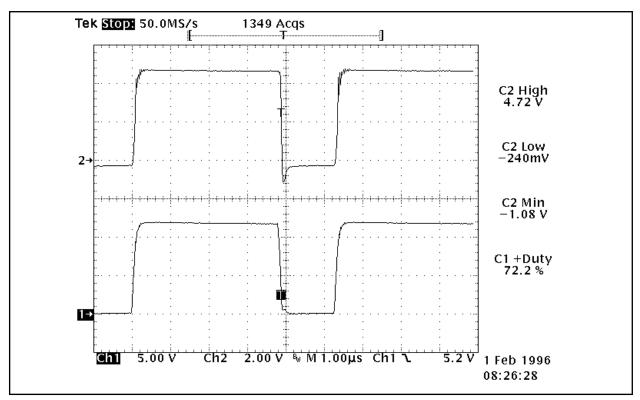

The operating duty cycle for this Buck converter is derived based on the equation<sup>3</sup>

$$\mathsf{D} = \frac{\mathsf{V}_{\mathsf{O}} + \mathsf{I}_{\mathsf{O}} \bullet (\mathsf{R}_{\mathsf{SENSE}} + \mathsf{R}_{\mathsf{LOUT}}) + \mathsf{V}_{\mathsf{F}}}{\mathsf{V}_{\mathsf{IN}} - (\mathsf{I}_{\mathsf{O}} \bullet \mathsf{R}_{\mathsf{DSon}}) + \mathsf{V}_{\mathsf{F}}}$$

Likewise, the short circuit operating duty cycle is

| ~   | NOD  | b)   |

|-----|------|------|

|     | iven | 1.14 |

| . 9 |      | ~ ,  |

| 9                                                                                                        |                                         |  |  |

|----------------------------------------------------------------------------------------------------------|-----------------------------------------|--|--|

| $D_{\text{SENSE}} = 0.0V + I_{\text{SC}} \cdot (R_{\text{SENSE}} + R_{\text{LOUT}}) + V_{\text{F}}$      |                                         |  |  |

| $D_{SC} = \frac{V_{IN} - (I_{SC} \bullet R_{DSon}) + V_{F}}{V_{IN} - (I_{SC} \bullet R_{DSon}) + V_{F}}$ |                                         |  |  |

|                                                                                                          |                                         |  |  |

| Given R <sub>SENSE</sub>                                                                                 | = 0.01                                  |  |  |

| R <sub>LOUT</sub>                                                                                        | = 0.012 at 25°C,                        |  |  |

|                                                                                                          | full load current                       |  |  |

| V <sub>F</sub>                                                                                           | = 0.35V at full load,                   |  |  |

|                                                                                                          | 0.25 at minimum load                    |  |  |

| I <sub>SC</sub>                                                                                          | = 12.5A Nominal Short                   |  |  |

|                                                                                                          | Circuit Current                         |  |  |

| V <sub>IN</sub>                                                                                          | = 5.00V Nominal                         |  |  |

| R <sub>DSon</sub>                                                                                        | = 0.025 at 110°C                        |  |  |

| Vo                                                                                                       | = 3.10V Nominal                         |  |  |

| Then typical duty of                                                                                     | cycles will be approximately:           |  |  |

| Operating:                                                                                               | ≈ 73% at Full load, 25°C T <sub>A</sub> |  |  |

≈ 73% at Full load, 25°C  $I_A$ ≈ 64% at minimum load, 25°C  $T_A$

The maximum operating power dissipation at the diode's maximum operating junction temperature of 110°C is given by

$$P_{Dmax} = V_{F} \bullet I_{Omax} \bullet (1 - D_{max})$$

= 0.35V \cdot 11.2A \cdot (1 - 0.73) = 1.06W

The power dissipation under short circuit conditions, however, is substantially larger

$$P_{Dsc} = V_F \bullet I_{sc} \bullet (1 - D_{sc}) = 0.35V \bullet 1.12A \bullet$$

$$(1 \bullet 0.73) = 1.06W$$

Let  $T_{Jmax} = 115^{\circ}C$  under operating conditions and

150°C under short circuit conditions (Rated T<sub>Jmax</sub> for device)

The two governing formulas defining the heat sink requirements (thermal impedance  $R\theta HS$ ) are

115°C = 50°C + 1.06W • (3.0 + R

$$\theta$$

HS),

R $\theta$ HS = 58°C/W

150°C = 50°C +3.80W • (3.0 + R $\theta$ HS),

R $\theta$ HS = 23.3°C/W

The short circuit operation must be used to choose the heat sink. AAVID P/N 577002 with 100LFM of airflow meets the heat sink requirement of  $\leq$ 23°C/W. Note that the accurate current limit set

| Description                                               | Power Dissipated [W] | Budget Remaining [W] |

|-----------------------------------------------------------|----------------------|----------------------|

| Budgeted Power                                            | <u> </u>             | 8.68                 |

| Estimated 3% Power Distribution (I <sup>2</sup> R) Losses | 1.1                  | 7.58                 |

| Diode Losses                                              | 1.1                  | 6.48                 |

| Sense Resistor                                            | 1.25                 | 5.23                 |

| Output Inductor (I <sup>2</sup> R)                        | 1.3                  | 3.93                 |

| Output Inductor (Core)                                    | 0.1                  | 3.83                 |

| Input Capacitance Ripple Current Losses                   | 0.5                  | 3.33                 |

| UC3886 + UC3910 + Bias loads                              | 0.3                  | 3.03                 |

| MOSFET (Switching, Conduction, Gate Drive)                | 3.03                 | 0.00                 |

#### **TABLE 2 - POWER DISSIPATION BUDGET**

point achieved by the UC3886 allows for a minimum heat sink solution.

#### **MOSFET Switch: Q1**

International Rectifier IRL3103

$R_{DSon} \approx 0.025 \Omega$  Estimated at  $V_{GS} = 7V$ ,  $T_J = 115^{\circ}C$

$Q_G$  (Total Gate Charge)  $\approx 50nC$  estimated at  $V_{GS}$  =7V

Heat Sink  $\approx$  AAVID P/N 577202 or equivalent

From the power budget, the MOSFET should be chosen to achieve the desired losses, including the gate drive losses. Choosing a Logic Level MOSFET or a standard threshold voltage MOSFET is discussed in U-156[3]. This application will utilize a Generation 5 MOSFET from International Rectifier because of its combination of low R<sub>DSon</sub> at low V<sub>GS</sub> as well as rated V<sub>GS</sub> of ±20V.

The power dissipation of the MOSFET consists of 4 components; (a) Gate drive, (b) C<sub>OSS</sub>, (c) Crossover losses, and (d) Conduction losses

a) Gate Drive losses are given by

$P_{GATE} = I_{GATEavg} \bullet V_{GS}$

From the IRL3103 charge curve, with  $V_{GS} = 7$  volts, the required total charge,  $Q_G$ , is estimated to be 50nC. The average current is given by

$$I_{GATEavg} = Q_G \bullet F_S = 50nC \bullet 200kHz = 10mA$$

$$P_{GATE} = 0.010 \text{ Amps} \bullet 12 \text{ Volts} = 0.12 \text{ Watts}$$

b) Coss losses are due to the discharge of the energy stored in the capacitance Coss each cycle, equivalent to

$$P_{COSS} = 0.5 \bullet Coss \bullet (V_{IN} + V_F)^2 \bullet F_S$$

From the IRL3103 capacitance curve, Coss is estimated to be 2400pF. Therefore,

$$P_{COSS} = 0.5 \cdot 2400 \text{pF} \cdot (5.35 \text{V})^2 \cdot 200 \text{kHz}$$

= 0.007W.

c) Crossover (turn-on and turn-off) losses can be estimated as

$$P_{CROSSOVER} = \frac{1}{6} \bullet (V_{IN} + V_F) \bullet I_O \bullet \frac{T_{RISE/FALL}}{T_S}$$

where  $T_{RISE/FALL}$  is the MOSFET current rise and fall time, estimated to be approximately 150ns, and  $T_S$  is the switching period. This loss occurs once at turn-on, and once at turn-off, and therefore, for this application

$$P_{CROSSOVER} = 2 \cdot \frac{1}{6} \cdot 5.35V \cdot 11.2A \cdot \frac{150ns}{5\mu s}$$

$$= 0.6 \text{ Watts}$$

d) Conduction losses are determined by

$$\mathsf{P}_{\mathsf{COND}} = \mathsf{I}_{\mathsf{O}^2} \bullet \mathsf{R}_{\mathsf{DSon}} \bullet \mathsf{D}_{\mathsf{MAX}}$$

and are worst at the maximum operating junction temperature, where  $R_{DSon}$  is highest. For the IRL3103, this loss is

$$P_{COND} = 11.2^2 \cdot 0.025\Omega \cdot 0.73 = 2.29$$

Watts

The MOSFET heat sink requirements are determined from

$$115^{\circ}C = 50^{\circ}C + 3.02W \bullet (2.0 + R_{\theta}HS),$$

$R_{\theta}HS = 19.5^{\circ}C/W$

AAVID P/N 577202 with 100LFM of airflow provides  $\leq$ 14°C/W, exceeding the heat sink requirement.

#### **Output Inductor: L1**

Coilcraft P/N S6030-B

20µH @ 0 Adc

10µH @11.2 Adc

13 Turns, # 16AWG on Micrometals T60-52D Core

$R_{DC} \leq 0.008\Omega$  max, 20°C Ambient

$T_{RISE} \approx 40^{\circ}C$  at maximum load

The output inductor of a Buck regulator is often chosen to maintain continuous current in the inductor under minimum load conditions. The ripple current in the inductor under minimum DC current conditions is equal to  $2 \cdot I_{MIN}$  for this rule to apply. For this power supply,  $L_{OUT}$  is determined by

$$L_{OUT} = \frac{(V_{IN} - V_{OUT}) \cdot Duty}{2 \cdot I_{MIN} \cdot F_{S}} = \frac{(5V - 3.1V) \cdot 0.64}{2 \cdot 0.3A \cdot 200 \text{ kHz}}$$

$$= 10.1 \text{ uH } @ \text{ Low Load}$$

A second condition for choosing the output inductor value is to limit the input current to the power supply during a step change in current from  $I_{MIN}$  to  $I_{MAX}$ . After a step change in load current, the duty cycle of the Buck regulator responds by assuming a maximum duty cycle of 100%. The input current therefore equals the output inductor current. To limit the input current rate to the required 0.1A/µs, the output inductor is chosen by

$$L_{OUT} = \frac{(V_{IN} - V_{OUT})}{di/dt} = \frac{(5V - 3.1V)}{0.1A/\mu s} = 19\mu H$$

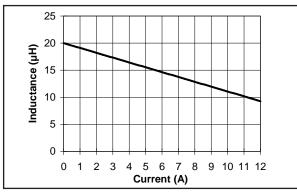

A toroidal inductor design is used to meet these needs. The form factor allows a component height of 0.800", thus allowing a sizable inductor that can be designed for low cost and simple winding techniques. The inductance vs DC current is shown in Figure 3. The inductor must not saturate with DC

#### **APPLICATION NOTE**

current equal to the power supply short circuit current limit, or the current limiting will not be effective.

Figure 3. Output Inductor Performance vs DC Current - No AC Flux

The in-circuit inductance will tend to be higher due to the AC Flux imposed by the volt-seconds product of the Buck regulator. Micrometals -52 material's permeability increases substantially with AC Flux. This same effect of AC Flux on the permeability of the -52 material plays a major role during the transient load response of the power supply. During a transient load response, the voltage differential across the output inductor is approximately V<sub>IN</sub>-V<sub>OUT</sub>. The duration of the transient response, in excess of 100 $\mu$ s, means that the AC Flux on the core for this time is given by

$$\Delta B_{AC} = \frac{(V_{IN} - V_{OUT}) \cdot T_{LOUT} \cdot 10^8}{N \cdot Ae}$$

$$= \frac{(5V - 3.1V) \cdot 100\mu s \cdot 10^8}{13Turns \cdot 0.374 \text{ cm}^2}$$

$$= 3908 \text{ Gauss}$$

which, according to Micrometals [3] results in multiplying the output capacitance by approximately 260%. This results in a dynamic inductance, during a load step, of approximately  $26\mu$ H. This feature will play an important role in the selection of the output capacitors to meet the transient load performance.

#### Output Capacitors: C06-C09, C11, C12, C29

SANYO - 6MV1500GX - 4 in Parallel C = 1500 $\mu$ F Form Factor = 10x20mm, Radial ESR = 0.044 $\Omega$ ESL  $\approx$  4nH (Estimated) Ripple Current Rating = 1.25A @ 105°C, 100kHz Choosing the output capacitors for this regulator may be the single most important decision with regards to meeting the transient load behavior of the Pentium<sup>®</sup>Pro. The transient load step of the Pentium<sup>®</sup>Pro is so large and so fast that there is no control loop which can respond quickly enough and maintain regulation. Capacitance, providing a low impedance output, is therefore the best solution to maintaining the proper output voltage.

#### Understanding the Response to a Step Load

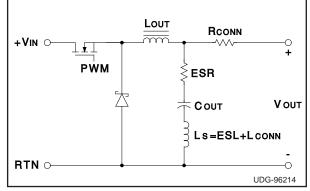

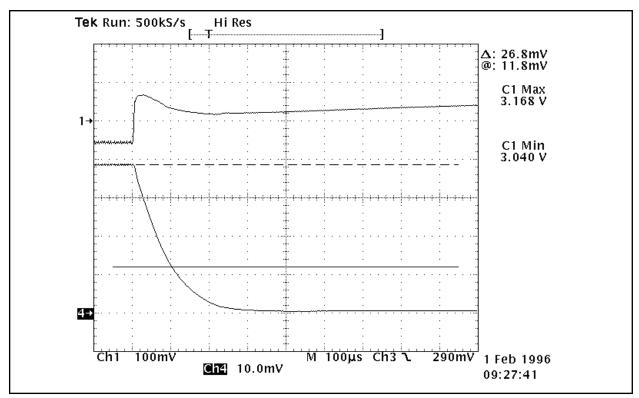

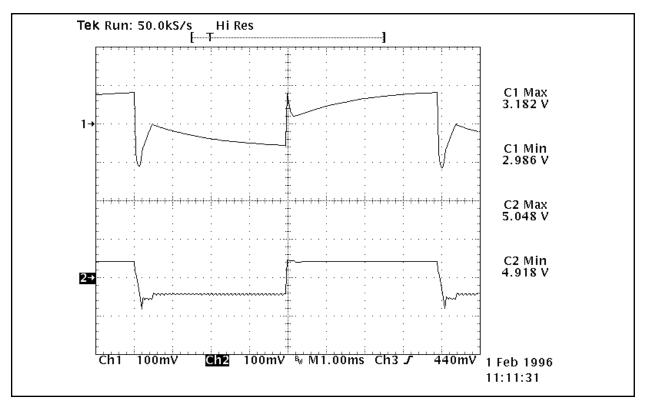

During a step load change from minimum to maximum current, the output of the power supply can be modeled as shown in Figure 4. Prior to the change in load current, the average current in the output inductor is  $I_{MIN}$  and the average current in the output capacitor is 0 amperes. Once the load current changes from Imin to  $I_{MAX}$ , the parasitic components shown in Figure 4 have a large affect on the output voltage.

Figure 4. Large Signal Transient Model of Power Supply Output Stage

The VRM connector pins have parasitic resistance and inductance termed R<sub>CONN</sub> and L<sub>CONN</sub>. The parasitic inductance of the connector and the output capacitors (ESL) are summed together as L<sub>S</sub>. ESR and R<sub>CONN</sub> cannot be combined in the capacitor path as this would result in a DC load regulation error.

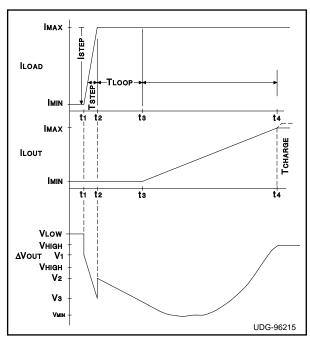

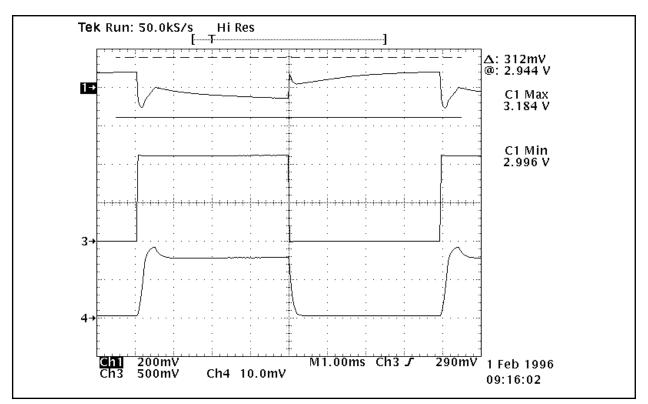

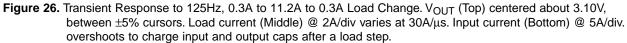

Figure 5 below illustrates the complexity of the output voltage waveform during a step in the output load current. A power supply with excellent load regulation is assumed for the purposes of understanding these dynamics. Reducing the load regulation through non-integrating [3] voltage loop gain will be discussed later in this application note. The output voltage responds to the load current step in four distinct phases, T<sub>STEP</sub>, T<sub>LOOP</sub>, T<sub>LOUT</sub> and T<sub>CHARGE</sub>.

Figure 5. Dynamics of a Step Load

Phase 1, the step current phase from  $t_1$  to  $t_2$  (T<sub>STEP</sub>), is characterized by a specified change in current and rise time. The response of the output voltage consists of:

- A voltage step proportional to the parasitic circuit inductance, L<sub>S</sub>.

- b) A ramp in voltage proportional to the parasitic circuit resistance,  $R_S$ , where  $R_S = R_{CONN} + ESR$ .

- c) A droop in voltage proportional to the power supply output capacitance.

The response of the output voltage during the time  $t_1$  to  $t_2$  is therefore given by  $t_2$

$$\Delta V_{OUT} = L_{S} \bullet \frac{\Delta I}{\Delta T} + i(t) \bullet R_{S} + \frac{1}{C_{OUT}} \int_{t_{1}} i(t) dt$$

which, at the end of T<sub>STEP</sub>, is equal to

$$\Delta V_{OUT} = I_{STEP} \bullet \left( \frac{L_S}{T_{STEP}} + \frac{T_{STEP}}{2 \bullet C_{OUT}} + R_S \right)$$

Phase 2, from  $t_2$  to  $t_3$  (T<sub>LOOP</sub>), is the time where the load current has settled at its maximum value, I<sub>MAX</sub>, but the power supply loop has not yet responded. The inductor current is therefore still set at I<sub>MIN</sub> and the response of the output voltage is therefore determined by

- a) A voltage proportional to R<sub>S</sub>.

- b) A droop in voltage proportional to the power supply output capacitance.

There is an initial discharge of the capacitor at the end of Phase 1 which is the initial condition for Phase 2, determined by

$$\Delta V_Phase1 = \frac{1}{C_{OUT}} \int_{t_1}^{t_2} \frac{I_{STEP}}{T_{STEP}} \bullet t dt$$

$$= \frac{I_{STEP} \bullet T_{STEP}}{2 \bullet C_{OUT}}$$

The response of the output voltage during the time  $t_2$  to  $t_3$  is therefore given by

$$\Delta V_{OUT} = \frac{I_{STEP} \bullet T_{STEP}}{2 \bullet C_{OUT}} + \frac{1}{C_{OUT}} \int_{t_2}^{t_3} i(t)dt + R_S \bullet$$

$$I_{STEP} = I_{STEP} \bullet \left(\frac{T_{STEP}}{2 \bullet C_{OUT}} + \frac{T_{LOOP}}{C_{OUT}} + R_S\right)$$

$T_{LOOP}$ , for the UC3886 Average Current Mode Controller and the compensation components shown in Figure 2, is less than one switching cycle.

Phase 3, from  $t_3$  to  $t_4$  ( $T_{LOUT}$ ), is the time when control loop has forced the Buck regulator to the maximum duty cycle (100% for the UC3886) and the inductor current is ramping from  $I_{MIN}$  to  $I_{MAX}$ . The output inductor current during this phase is given by

$$iL_{OUT(t)} = \frac{(V_{IN} - V_{OUT})}{L_{OUT}} \bullet t$$

Since the inductor current is ramping up during Phase 3, the capacitor current is ramping down, and is given by

$$\begin{split} \text{iC}_{\text{OUT}(t)} &= \text{I}_{\text{STEP}} - \text{IL}_{\text{OUT}(t)} \\ &= \text{I}_{\text{STEP}} - \frac{(\text{V}_{\text{IN}} \cdot \text{V}_{\text{OUT}})}{\text{L}_{\text{OUT}}} \bullet t \end{split}$$

The change in output voltage during Phase 3 consists of

- a) A voltage drop proportional to ESR and R<sub>CONN</sub>.

- b) A droop in voltage proportional to the output capacitance.

During Phase 3, the voltage drop due to the ESR and the capacitance is changing because the capacitor current decreases. The voltage drop due to  $R_{CONN}$  is constant, as it is set by the constant value of  $R_{CONN}$  and the maximum load current,  $I_{STEP}$ . There is an initial discharge of the capacitor at the end of Phase 2 which is the initial condition for Phase 3, determined by

$$\Delta V\_Phase2 = \frac{1}{C_{OUT}} \int_{t_1}^{t_2} \frac{I_{STEP}}{T_{STEP}} \bullet t \, dt + \frac{1}{C_{OUT}}$$

$$\int_{t_2}^{t_3} I_{STEP} \, dt = \left(\frac{I_{Step}}{2}\right) \bullet \left(\frac{2 \bullet T_{LOOP} - T_{STEP}}{C_{OUT}}\right)$$

The change in output voltage during Phase 3 is given by

$$\Delta V_{OUT} = \left(\frac{I_{STEP}}{2}\right) \cdot \left(\frac{2 \cdot T_{LOOP} - T_{STEP}}{C_{OUT}}\right) + \frac{1}{C_{OUT}} \int_{t_3}^{t_3} iC_{OUT(t)} dt + iC_{OUT(t)} \cdot ESR + I_{STEP} \cdot R_{CONN}$$

Which yields

$$\Delta V_{OUT} = \left(\frac{I_{STEP}}{C_{OUT}}\right) \bullet \left(t - \frac{T_{STEP}}{2} + T_{LOOP} - \frac{t^2}{2 \bullet T_{LOUT}}\right) + I_{STEP} \bullet \left(EST - \frac{ESR \bullet t}{T_{LOUT}} R_{CONN}\right)$$

$T_{\text{LOUT}}$  is defined as the time it takes for the inductor current to equal the change in load current,  $I_{\text{STEP}}.$

$$T_{\text{LOUT}} = \left(\frac{I_{\text{STEP}}}{(V_{\text{IN}} - V_{\text{OUT}})}\right) \bullet L_{\text{OUT}}$$

Phase 4, T<sub>CHARGE</sub>, is the time when the inductor current overshoots to reach the programmed short circuit current limit in order to replace charge lost by the output capacitor. At the end of phase 4, the output voltage drop settles to

$\Delta V_{OUT} = I_{STEP} \bullet R_{CONN}$ The duration of phase 4 is determined by

$$I_{Cout} = C_{OUT} \cdot \frac{dv}{dt}$$

which yields a time of

$$T_{CHARGE} = \frac{C_{OUT} \bullet \Delta V_Phase3}{(I_{SC} - I_{MAX})}$$

where  $I_{SC}$  is the programmed short circuit current limit, and  $\Delta V$ \_Phase3 is the voltage at the end of phase 3, determined by

$$\Delta V_Phase3 = \frac{I_{STEP}}{C_{OUT}} \cdot \left(\frac{T_{LOUT}}{2} - \frac{T_{STEP}}{2} + T_{LOOP}\right)$$

### Procedure for Determining the Required Output Capacitor(s)

Step 1: Determine the parasitic values of  $R_{CONN}$  and  $L_{CONN}$ . The following are estimates based on the connector pair used and the printed circuit board.

Resistance per pin  $\approx 10 m\Omega$

Resistance per mated pin set  $\approx 20m\Omega$

Inductance per mated pin set  $\approx$  4.28nH Number of output pins = 11 pairs in parallel Resistance of printed circuit board to the connector  $\approx$  0.2m $\Omega$

Inductance of printed circuit board to the connector  $\approx 0.2 nH$

$$\mathsf{R}_{\mathsf{CONN}} = \frac{20\mathrm{m}\Omega}{11} + 0.2\mathrm{m}\Omega = 2.02\mathrm{m}\Omega$$

$$L_{CONN} = \frac{4.28 \text{nH}}{11} + 0.2 \text{nH} = 0.59 \text{nH}$$

Step 2: Establish an allowable maximum voltage drop,  $\Delta V_{OUT}$ , at the output.

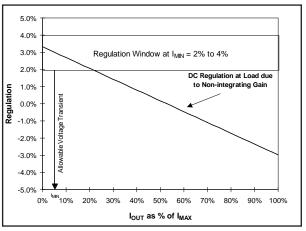

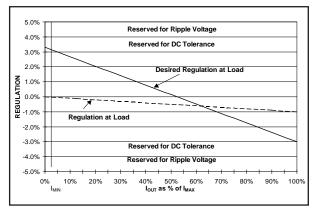

Application Note U-156 [3] discusses the use of non-integrating gain which allows a larger voltage deviation during a load transient. Set the minimum load regulation to be  $V_{NOM}$  +3% ±1%. Therefore, a -7% voltage deviation is allowed on the output voltage while still meeting a minimum overall voltage of -5%. Voltage ripple is not considered during this transient response as the duty cycle is effectively 100%, and there is no voltage ripple. These limits are illustrated in Figure 6.

Figure 6. Setting the Regulation and Voltage Transient Requirements

$$\Delta V_{OUT} = 0.07 \cdot 3.1V = 0.217$$

volts

Step 3: Estimate the total parasitic inductance, L<sub>S</sub>, in order to derive a required value of R<sub>S</sub> from the voltage step at the end of Phase

1. Aluminum electrolytic capacitors, size

10mm x 20mm, are estimated to have an ESL of approximately 4.0nH. Size 1206 ceramic chip capacitors are estimated to

have an ESL of approximately 1.9nH [1]. Assume that the combined ESL will be less than 0.51nH, for a total parasitic inductance

$L_{S} = 1.10 nH$

This value must be insured to maintain overall regulation limits during the first phase, T<sub>STEP</sub>.

Step 4: Equate the voltage deviation at the end of Phase 1 to the allowed voltage step. Assume that the change in voltage due to capacitive discharge is less than 1% of the overall change.

Therefore, the minimum value of  $\ensuremath{\mathsf{C}}_{\ensuremath{\mathsf{OUT}}}$  is equal to

$$C_{OUTmin} = \frac{10.9A \cdot 360ns}{2 \cdot 0.217V \cdot 0.01} = 904 \mu F$$

Solving for the maximum value of  $R_S$  for a step of 11.2A – 0.3A = 10.9A yields,

$$R_{S} = \frac{(0.217V \cdot 0.99) - (10.9A \cdot \frac{1.1nH}{360ns})}{10.9A}$$

$$= 16.6m\Omega$$

Step 5: Equate the voltage deviation at the end of Phase 2 to the allowed voltage step, from which a minimum value of C<sub>OUT</sub> can be obtained

$$0.217V = \left(\frac{10.9A}{2}\right) \bullet \left(\frac{2 \bullet 5.0 \mu \text{s} - 360 \text{ns}}{\text{C}_{\text{OUTmin}}}\right) + (13.8 \text{m}\Omega \bullet 10.9 \text{A})$$

$$C_{OUTmin} = \frac{\frac{10.9A}{2}(2.5\mu s \cdot 360ns)}{0.217V - (16.6m\Omega \cdot 10.9A)}$$

=1457µF

Step 6: Choose a capacitor type, manufacturer(s) and values. Determine the number of capacitors required to meet the ESR requirements from Step 4 and the minimum capacitance requirements from Step 5. Add 20% margin for variations in ESR from 20°C down to 10°C (minimum operating temperature).

> Radial, high frequency aluminum electrolytic capacitors are chosen based on the height allowed for this power supply VRM as well as their inherently low ESR and ESL. Many manufacturers offer 6.3V low ESR devices rated for 100kHz - 200kHz operation. Sanyo's MV-GX series of alu

minum electrolytic capacitors are chosen based on their lower ESR specifications.

ESR Required =  $16.6m\Omega \cdot 0.8 = 13.3m\Omega$

Sanyo MV-GX 1500 $\mu$ F, 10mm x 20mm, 6.3V device has a rated maximum ESR of 44m $\Omega$ . 4 devices are required, using 400mm<sup>2</sup> of board area. Sanyo MV-GX 1000 $\mu$ F, 8mm x 20mm, 6.3V device has a rated maximum ESR of 64m $\Omega$ . 6 devices are required, using 384mm<sup>2</sup> of board area. The 1500 $\mu$ F device is chosen to reduce the total parts count. The solution is:

$\mathsf{ESR} = 44\mathrm{m}\Omega \,/\,4 = 11.0\mathrm{m}\Omega$

$ESL \approx 4nH / 4 = 1.0nH$

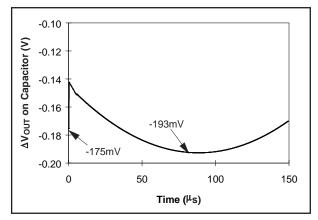

Step 7: Determine the voltage waveform at the output given this solution of output capacitors.

The current in the capacitor, during a transient, ramps up (or down) in a time determined by the output inductor. The output inductor, during a transient load step, is approximately  $26\mu$ H.

$$T_{\text{LOUT}} = \left(\frac{I_{\text{STEP}}}{(V_{\text{IN}} - V_{\text{OUT}})}\right) \bullet L_{\text{OUT}}$$

$$= \left(\frac{10.9\text{A}}{(5.0\text{V} - 3.1\text{V})}\right) \bullet 26\mu\text{H} = 149\mu\text{s}$$

The capacitor current is defined as

$$iC_{OUTt} = I_{STEP} - \frac{I_{STEP}}{T_{LOUT}} \cdot t$$

The voltage drop at the output of the power supply, during Phase 3 ( $T_{LOUT}$ ) of the load transition, is determined by

$$\Delta V_{OUT} = \frac{I_{STEP}}{C_{OUT}} \bullet$$

$$\left(t - \frac{T_{STEP}}{2} + T_{LOOP} - \frac{t^2}{2 \bullet T_{LOUT}}\right) + I_{STEP}$$

$$\bullet \left(ESR - \frac{ESR \bullet t}{T_{LOUT}} + R_{CONN}\right)$$

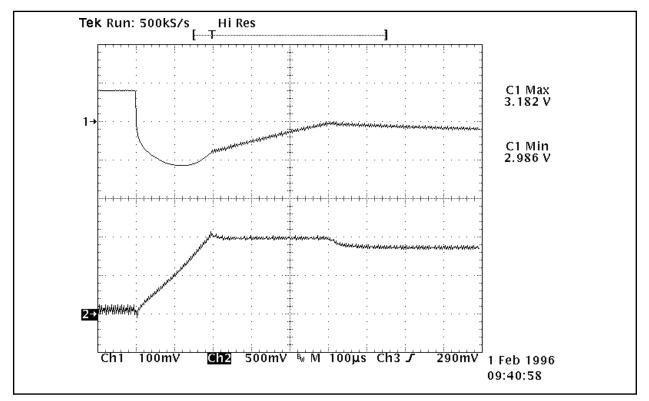

The entire voltage response is plotted in Figure 7. Ceramic and tantalum capacitors (C11, C12, C29) are added in parallel to the aluminum output capacitors to reduce the overall ESL to less than the required

Figure 7. Voltage Droop on Power Supply Output during Load Transient

0.51nH and to reduce high frequency noise to meet the ripple requirement of  $\leq 2\%$  peak-to-peak.

#### Input Capacitors: C01-C05

SANYO - 6MV1500GX - 3 in Parallel

$C = 1500 \mu F$

Form Factor = 10 x 20mm, Radial

$\mathsf{ESR} = 0.044\Omega$

$ESL \approx 4nH$  (Estimated)

Ripple Current Rating = 1.25A @ 105°C, 100kHz

The input capacitance for a Buck regulator is chosen based on several criteria:

- a) Ripple Current Handling at FSWITCH

- b) Ripple voltage at F<sub>SWITCH</sub>

- c) Maintaining Input voltage during load transients

The resulting solution must present a very low impedance to the input supply and to the Buck Regulator, resulting in a need for low ESR, large value capacitors.

#### **Ripple Current and Voltage**

The input capacitors are chosen primarily based on their switching frequency RMS current handling capability. With just 10's of nanohenries parasitic input inductance the input capacitors must handle virtually all of the 200kHz switching current.

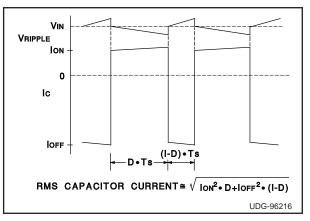

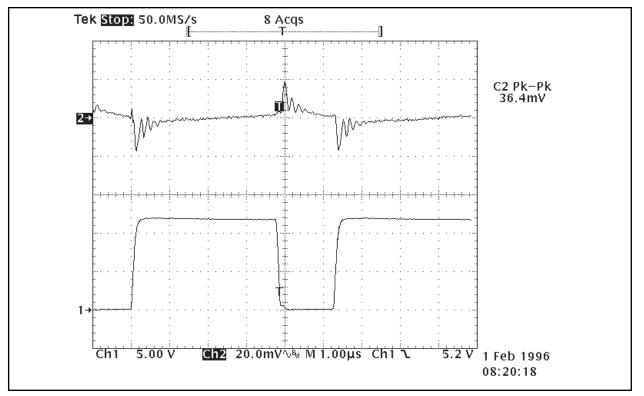

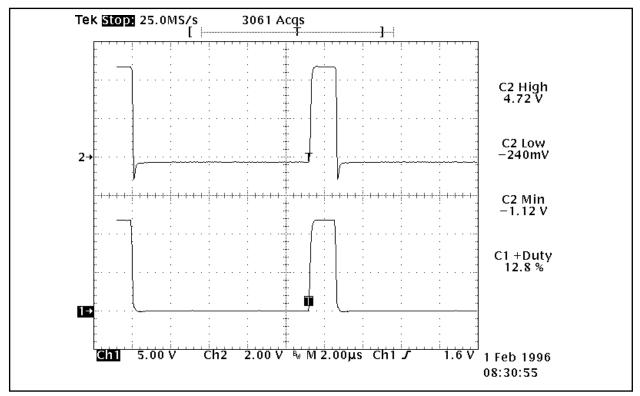

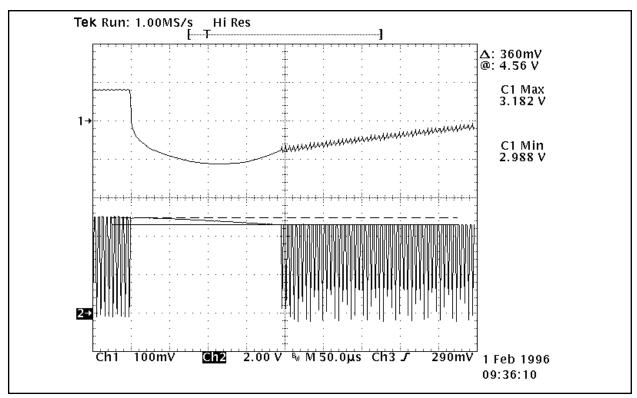

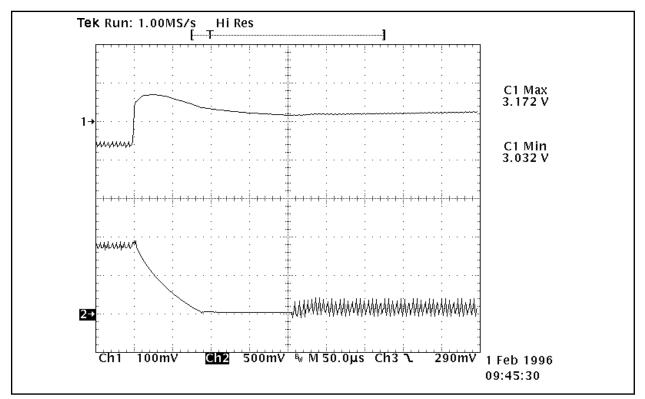

Figure 8 shows the switching waveforms in the input capacitor(s). The average VRM power supply input current is calculated based on the maximum load of the power supply and the efficiency at maximum load.

Figure 8. Input Capacitor(s) Current Waveform

$$I_{AVG} = \frac{P_{INPUTmax}}{V_{INPUT}} = \frac{I_{Omax} \cdot V_{OUT}}{Efficiency \cdot V_{INPUT}}$$

$$= \frac{11.2A \cdot 3.1V}{0.80 \cdot 5.0V} = 8.68A$$

During the MOSFET ON time, the input capacitors must provide the difference between the load current and the input current. During the MOSFET OFF time, the capacitor current is the complete input average current. Therefore,

$$I_{ON} = I_{Omax} - I_{AVG} = 11.2A - 8.68A = 2.52A$$

$I_{OFF} = -I_{AVG} = -8.68A$

The duty cycle at the maximum operating current is approximately 73%, and therefore the RMS current in the capacitors, assuming a rectangular waveform since the current ramp is very small, is given by

$$I_{RMS} = \sqrt{I_{OFF}^2 \cdot (1 - \text{Duty}) + I_{ON}^2 \cdot \text{Duty}}$$

= 5.0 A<sub>RMS</sub>

Three (3) Sanyo capacitors are chosen to maintain reliable operation while operating at this RMS current level.

Given the current waveform of Figure 8, the input voltage ripple will be proportional to the input capacitance and ESR, as shown in the voltage waveform of Figure 8. Low ESR and high capacitance will keep the ripple voltage low.

C01 and C02 ceramic capacitors are added to filter high frequency noise from the switching power supply from the +5V input power bus.

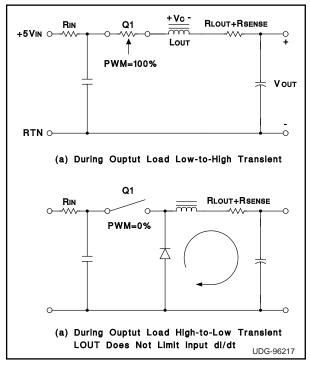

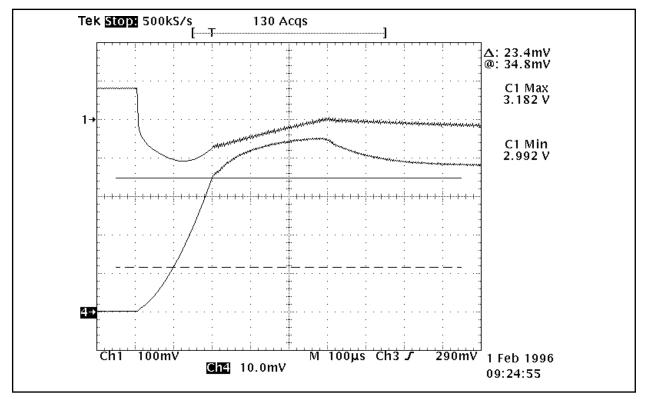

### Filtering VINPUT During Load Transients

During a low-to-high output load transient, the duty cycle goes to 100% until the output inductor current is equal to the load current, and the output inductor limits di/dt of the input current. During a high-to-low output load transient, however, there is no output

inductor limiting the input current rate because the input switch is opened (0% duty cycle). The result is the +5V bulk power supply will continue to source high current into this power supply for some time. Figure 9 illustrates the difference in the circuits between a low-to-high and a high-to-low load transient.

Figure 9. Lout limits the input current only on a low-tohigh output current transient

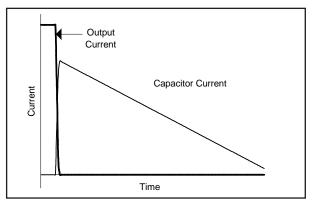

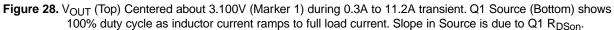

Figure 10 shows typical current waveforms during a high-to-low load transient. The output current abruptly stops but the +5V bulk power supply takes a finite time to react to this change in load current, therefore sourcing energy into the input capacitors. Intel specifies that this input current must not change at a rate faster than  $0.1A/\mu$ s.

The input capacitor(s) are chosen to limit the voltage surge on the input capacitors to less then 0.15

Figure 10. Current Waveforms during High-to-Low Output Transient

volts (3% of  $V_{\text{IN}}$ ) during a high-to-low load transient. The current in the capacitor(s) is defined as

$$iC_{IN(t)} = I_{AVG} - I_{In\_Rate} \bullet t$$

$$= 8.68A - (0.1A/\mu s) \bullet t$$

where  $I_{In\_Rate}$  is defined as the rate at which the input current decays based on the +5V bulk power supply, assumed here to be 0.1A/µs, therefore decaying to 0.0A in 86.8µs.

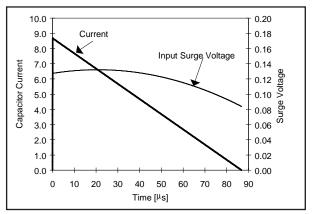

The voltage surge on the input capacitance during this time is  $_{R \in R_{\rm HS}}$

$$vC_{IN(t)} = \frac{1}{C_{IN}} \int_{0}^{0} = iC_{IN(t)} + (ESR_{IN} \bullet iC_{IN(t)}) = \left(\frac{8.68}{Cin} - (10^5 \bullet ESR)\right) \bullet t - \left(\frac{10^5 \bullet t^2}{2 \bullet C_{IN}}\right) + 8.68 \bullet ESR$$

which is plotted in Figure 11 for 3 Sanyo MV-GX type 1500 $\mu$ F, 0.044 $\Omega$  Aluminum Electrolytic Capacitors.

Figure 11. Input Capacitor Current and Surge Voltage During a High-to-Low Load Transient

#### Sense Resistor: R01

Dale P/N WSR-2 0.01Ω 1%

$10m\Omega,$  2.0 watt 2 wire SMD sense resistor,  $\pm75ppm$  TCR

The sense resistor is chosen by the criteria discussed in U-156, Appendix 5 [3]. R<sub>SENSE</sub> is a 2wire, 2 watt surface mount power product with very low inductance. The 2 watt rating (to ambient temperatures of 75°C) allows for 50% derating at the typical maximum current of 9.9 Amperes [1].

A short circuit current,  $I_{SC}$ , is chosen at a nominal 12.5 Amperes, more than 10% over the maximum current. The value of the UC3886 Current Amplifier's gain,  $G_{CSA}$ , is bounded to

$$G_{CSA\_MIN} = 5.0 \text{ and } G_{CSA\_MAX}$$

= 2.5MHz/200kHz

#### APPLICATION NOTE

From

$$G_{CSA} \bullet R_{SENSE} = \frac{1.0 \text{ Volt}}{I_{SC}}$$

A 12.5A limit implies that Rsense must lie between  $0.0064\Omega$  and  $0.016\Omega$ . Choose  $0.010\Omega$  as the lowest standard value.

The power dissipation in  $R_{SENSE}$  during normal and short circuit conditions is

Normal:

$$P_{\rm D} = I_{\rm AVG}^2 \bullet R_{\rm SENSE} = 9.9^2 \bullet 0.010\Omega$$

Short Circuit:

$$P_D = I_{SC}^2 \cdot R_{SENSE} = 12.5^2 \cdot 0.010\Omega$$

= 1.56 Watt = 78% of rated

#### CONFIGURING THE UC3910 4-BIT DAC AND VOLTAGE MONITOR AND THE UC3886 AVER-AGE CURRENT MODE PWM CONTROLLER

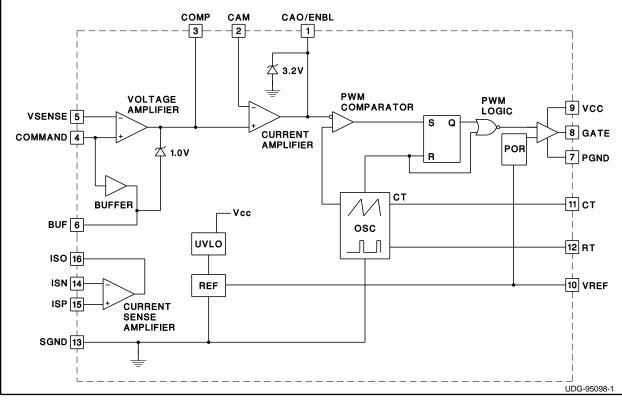

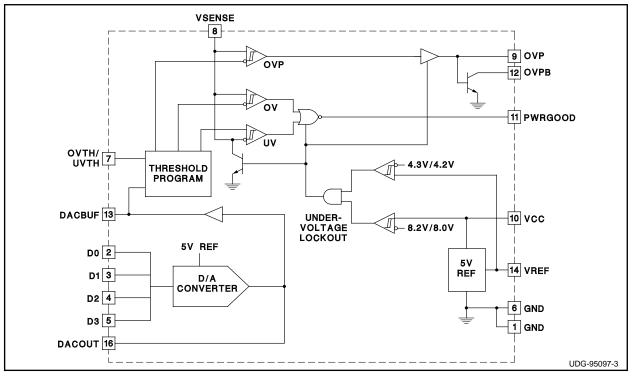

With the power stage chosen, the UC3910 and UC3886 are ready to be programmed for the proper operation. Figure 12 and Figure 13 show block diagrams for the UC3886 and the UC3910 ICs.

#### Grounding

The UC3886 signal ground (SGND) pin as well as the UC3910's two ground pins are referenced to

the output voltage return path for best regulation and noise immunity. The PGND pin of the UC3886 is referenced to the input voltage return path, as discussed in U-156 [4], for best gate drive performance.

#### Decoupling

High frequency decoupling is provided at the VCC power pins (C14, C18) and the VREF pins (C13, C17) of both ICs. VCC is decoupled to PGND on the UC3886 additionally with a low ESR  $0.1\mu$ F capacitor (C19) to provide a low impedance gate drive source.

#### Set the UC3886 Oscillator Frequency to 200kHz

During a load transient, a very high duty cycle is desired. Therefore, set the maximum duty cycle to 99%. From the UC3886 Data Sheet:

$$D_{MAX} = 1 - \frac{2.0V}{(R_T \bullet 4.0mA)} = 0.99 \rightarrow$$

$$R_{T} = \frac{2.0V}{(1 - D_{MAX}) \bullet 4.0mA} = 50k\Omega$$

$$C_{T} = \frac{2.0V \bullet ((4.0mA \bullet R_{T}) - 2.0V]}{F_{S} \bullet 1.8V \bullet R_{T}^{2} \bullet 4.0mA} = 110pF$$

Choose  $C_T = 100 \text{pF}$  (C20)  $R_T = 54.9 \text{k}\Omega$  (R10)

Figure 12. UC3886 Average Current Mode PWM Control IC

Figure 13. UC3910 4-BIT DAC and Voltage Monitor IC

Note that internal capacitance on the UC3886 CT pin adds approximately 10 to 15pF of capacitance. When using a capacitor as low as 100pF, a substantial frequency shift can result.

A 24 $\Omega$  resistor and Test Point 1 (R11 and TP1) are provided to allow external synchronization of the unit from a narrow synchronizing pulse [3]. This resistor is not required unless external synchronization is desired.

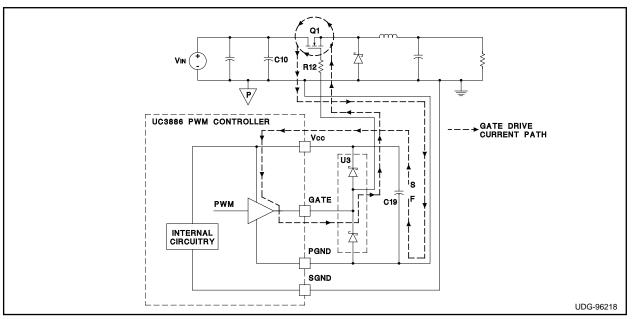

# Driving the MOSFET Gate from the UC3886 Gate Drive Output

A 10 $\Omega$  gate drive resistor (R12) is placed close to the MOSFET gate. The 10 $\Omega$  resistor limits the peak current and provides damping at the MOSFET gate to prevent oscillations. The power dissipation in this resistor is approximately 1.0mW based on an average current of 10mA.

Figure 14 shows that the current path for a gate drive signal originates from C19, a low decoupling capacitor located closely to the UC3886 GATE pin. C10 is added from the input voltage to the Power Ground (PGND) to decouple the high frequency current spike which exits the MOSFET from the DRAIN and must find a path back to PGND. C10 should be located as closely as possible to the MOSFET to prevent high frequency ringing at the MOSFET.

U3, the UC3612 dual schottky diode, is added to protect the UC3886 from inductive spikes above  $V_{CC}$  and below ground which may occur due to high gate drive spikes and parasitic inductance.

# **External Enable Signal**

Intel specifies [1] that the Pentium<sup>®</sup>Pro power supply be enabled by an open collector, active high signal, OUTEN.

The UC3886 CAO/ENBL is connected to the input of the UC3886 PWM comparator (Figure 12), with the other side of the comparator attached to the oscillator ramp. The oscillator ramp is nominally a 1.0V to 2.8V peak ramp signal. The UC3886 gate drive is disabled by bringing the CAO/ENBL signal to a level below the oscillator ramp signal.

The external OUTEN signal is connected to the UC3886 CAO/ENBL signal through a  $1.0k\Omega$  resistor, R2. A  $1.0k\Omega$  resistor is recommended to provide a high impedance buffer between external noise and the output of the UC3886 Current Amplifier Output, to insure noise does not couple into the control loop. The CAO/ENBL pin may source up to  $400\mu$ A. Using a  $1.0k\Omega$  resistor will result in a 400mV drop. A reasonable open collector output stage will be able to sink  $400\mu$ A and maintain a saturation voltage less than 400mV, keeping the LOW level voltage at CAO/ENBL to less than 800mV.

Figure 14. Driving Q1 with the UC3886

#### **External Signal UP#**

Intel specifies [1] that the UP# signal be used to disable the power supply if it is not capable of supporting an upgraded processor, either by varying the voltage or by supporting the higher load currents. The UP# signal is also an open collector signal, normally high, but pulled low when an Upgrade Processor is in place. By inserting a  $0\Omega$  jumper resistor for R25, the power supply will be disabled in the case of an upgrade processor.

THE UNITRODE DEMONSTRATION KIT IS SHIPPED WITHOUT R25. UPGRADE PROCESSORS MAY EXCEED THE 12.5A CURRENT LIMIT OF THE DEMONSTRA-TION KIT. INSERT A  $0\Omega$  0603 SMD JUMPER RESISTOR FOR R25 TO DISABLE THE POWER SUPPLY IN AN UPGRADE PROCESSOR APPLICATION

#### CONFIGURING THE UC3910 VOLTAGE MONITORING AND PROTECTION FEATURES

The regulation requirements for this power supply are set at  $\pm$ 5%. The PWRGD requirement is set to signal a voltage regulation failure when the output voltage is outside of the range of  $\pm$ 10%. The UC3910 Undervoltage and Overvoltage (UV, OV) thresholds are therefore chosen at midrange to be nominally  $\pm$ 7.5%.

The equations for setting the Voltage Monitoring thresholds (see U-158 [7]) are

$$\% V_{\text{UV}} = -\left(\mathsf{R}_{\text{DIV}} \bullet \frac{3.34 \mathrm{k}\Omega}{20 \mathrm{k}\Omega}\right) \bullet 100 = -(\mathsf{R}_{\text{DIV}} \bullet 16.7)$$

%Vov =

$$R_{DIV} \bullet 16.7$$

$%Vovp = R_{DIV} \bullet 33.4 = \%Vov \bullet 2.0$

Setting %V\_UV and %V\_OV to  $\pm 7.55$  yields a divider ratio R\_DIV of 0.45.

R8 and R9 act as a voltage divider between the UC3910's DACBUF pin and OVTH/UVTH pin. R8 and R9 are chosen to draw approximately 1.0mA.

$R8 = 1.69 k\Omega$ ,  $R9 = 1.34 k\Omega$ ,  $R_{DIV} = 0.448$

The nominal thresholds are

\_\_\_\_

| Overvoltage Threshold            | = +7.48%  |

|----------------------------------|-----------|

| Undervoltage Threshold           | = -7.48%  |

| Overvoltage Protection Threshold | = +14.96% |

#### **PWRGD Signal:**

Intel requires [1] the PWRGD signal to be an open collector active HIGH signal when the voltage is within specification. R7 is a  $4.7k\Omega$  resistor which can be added internally to the demonstration kit power supply for evaluation purposes. See the schematic of Figure 2.

R7 IS NOT INSTALLED ON UNITRODE'S DEMONSTRATION KIT. USE A 4.7kΩ 1/10W 0603 SMD RESISTOR IF INTER-NAL PULLUP IS DESIRED.

#### **Overvoltage Protection:**

The UC3910 provides both OVP and OVPB pins for protection in the case of overvoltage. OVP is capable of driving an SCR to perform a crowbar func-

tion. OVPB is an open collector, active low signal which is designed to pull down on the UC3886 CAO/ENBL signal to disable the UC3886 gate drive.

The Overvoltage Protection circuit consists of F1, SCR1, CR2, R05 and R06. Fuse F1 serves to protect the circuit under two circumstances: a MOSFET short circuit failure and when the crowbar SCR is fired. The fuse is chosen based on the maximum operating power and efficiency.

$P_{OUTmax} = 3.4 \text{ Volts} \bullet 11.2 \text{ Amps} = 38 \text{ Watts}$  $I_{INmax} = \frac{38 \text{ Watts}}{0.80 \bullet 5.0 \text{ V}} = 9.5 \text{ Amperes}$

# A 10 Ampere SMD fuse is chosen.

Characterizing SCR's for Crowbar Applications is discussed extensively in Motorola's Thyristor Device Data book [5]. SCR1 is chosen based on its low gate trigger current, its On-State RMS current rating, and because it has to discharge a substantial amount of low ESR aluminum capacitors, its Peak Non-repetitive surge current rating.

SCR1 by itself will not protect the Pentium<sup>®</sup>Pro processor against an overvoltage except by causing the fuse F1 to open, which can take a substantial amount of time. CR2 provides an additional path to discharge the output capacitors directly in order to clamp the output voltage and protect the processor immediately. CR2 is connected before the sense resistor, R1, in order to use R1 as a current limiting resistor when the crowbar is fired. CR2 has a rated surge current of 200 Amperes.

Connecting an SCR as a crowbar to the output voltage may appear to be the best way to protect the Pentium®Pro processor in the case of an overvoltage failure. However, the UC3886 provides a current limiting mechanism, which would cause the SCR to sink the programmed current limit. An input fuse would not open under these circumstances because of the low output power being delivered. The SCR on the output would most likely fail thermally and open, thus defeating the protection mechanism.

Resistor R6 from the SCR gate to ground is chosen to protect the SCR against false firing due to dv/dt conditions. R6 will draw approximately 15mA when the SCR is fired, as the gate voltage is approximately 1.5 volts. R5 is chosen to limit the current from the UC3910 while insuring that the SCR gate trigger current is sufficient down to 10°C. The UC3910 will source at least 65mA when activated. R5 limits the current preventing excessive droop on VCC when the SCR is fired. The open collector signal OVPB is also triggered during an overvoltage protection fault. This signal can be used to disable the UC3886 gate drive by connecting it directly to the UC3886 CAO/ENBL signal. R26 is installed in Unitrode's demonstration kit as a "jumper" only, to enable or disable this feature. Normal applications will directly connect the UC3886 CAO/ENBL pin to the UC3910 OVPB pin. Note that the OVPB signal is an open collector signal and therefore may be "OR';d" with the external open collector OUTEN and UP# signals.

# Setting the RC Filters at VSENSE and DACOUT of the UC3910

The UC3910 VSENSE pin requires an R-C filter to isolate the pin from the power supply output [6]. The resistor acts both as part of an R-C filter and to limit the current into the VSENSE pin. During UVLO of the UC3910, VSENSE is actively pulled low in order to prevent false overvoltage protection signals.

The filter resistor R3 is chosen to limit the input current to  $\leq$ 500µA under the maximum programmable voltage for the Pentium<sup>®</sup>Pro.

$$R3 \quad \frac{3.4V}{500\mu A} = 6.8k\Omega$$

The filter capacitor C16 is chosen to set the filter corner frequency at approximately  $F_{SWITCH}/10$  in order to reduce the switching frequency ripple by 20dB.

C16 =

$$\frac{1}{R3 \cdot 2 \cdot \pi \cdot (200 \text{ kHz/10})}$$

= 1170pF

Use R3 =  $6.8k\Omega$

C16 = 1200pF as standard values

The filter capacitor at the output of DACOUT, C15, is chosen to insure that DACOUT rises at a faster rate than VSENSE. This prevents false OVP signals during  $V_{CC}$  brownout or glitch conditions.

$$\begin{split} &\mathsf{R3}\bullet\mathsf{C16}>3k\Omega\bullet\mathsf{C15}\rightarrow\\ &\mathsf{C15}\leq\frac{\mathsf{R3}\bullet\mathsf{C16}}{3k\Omega}\quad\text{2720pF} \end{split}$$

Use C15 = 2700pF as a standard value

Note that resistor R4 connected to the UC3910 VSENSE pin is used for debug purposes only and is not required for normal operation.

# Programming the Current Limit with the Current Sense Amplifier of the UC3886

A nominal current limit of 12.5 Amperes is desired to protect the power supply under short circuit con-

ditions. Accurate current limiting is advantageous in this Buck regulator as it limits the power dissipated in the freewheeling diode under short circuit conditions.

The gain of the current sense amplifier,  $G_{CSA}$ , is set based on the desired current limit and the value of the sense resistor [4], using:

$$G_{CSA} \bullet R_{SENSE} = \frac{1.0 \text{ Volt}}{I_{SC}} \rightarrow$$

$$G_{CSA} = \frac{1.0 \text{ Volt}}{12.5A \bullet 0.01\Omega} = 8.0$$

The current sense amplifier is configured as a differential amplifier using four external resistors, R18, R19, R20 and R21, with the gain equal to

$$GCSA = 8.0 = \frac{R20}{R18} = \frac{R21}{R19}$$

R20 and R21 should not load down the UC3886 Current Sense Amplifier, and are chosen as  $33.2k\Omega$ . Therefore

$R18 = R19 = 4.22k\Omega$  resulting in

$G_{CSA} = 7.87$  and a nominal short circuit current limit,  $I_{SC}$ , of 12.7 Amperes.

The BUF signal at pin 6 of the UC3886 must be filtered by C22 to insure a noise free bias voltage for the current sense signal ISO.

# Programming the Non-Integrating Gain for the Voltage Amplifier of the UC3886

Managing the voltage regulation at the load, and maintaining regulation of  $\pm 5\%$  involves the use of non-integrating gain about the UC3886 voltage amplifier. Without non-integrating gain, the number of output capacitors must increase. Application note U-156 [4], Appendix 3, details the goals and requirements for programming non-integrating gain.

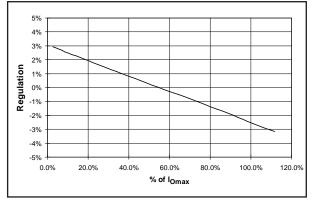

The specified regulation window is  $\pm 5\%$ . V<sub>RIPPLE</sub> and DC Error, which are each  $\pm 1\%$ , reserve  $\pm 2\%$  of the specified window. This leaves  $\pm 3\%$  of the window for load regulation. The desired regulation performance, versus load current, is shown in Figure 15. Setting the low load regulation to +3% nominally will allow the maximum voltage excursion during a load transient.

The UC3886 error voltage, COMP, will vary with load current from 0.0A to  $I_{SC}$  = 12.7A. The change in the error voltage will be

$$\Delta \text{Ve} = \frac{\text{I}_{MAX}}{\text{I}_{SC}} \bullet 0.95\text{V} = \frac{11.2 \text{ Amps}}{12.7 \text{ Amps}} \bullet 0.95\text{V}$$

$$= 0.834 \text{ Volts}$$

Figure 15. Load Regulation

A change in COMP of 0.95 volts is used because the change is 1.0V  $\pm$ 50mV, and under worst case the regulation window must be held.

Figure 15 shows that the load regulation due to parasitic resistances is -1% from no load to maximum load. From the desired load regulation curve, the swing in output voltage associated with the change from 0 Amps (Not I<sub>MIN</sub> in this case) to I<sub>MAX</sub> is determined to be -6.3%. The I • R drop intrinsic to the circuit is then subtracted and the desired regulation swing is set at -5.3%. From the lowest operating voltage, the change in the output voltage is

$$\Delta V_{OUT} = 2.4 \text{ V} \cdot 5.3\% = 0.127 \text{ Volts}$$

The gain around the Voltage Amplifier determined by the ratio of R16 to R14 is chosen to achieve the desired voltage swing over the operating load range.

$$\Delta V_{OUT} = \frac{\Delta V_E}{Gain} = \frac{\Delta V_E}{R16/R14}$$

and

therefore R16/R14 =

$$\frac{0.88V}{0.127V}$$

= 6.57

The feedback resistor is chosen very large to insure that there are no loading effects on the voltage amplifier output.

Use R16 =

$$100k\Omega$$

R14 =  $15k\Omega$  resulting in the gain about

the Voltage Amplifier of 6.67.

Non-Integrating gain has a negative regulation slope with regards to load current, and must be shifted up in order to swing  $\pm 3\%$  about the nominal voltage. A DC offset is created by the resistive divider of R14 and R17 which shifts the regulation window up by +3.1%. R17 is chosen by

$$(V_{NOM} + 3\%) \bullet \frac{R17}{R14 + R17} = V_{NOM}$$

and therefore

$\frac{R17}{R14 + R17} = \frac{1}{1.03}$  yielding R17 = 487k $\Omega$ .

# Filtering and Canceling Offset Current at the Command Pin of the UC3886

It is recommended that the decoupling capacitor, C21 be placed very close to the COMMAND pin of the UC3886, as this voltage is the voltage which commands the power supply output, and noise will directly couple to the power supply output. R13 is added in series between the UC3910 DACOUT pin and the UC3886 COMMAND pin in order to minimize DC errors due to offset currents in the UC3886 voltage amplifier. R13 is chosen to match the impedance at the V<sub>SENSE</sub> input to the UC3886 voltage amplifier. Remember that the UC3910 DACOUT pin has an internal  $3k\Omega$  resistor. Therefore

R13 =

$$\frac{1}{\frac{1}{R16} + \frac{1}{R14} + \frac{1}{R17}} - R_{DAC} =$$

=  $\frac{1}{\frac{1}{\frac{1}{100k\Omega} + \frac{1}{15k\Omega} + \frac{1}{487k\Omega}}} - 3k\Omega = 9.7k\Omega$

Use R13 =  $10k\Omega$

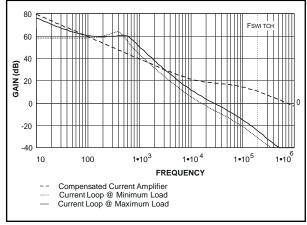

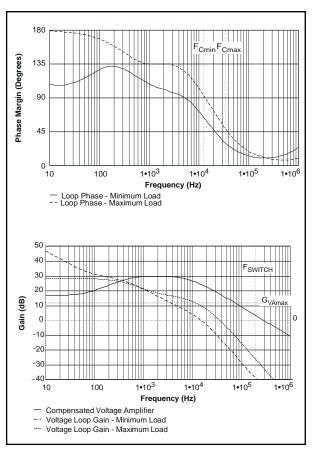

#### CLOSING THE LOOP WITH THE UC3886 AVERAGE CURRENT MODE PWM CONTROLLER

The basis for closing the Average Current and the Voltage loops of this circuit is found in Unitrode Application Note U-140 [2] and in the Unitrode Seminar Topic "Switching Power Supply Control Loop Design" [7]. This application note presents a step-by-step methodology solving for the loop compensation components found in Figure 2. The current loop is completed first with the voltage loop to follow.

The goal in closing the loops for this power supply is to obtain a stable closed loop response for the current and voltage loops, with an overall closed loop crossover frequency between 10kHz and

$$\frac{\mathsf{F}_{\mathsf{S}}}{2\pi} = 32 \mathsf{kHz}.$$

#### **Closing the Current Loop**

Step 1: Calculate the Oscillator Ramp as seen at the PWM Comparator input. From U-140, it is known that "The amplified inductor current downslope at one input of the PWM comparator must not exceed the oscillator ramp slope at the other comparator input". From the oscillator timing equations, the ramp slope is

$$T_{S} = \frac{1}{F_{S}} = 5.0 \mu s$$

$T_D \approx 50$ ns (Deadtime of oscillator)

$$Ramp = 2.8V - 1.0V = 1.8Vp-p$$

$$Ramp Slope = \frac{Ramp}{T_S - T_D} = \frac{1.8V}{4.95\mu s}$$

$$= 0.364 \text{ Volts/}\mu s$$

Step 2: Calculate the inductor current downslope. The downslope occurs during the Buck regulator switch OFF time.

> The inductor downslope is maximum at the maximum output voltage and with the minimum output inductance, which occurs at maximum load and maximum output voltage.

> The diode forward voltage of CR1 is approximately 0.35V at 11.2A

$V_{OUTmax} = 3.4V$

$L_{OUT}$  at the maximum operating current =  $12\mu H$

Inductor di /dt =  $\frac{3.4V + 0.35V}{12.0\mu H}$  = 0.313A/µs

Step 3: Convert the inductor current downslope to a voltage downslope as seen at the output of the Current Sense Amplifier.

Inductor  $dv/dt = 0.313A/\mu s \cdot 0.01\Omega \cdot$

$$\frac{33.2k\Omega}{4.22k\Omega} = 24.6 \text{mV/}\mu\text{s}$$

Step 4: Set the gain from the Current Amplifier to meet the slope criteria. Reduce G<sub>CAmax</sub> by 25% to account for amplified voltage ripple due to the ESR of the output capacitors. Reduce the gain by 15% more to account for Inductor and Oscillator variations.

The oscillator Ramp Slope =  $0.364V/\mu s \ge G_{CA} \bullet Inductor dv/dt$

where  $G_{CA}$  = The gain of the Current Amplifier at the switching frequency

Therefore:

$$G_{CA}$$

at  $F_{SWITCH} = \frac{364 \text{mV} / \text{ms}}{24.6 \text{mV} / \text{ms}} \cdot 0.60 = 8.9$

Resistors R23 and R24 set the inverting

gain about the UC3886 Current Amplifier. Pick R24 to limit the loading on the Current Amplifier output. Then set R23 and R24 to program the Current Amplifier's inverting gain at F<sub>SWITCH</sub>.

Use

$R24 = 10.5 k\Omega$

$R23 = 1.24k\Omega$

as standard values

G<sub>CA</sub> = 8.47

The GBW product for the UC3886 Current Amplifier is 3.5MHz and therefore a gain of 8.47 at 200kHz is within the device's GBW.

Step 5: Find the crossover frequency of the current loop gain by first finding the small signal control-to-output gain, G<sub>P</sub>, of the buck regulator current loop power section. Consider the fact that the inductor, L<sub>OUT</sub>, plays a key role in the equation for G<sub>P</sub>, and that since L<sub>OUT</sub> swings significantly with load current, so does G<sub>P</sub>.

The small signal control-to-output gain is defined in U-140 from the CA output,  $V_{CA}$ , to the voltage across the sense resistor,  $V_{RS}$ . The UC3886 application however must add a gain stage factor for the Current Sense Amplifier gain. G<sub>P</sub> is determined by

$$\frac{V_{RS}}{V_{CA}} = \left(\frac{Duty}{V_{CA}}\right) \bullet \left(\frac{V_{RS}}{I_{Lout}}\right) \bullet \left(\frac{I_{Lout}}{Duty}\right) \bullet G_{CSA}$$

$$= G_{P}$$

The change in duty cycle to change in Current Amplifier output is  $100\%/V_S$ , or

$\frac{\text{Duty}}{\text{V}_{\text{CA}}} = \frac{1}{\text{V}_{\text{S}}}$

where

$V_{S}$  = The peak-to-peak voltage change of the oscillator ramp

The change in the resistor voltage to change in the inductor current is simply the value of the sense resistor,  $R_S$  ( $R_S = R1$  in Figure 2).

$$\frac{V_{RS}}{I_{Lout}} = Rs$$

The change in inductor current per the change in duty cycle is a function of the input voltage. The small signal voltage applied at the inductor is simply the small signal changes in  $V_{IN} \bullet$  Duty. The change in inductor current per the change in applied inductor voltage (small signal) is given by:

$$\frac{I}{v} = \frac{1}{Z_{OUT}} \text{ where } v = V_{IN} \bullet \text{Duty}$$

and therefore

$$\frac{I_{Lout}}{\text{Duty} \bullet V_{IN}} = \frac{1}{Z_{OUT}}$$

which leads to the transfer function of

$$\frac{I_{Lout}}{Duty} = \frac{V_{IN}}{Z_{OUT}}$$

$Z_{OUT}$  is dominated by the output inductor at frequencies above the L • C resonant frequency, and results in a single pole rolloff due to that inductor, which is what is shown in U-140 as the "V<sub>IN/S</sub> • L<sub>OUT</sub>" term. The complete impedance function includes the output Inductor, Capacitor, Sense Resistor, Inductor Resistance, ESR, ESL and Load Resistance. The parasitic resistances will help dampen the response at the resonant frequency and should not be ignored.

The output impedance is given by:

$$Z_{OUT} = s \cdot L_{OUT} + R_{S} + RLout + \left(\frac{1}{s \cdot C} + ESR + s \cdot ESL\right) \cdot RL$$

$$\left(\frac{1}{s \cdot C} + ESR + s \cdot ESL\right) + RL$$

where

R<sub>Lout</sub> = DC Resistance of output inductor

C = Output capacitance

ESR = Output capacitance ESR

ESL = Output capacitance ESL

R<sub>L</sub> = Load Resistance

Now, solving for the control-to-output gain,  $G_P$  (of the Current Loop only),

$$G_{p} = \left(\frac{\text{Duty}}{\text{V}_{CA}}\right) \bullet \left(\frac{\text{V}_{RS}}{\text{I}_{Lout}}\right) \bullet \left(\frac{\text{I}_{Lout}}{\text{Duty}}\right) \bullet \text{GCSA}$$

can be simplified as

$$G_{P} = \left(\frac{1}{V_{A}}\right) \bullet (R_{SENSE}) \bullet \left(\frac{V_{IN}}{Z_{OUT}}\right) \bullet G_{CSA}$$

U-140 states to multiply the control-to-output power loop gain, Gp, by the gain of the Current Amplifier to achieve the overall current loop gain.

$$Loop = G_{P} \bullet G_{CA} = \left[ \left( \frac{1}{V_{S}} \right) \bullet \left( \frac{V_{IN}}{Z_{OUT}} \right) \bullet (R_{S}) \right]$$

$$\bullet G_{CSA} \bullet \left[ \frac{V_{S} \bullet L_{OUT}}{(T_{S} \bullet T_{D}) \bullet R_{S} \bullet (V_{O} + V_{F}) \bullet G_{CSA}} \right]$$

Equating the current loop gain to 1 will yield the loop crossover frequency,  $F_C$ .

$$1 = \left[ \left( \frac{1}{V_{S}} \right) \bullet \left( \frac{V_{IN}}{Z(2 \bullet \pi \bullet F_{C})} \right) \bullet (R_{S}) \bullet G_{CSA} \right]$$

$$\bullet \left[ \frac{V_{S} \bullet L_{OUT}}{(T_{S} - T_{D}) \bullet R \bullet (V_{O} + V_{F}) \bullet G_{CSA}} \right]$$

$Z_{OUT}$  is dominated by the output inductor in the region of the crossover frequency, and therefore  $Z_{OUT(fc)}$  can be replaced by s •  $L_{OUT}$

Solving for F<sub>C</sub> and simplifying yields:

$$F_{C} = \frac{V_{IN}}{2 \bullet \pi \bullet (V_{O} + V_{F}) \bullet (T_{S} - T_{D})}$$

Notice that  $L_{OUT}$  falls out of the equation, and therefore the only "Load" dependency is in the value of Vf. This is true ONLY if Lout is Constant with load current. If a swinging choke is used, then Lout cannot drop out of the equation.

The crossover frequency of the current loop can therefore be determined by

$$\frac{V_{IN} \bullet R_S}{V_S \bullet 2 \bullet \pi \bullet F_C \bullet L_{OUT}} \bullet G_{CSA} \bullet G_{CA} = 1$$

and therefore

$$F_{C} = \frac{V_{IN} \bullet R_{S}}{V_{S} \bullet 2 \bullet \pi \bullet L_{OUT}} \bullet G_{CSA} \bullet G_{CA}$$

The crossover frequency of the current loop will therefore vary as a function of load, with the minimum crossover frequency at the maximum input voltage and maximum value of  $L_{OUT}$ , or at minimum load.

Solving for the crossover frequency:

$$F_{Cmax} = \frac{V_{Imax} \bullet R_S}{V_S \bullet 2 \bullet \pi \bullet L_{OUTmin}} \bullet G_{CSA} \bullet G_{CA}$$

$$=\frac{5.25V \bullet 0.01\Omega}{1.8V \bullet 2 \bullet \pi \bullet 120\text{mH}} \bullet 7.87 \bullet 8.47$$

$$F_{Cmin} = \frac{V_{Imin} \bullet R_S}{V_S \bullet 2 \bullet \pi \bullet L_{OUTmax}} \bullet G_{CSA} \bullet G_{CA}$$

$$=\frac{4.75V \bullet 0.01\Omega}{1.8V \bullet 2 \bullet \pi \bullet 24.0\mu H} \bullet 7.87 \bullet 8.47$$

= 11.7kHz

where the input voltage is  $+5V \pm 5\%$

Step 6: Add the pole-zero compensation into the Current Amplifier by solving for  $C_{ZERO}$  (C25 + C28) and  $C_{POLE}$  (C27), and solve for the current loop transfer function.

The zero should be placed at or below the minimum current loop crossover frequency,  $F_{Cmin}$ . The value of  $C_{ZERO}$  is determined by

Czero =

$$\frac{1}{2 \cdot \pi \cdot F_{Cmin} \cdot R24}$$

$$= \frac{1}{2 \cdot \pi \cdot 11.7 \text{kHz} \cdot 10.5 \text{k}\Omega}$$

$$= 1296 \text{pF}$$

Use  $C_{ZERO} = C25 + C28 = 1220pF$  (2 capacitors are used to allow tuning of this frequency)

The pole should be placed at  $F_S/2$ . The value of  $C_{POLE}$  is determined by

$$C_{\text{POLE}} = \frac{C_{\text{ZERO}}}{(2 \bullet \pi \bullet F_{\text{S}}/2 \bullet \text{R24} \bullet C_{\text{ZERO}}) - 1}$$

= 173pF Use C<sub>POLE</sub> = C27 = 180pF

The transfer function of the compensated current amplifier is

$G_{CAs} =$

$$\frac{\text{R24} \bullet (\text{C}_{\text{POLE}} + \text{C}_{\text{ZERO}}) \bullet \text{s} + 1}{\text{s} \bullet (\text{C}_{\text{ZERO}} \bullet \text{R23} \bullet (\text{R24} \bullet \text{s} \bullet \text{C}_{\text{POLE}} + 1)}$$

and the overall current loop is determined by multiplying the control-to-output transfer function by the current amplifier transfer function. or

$$Loop = G_{P} \bullet G_{CAS} = \left(\frac{1}{V_{S}} \bullet \frac{V_{IN}}{Z_{OUTS}} \bullet R_{S} \bullet G_{CSA}\right) \bullet G_{CAS}$$

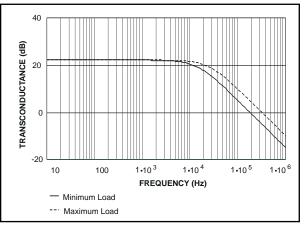

which is plotted in Figure 16.

Figure 16. Current Amplifier and Current Loop Bode Plot - Minimum and Maximum Loads

The lower crossover frequency is above the estimated range of 11.7kHz because the gain of the compensated Current Amplifier is not a flat gain of 8.47 but is slightly higher due to the integrating feedback of the Current Amplifier.

The changes in loop gain at low frequencies is dominated by the changes in load resistance, while the variation at and around the crossover frequency is a function of the change in inductance vs current.

#### Closing the Voltage Loop:

The voltage loop must now be closed according to the guidelines in Unitrode Seminar Topic [7] "Switching Power Supply Control Loop Design". The compensation around the voltage amplifier of this circuit will differ from the seminar topic however by utilizing non-integrating gain [4].

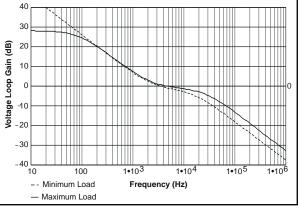

Step 7: Generate a model for the closed current loop transconductance.

> The small signal current loop can be modeled as a fixed gain at low frequencies equal the transconductance forced by the current loop, and having a pole at the current loop crossover frequency, fcl, as shown in Figure 17 below.

Figure 17. Small Signal Current Loop Transfer Function - Min and Max Loads

where the transconductance, TC(s) is determined by

$$\Gamma_{C(s)} = \frac{1}{R_{S} \bullet G_{CSA}} \bullet \left(\frac{1}{1 + \frac{s}{2 \bullet \pi \bullet f_{CL}}}\right)$$

The low frequency gain is the transconductance (remember, transconductance units is  $\Omega^{-1}$ )

$$Gain = \frac{1}{R_{S} \bullet G_{CSA}} = \frac{1}{0.01\Omega \bullet 7.87} = \frac{22.1 \text{dB}}{\Omega}$$

Step 8: Determine the output impedance and power circuit gain, G<sub>Vs</sub>.

> The output impedance is determined by the output capacitance, its parasitics, and the load resistance.

$$\frac{\left(\frac{1}{s \cdot C_{OUT}} + ESR + s \cdot ESL\right) \cdot R_{LOAD}}{\left(\frac{1}{s \cdot C_{OUT}} + ESR + s \cdot ESL\right) + R_{LOAD}}$$

ZVo

$\sqrt{s \cdot C_{OUT}}$  + ESR + s • ES RLOAD

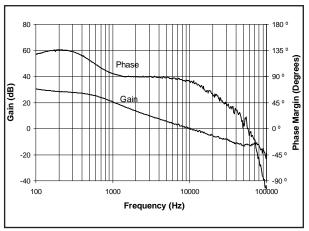

The power circuit gain equals the current loop transconductance times the output impedance, or