# Application Note UCC28950/UCC28951 600-W, Phase-Shifted, Full-Bridge Application Note

# TEXAS INSTRUMENTS

### Michael O'Loughlin

### ABSTRACT

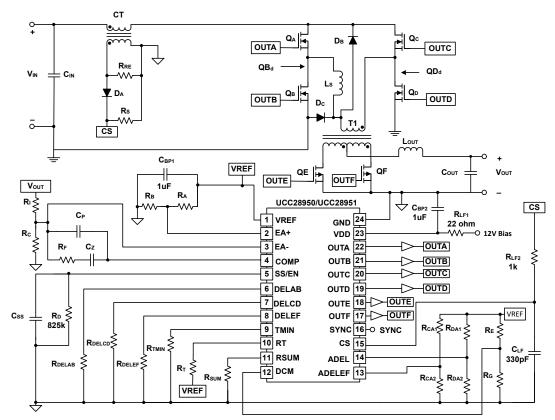

In high-power server applications to meet high-efficiency goals of greater than 92% some power-supply designers have found it easier to use a phase-shifted full-bridge (PSFB) converter (Figure 2-1). This is because the PSFB converter can obtain zero-voltage switching on the primary side of the converter reducing switching losses and increasing overall system efficiency. The purpose of this application note is to review the design of a 600-W, phase-shifted, full-bridge converter , using the UCC28950 or the newer UCC28951 PSFB controller. The design specifications for this design are presented in Table 1-1. Hopefully this information will aid other power supply designers in their efforts to design an efficient phase-shifted, full-bridge converter. Also note there is an Excel Design Tool that goes along with this application note as well to aid in the design process.

# **Table of Contents**

| 1 Design Specifications                                                                               | 2  |

|-------------------------------------------------------------------------------------------------------|----|

| 1 Design Specifications<br>2 Functional Schematic                                                     | 2  |

| 3 Power Budget                                                                                        |    |

| 4 Transformer Calculations (T1)                                                                       |    |

| 5 QA, QB, QC, QD FET Selection                                                                        | 6  |

| 6 Selecting L <sub>S</sub>                                                                            | 7  |

| 7 Output Inductor Selection (L <sub>OUT</sub> )                                                       | 7  |

| 8 Output Capacitance (C <sub>OUT</sub> )                                                              | 8  |

| 9 Select FETs QE and QF                                                                               | 9  |

| 10 Input Capacitance (C <sub>IN</sub> )                                                               |    |

| 11 Setting Up the Current Sense (CS) Network (CT, R <sub>S</sub> , R <sub>RE</sub> , D <sub>A</sub> ) |    |

| 12 Voltage Loop and Slope Compensation                                                                |    |

| 13 Setting Turn-on Delays to Achieve Zero Voltage Switching (ZVS)                                     |    |

| 14 Turning SR FETs-off Under Light Load Conditions                                                    | 21 |

| 15 600 W FSFB Detailed Schematic and Test Data                                                        |    |

| 16 References                                                                                         |    |

| 17 Revision History                                                                                   | 25 |

# List of Figures

| Figure 2-1. UCC28950/UCC28951 Phase-Shifted, Full-Bridge Functional Schematic                             | . 2 |

|-----------------------------------------------------------------------------------------------------------|-----|

| Figure 4-1. T1 Primary and QE and QF FET Currents                                                         |     |

|                                                                                                           |     |

| Figure 9-1. V <sub>g</sub> vs. Q <sub>g</sub> for QE and QF FETs<br>Figure 12-1. Loop Gain and Loop Phase | 15  |

| Figure 13-1. t <sub>ABSET</sub> to Achieve Valley Switching at Light Loads                                |     |

| Figure 13-2. t <sub>CDSET</sub> to Achieve Valley Switching at Light Loads                                | 19  |

|                                                                                                           |     |

| Figure 15-1. Daughter Board Schematic                                                                     | 22  |

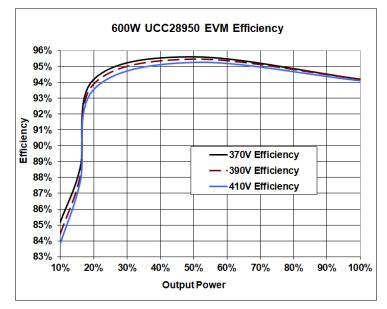

| Figure 15-3. 600-W Phase Shifted Full Bridge Efficiency                                                   |     |

| Figure 15-4. Q4 <sub>g</sub> Q4 <sub>d</sub> , V <sub>IN</sub> = 390 V, I <sub>OUT</sub> = 5 A            |     |

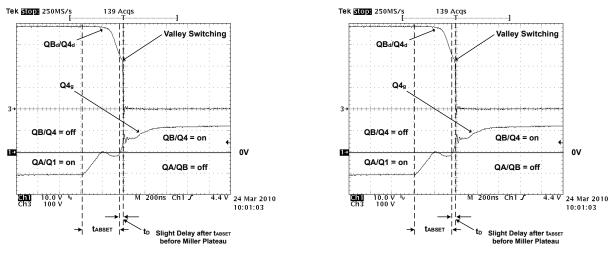

| Figure 15-5. Q3 <sub>a</sub> Q3 <sub>d</sub> , V <sub>IN</sub> = 390 V, I <sub>OUT</sub> = 5 A            |     |

| Figure 15-6. Q4 <sub>a</sub> Q4 <sub>d</sub> , V <sub>IN</sub> = 390 V, I <sub>OUT</sub> = 10 A           | 24  |

| Figure 15-7. Q3 <sub>a</sub> Q3 <sub>d</sub> , V <sub>IN</sub> = 390 V, I <sub>OUT</sub> = 10 A           |     |

| Figure 15-8. Q4 <sub>a</sub> Q4 <sub>d</sub> , V <sub>IN</sub> = 390 V, I <sub>OUT</sub> = 25 A           | 24  |

| Figure 15-9. Q3 <sub>a</sub> Q3 <sub>d</sub> , V <sub>IN</sub> = 390 V, I <sub>OUT</sub> = 25 A           |     |

| Figure 15-10. Q4 <sub>g</sub> Q4 <sub>d</sub> , V <sub>IN</sub> = 390 V, I <sub>OUT</sub> = 25 A | 5 |

|--------------------------------------------------------------------------------------------------|---|

| Figure 15-11. $Q3_g^3 Q3_d$ , $V_{IN} = 390 \text{ V}$ , $I_{OUT} = 25 \text{ A}$                | 5 |

# List of Tables

| Table 1-1. Design Specifications | 2 |

|----------------------------------|---|

|----------------------------------|---|

### Trademarks

All trademarks are the property of their respective owners.

# 1 Design Specifications

| V I                         |                                       |                                                                                                                          |  |  |  |  |

|-----------------------------|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Min                         | Тур                                   | Max                                                                                                                      |  |  |  |  |

| 370 V (V <sub>INMIN</sub> ) | 390 V (V <sub>IN</sub> )              | 410 V (V <sub>INMAX</sub> )                                                                                              |  |  |  |  |

| 11.4 V                      | 12 V (V <sub>OUT</sub> )              | 50 V                                                                                                                     |  |  |  |  |

|                             |                                       | 600 W                                                                                                                    |  |  |  |  |

|                             |                                       | 600 mV ( V <sub>TRAN</sub> )                                                                                             |  |  |  |  |

| 93% (η)                     | 94%                                   |                                                                                                                          |  |  |  |  |

|                             | 200 kHz (f <sub>S</sub> )             |                                                                                                                          |  |  |  |  |

|                             | 370 V (V <sub>INMIN</sub> )<br>11.4 V | 370 V (V <sub>INMIN</sub> )     390 V (V <sub>IN</sub> )       11.4 V     12 V (V <sub>OUT</sub> )       93% (η)     94% |  |  |  |  |

# **2** Functional Schematic

Texas

Instruments

www.ti.com

# 3 Power Budget

To reach the efficiency goal in this PSFB design, careful consideration needs to be taken in selecting electrical components. The devices need to be selected based voltage rating, current rating and power dissipation. The initial step in this design process is to set a power budget ( $P_{BUDGET}$ ) which the total losses of the electrical components selected for the design cannot exceed.

$$P_{BUDGET} = P_{OUT} \times \left(\frac{1-\eta}{\eta}\right) \approx 45.2 \text{ W}$$

(1)

# 4 Transformer Calculations (T1)

The PSFB uses a transformer to deliver energy from the primary to the secondary. The voltage is stepped up or down through the transformers turns ratio (a1).

$$a1 = \frac{N_P}{N_S} = \frac{V_{IN}}{V_{OUT}}$$

(2)

Estimated FET voltage drop (V<sub>RDSON</sub>):

$$V_{\rm RDSON} = 0.3 \, \rm V \tag{3}$$

Select transformer turns based on 70% duty cycle ( $D_{MAX}$ ) at minimum specified input voltage. This will give some room for dropout if a PFC front end is used.

$$D_{MAX} = 70 \%$$

(4)

$$a1 = \frac{(V_{\text{INMIN}} - 2 \times V_{\text{RDSON}}) \times D_{\text{MAX}}}{V_{\text{OUT}} + V_{\text{RDSON}}} \approx 21$$

(5)

Calculated typical duty cycle (D<sub>TYP</sub>) based on average input voltage.

$$D_{\text{TYP}} = \frac{(V_{\text{OUT}} + V_{\text{RDSON}}) \times a1}{(V_{\text{IN}} - 2 \times V_{\text{RDSON}})} \approx 0.66$$

(6)

To keep the RMS current in the output capacitance to a minimum  $L_{OUT}$  will be selected so the inductor ripple current ( $\Delta I_{LOUT}$ ) will be 20% of the DC output current.  $\Delta I_{LOUT}$  is needed to calculate transformer peak and RMS currents

$$\Delta I_{\text{LOUT}} = \frac{P_{\text{OUT}} \times 0.2}{V_{\text{OUT}}} = 10 \text{ A}$$

(7)

Care needs to be taken in selecting a transformer with the correct amount of magnetizing inductance ( $L_{MAG}$ ). The following equations calculate the minimum magnetizing inductance of the primary of the transformer (T1) to ensure the converter operates in peak-current mode control. If  $L_{MAG}$  is too small the magnetizing current could cause the converter to operate in voltage mode control instead of peak-current mode control. This is because the magnetizing current is too large, it will act as a PWM ramp swamping out the current sense signal across R<sub>S</sub>.

$$L_{MAG} \ge \frac{V_{IN} \times (1 - D_{TYP})}{\frac{\Delta I_{LOUT} \times 0.5}{a_1} \times f_s} \approx 2.76 \text{ mH}$$

(8)

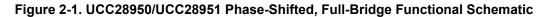

Figure 4-1 shows T1 primary current ( $I_{PRIMARY}$ ) and synchronous rectifiers currents, (QE ( $I_{QE}$ ) and QF ( $I_{QF}$ )), with respect to the synchronous rectifier gate drive currents. Note that  $I_{QE}$  and  $I_{QF}$  are also T1's secondary winding currents as well. Variable D is the converters duty cycle.

Calculate T1 secondary RMS current (I<sub>SRMS</sub>):

$$I_{PS} = \frac{P_{OUT}}{V_{OUT}} + \frac{\Delta I_{LOUT}}{2} \approx 55 \text{ A}$$

$$I_{MS} = \frac{P_{OUT}}{V_{OUT}} - \frac{\Delta I_{LOUT}}{2} \approx 45 \text{ A}$$

(10)

$$I_{MS2} = I_{PS} - \frac{\Delta I_{LOUT}}{4} \approx 50 \text{ A}$$

(11)

Secondary RMS current (I<sub>SRMS1</sub>) when energy is being delivered to the secondary:

$$I_{SRMS1} = \sqrt{\left(\frac{D_{MAX}}{2}\right) \left[I_{PS} \times I_{MS} + \frac{\left(I_{PS} - I_{MS}\right)^2}{3}\right]} \approx 29.6 \text{ A}$$

(12)

Secondary RMS current (I<sub>SRMS2</sub>) when current is circulating through the transformer when QE and QF are both on.

$$I_{SRMS2} = \sqrt{\left(\frac{1 - D_{MAX}}{2}\right) \left[I_{PS} \times I_{MS2} + \frac{\left(I_{PS} - I_{MS2}\right)^2}{3}\right]} \approx 20.3 \text{ A}$$

(13)

Secondary RMS current (I<sub>SRMS3</sub>) caused by the negative current in the opposing winding during freewheeling period, please refer to Figure 4-1.

$$I_{\text{SRMS3}} = \frac{\Delta I_{\text{LOUT}}}{2} \sqrt{\left(\frac{1 - D_{\text{MAX}}}{2 \times 3}\right)} \approx 1.1 \text{ A}$$

(14)

Total secondary RMS current (I<sub>SRMS</sub>):

$$I_{SRMS} = \sqrt{I_{SRMS1}^{2} + I_{SRMS2}^{2} + I_{SRMS3}^{2}} \approx 36.0 \text{ A}$$

(15)

Calculate T1 Primary RMS Current (I<sub>PRMS</sub>):

$$\Delta I_{\text{LMAG}} = \frac{V_{\text{INMIN}} \times D_{\text{MAX}}}{L_{\text{MAG}} \times f_{\text{S}}} \approx 0.47 \text{ A}$$

(16)

$$I_{PP} = \left(\frac{P_{OUT}}{V_{OUT} \times \eta} + \frac{\Delta I_{LOUT}}{2}\right)\frac{1}{a1} + \Delta I_{LMAG} \approx 3.3 \text{ A}$$

(17)

$$I_{MP} = \left(\frac{P_{OUT}}{V_{OUT} \times \eta} - \frac{\Delta I_{LOUT}}{2}\right) \frac{1}{a1} + \Delta I_{LMAG} \approx 2.8 \text{ A}$$

(18)

T1 Primary RMS (IPRMS1) current when energy is being delivered to the secondary.

$$I_{PRMS1} = \sqrt{(D_{MAX}) \left[ I_{PP} \times I_{MP} + \frac{(I_{PP} - I_{MP})^2}{3} \right]} \approx 2.5 \text{ A}$$

(19)

T1 Primary RMS (I<sub>PRMS2</sub>) current when the converter is free wheeling.

$$I_{MP2} = I_{PP} - \left(\frac{\Delta I_{LOUT}}{2}\right) \frac{1}{a1} \approx 3.0 \text{ A}$$

<sup>(20)</sup>

$$I_{PRMS2} = \sqrt{\left(1 - D_{MAX}\right) \left[I_{PP} \times I_{MP2} + \frac{\left(I_{PP} - I_{MP2}\right)^2}{3}\right]} \approx 1.7 A$$

(21)

Total T1 primary RMS current (I<sub>PRMS</sub>)

$$I_{PRMS} = \sqrt{I_{PRMS1}^2 + I_{PRMS2}^2} \approx 3.1 \text{ A}$$

(22)

The transformer calculations were given to Vitec a magnetic manufacturer to design a custom transformer to meet our design requirements. The transformer they designed for this application is part number 75PR8107 and the transformer has the following specifications.

| QA, QB, QC, QD FET Selection                                                                                                                                                                                                                                                                                           | TEXAS<br>INSTRUMENTS<br>www.ti.com |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|

| a1 = 21                                                                                                                                                                                                                                                                                                                | (23)                               |

| $L_{MAG} = 2.8 \text{ mH}$                                                                                                                                                                                                                                                                                             | (24)                               |

| Measured leakage inductance on the Primary:                                                                                                                                                                                                                                                                            |                                    |

| $L_{LK} = 4 uH$                                                                                                                                                                                                                                                                                                        | (25)                               |

| Transformer Primary DC resistance:                                                                                                                                                                                                                                                                                     |                                    |

| $DCR_P = 0.215 \Omega$                                                                                                                                                                                                                                                                                                 | (26)                               |

| Transformer Secondary DC resistance:                                                                                                                                                                                                                                                                                   |                                    |

| $DCR_S = 0.58 \Omega$                                                                                                                                                                                                                                                                                                  | (27)                               |

| Estimated transform losses (P <sub>T1</sub> ) are twice the copper loss.                                                                                                                                                                                                                                               |                                    |

| Note                                                                                                                                                                                                                                                                                                                   |                                    |

| This is just an estimate and the total losses can vary based on magnetic design.                                                                                                                                                                                                                                       |                                    |

| $P_{T1} \approx 2 \times (I_{PRMS}^2 \times DCR_P + 2 \times I_{SRMS}^2 \times DCR_S) \approx 7.0 W$                                                                                                                                                                                                                   | (28)                               |

| Calculate remaining power budget:                                                                                                                                                                                                                                                                                      |                                    |

| $P_{BUDGET} = P_{BUDGET} - P_{T1} \approx 38.1 W$                                                                                                                                                                                                                                                                      | (29)                               |

| 5 QA, QB, QC, QD FET Selection                                                                                                                                                                                                                                                                                         |                                    |

| The FETs to drive the HBridge (QAQD) need to selected based on maximum drain t $(V_{dsQA_max})$ and peak drain to source current $(I_{dsQA_max})$ .                                                                                                                                                                    | o source voltage                   |

| $V_{dsQA_max} \ge V_{INMAX} = 410 V$                                                                                                                                                                                                                                                                                   | (30)                               |

| $I_{dsQA_max} \ge I_{PP} = 3.3 \text{ A}$                                                                                                                                                                                                                                                                              | (31)                               |

| The FETs then need to be selected based on efficiency goals and FET power dissipa error process. Equations 32 through 38 are used to estimate P <sub>QA</sub> based on FET data our efficiency goals, we selected a 20 A, 650 V, CoolMOS FETs from Infineon that ha W and would enable us to hit our efficiency goals. | sheet parameters. To meet          |

| In this design, to meet efficiency and voltage requirements 20 A, 650 V, CoolMOS FE chosen for QAQD.                                                                                                                                                                                                                   | Ts from Infineon were              |

| FET drain to source on resistance:                                                                                                                                                                                                                                                                                     |                                    |

| $R_{ds(on)QA} = 0.220 \ \Omega$                                                                                                                                                                                                                                                                                        | (32)                               |

| FET Specified C <sub>OSS</sub> :                                                                                                                                                                                                                                                                                       |                                    |

| $C_{OSS_QA_SPEC} = 780 \text{ pF}$                                                                                                                                                                                                                                                                                     | (33)                               |

| Voltage across drain-to-source ( $V_{dsQA}$ ) where $C_{OSS}$ was measured, data sheet param                                                                                                                                                                                                                           | neter:                             |

| $V_{dsQA} = 25V$                                                                                                                                                                                                                                                                                                       | (34)                               |

| Calculate average C <sub>oss</sub> [2]:                                                                                                                                                                                                                                                                                |                                    |

UCC28950/UCC28951 600-W, Phase-Shifted, Full-Bridge Application Note

(35)

$$C_{OSS_QA_AVG} = C_{OSS_QA_SPEC} \sqrt{\frac{V_{dsQA}}{V_{INMAX}}} \approx 193 \text{ pF}$$

QA FET gate charge:

$QA_g = 15 \text{ nC}$ (36)

Voltage applied to FET gate to activate FET:

$$V_{g} = 12 V$$

(37)

Calculate QA losses (P<sub>QA</sub>) based on R<sub>ds(on)QA</sub> and gate charge (QA<sub>g</sub>):

$$P_{QA} = I_{PRMS}^{2} \times R_{ds(on)QA} + 2 \times QA_{g} \times V_{g} \times \frac{fs}{2} \approx 2.1 W$$

(38)

Recalculate power budget:

$P_{BUDGET} = P_{BUDGET} - 4 \times P_{QA} \approx 29.7 \text{ W}$ (39)

### 6 Selecting L<sub>S</sub>

Calculating the shim inductor (L<sub>S</sub>) is based on the amount of energy required to achieve zero voltage switching. This inductor needs to able to deplete the energy from the parasitic capacitance at the switch node. The following equation selects L<sub>S</sub> to achieve Zero Voltage Switching (ZVS) at 100% load down to 50% load based on the primary FET's average total  $C_{OSS}$  at the switch node.

There might be more parasitic capacitance than was estimated at the switch node and  $L_S$  might have to be adjusted based on the actual parasitic capacitance in the final design.

Note

$$L_{S} \ge \left(2 \times C_{OSS\_QA\_AVG}\right) \frac{V_{INMAX}^{2}}{\left(\frac{I_{PP}}{2} - \frac{\Delta I_{LOUT}}{2 \times a1}\right)^{2}} - L_{LK} \approx 26 \text{ uH}$$

(40)

For this design Vitec Electronics Corporation designed a customer  $L_S$ , part number 60PR964. 60PR964 had a DC resistance (DCR<sub>LS</sub>) of 27 m $\Omega$ .

$DCR_{LS} = 27 \text{ m}\Omega \tag{41}$

Estimate L<sub>S</sub> power loss (P<sub>LS</sub>) and readjust remaining power budget:

$P_{LS} = 2 \times I_{PRMS}^{2} \times DCR_{LS} \approx 0.5 W$ (42)

$$P_{BUDGET} = P_{BUDGET} - P_{LS} \approx 29.2 \text{ W}$$

(43)

# 7 Output Inductor Selection (L<sub>OUT</sub>)

To keep the RMS current in the output capacitance to a minimum  $L_{OUT}$  will be designed for and inductor ripple current ( $\Delta I_{LOUT}$ ) will be 20% of the DC output current.

$$\Delta I_{\text{LOUT}} = \frac{P_{\text{OUT}} \times 0.2}{V_{\text{OUT}}} = \frac{600W \times 0.2}{12V} \approx 10 \text{ A}$$

(44)

$$L_{OUT} = \frac{V_{OUT} \times (1 - D_{TYP})}{\Delta I_{LOUT} \times f_{s}} \approx 2 \text{ uH}$$

(45)

Calculate output inductor RMS current (I<sub>LOUT RMS</sub>):

$I_{\text{LOUT}_\text{RMS}} = \sqrt{\left(I_{\text{OUT}}\right)^2 + \left(\frac{\Delta I_{\text{LOUT}}}{\sqrt{3}}\right)^2} = 50.3 \text{ A}$

The L<sub>OUT</sub> inductor requirements to meet these design specifications was given to Vitec Electronics Corp and they design a custom inductor for this design that met are design requirements, part number 75PR108. The 75PR108 had a DC resistance (DCR<sub>LOUT</sub>) of 750  $\mu\Omega$

$$DCR_{LOUT} = 750 \text{ u}\Omega \tag{47}$$

Estimate output inductor losses ( $P_{LOUT}$ ) and recalculate power budget. Note  $P_{LOUT}$  is an estimate of the inductor losses and was estimated to twice the copper loss. Note this may vary based on magnetic manufactures. It is advisable to double check the magnetic loss with the magnetic manufacture.

$$P_{LOUT} = 2 \times I_{LOUT_{RMS}}^{2} \times DCR_{LOUT} \approx 3.8 W$$

(48)

$$P_{BUDGET} = P_{BUDGET} - P_{LOUT} \approx 25.4 \, W \tag{49}$$

# 8 Output Capacitance (C<sub>OUT</sub>)

The output capacitor is being selected based on holdup time  $(t_{HU})$  and load transient requirements.

$t_{HU}$  is the time it takes  $L_{OUT}$  to change 90% of its full load current:

$$t_{HU} = \frac{\frac{L_{OUT} \times P_{OUT} \times 0.9}{V_{OUT}}}{V_{OUT}} = 7.5 \ \mu s$$

(50)

During load transients most of the current will immediately go through the capacitors equivalent series resistance (ESR<sub>COUT</sub>). The following equations are used to select ESR<sub>COUT</sub> and C<sub>OUT</sub> based on a 90% load step in current. The ESR is selected for 90% of the allowable transient voltage (V<sub>TRAN</sub>), while the output capacitance (C<sub>OUT</sub>) is selected for 10% of V<sub>TRAN</sub>.

$$\text{ESR}_{\text{COUT}} \le \frac{V_{\text{TRAN}} \times 0.9}{\frac{P_{\text{OUT}} \times 0.9}{V_{\text{OUT}}}} = 12 \text{ m}\Omega$$

(51)

$$C_{OUT} \ge \frac{\frac{P_{OUT} \times 0.9 \times t_{HU}}{V_{OUT}}}{\frac{V_{OUT}}{V_{TRAN} \times 0.1}} \approx 5.6 \text{ mF}$$

(52)

Before selecting the output capacitance it is also required to calculate the output capacitor RMS current ( $I_{COUT RMS}$ ).

$$I_{\text{COUT}_RMS} = \frac{\Delta I_{\text{LOUT}}}{\sqrt{3}} \approx 5.8 \text{ A}$$

(53)

To meet our design requirements five 1500- $\mu$ F, aluminum electrolytic capacitors were chosen for the design from United Chemi-Con, part number EKY-160ELL152MJ30S. These capacitors had an ESR of 31 m $\Omega$ . The five capacitors when used in series will have an equivalent ESR of 6.2 mOhm which meets are design requirements.

Number of output capacitors:

Total output capacitance:

8

$C_{OUT} = 1500 uF \times n \approx 7500 uF$

Effective output capacitance ESR:

(55)

(46)

$$ESR_{COUT} = \frac{31m\Omega}{n} = 6.2 \text{ m}\Omega$$

Calculate output capacitor loss (P<sub>COUT</sub>): (56)

$$P_{COUT} = I_{COUT_{RMS}}^{2} \times ESR_{COUT} \approx 0.21 \, W$$

(57)

Recalculate remaining Power Budget:

$$P_{BUDGET} = P_{BUDGET} - P_{COUT} \approx 25.2 \text{ W}$$

(58)

### 9 Select FETs QE and QF

The synchronous FETs are chosen based on current and voltage ratings; as well as, power dissipation to meet the designs efficiency goals. This can be a trial an error process. We selected an evaluated a 75-V, 120-A FETs, from Fairchild, part number FDP032N08 to see if they could be used for synchronous FETs QE and QF to hit our efficiency goals. After estimating the total FET losses and power budget it was determined that these FETs could be used in this design.

$$QE_{g} = 152nC$$

(59)

$$R_{ds(on)QE} = 3.2 \text{ m}\Omega \tag{60}$$

Calculate average FET  $C_{OSS}$  ( $C_{OSS\_QE\_AVG}$ ) based on the data sheet parameters for  $C_{OSS}$  ( $C_{OSS\_SPEC}$ ), and drain to source voltage where  $C_{OSS\_SPEC}$  was measured ( $V_{ds\_spec}$ ), and the maximum drain to source voltage in the design ( $V_{dsQE}$ ) that will be applied to the FET in the application.

Voltage across FET QE and QF when they are off:

$$V_{dsQE} = \frac{2 \times V_{INMAX}}{a1} \approx 39V$$

(61)

Voltage where FET C<sub>OSS</sub> is specified and tested in the FET data sheet:

$$V_{ds spec} = 25 V$$

(62)

Specified output capacitance from FET data sheet:

$$C_{OSS\_SPEC} = 1810 \text{ pF}$$

(63)

Average QE and QF C<sub>OSS</sub> [2]:

$$C_{OSS\_QE\_AVG} = C_{OSS\_SPEC} \sqrt{\frac{V_{dsQE}}{V_{ds\_spec}}} \approx 1.6 \text{ nF}$$

(64)

QE and QF RMS current:

$$I_{QE_RMS} = I_{SRMS} = 36.0 \text{ A}$$

(65)

To estimate FET switching loss the V<sub>g</sub> vs.  $Q_g$  curve from the FET data sheet needs to be studied. First the gate charge at the beginning of the miller plateau needs to be determined ( $QE_{MILLER\_MIN}$ ) and the gate charge at the end of the miller plateau ( $QE_{MILLER\_MAX}$ ) for the given V<sub>DS</sub>.

(67)

### Figure 9-1. Vg vs. Qg for QE and QF FETs

Maximum gate charge at the end of the miller plateau:

| $QE_{MILLER_MAX} \approx 100 \text{ nC}$ (6) | 66) |

|----------------------------------------------|-----|

|----------------------------------------------|-----|

Minimum gate charge at the beginning of the miller plateau:

| $QE_{MILLER MIN} \approx 52 \text{ nC}$ |  |

|-----------------------------------------|--|

|-----------------------------------------|--|

#### Note

The FETs in this design were driven with UCC27324 setup to drive 4-A (I<sub>P</sub>) of gate drive current.

$$I_{\rm P} \approx 4 {\rm A}$$

(68)

Estimated FET V<sub>ds</sub> rise and fall time:

$$t_r \approx t_f = \frac{100nC - 52nC}{\frac{l_P}{2}} = \frac{48nC}{\frac{4A}{2}} \approx 24 \text{ ns}$$

(69)

Estimate QE and QF FET Losses (PQE):

$$P_{QE} = I_{QE_{RMS}}^{2} \times R_{ds(on)QE} + \frac{P_{OUT}}{V_{OUT}} \times V_{dsQE}(t_{r} + t_{f})\frac{f_{s}}{2} + 2 \times C_{OSS_{QE}_{AVG}} \times V_{dsQE}^{2}\frac{f_{s}}{2} + 2 \times Q_{gQE} \times V_{gQE}\frac{f_{s}}{2}$$

(70)

$$P_{QE} \approx 9.3 \text{ W}$$

(71)

Recalculate the power budget and check remaining power budget to hit efficency goal.

$$P_{BUDGET} = P_{BUDGET} - 2 \times P_{QE} \approx 6.5 W$$

(72)

# **10 Input Capacitance (CIN)**

This design was being fed by a PFC pre-regulator and the input capacitor ( $C_{IN}$ ) will need to be selected based on holdup requirements; as well as, ripple current and voltage requirements.

#### Note

The delay time needed to achieve ZVS can act as a duty cycle clamp (D<sub>CLAMP</sub>).

Calculate tank frequency:

$$f_{\rm R} = \frac{1}{2\pi\sqrt{L_{\rm S} \times \left(2 \times C_{\rm OSS\_QA\_AVG}\right)}}$$

(73)

Estimated delay time:

$$t_{\text{DELAY}} = \frac{2}{f_{\text{R}} \times 4} \approx 314 \text{ns}$$

(74)

Effective duty cycle clamp (D<sub>CLAMP</sub>):

$$D_{\text{CLAMP}} = \left(\frac{1}{\text{fs}} - t_{\text{DELAY}}\right) \times \text{fs} = 94\%$$

(75)

$V_{DROP}$  is the minimum input voltage where the converter can still maintain output regulation. The converter's input voltage would only drop down this low during a brownout or line-drop condition if this converter was following a PFC pre-regulator.

$$V_{DROP} = \left(\frac{2 \times D_{CLAMP} \times V_{RDSON} + a1 \times (V_{OUT} + V_{RDSON})}{D_{CLAMP}}\right) = 276.2 \text{ V}$$

(76)

C<sub>IN</sub> was calculated based on one line cycle of holdup:

$$C_{\rm IN} \ge \frac{2 \times P_{\rm OUT} \times \frac{1}{60 \text{Hz}}}{\left(V_{\rm IN}^2 - V_{\rm DROP}^2\right)} \approx 364 \text{ uF}$$

(77)

Calculate high frequency input capacitor RMS current (I<sub>CINRMS</sub>).

$$I_{\text{CINRMS}} = \sqrt{I_{\text{PRMS1}}^2 - \left(\frac{P_{\text{OUT}}}{V_{\text{INMIN}} \times a1}\right)^2} = 1.8 \text{ A}$$

(78)

To meet the input capacitance and RMS current requirements for this design we chose a 330-µF capacitor from Panasonic part number EETHC2W331EA.

$$C_{\rm IN} = 330 \, {\rm uF}$$

(79)

This capacitor had a high frequency (ESR<sub>CIN</sub>) of 150 m $\Omega$  this was measured with an impedance analyzer at both 120 and 200 kHz.

$$ESR_{CIN} = 0.150 \ \Omega \tag{80}$$

Estimate C<sub>IN</sub> power dissipation (P<sub>CIN</sub>):

$$P_{CIN} = I_{CINRMS}^{2} \times ESR_{CIN} = 0.5 W$$

(81)

Recalculate remaining power budget:

$P_{BUDGET} = P_{BUDGET} - P_{CIN} \approx 6.0 W$

There is roughly 6.0 W left in the power budget left for the current sensing network, and biasing the control device and all resistors supporting the control device.

# 11 Setting Up the Current Sense (CS) Network (CT, R<sub>S</sub>, R<sub>RE</sub>, D<sub>A</sub>)

The current sense transforer (CT) chosen for this design had a turn's ratio (a2) of 100:1. This transformer was selected to attenenuate the T1's primary current for current sensing to reduce power disipation in the current sense resistor ( $R_S$ ) improving system efficency.

$$a2 = \frac{l_P}{l_S} = 100 \tag{83}$$

Calculate nominal peak current (I<sub>P1</sub>) at V<sub>INMIN</sub>:

Peak primary current:

$$I_{P1} = \left(\frac{POUT}{VOUT \times \eta} + \frac{\Delta ILOUT}{2}\right)\frac{1}{a1} + \frac{V_{INMAX} \times D_{MAX}}{L_{MAG} \times 2 \times f_S} \approx 3.3 \text{ A}$$

(84)

The voltage where peak current limit will trip.

$$V_{\rm P} = 2V$$

(85)

Calculate current sense resistor ( $R_S$ ) and leave 200 mV for slope compensation:

$$R_{\rm S} = \frac{V_{\rm P} - 0.2V}{\frac{\rm I_{\rm PEAK}}{\rm a2} \times 1.1} \approx 49.9 \,\Omega \tag{86}$$

Select a standard resistor for R<sub>S</sub>:

$$R_{\rm S} = 48.7 \,\Omega$$

(87)

Estimate power loss (P<sub>RS</sub>)for R<sub>S</sub>:

$$P_{\rm RS} = \left(\frac{I_{\rm PRMS1}}{a2}\right)^2 \times R_{\rm S} \approx 0.03 \,\,\rm W \tag{88}$$

Calculate maximum reverse voltage (V<sub>DA</sub>) on D<sub>A</sub>:

$$V_{DA} = V_P \times \frac{D_{CLAMP}}{1 - D_{CLAMP}} \approx 29.8 V$$

(89)

Estimate  $D_A$  power loss ( $P_{DA}$ ):

$$P_{DA} = \frac{P_{OUT} \times 0.6V}{V_{INMIN} \times \eta \times a2} \approx 0.01 \text{ W}$$

(90)

Calculate R<sub>S</sub> reset resistor R<sub>RE</sub>:

Resistor  $R_{RE}$  is used to reset the current sense transformer CT.

$$R_{RE} = 100 \times R_S = 4.87 \text{ k}\Omega \tag{91}$$

Resistor  $R_{LF}$  and capacitor  $C_{LF}$  form a low pass filter for the current sense signal (Pin 15). For this design we chose the following values. This filter has a low frequency pole ( $f_{LFP}$ ) at 482 kHz. This should work for most applications but maybe adjusted to suit individual layouts and EMI present in the design.

12 UCC28950/UCC28951 600-W, Phase-Shifted, Full-Bridge Application Note

(82)

Voltage Loop and Slope Compensation

$$R_{LF} = 1 k\Omega$$

(92)

$C_{LF} = 330 \text{ pF}$  (93)

$f_{LFP} = \frac{1}{2\pi f \times R_{LF} \times C_{LF}} = 482 \text{ kHz}$  (94)

The current sense network dissipated roughly 0.04 W and had very little effect on the power budget.

$$P_{BUDGET} \approx P_{BUDGET} - P_{RS} - P_{DA} \approx 5.96 \text{ W}$$

(95)

### 12 Voltage Loop and Slope Compensation

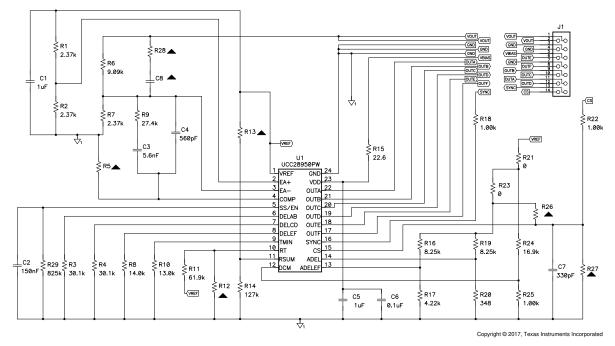

The UCC28950/1 VREF output (Pin 1) needs a high frequency bypass capacitor to filter out high frequency noise. This pin needs at least 1  $\mu$ F of high frequency bypass capacitance (C<sub>BP1</sub>). Please refer to figure 1 for proper placement.

$$C_{BP1} = 1 \text{ uF}$$

The voltage amplifier reference voltage (Pin 2, EA +) can be set with a voltage divider ( $R_A$ ,  $R_B$ ), for this design example we are going to set the error amplifier reference voltage (V1) to 2.5 V. Select a standard resistor value for  $R_B$  and then calculate resistor value  $R_A$ .

UCC28950/1/1 reference voltage:

$$V_{\rm REF} = 5 \, \rm V \tag{97}$$

Set voltage amplifier reference voltage:

$$V1 = 2.5 V$$

(98)

$$R_{\rm B} = 2.37 \ \rm k\Omega \tag{99}$$

$$R_{A} = \frac{R_{B} \times (V_{REF} - V1)}{V1} = 2.37 \text{ k}\Omega$$

(100)

Voltage divider formed by resistor  $R_C$  and  $R_I$  are chosen to set the DC output voltage (V<sub>OUT</sub>) at Pin 3 (EA-). Select a standard resistor for  $R_C$ :

$R_{\rm C} = 2.37 \, \rm k\Omega \tag{101}$

Calculate R<sub>I</sub>:

$$R_{I} = \frac{Rc \times (V_{OUT} - V1)}{V1} \approx 9 \text{ k}\Omega$$

(102)

Then choose a standard resistor for R<sub>I</sub>:

$$R_{\rm I} = 9.09 \,\rm k\Omega \tag{103}$$

Compensating the feedback loop can be accomplished by properly selecting the feedback components ( $R_F$ ,  $C_Z$  and  $C_P$ ). These components are placed as close to pin 3 and 4 as possible of the UCC28950/1.

Calculate load impedance at 10% load (R<sub>LOAD</sub>):

$$R_{\text{LOAD}} = \frac{V_{\text{OUT}}^2}{P_{\text{OUT}} \times 0.1} = 2.4 \,\Omega \tag{104}$$

Approximation of control to output transfer function  $(G_{CO}(f))$  as a function of frequency:

$$G_{CO(f)} \approx \frac{\Delta V_{OUT}}{\Delta V_{C}} = a1 \times a2 \times \frac{R_{LOAD}}{R_{S}} \times \left(\frac{1 + 2\pi j \times f \times ESR_{COUT} \times C_{OUT}}{1 + 2\pi j \times f \times R_{LOAD} \times C_{OUT}}\right) \times \frac{1}{1 + \frac{S(f)}{2\pi \times f_{PP}} + \left(\frac{S(f)}{2\pi \times f_{PP}}\right)^{2}}$$

(105)

Double pole frequency of G<sub>CO</sub>(f):

$$f_{\rm PP} \approx \frac{fs}{4} = 50 \text{ kHz}$$

(106)

Angular velocity:

$$S(f) = 2\pi \times j \times f \tag{107}$$

Compensate the voltage loop with type 2 feedback network. The following transfer function is the compensation gain as a function of frequency ( $G_C(f)$ ). Please refer to Figure 2-1 for component placement.

$$G_{C(f)} = \frac{\Delta V_C}{\Delta V_{OUT}} = \frac{2\pi j \times f \times R_F \times C_Z + 1}{2\pi j \times f \times (C_Z + C_P)R_I \left(\frac{2\pi j \times f \times C_Z \times C_P \times R_F}{C_Z + C_P} + 1\right)}$$

(108)

(109)

Calculate voltage loop feedback resistor ( $R_F$ ) based on crossing the voltage ( $f_C$ ) loop over at a 10<sup>th</sup> of the double pole frequency ( $f_{PP}$ ).

$$f_{\rm C} = \frac{f_{\rm PP}}{10} = 5 \,\rm kHz$$

(110)

$$R_{\rm F} = \frac{R_{\rm I}}{G_{\rm CO}\left(\frac{f_{\rm PP}}{10}\right)} \approx 27.9 \,\rm k\Omega \tag{111}$$

Select a standard resistor for R<sub>F</sub>.

$$R_{\rm F}\approx 27.4\,{\rm k}\Omega \tag{112}$$

Calculate the feedback capacitor (C<sub>Z</sub>) to give added phase at crossover.

$C_{Z} = \frac{1}{2 \times \pi \times R_{F} \times \frac{f_{C}}{5}} \approx 5.8 nF$ (113)

$$C_Z = 5.6nF \tag{114}$$

Select a standard capacitance value for the design.

Put a pole at two times f<sub>C</sub>.

$$C_{\rm P} = \frac{1}{2 \times \pi \times R_{\rm F} \times f_{\rm C} \times 2} \approx 580 \rm{pF}$$

(115)

Select a standard capacitance value for the design.

$$C_{\rm P} = 560 \rm pF$$

(116)

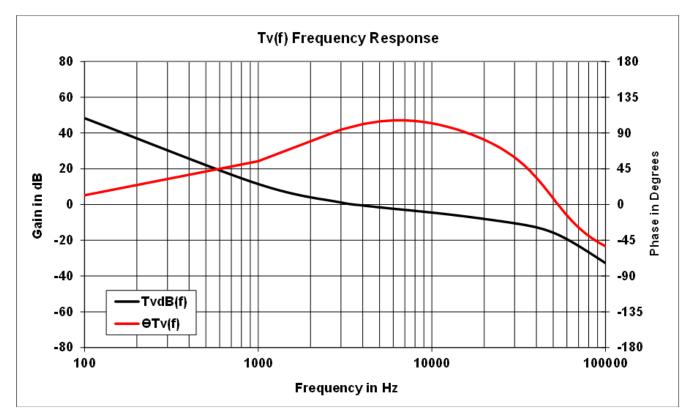

Loop gain as a function of frequency  $(T_V(f))$  in dB.

$$T_V dB(f) = 20 \log(|G_C(f) \times G_{CO}(f)|)$$

(117)

Plot theoretical loop gain and phase to graphically check for loop stability (Figure 11-1). The theoretical loop gain crossed over at roughly 3.7 kHz with a phase margin of greater than 90 degrees.

#### Note

It is wise to check your loop stability of your final design with transient testing and/or a network analyzer and adjust the compensation  $(G_C(f))$  feedback as necessary.

To limit over shoot during power up the UCC28950/1 has a soft-start function (SS, Pin 5) which in this application was set for a soft start time of 15 ms ( $t_{SS}$ ).

$$t_{ss} = 15 \text{ ms}$$

(118)

$$C_{ss} = \frac{t_{ss} \times 25uA}{V1 + 0.55} \approx 123 \text{ nF}$$

(119)

Select a standard capacitor for the design.

$$C_{ss} = 150 \text{ nF}$$

(120)

The UCC28950/1 also provides slope compensation for peak current mode control (Pin 12). This can be set by setting  $R_{SUM}$  with the following equations. The following equations will calculate the required amount of slope compensation ( $V_{SLOPE}$ ) that is needed for loop stability.

#### Note

The change in magnetizing current on the primary  $\Delta IL_{MAG}$  contributes to slope compensation.

$$\Delta IL_{MAG} = \frac{V_{IN}(1 - D_{TYP})}{L_{MAG} \times fs} = 234 \text{ mA}$$

(121)

To help improve noise immunity  $V_{SLOPE}$  is set to have a total slope that will equal 10% of the maximum current sense signal (0.2 V) over one inductor switching period.

If  $V_{SLOPE2} < V_{SLOPE1}$  set  $V_{SLOPE} = V_{SLOPE1}$

Select a standard resistor for RSUM

$R_{\text{SUM}} = 127 \ \text{k}\Omega$

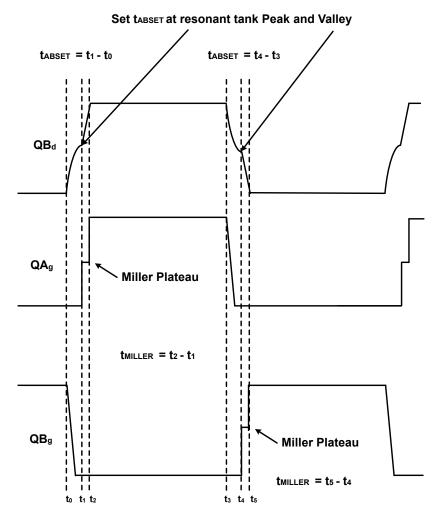

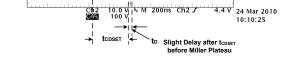

This application note presents a fixed delay approach to achieving ZVS from 100% load down to 50% load. When the converter is operating below 50% load the converter will be operating in valley switching. In order to achieve zero voltage switching on switch node of QB<sub>d</sub>, the turn-on (t<sub>ABSET</sub>) delays of FETs QA and QB needs to be initially set based on the interaction of  $L_{S}$  and the theoretical switch node capacitance. The following equations are used to set t<sub>ABSET</sub> initially.

Equate shim inductance to two times C<sub>0</sub> conacitance.

$$2\pi \times f_{R}L_{S} = \frac{1}{2\pi \times f_{R} \times (2 \times C_{OSS}QA_{AVG})}$$

(126)

Calculate tank frequency:

$R_{DA1} = 8.25 \text{ k}\Omega$

$$f_{\rm R} = \frac{1}{2\pi\sqrt{L_{\rm S} \times \left(2 \times C_{\rm OSS} QA_{\rm A}VG\right)}}$$

Set initial  $t_{\mbox{\scriptsize ABSET}}$  delay time and

The 2.25 factor of the t<sub>ABSET</sub> equation was derived from empirical test data and may vary based on individual design of

$$t_{ABSET} = \frac{2.25}{f_R \times 4} \approx 346 \text{ ns}$$

(128)

The resistor divider formed by R<sub>DA1</sub> and R<sub>DA2</sub> programs the t<sub>ABSET</sub>, t<sub>CDSET</sub> delay range of the UCC28950/1. Select a standard resistor value for R<sub>DA1</sub>.

Note

|  |  | ~ ~ |  | 400 |  |

|--|--|-----|--|-----|--|

|  |  |     |  |     |  |

t<sub>ABSET</sub> can be programmed between 30 ns to 1000 ns.

The voltage at the ADEL input of the UCC28950/1 (V<sub>ADEL</sub>) needs to be set with R<sub>DA2</sub> based on the following conditions.

If t<sub>ABSET</sub> > 155 ns set V<sub>ADEL</sub> = 0.2 V, t<sub>ABSET</sub> can be programmed between 155 ns and 1000 ns:

If t<sub>ABSET</sub> ≤ 155 ns set V<sub>ADEL</sub> = 1.8 V, t<sub>ABSET</sub> can be programmed between 29 ns and 155 ns:

0.0417

$$V_{\text{SLOPE1}} = 0.2V \times \text{fs} \times \frac{0.04V}{\text{us}}$$

(122)

$$\left(\frac{\Delta \text{IL}_{\text{OUT}}}{1 - \Delta \text{IL}_{\text{MAC}}}\right) \times \text{Re}(1 - \text{Dryp}) \times \text{fc}$$

$$V_{\text{SLOPE2}} = 0.2V \times \text{fs} - \frac{\left(\frac{1}{a1 \times 2} - \frac{1}{a1} + \frac{1}{a2}\right)^{3/3} + \frac{1}{a2} + \frac{1}{a$$

If  $V_{SLOPE2} \ge V_{SLOPE1}$  set  $V_{SLOPE} = V_{SLOPE2}$

$$R_{SUM} = \frac{2.5V \times 10^3 \Omega}{V_{SLOPE} \times 0.5 us} \approx 125.4 \text{ k}\Omega$$

(124)

$$\frac{1}{f_{R} \times (2 \times C_{OSS} \text{ OA AVG})}$$

$$=\frac{1}{2\sqrt{1-1}}$$

(127)

SLUA560D - JUNE 2011 - REVISED MARCH 2022

(129)

Submit Document Feedback

RUMENTS www.ti.com

(123)

(125)

Based on V<sub>ADEL</sub> selection, calculate R<sub>DA2</sub>:

$$R_{DA2} = \frac{R_{DA1} \times V_{ADEL}}{5V - V_{ADEL}} \approx 344 \,\Omega \tag{130}$$

Select the closest standard resistor value for R<sub>DA2</sub>:

$$R_{DA2} = 348 \,\Omega \tag{131}$$

Recalculate  $V_{ADEL}$  based on resistor divider selection:

$$V_{ADEL} = \frac{5V \times R_{DA2}}{R_{DA1} + R_{DA2}} = 0.202 V$$

(132)

Resistor R<sub>DELAB</sub> programs t<sub>ABSET</sub>:

$$R_{\text{DELAB}} = \frac{(t_{\text{ABSET}} - 5\text{ns})}{\text{ns}} \times \frac{(0.15V + V_{\text{ADEL}} \times 1.46) \times 10^3}{5} \times \frac{1}{1\text{A}} \approx 30.4 \text{ k}\Omega$$

(133)

Select a standard resistor value for the design:

$$R_{\text{DELAB}} = 30.1 \,\text{k}\Omega \tag{134}$$

Note

Once you have a prototype up and running it is recommended you fine tune  $t_{ABSET}$  at light load to the peak and valley of the resonance between  $L_S$  and the switch node capacitance. In this design the delay was set at 10% load.

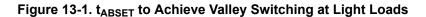

The initial starting point for the QC and QD turn on delays ( $t_{CDSET}$ ) should be initially set for the same delay as the QA and QB turn on delays (Pin 6). The following equations program the QC and QD turn-on delays ( $t_{CDSET}$ ) by properly selecting resistor  $R_{DELCD}$  (Pin 7).

$$t_{ABSET} = t_{CDSET}$$

Resistor R<sub>DELCD</sub> programs t<sub>CDSET</sub>:

$$R_{DELCD} = \frac{(t_{ABSET} - 5ns)}{ns} \times \frac{(0.15V + V_{ADEL} \times 1.46) \times 10^3}{5} \times \frac{1}{1A} \approx 30.4 \text{ k}\Omega$$

(136)

Select a standard resistor for the design:

$$R_{\text{DELCD}} = 30.1 k\Omega \tag{137}$$

(135)

#### Note

Once you have a prototype up and running it is recommended to fine tune  $t_{CDSET}$  at light load. In this design the CD node was set to valley switch at roughly 10% load. Obtaining ZVS at lighter loads with switch node QD<sub>d</sub> is easier due to the reflected output current present in the primary of the transformer at FET QD and QC turnoff/on. This is because there was more peak current available to energize L<sub>S</sub> before this transition, compared to the QA and QB turnoff/on.

There is a programmable delay for the turnoff of FET QF after FET QA turnoff ( $t_{AFSET}$ ) and the turnoff of FET QE after FET QB turnoff ( $t_{BESET}$ ). A good place to set these delays is 50% of  $t_{ABSET}$ . This will ensure that the appropriate synchronous rectifier turns off before the AB ZVS transition. If this delay is too large it will cause OUTE and OUTF not to overlap correctly and it will create excess body diode conduction on FETs QE and QF.

$t_{AFSET} = t_{BESET} = t_{ABSET} \times 0.5$

(138)

The resistor divider formed by  $R_{CA1}$  and  $R_{CA2}$  programs the  $t_{AFSET}$  and  $t_{BESET}$  delay range of the UCC28950/1. Select a standard resistor value for  $R_{CA1}$ .

#### Note

$t_{\text{EFSET}}$  and  $t_{\text{BESET}}$  can be programmed between 32 ns to 1100 ns.

$$R_{CA1} = 8.25 \text{ k}\Omega \tag{139}$$

The voltage at the  $A_{DELEF}$  pin of the UCC28950/1 ( $V_{ADELEF}$ ) needs to be set with  $R_{CA2}$  based on the following conditions.

If  $t_{AFSET}$  < 170 ns set  $V_{ADEL}$  = 0.2 V,  $t_{ABSET}$  can be programmed between 32 ns and 170 ns:

If t<sub>ABSET</sub> > or = 170 ns set V<sub>ADEL</sub> = 1.7 V, t<sub>ABSET</sub> can be programmed between 170 ns and 1100 ns:

Based on  $V_{ADELEF}$  selection, calculate  $R_{CA2}$ :

$$R_{CA2} = \frac{R_{CA1} \times V_{ADELEF}}{5V - V_{ADELEF}} \approx 4.25 \text{ k}\Omega$$

(140)

Select the closest standard resistor value for R<sub>CA2</sub>:

$$R_{CA2} = 4.22 \text{ k}\Omega \tag{141}$$

Recalculate V<sub>ADELEF</sub> based on resistor divider selection:

$$V_{\text{ADELEF}} = \frac{5V \times R_{\text{CA2}}}{R_{\text{CA1}} + R_{\text{CA2}}} = 1.692 \text{ V}$$

(142)

The following equation was used to program t<sub>AFSET</sub> and t<sub>BESET</sub> by properly selecting resistor R<sub>DELEF</sub>.

$$R_{\text{DELEF}} = \frac{(t_{\text{AFSET}} \times 0.5 - 4ns)}{ns} \times \frac{(2.65V - V_{\text{ADELEF}} \times 1.32) \times 10^3}{5} \times \frac{1}{14} \approx 14.1 \text{ k}\Omega$$

(143)

A standard resistor was chosen for the design.

$$R_{\text{DELEF}} = 14 \text{ k}\Omega \tag{144}$$

Resistor  $R_{TMIN}$  programs the minimum duty cycle on time ( $t_{MIN}$ ) that the UCC28950/1 (Pin 9) can demand before entering burst mode. If the UCC28950/1 controller tries to demand a duty cycle on time of less than  $t_{MIN}$  the power supply will go into burst mode operation. Please see the UCC28950/1 data sheet for details regarding burst mode. For this design we set the minimum on time to 100 ns.

$$t_{\rm MIN} = 100 \ \rm ns$$

(145)

The minimum on time is set by selecting  $R_{TMIN}$  with the following equation.

$$R_{\rm TMIN} = 12.1 \, \rm k\Omega \tag{146}$$

$$R_{TMIN} = \frac{(t_{MIN} - 15ns) \times 10^3}{6.6s} \approx 12.9 \text{ k}\Omega$$

(147)

A standard resistor value is then chosen for the design.

$$R_{\rm TMIN} = 12.1 \, \rm k\Omega \tag{148}$$

There is a pin that is provided for setting up the converter switching frequency (Pin 10). The frequency can be selected by adjusting timing resistor  $R_T$ .

$$R_{\rm T} = \left(\frac{2.5 \times 10^6 \frac{\Omega \text{Hz}}{\text{V}}}{\frac{\text{f}_{\rm S}}{2}} - \frac{\Omega}{\text{V}}\right) \times (\text{V}_{\rm REF} - 2.5\text{V}) \times 2.5 \times 10^3 \approx 60 \text{ k}\Omega$$

(149)

Select a standard resistor for the design.

$$R_{\rm T} = 61.9 \,\rm k\Omega \tag{150}$$

# 14 Turning SR FETs-off Under Light Load Conditions

To increase efficiency at lighter loads the UCC28950/1programmed (Pin 12, DCM) under light load conditions to turn off the synchronous FETs on the secondary side of the converter ( $Q_E$  and  $Q_F$ ). This threshold is programmed with resistor divider formed by  $R_E$  and  $R_G$ . This DCM threshold needs to be set at a level before the inductor current goes discontinues. The following equation sets the synchronous rectifiers to turnoff at roughly 15% load current.

$$V_{\rm RS} = \frac{\left(\frac{P_{\rm OUT} \times 0.15}{V_{\rm OUT}} + \frac{\Delta I_{\rm LOUT}}{2}\right) \times R_{\rm S}}{a1 \times a2} = 0.29V$$

(151)

$$R_{\rm G} = 1 \ \rm k\Omega \tag{152}$$

Select a standard resistor value for R<sub>G</sub>.

$$R_{\rm E} = \frac{R_{\rm G}(V_{\rm REF} - V_{\rm RS})}{V_{\rm RS}} \approx 16.3 \,\mathrm{k\Omega} \tag{153}$$

Select a standard resistor value for this design

$$R_{\rm E} = 16.9 {\rm k}$$

(154)

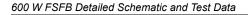

### 15 600 W FSFB Detailed Schematic and Test Data

Figure 15-1. Daughter Board Schematic

Note

Black triangles designate not populated.

Note

It is recommended to use an RCD clamp to protect the output synchronous FETs from over voltage due to switch node ringing. This RCD clamp is formed by diodes D4, D6 and resistor R6, R8 and R9 and capacitor C1.

Figure 15-3. 600-W Phase Shifted Full Bridge Efficiency

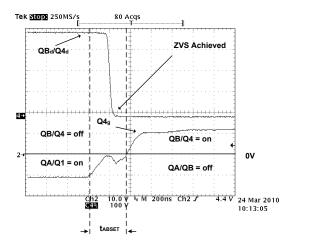

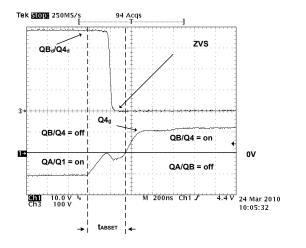

Full bridge gate drives and primary switch nodes (QB<sub>d</sub> and QD<sub>d</sub>) at V<sub>IN</sub> = 390 V, I<sub>OUT</sub> = 5 A.

Figure 15-4.  $Q4_g Q4_d$ ,  $V_{IN}$  = 390 V,  $I_{OUT}$  = 5 A

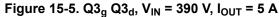

Full bridge gate drives and switch nodes at V\_{IN} = 390 V, I\_{OUT} = 10 A

οv

Figure 15-6.  $Q4_{q} Q4_{d}$ ,  $V_{IN}$  = 390 V,  $I_{OUT}$  = 10 A

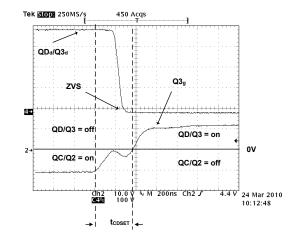

Q3g

QD/Q3 = on

QC/Q2 = off

Figure 15-7.  $Q3_g Q3_d$ ,  $V_{IN} = 390 V$ ,  $I_{OUT} = 10 A$

#### Note

Switch node QB<sub>d</sub>/Q4<sub>d</sub> is valley switching and node QD<sub>d</sub>/Q3<sub>d</sub> has achieved ZVS. It is not uncommon for switch node  $QD_d/Q3_d$  to obtain ZVS before  $QB_d/Q4_d$ . This is because during the  $QD_d/Q3_d$  switch node voltage transition, the reflected output current provides immediate energy for the LC tanking at the switch node. Where at the  $QB_d/Q4_d$  switch node transition the primary has been shorted out by the high side or low side FETs in the H bridge. This transition is dependent on the energy stored in  $L_S$ and LLK to provide energy for the LC tanking at switch node QBd/Q4d making it take longer to achieve ZVS.

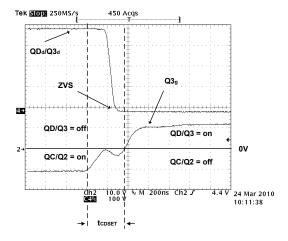

Full bridge gate drives and switch nodes at  $V_{IN}$  = 390 V,  $I_{OUT}$  = 25 A

#### Note

When the converter is running at 25 A both switch nodes are operating into zero voltage switching (ZVS). It is also worth mentioning that there is no evidence of the gate miller plateau during gate driver switching. This makes sense because the voltage across the drain and source of FETs QA through QD has already transition before the gate drives have transitioned.

### Full bridge gate drives and switch nodes at V<sub>IN</sub> = 390 V, $I_{OUT}$ = 50 A

Figure 15-10.  $Q4_g Q4_d$ ,  $V_{IN}$  = 390 V,  $I_{OUT}$  = 25 A

Note

ZVS was maintained from 50% to 100% output power.

### **16 References**

- 1. Bill Andreycak, *Phase Shifted, Zero Voltage Transition Design Considerations and the UC3875 PWM Controller* Unitrode Application Note SLUA107, September 5, 1999

- 2. Lazlo Balogh, *Design and Application Guide for High Speed Mosfet Gate Drive, Unitrode Power Supply* Design Seminar, Topic 2, 2001

- 3. Colin Gillmore, *Making the Correct Choice: UCC28950-Q1 or UCC28951-Q1*, *Application Note SLUA853, December 2017*, Topic 2, 2001

- 4. Texas Instruments, UCC28950 Green phase-shifted full-bridge controller with Synchronous Rectification control, data sheet

- 5. Texas Instruments, UCC28951 Green phase-shifted full-bridge controller with Synchronous Rectification control, data sheet

### **17 Revision History**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

# IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022, Texas Instruments Incorporated