# 5W USB Flyback Design Review/Application Report

Michael O'Loughlin

Senior Power Applications Engineer

#### **Introduction:**

In USB and isolated low power converter designs-quasi resonant and discontinuous conduction mode flyback converter topologies are a popular choice, due to their low parts count and relatively low cost. To reduce the cost even further, TI has developed a quasi-resonant/discontinuous current mode flyback controller with primary-side control. This removes the need for optocoupler and TL431 feedback circuitry reducing the cost of these low power designs even more. To achieve relatively low no load input power and regulate the output voltage and output current this device uses a control methodology known as control law. This control methodology uses a combination of primary peak current amplitude modulation (AM) and frequency modulation (FM) to regulate the output current and voltage please refer to the data sheet [1] for details. This application report reviews the design of the 5W adapter, UCC28700EVM-068, evaluation module [2] using the UCC28700 power supply controller. The design calculations are based on typical values. In a production design the values need to be modified for worst case conditions. Also note there is a MathCAD design tool [3] that goes along with this application note to make the power supply design process easier using this device.

### **Design Specifications:**

| Description                                      | Minimum                  | Typical               | Maximum                    | Units |

|--------------------------------------------------|--------------------------|-----------------------|----------------------------|-------|

| RMS Input Voltage                                | 90 (V <sub>INMIN</sub> ) | 115/230               | 265 (V <sub>INMAX</sub> )  | V     |

| No Load Input Power                              |                          |                       | 30 (P <sub>INL</sub> )     | mW    |

| Output Voltage                                   | 4.75                     | 5 (V <sub>оит</sub> ) | 5.25                       | V     |

| Output Voltage Ripple                            |                          |                       | 100 (V <sub>RIPPLE</sub> ) | mVpp  |

| Output Load Step<br>(0.1 to 0.6A), (0.6 to 0.1A) | 4.1 (V <sub>OTRM</sub> ) |                       | 6.0                        | V     |

| Output Current                                   |                          |                       | 1(I <sub>OUT</sub> )       | Α     |

| Switching Frequency                              |                          |                       | 105 (f <sub>MAX</sub> )    | kHz   |

| Full Load Efficiency<br>(230/115V RMS input)     | 73(η)                    |                       |                            | %     |

Table 1, Design Specifications

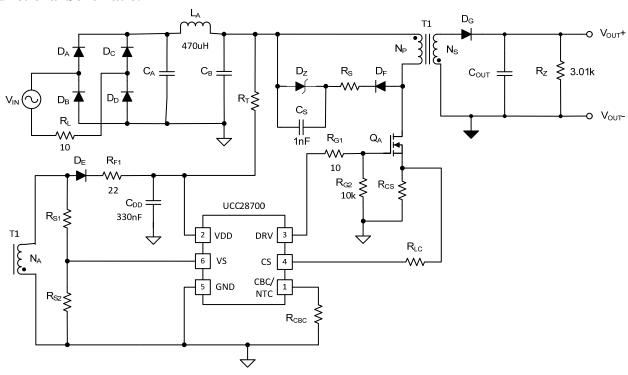

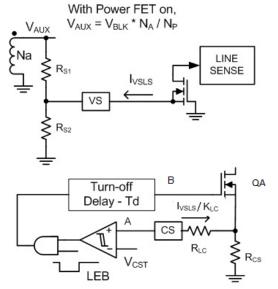

### **Functional Schematic:**

Figure 1, UCC28700 5W Offline Flyback Functional Schematic

### **Selecting RCB/NTC Resistor:**

In this design cable compensation was not used and resistor R8 was not populated. Please refer to the data sheet on how to setup cable compensation [1].

#### **Initial Power Budget:**

To meet the efficiency ( $\eta$ ) goal an initial power loss budget ( $P_{BUDGET}$ ) needs to be set.

$$P_{OUT} = V_{OUT} \times I_{OUT} = 5V \times 1A = 5W$$

$$P_{BUDGET} = \left(\frac{P_{OUT}}{0.74}\right) - P_{OUT} \approx 1.85W$$

### **Bridge Rectifier Selection (D<sub>A</sub> ..D<sub>D</sub>):**

For this design a 600V, 0.8A, bridge rectifier from Diodes Incorporated was chosen for the bridge rectifier diode ( $D_A$ ..  $D_D$ ), part number HD06.

$V_{FDA} = 1V$ , forward voltage drop of bridge rectifier diode (V<sub>FDA</sub>)

$$I_{DA} = \left(\frac{\frac{P_{OUT}}{\eta}}{V_{INMIN} \frac{2}{\pi} \sqrt{2}}\right) = \frac{\frac{5W}{0.74}}{90V \frac{2}{\pi} \sqrt{2}} \approx 85mA$$

, bridge rectifier average diode current (I<sub>DA</sub>)

$P_{DA} = V_{FDA} \times I_{DA} = 85 mW$ , estimate power dissipated in bridge rectifier diode (PDA)

Estimate remaining power budget based on bridge rectifier loss.

$$P_{BUDGET} = P_{BUDGET} - 2 \times P_{DA} \approx 1.68W$$

### **Transformer Calculations (T1):**

Transformer demagnetizing duty cycle (D<sub>MAG</sub>) is fixed to 42.5% based on the UCC28700 control law methodology [1].

$$D_{MAG} = 0.425$$

T<sub>R</sub> is the estimated period of the LC resonant frequency at the switch node.

$$T_R = 2us$$

Calculate maximum duty cycle (D<sub>MAX</sub>):

$$D_{MAX} = 1 - D_{MAG} - f_{MAX} \frac{T_R}{2} = 1 - 0.425 - 105kHz \frac{2\mu s}{2} = 0.47$$

Calculate transformer primary peak current (I<sub>PPK</sub>) based on a minimum flyback input voltage. This calculation includes a factor of 0.6 to account for the reduction in flyback input voltage caused by the ripple voltage across the input capacitors (CA and C

$$I_{PPK} = \frac{2 \times P_{OUT}}{\eta \times V_{INMIN} \sqrt{2} \times 0.6 \times D_{MAX}} = \frac{2 \times 5W}{0.74 \times 90V \sqrt{2} \times 0.6 \times 0.47} \approx 382 mA$$

Selected primary magnetizing inductance (L<sub>PM</sub>) based on minimum flyback input voltage, transformer, primary peak current, efficiency and maximum switching frequency ( $f_{MAX}$ ).

$$L_{PM} = \frac{\frac{2 \times P_{OUT}}{\eta}}{I_{PPK}^2 \times f_{MAX}} = \frac{\frac{2 \times 5W}{0.74}}{(376mA)^2 \times 105kHz} \approx 896uH$$

$V_{OAON} = 2V$ , estimated voltage drop across FET during conduction

$V_{RCS} = 0.75V$ , voltage drop across current sense resistor

$V_{DG} = 0.6V$  , estimated forward voltage drop across output diode

Calculate transformer turns ratio primary to secondary  $(a_1)$  based on volt-second balance. Note in the following equation  $L_{SM}$  is secondary magnetizing inductance.

$$a_{1} = \frac{N_{P}}{N_{S}} = \sqrt{\frac{L_{PM}}{L_{SM}}} = \frac{D_{MAX} \times (V_{INMIN} \sqrt{2} \times 0.6 - V_{AON} - V_{RCS})}{D_{MAG} \times (V_{OUT} + V_{DG})} \approx 14.5$$

$V_{\rm DDMIN} = 8V$  , UCC28700 minimum VDD voltage before UVLO turnoff.

$V_{DE} = 0.3V$ , estimated auxiliary diode forward voltage drop

$V_{OUT\_INIT} = 2V$  , Minimum voltage on the output when adapter is connected to a device with a depleted battery.

Calculate transformer auxiliary to secondary turns ratio (a<sub>2</sub>)

$$a_2 = \frac{N_A}{N_S} = \frac{V_{DDMIN} + V_{DE}}{V_{OUT-INIT} + V_{DG}} \approx 3.2$$

Transformer primary RMS current (I<sub>PRMS</sub>)

$$I_{PRMS} = I_{PPK} \sqrt{\frac{D_{MAX}}{3}} = 151 mA$$

Transformer secondary peak current RMS current (I<sub>SPK</sub>)

$$I_{SPK} = \frac{P_{OUT} \times 2}{V_{OUT} \times D_{MAG}} \approx 4.7A$$

Transformer secondary RMS current (I<sub>SRMS</sub>)

$$I_{\it SRMS} = I_{\it SPK} \sqrt{\frac{D_{\it MAG}}{3}} \approx 1.8 A$$

, transformer secondary RMS current

For this design we estimated the power dissipated by the UCC28700 (P<sub>IC</sub>) would be 50mW maximum. Note this will vary in the design based on the FET that is being driven and the maximum frequency it is being driven at.

$$P_{IC} = 50mW$$

Calculate auxiliary winding peak current (I<sub>APK</sub>)

$$I_{APK} = \frac{P_{IC} \times 2}{(V_{OUT} + V_{DE}) \times a_2 \times D_{MAG}} = 13mA$$

Calculate auxiliary winding RMS current (I<sub>ARMS</sub>)

$$I_{ARMS} = I_{APK} \sqrt{\frac{D_{MAG}}{3}} \approx 5.0 mA$$

For this transformer we allow for 3% efficiency loss from the transformer ( $P_{T1}$ )

$$P_{T1} = P_{OUT} \times 0.03 = 150 mW$$

Recalculate remaining power budget

$$P_{BUDGET} = P_{BUDGET} - P_{T1} \approx 1.53W$$

A Wurth Electronik transformer was designed for this application, part number 750312723, which has the following specifications:

$$a_1 = 15.33$$

$$a_2 = 3.83$$

$$L_{PM} = 925uH$$

$L_{LK} = 16uH$ , primary leakage inductance

## Input Capacitor Selection ( $C_{IN} = C_A + C_B$ ):

Calculate input capacitor charge time (t<sub>CH</sub>) based on 40% input capacitor ripple voltage.

$$t_{CH} = \frac{1 - \sin^{-1} \left( \frac{V_{INMIN} \sqrt{2} - V_{INMIN} \sqrt{2} \times 0.6}{V_{INMIN} \sqrt{2}} \right)}{4 \times 47 Hz} = 3.4 ms$$

Calculate flyback average primary current (I<sub>PT1</sub>) during input capacitor discharge.

$$I_{PT1} = \frac{\frac{P_{OUT}}{\eta \times V_{INMIN}\sqrt{2}} + \frac{P_{OUT}}{\eta \times V_{INMIN}\sqrt{2} \times 0.6}}{2} = 72mA$$

Calculate total input capacitance ( $C_{IN}$ ) based on minimum flyback input voltage and 40% ripple voltage across the input capacitor.

$$T_{RL} = \frac{1}{2 \times 47 Hz} \approx 11 ms$$

, longest period of the rectified line voltage

$V_{\mathit{INRIPPLE}} = V_{\mathit{INMIN}} \times \sqrt{2} \times 0.4 \approx 50.9 V$ , input ripple to the flyback converter

$$C_{IN} = \frac{I_{PT1}(T_{RL} - t_{CH})}{V_{INRIPPLE}} \approx 10uF$$

$$C_A = C_B = \frac{C_{IN}}{2} = 5uF$$

Calculate input capacitor (C<sub>A</sub>) RMS current (I<sub>C\_ARMS</sub>) based on 40% input capacitor ripple voltage.

$$I_{CINP} = \frac{2 \times (C_A + C_B) \times V_{INMIN} \sqrt{2} \times 0.4}{t_{CH}} \approx 311 mA \text{ , peak input capacitor charge current (I_{CINP})}$$

$$I_{CA\_RMS} = \sqrt{\left(\frac{I_{CINP}}{2}\sqrt{\frac{t_{CH}}{3 \times T_{RL}}}\right)^2 + \left(\frac{I_{CINP}}{2}\sqrt{\frac{T_{RL} - t_{CH}}{3 \times T_{RL}}}\right)^2 - \left(\frac{I_{PT1}}{2}\right)^2} \approx 82mA$$

Estimate of capacitor  $C_B$ 's low frequency (1/ $T_{RL}$ ) RMS current ( $I_{CB\_LFRMS}$ )

$$I_{CB\_LFRMS} = I_{CA\_RMS}$$

Estimate of C<sub>B</sub>'s high frequency RMS current (I<sub>CB HFRMS</sub>)

$$I_{CB\_HFRMS} = \sqrt{\left(I_{PPK}\sqrt{\frac{D_{MAX}}{3}}\right)^2 - \left(I_{PPK}\frac{D_{MAX}}{2}\right)^2} \approx 122mA$$

Estimate of C<sub>B</sub>'s total RMS current (I<sub>CB RMS</sub>)

$$I_{CB\_RMS} = \sqrt{(I_{CB\_LFRMS})^2 + (I_{CB\_HFRMS})^2} \approx 147 mA$$

For this design 4.7uF, 400V electrolytic capacitors, from Nichicon part number UVR2G4R7MPD were chosen for the design.

$$C_A = C_B = 4.7 uF$$

These capacitors had a measured ESR of 6 ohms at 105 kHz

$$ESR_{CA} = ESR_{CB} = 6\Omega$$

Recalculate remaining power budget based on power dissipation by the ESRs in the input capacitors.

$$P_{BUDGET} = P_{BUDGET} - (I_{CA\_RMS})^2 \times ESR_{CA} - (I_{CB\_RMS})^2 \times ESR_{CB} \approx 1.36W$$

### Filter Inductor $(L_A)$ :

Filter inductor (L<sub>A</sub>) is used for EMI filtering. In this design it is just a place holder and the design has not been optimized for EMI. 470uH inductor from Bourns was chosen, part number RLB0608-471KL. This inductor has a DCR of 6.5 ohms.

$$DCR = 6.5\Omega$$

Recalculate power budget based on DCR losses

$$P_{BUDGET} = P_{BUDGET} - (I_{PRMS})^2 \times DCR \approx 1.212W$$

### **Fusible Resistor (R<sub>L</sub>):**

To limit the inrush current during power and for safety a 10 ohm, 3W fusible resistor from Bourn, part number PWR4522AS10R0JA was placed at the input of this design.

$$R_L = 10\Omega$$

Recalculate power budget based on estimated R<sub>L</sub> losses

$$P_{BUDGET} = P_{BUDGET} - (I_{PRMS})^2 \times R_L \approx 0.984W$$

### **Trickle Charge Resistor (R<sub>T</sub>):**

To reduce no load power losses  $R_T$  and to keep no load power to a minimum, three  $5.11M\Omega$  are used in series for  $R_T$

$$R_T = 5.11M\Omega \times 3 = 15.33M\Omega$$

$$P_{RT} = \frac{\left(V_{INMAX}\sqrt{2}\right)^2}{R_T} \approx 9.2 mW$$

, Total trickle charge resistor power dissipation

Recalculate power budget

$$P_{RUDGET} = P_{RUDGET} - P_{RT} \approx 0.974W$$

#### **VDD** Capacitor Selection (C<sub>DD</sub>):

The  $C_{DD}$  is selected with the following equation based on the desired startup time (dt<sub>CDDS</sub>) of the UCC28700 controller and knowing the start current ( $I_{START}$ ), as well as, the UCC28700 device startup threshold ( $V_{VDD(on)}$ ). For this design a 330nF capacitor was selected.

$$dt_{CDDS} = 1s$$

$$I_{START} = 1.5uA$$

$$V_{VDD(on)} = 21V$$

$$C_{DD} = \frac{\left(\frac{V_{INMIN}\sqrt{2}}{R_T} - I_{START}\right) \times dt_{CDDS}}{V_{VDD(on)}} = 324nF \approx 330nF$$

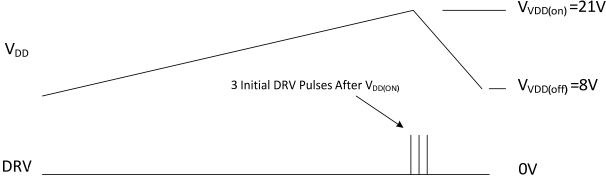

Note after  $C_{DD}$  has been charged up to the device turn on threshold  $(V_{VDD(on)})$ , the UCC28700 will initiate three small gate drive pulses (DRV) and start sensing current and voltage. (Please refer to figure 2) If a fault is detected such as an input under voltage or any other fault, the UCC28700 will terminate

the gate drive pulses and discharge  $C_{DD}$  to initiate an under voltage lockout. This capacitor will be discharged with the run current of the UCC28700 ( $I_{RUN}$ ) intil the  $V_{DD}$  turnoff ( $V_{VDD(off)}$ ) threshold is reached. Note the  $C_{DD}$  discharge time ( $t_{CDDD}$ ) from this forced soft start can be calculated knowing the controller run current ( $I_{RUN}$ ) without out gate driver switching and the controller's VDD turnoff threshold ( $V_{VDD(off)}$ ) and the following equations. If no fault is detected, the UCC28700 will continue driving  $Q_A$  and controlling the input and output currents [1] and a soft start will not be initiated.

$$\begin{split} I_{RUN} &= 2.1 mA \\ V_{VDD(off)} &= 8V \\ dt_{CDD} &= C_{DD} \frac{V_{VDD(on)} - V_{VDD(off)}}{\left(\frac{V_{INMAX} \sqrt{2}}{R_T} - I_{RUN}\right)} = 71 ms \end{split}$$

Figure 2, VDD and DRV at Startup with Fault

### **Current Sense Resistor (R<sub>CS</sub>):**

For this design 2.05 ohm resistor was selected based on a nominal maximum current sense signal of 0.75V.

$$R_{CS} = \frac{0.75V}{I_{PPK}} = 1.965\Omega \approx 2.05ohm$$

$$P_{RCS} = (I_{PRMS})^2 \times R_{CS} = 0.046W$$

, nominal current sense resistor power dissipation

Recalculate power budget

$$P_{BUDGET} = P_{BUDGET} - P_{RCS} \approx 0.928W$$

### **Select Output Diode (D<sub>G</sub>):**

Calculate diode reverse voltage (V<sub>RDG</sub>)

$$V_{RDG} = V_{OUT} + V_{INMAX} \sqrt{2} \frac{1}{a_1} \approx 29.45V$$

Calculate peak output diode (I<sub>DGPK</sub>)

$$I_{DGPK} = I_{SPK} = 4.7A$$

For this design we selected a 3A, 40V schottky rectifier with a forward voltage drop (V<sub>FDG</sub>) of 0.31V.

$$V_{FDG} = 0.31V$$

Estimated diode power loss (P<sub>DG</sub>)

$$P_{DG} = \frac{P_{OUT} \times V_{FDG}}{V_{OUT}} \approx 0.31 \text{W}$$

Recalculate power budget

$$P_{BUDGET} = P_{BUDGET} - P_{DG} \approx 0.618W$$

### **Select Output Capacitors (COUT):**

Select output ESR based on 90% of the allowable output ripple voltage

$$ESR_{COUT} = \frac{V_{RIPPLE} \times 0.9}{I_{SPK}} = \frac{100mV \times 0.9}{4.7A} = 19m\Omega$$

For this design the output capacitor ( $C_{OUT}$ ) was selected to prevent  $V_{OUT}$  from dropping below the minimum output voltage during transients ( $V_{OTRM}$ ).

$$V_{OTRM} = 4.1V$$

$$C_{OUT} \ge \frac{2ms \times \frac{P_{OUT}}{V_{OUT} \times 2}}{V_{OUT} - V_{OTRM}} = 1.1mF$$

For this design two 560uF capacitors were used in parallel on the output, with an ESR of  $13m\Omega$  each.

$$C_{OUT} = 2 \times 560 uF = 1.12 mF$$

$$ESR_{COUT} = \frac{13m\Omega}{2} = 6.5m\Omega$$

Estimate total output capacitor RMS current (I<sub>COUT RMS</sub>)

$$I_{COUT\_RMS} = \sqrt{\left[\frac{I_{SPK} \times \sqrt{D_{MAG}}}{\sqrt{3}}\right]^2 - \left(\frac{P_{OUT}}{V_{OUT}}\right)^2} \approx 1.46A$$

Estimate total output capacitor loss (P<sub>COUT</sub>)

$$P_{COUT} = (I_{COUT\_RMS})^2 \times ESR_{COUT} = 14mW$$

Recalculate power budget

$$P_{BUDGET} = P_{BUDGET} - P_{COUT} \approx 0.604W$$

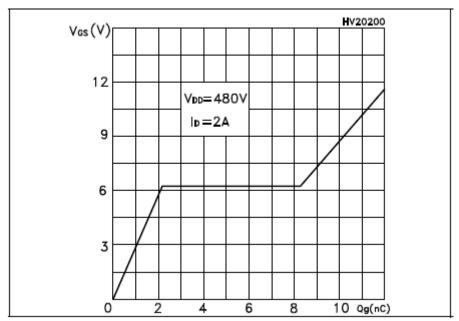

### **Select FET Q<sub>A</sub>:**

For this design we had chosen a 600V rated MOSFET with the following characteristics:

$$R_{DSON} = 4.5ohm$$

, FET Q<sub>A</sub> on resistance

$C_{OSS} = 8.5 pF$ , average FET drain to source capacitance

Figure 3, Gate Charge vs  $V_{\rm gs}$

Estimate FET losses (PQA)

$I_{DRIVE} = 0.35A$ , maximum FET gate drive current

$Q_g = 9nC$ , gate charge just above the miller plateau

$$t_r = Q_g \frac{2}{I_{DRIVE}} \approx 52 ns$$

, estimated FET  $V_{ds}$  rise and fall time

Estimate FET power loss by driving the FET's gate (Pg)

$Q_{g1} = 12nC$ , Gate charge at 12V drive clamp

$$V_g = 12V$$

$$P_{g} = 12V \times Q_{g1} \times f_{MAX} = 15mW$$

Calculate the average input voltage to the flyback at the maximum input voltage ( $V_{\text{INMAX}}$ ).

$$V_{\scriptscriptstyle FLY} = V_{\scriptscriptstyle INMAX} \times \sqrt{2} - \frac{V_{\scriptscriptstyle INRIPPLE}}{2} - 2 \times V_{\scriptscriptstyle FDA} \approx 347 V$$

Estimate FET average switching loss (P<sub>SW</sub>)

$$P_{SW} = V_{FLY} - (V_{OUT} + V_{VDG}) \times a_1 \frac{I_{PPK} \times t_r \times f_{MAX}}{2} \approx 269mW$$

Estimated FET Coss power dissipation (P<sub>COSS</sub>)

$C_{OSS} = 8.5 pF$ , average FET drain to source capacitance

$$P_{COSS} = \frac{C_{OSS}}{2} \times (V_{FLY})^2 \times f_{MAX} \approx 54mW$$

Calculate power loss from Rdson (P<sub>RDSON</sub>)

$$P_{RDSON} = (I_{PRMS})^2 \times R_{DSON} = 0.1W$$

Estimate total FET losses (POA)

$$P_{QA} = P_{RDSON} + P_{SW} + P_g + P_{COSS} \approx 441 mW$$

Recalculate the power budget

$$P_{BUDGET} = P_{BUDGET} - P_{QA} \approx 163 mW$$

### Setup Zener Clamp to Protect FET Q<sub>A</sub>:

$V_Z = 82V$ , Zener Clamp Voltage (D<sub>Z</sub>)

$V_{ds-MAX} = 600V$ , FET maximum drain to source voltage

$$V_{CLAMP} = V_{ds-MAX} \times 0.9 - V_{INMAX} \sqrt{2} \approx 165.2V$$

, Available Clamp Voltage to Protect FET QA

$$R_S = \frac{V_{CLAMP} - 0.6 - V_Z}{I_{PPK}} \approx 216.5\Omega$$

Select a standard resistor for the design.

$$R_S = 215\Omega$$

Estimate Zener Clamp/L<sub>LK</sub> power dissipation (P<sub>LK</sub>)

$$P_{LLK} = \frac{L_{LPK} \times (I_{PPK})^2 \times f_{MAX}}{2} = 122mW$$

Recalculate power budget

$$P_{BUDGET} = P_{BUDGET} - P_{LLK} \approx 40 mW$$

Select VS voltage divider  $(R_{S1}, R_{S2})$ :

$$I_{VSL(run)} = 220uA$$

VS Line-sense run current

Note R<sub>S1</sub> so the converter will go into under voltage lockout when the input is below 80% of the minimum specified input voltage.

$$R_{S1} = \frac{\frac{a_2}{a_1} V_{INMIN} \sqrt{2} \times 0.8}{I_{VSL(run)}} \approx 115.6 k\Omega$$

Select a standard resistor for the design

$$R_{S1} = 121k\Omega$$

$$R_{S2} = \frac{4V}{\underbrace{\left(V_{OUT} + V_{DG}\right) \times a_2 - 4V}_{R_{CI}}} \approx 27.7k\Omega$$

Calculated R<sub>S2</sub> is a starting point and will need to be adjusted in circuit. To have a 5V regulated output this resistor was adjusted to  $30.1k\Omega$

$$R_{S2} = 30.1k\Omega$$

Calculate VS divider power dissipation (P<sub>VS</sub>)

$$P_{VS} = \frac{\left(\sqrt{D_{MAX}} \left(V_{OUT} + V_{DG}\right) a_2\right)^2}{\left(R_{S1} + R_{S2}\right)} \approx 1.3 mW$$

Select auxiliary diode (D<sub>E</sub>) for this design that had a forward voltage drop (V<sub>DE</sub>) of 0.6V.

$$V_{DE} = 0.6V$$

$$V_{DD} = (V_{OUT} + V_{DG}) \times a_2 - V_{DE} \approx 20.8V$$

, UCC28700 supply voltage at  $V_{DD}$

$$V_{RDE} = V_{DD} + V_{INMAX} \sqrt{2} \times \frac{a_2}{a_1} \approx 115V$$

, maximum reverse voltage across  $V_{DE}$

$I_{RUN} = 2.1 mA$ , UCC28700 bias current when gate drive = 0V

$$I_{DD} = \frac{P_{g} + I_{RUN} \times V_{VDD}}{V_{DD}} \approx 2.8 mA \text{ , Estimated UCC28700 VDD current.}$$

Calculate D<sub>E</sub> power dissipation (P<sub>DE</sub>)

$$P_{DE} = I_{DD} \times V_{DE} \approx 1.7 mW$$

Recalculated power budget

$$P_{BUDGET} = P_{BUDGET} - P_{VS} - P_{DE} \approx 037 mW$$

### **Preload Resistor Selection (Rz):**

To keep the output voltage from climbing at no load a pre-load resistor is required. This is generally a trial an error process. For this designs the preload resistor that kept the output regulated under no load conditions was  $3.01 \text{ k}\Omega$ .

$$R_Z = 3.01K$$

Calculate  $R_Z$  power dissipation ( $P_{RZ}$ )

$$P_{RZ} = \frac{\left(V_{OUT}\right)^2}{R_Z} \approx 8.3 mW$$

Recalculated power budget and there is 29 mW of margin left in the power budget to meet the efficiency requirements of the design. Note in production designs, more margin might be required. Also note these calculations are estimations and the final design may need to be adjusted to hit efficiency and regulation requirements.

$$P_{BUDGET} = P_{BUDGET} - P_{RZ} \approx 29mW$$

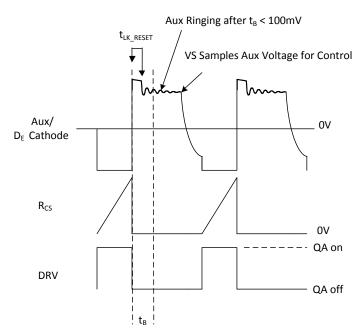

#### **Internal Blanking**

The UCC2870X controller regulates the output voltage by sensing the auxiliary (Aux) winding. This removes the need for opto isolator feedback scheme reducing the cost of the design. However, this voltage control feedback scheme is susceptible to leakage spikes at the switch node that occur in most flyback converters. This signal is coupled through the turns ratio of the transformer (T1) and shows up on the Aux winding during  $t_{LK\_RESET}$ , please refer to figure 4 for details.

To help insure the leakage spike on the Aux winding does not cause a control issues, the UCC2870X blanks (t<sub>B</sub>) the Aux signal to the controller for 500 ns to 1.5 us depending on loading. Please see the data sheet details [1]. Note the ringing on the auxiliary winding needs to be less than 100mV peak to peak after t<sub>B</sub>. Snubbing circuitry on the secondary and/or auxiliary winding may be required to reduce ringing.

Figure 4, Auxiliary Winding VS Blanking

To ensure the leakage spike does not cause control issues it needs to be dissipated before the Aux blanking ( $t_B$ ) has terminated. The tank frequency ( $f_{LC}$ ) between the switch node capacitance ( $C_{SWN}$ ) and the transformer leakage inductance ( $L_{LK}$ ) should be greater than 1MHz.

$$f_{LC} = \frac{1}{2 \times \pi \times \sqrt{L_{LK} \times C_{SWN}}}$$

$$f_{LC} \ge \frac{1}{2 \times 500 ns} = 1MHz$$

### Select line compensation resistor $R_{LC}$ :

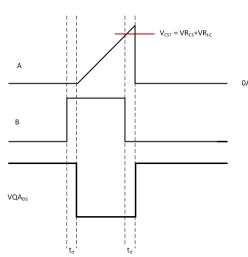

Resistor R<sub>LC</sub> provides offset to the peak current comparator input (CS). R<sub>LC</sub> is adjusted to terminate the gate drive signal (B) early to prevent primary current (A) from over shooting [1]. Please refer to figures 5 and 6 for details.

Figure 5, Peak Current Limit Comparator

Figure 6, CS(A), QA<sub>g</sub>(B), VQA<sub>DS</sub> Signals

$$K_{LC} = 25$$

, Line Compensating Ratio [1]

Calculate  $R_{LC}$  initial resistor setting based on  $QA_{DS}$  rise and fall time  $(t_r)$

$$R_{LC} = \frac{K_{LC} \times R_{S1} \times R_{CS} \times t_r \times a1/a2}{L_{PM}} \approx 1.38 k\Omega \text{ , Starting Point for } R_{LC}$$

In circuit adjust  $R_{LC}$  so the maximum output current is  $(I_{OUT})$ . For this design RLC was set to 4.64 k $\Omega$ .

$$R_{LC}=4.64k\Omega$$

### Estimate no load input power $(P_{NL})$ :

$f_{MIN} = 1kHz$ , Minimum operating frequency

$P_g = V_g \times Q_g \times f_{MIN} = 144uW$ , gate drive power dissipation at f<sub>MIN</sub>

$I_{WAIT} = 85uA$ , VDD input current at 1 kHz operating frequency [1]

$P_{VDD} = P_g + I_{WAIT} \times V_{DD} \approx 1.9 mW$ , Estimated UCC28700 power dissipation at f<sub>MIN</sub>

Estimate switching losses (P<sub>SWFM</sub>) at high line at f<sub>MIN</sub>

$$P_{SWFM} = V_{FLY} - (V_{OUT} - V_{VDG}) \times a1 \frac{I_{PPK}}{3} \times t_r \times f_{MIN}$$

$$\approx 945uW$$

$$P_{COSS} = \frac{C_{OSS}}{2} \times (V_{FLY})^2 \times f_{MIN} \approx 0.5 mW$$

, estimated C<sub>OSS</sub> losses at f<sub>MIN</sub>

$$P_{LLK} = \frac{L_{LPK} \times \left(\frac{I_{PPK}}{3}\right)^2 \times f_{MIN}}{2} \approx 129uW, \text{ estimate of leakage power dissipation at no load}$$

The estimated no load input power ( $P_{NL}$ ) is roughly 22 mW. In the actual 5W design the no load input power was roughly 20 mW at 230V RMS input voltage.

$$P_{RZ} = 8.3 mW$$

$$P_{RT} = 9.2mW$$

$$P_{\scriptscriptstyle NL} = P_{\scriptscriptstyle VDD} + P_{\scriptscriptstyle SWFM} + P_{\scriptscriptstyle COSS} + P_{\scriptscriptstyle RZ} + P_{\scriptscriptstyle RT} + P_{\scriptscriptstyle LLK} \approx 22mW$$

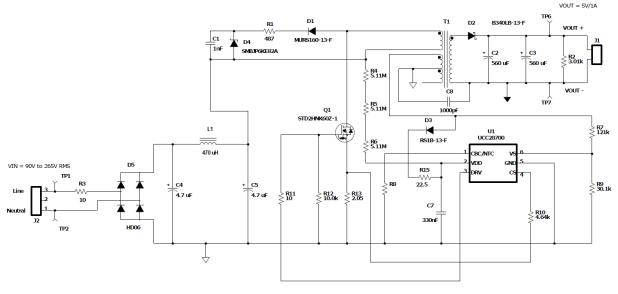

### **5W EVM Schematic:**

Figure 7, Schematic

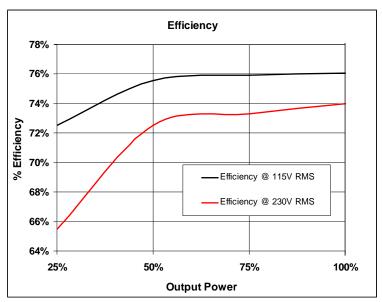

### **Efficiency:**

Figure 8, Efficiency

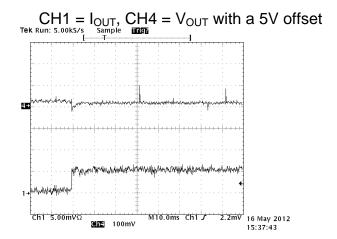

### **Load Transient at 115V RMS**

Figure 9, 0.1 to 0.6A load step

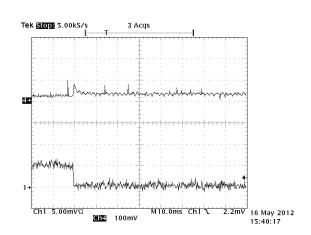

Figure 10, 0.6 to 0.1A load step

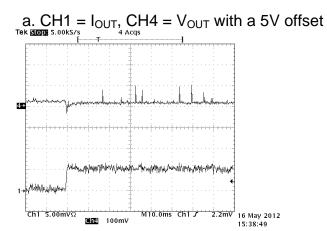

### **Load Transient at 230V RMS**

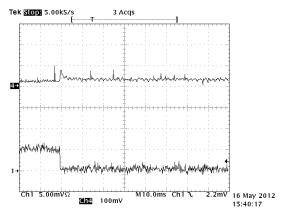

Figure 11, 0.1 to 0.6A load step

Figure 12, 0.6 to 0.1A load step

#### **REFERENCES**

[1] UCC28700/1/2/3 Data Sheet, Constant-Voltage, Constant-Current Controller with Primary Side Regulation, SLUSB41, July 2012, <a href="http://www.ti.com/lit/gpn/ucc28700">http://www.ti.com/lit/gpn/ucc28700</a>

[2]Using the UCC28700EVM-068, UCC28700EVM-068 5W USB Adapter, SLUU968, July 2012, <a href="http://www.ti.com/litv/pdf/sluu968">http://www.ti.com/litv/pdf/sluu968</a>

[3] UCC28700 MathCAD design tool, <a href="http://www.ti.com/litv/zip/sluc381">http://www.ti.com/litv/zip/sluc381</a>

#### IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

#### Products Applications

Audio www.ti.com/audio Automotive and Transportation www.ti.com/automotive Communications and Telecom Amplifiers amplifier.ti.com www.ti.com/communications **Data Converters** dataconverter.ti.com Computers and Peripherals www.ti.com/computers **DLP® Products** www.dlp.com Consumer Electronics www.ti.com/consumer-apps

DSP **Energy and Lighting** dsp.ti.com www.ti.com/energy Clocks and Timers www.ti.com/clocks Industrial www.ti.com/industrial Interface interface.ti.com Medical www.ti.com/medical logic.ti.com Logic Security www.ti.com/security

Power Mgmt <u>power.ti.com</u> Space, Avionics and Defense <u>www.ti.com/space-avionics-defense</u>

Microcontrollers microcontroller.ti.com Video and Imaging www.ti.com/video

RFID www.ti-rfid.com

OMAP Applications Processors <a href="https://www.ti.com/omap">www.ti.com/omap</a> TI E2E Community <a href="https://example.com/omap">e2e.ti.com/omap</a>

Wireless Connectivity <u>www.ti.com/wirelessconnectivity</u>