## bq77905 20S Cell Stacking Configuration

Taylor Vogt

BMS: Monitoring and Protection

#### **ABSTRACT**

The bq77905 is a 3–5S Low Power Protector with easy stacking capabilities for higher than 5S cell battery packs. This document provides an example for setting up a stacking configuration with the bq77905 and exhibits detailed analysis of the stacking functionality.

#### **Table of Contents**

| 1 Configuration                                    | 1  |

|----------------------------------------------------|----|

| 2 Functionality                                    |    |

| 3 Load Current                                     |    |

| 4 Troubleshooting FAQ                              | 10 |

| 5 References                                       |    |

| 6 Revision History                                 | 14 |

| •                                                  |    |

| List of Figures                                    |    |

| Figure 1-1. Block Diagram                          | 2  |

| Figure 2-1. UV Detection                           |    |

| Figure 2-2. UV Recovery                            | 3  |

| Figure 2-3. OV Detection                           |    |

| Figure 2-4. OV Recovery                            |    |

| Figure 3-1. Loading for Stacked Devices            |    |

| Figure 3-2. Example CTRx pin Characteristic        |    |

| Figure 3-3. Load Matching Resistors                |    |

| Figure 3-4. FET Drive Voltage With Cell Variation. |    |

| Figure 4-1. Measurement Loading Example on CTRC    |    |

| Figure 5-1 Schematic                               | 13 |

#### **Trademarks**

All trademarks are the property of their respective owners.

#### 1 Configuration

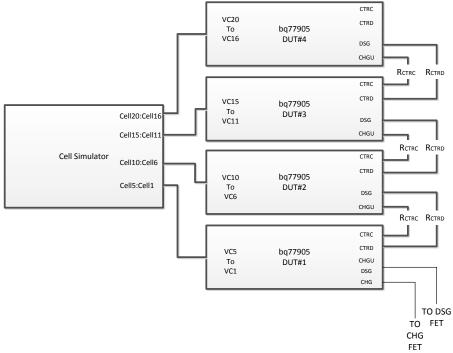

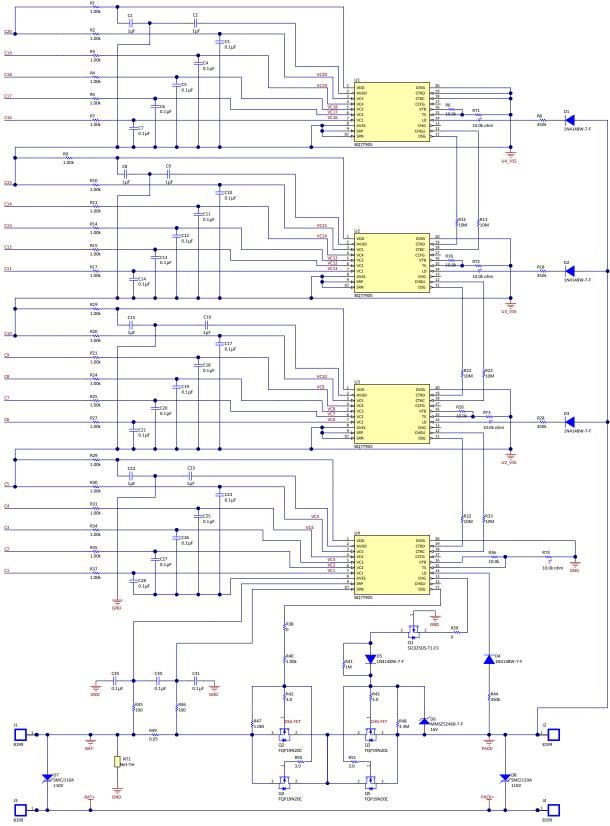

The following stacking configuration represents a battery pack protection system for a 20S cell pack. Therefore, the setup requires four stacked bq77905 devices supporting 5 cells each. Each device is numbered and labeled as a device under test (DUT) in the high-level block diagram illustrated in Figure 1-1.

#### Note

For other configurations where one or more devices on the stack supports a lower cell count (for example, 3 or 4) than the rest of the stacked devices, TI recommends using the upper-most device on the stack to support the highest cell count. For example, if the user wants to protect a 9S cell pack, DUT#2 shown in Figure 1-1 supports 5 cells while DUT#1 would support 4 cells. In that case, DUT#2 supports more cells because it is the higher and upper-most device on the stack. Furthermore, If the user wants to protect a 17S cell pack, DUT#4 would support 5 cells while DUT#1–3 would support 4. When possible, configure each DUT to support the same number of cells.

Configuration Vww.ti.com

Copyright © 2016, Texas Instruments Incorporated

Figure 1-1. Block Diagram

### 1.1 General Setup Instructions

The following instructions are useful when constructing any stacking configuration with the bq77905. The instructions refer to DUTs #1–4 shown in Figure 1-1 representing the devices labeled U1–U4, respectively, in the detailed schematic in Figure 5-1. Many of the steps refer to pin connections that can best be understood by observing the schematic. Further information on the setup of Stacking Implementations can be found on the bq77904 / bq77905: 3-5S Low Power Protector data sheet (SLUSCM3).

- For the bottom device (DUT#1 or U1), use the CHG pin to drive the CHG FET, and leave the CHGU pin unconnected.

- 2. For the upper devices (all except DUT#1 or U1), connect the CHGU pin to the CTRC pin of the immediately lower device with a R<sub>CTRC</sub> and leave the CHG pin unconnected.

- 3. Connect the DSG pins of the upper devices with a R<sub>CTRD</sub> to the CTRD pin of the immediate lower devices.

- 4. Ensure that the SRP and SRN pins of the upper devices are connected to its corresponding AVSS pin. Each device should have its own separate plane for referencing the AVSS/DVSS pin or any other pins.

- 5. Ensure that the CCFG pin for each device is connected appropriately (5 cells = floating, 4 cells = AVDD, 3 cells = AVSS)

- 6. Ground the CTRC and CTRD pins of the upper-most device (in this case DUT#4 or U4) to its corresponding reference plane.

- 7. If load removal is not used for UV recovery, connect the LD pin of the upper devices to its corresponding reference plane. Otherwise, refer to the data sheet link (SLUSCM3).

## 2 Functionality

The following sections describe a fault detected by a DUT and displays the results in several images. Each device in the stack is functional in protecting OV, UV, OTC, OTD, UTC, and UTD faults, but the following results display protection of cell 17 on the upper-most device (DUT#4). This is so the data can focus on FET switching time in response to a fault on the top of the stack. Typically this was recorded within a few ms of the response time of faults on the bottom device, so the bq77905 functions efficiently across a stack.

#### 2.1 Undervoltage (UV)

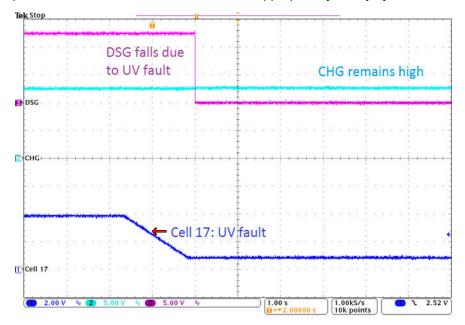

The UV fault test focuses on the DSG turn-off time as cell 17 is monitored below the desired threshold. In Figure 2-1, it is clear that DSG will fall and stay low while any cell has a UV fault detected. When examining the delay

www.ti.com Functionality

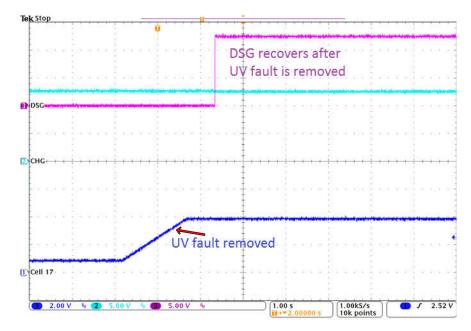

of DSG rise/fall by measuring the delta between the UV fault threshold (red arrows in Figure 2-1 and Figure 2-2) and DSG rise/fall, both figures display a similar response time of close to 1s due to the large  $R_{GS}$ . This is expected for the bq77905 and will need to be accounted for appropriately in any system.

Figure 2-1. UV Detection

Figure 2-2. UV Recovery

ISTRUMENTS Functionality www.ti.com

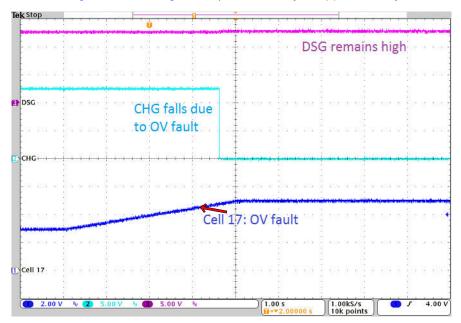

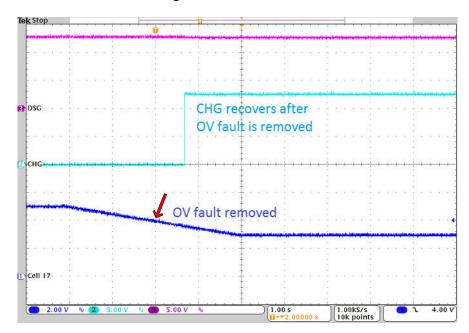

## 2.2 Overvoltage (OV)

The OV fault test is almost identical to the UV fault test, but instead focuses on the CHG turn-off time as a cell is monitored above the desired threshold. As shown in Figure 2-3, the CHG pin falls due to the OV fault (threshold designated by red arrows in Figure 2-3 and Figure 2-4) after a delay of approximately 400-600 ms.

Figure 2-3. OV Detection

Figure 2-4. OV Recovery

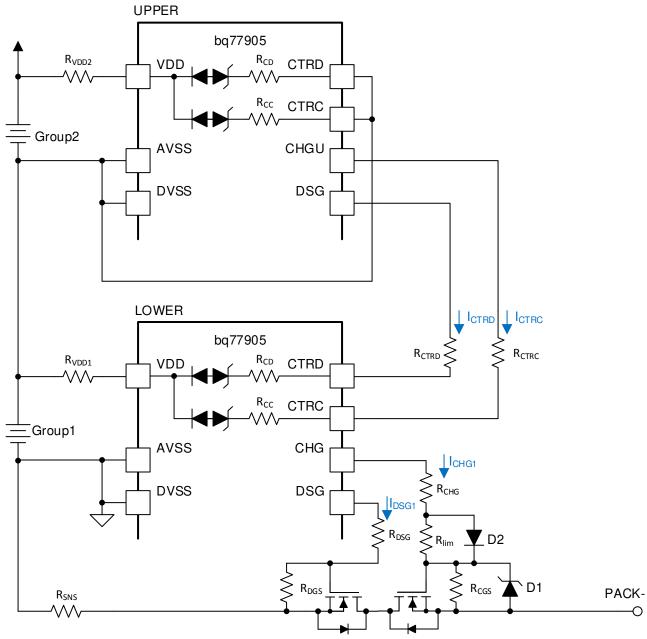

#### 3 Load Current

In the data sheet stacking schematics and Figure 5-1, the bottom device has the load of the FET gate-source resistors while the upper devices have only the load from the R<sub>CTRD</sub> and R<sub>CTRC</sub> resistors. Since the load is needed for the FETs, add load to the upper devices to more closely match the load between the devices. Adding the load on the CHG or CHGU and DSG output allows the load to match the mode of the battery rather than simply adding a load to the cells. Figure 3-1 shows currents into the FETs and stacking interface pins.

www.ti.com Load Current

Copyright © 2017, Texas Instruments Incorporated

Figure 3-1. Loading for Stacked Devices

Since the  $R_{DSG}$  and  $R_{CHG}$  are small with respect to the gate resistors, these can usually be neglected when estimating current and are omitted from the following equations. The currents for the DSG and CHG FET drive:

$$I_{DSG1} = V(FETON)/R_{DGS}$$

(1)

$$I_{CHG1} = \begin{pmatrix} V_{(FETON)} & -V_{D2} \end{pmatrix} / R_{CGS}$$

(2)

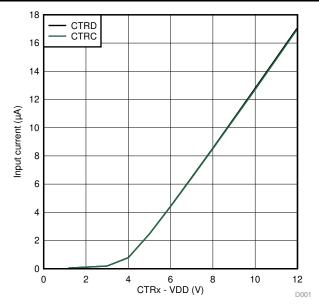

The CTRC and CTRD pins have an internal resistance which will limit the current into the clamp at the maximum pin voltage. The clamp voltage is shown at a specific test current in the data sheet,  $V_{CTR(MAXV)}$ . The internal resistance  $R_{CD} = R_{CC}$  or  $R_{Cx}$  has a nominal value of 440 k $\Omega$  but may vary significantly and is not a characterized value in the data sheet. The CTRC and CTRD characteristic for an example device is shown in Figure 3-2.

Load Current www.ti.com

Figure 3-2. Example CTRx pin Characteristic

At low currents the data sheet test conditions may be a good representation of the control input operating point and the equation for the input current is:

$$I_{CTRx} = \frac{\left(V_{(FETON)} - V_{CTR(MAXV)}\right)}{R_{CTRx}}$$

(3)

Using typical values in the data sheet and 10 M $\Omega$  for R<sub>CTRx</sub>, I<sub>CTRx</sub> would be 800 nA, near the 600 nA data sheet test current.

One method to match the load of the FETs would be to adjust R<sub>CTRx</sub>. However, at much higher currents it is better to consider the internal resistance and an internal clamp value V<sub>C</sub> in an equation for I<sub>CTRx</sub>:

$$I_{CTRx} = (V_{(FETON)} - V_C) / (R_{Cx} + R_{CTRx})$$

(4)

As  $R_{CTRx}$  is decreased to increase the current, the current becomes more sensitive to the internal  $R_{Cx}$  resistance variation. A designer may want to avoid using the R<sub>CTRx</sub> resistor to match the current of the FET unless the R<sub>xGS</sub> resistance were very large.

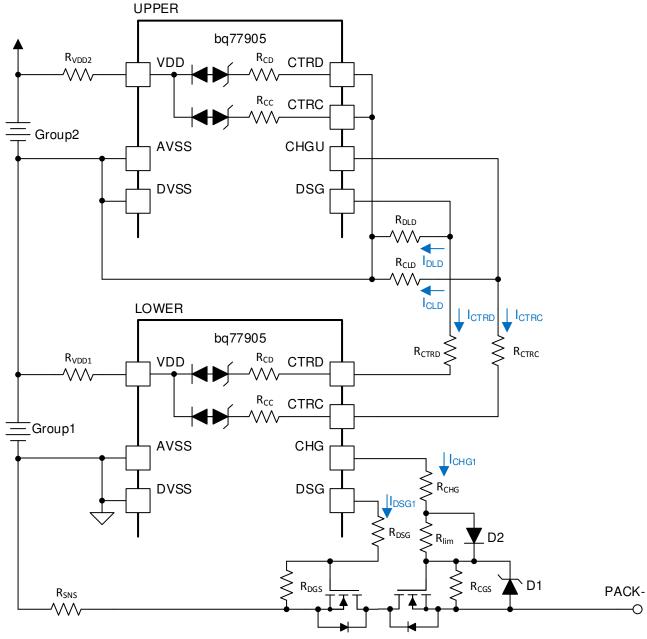

A better method to match the FET load current on the upper device would be to add resistors from the upper device FET outputs to the VSS reference, R<sub>DLD</sub> and R<sub>CLD</sub> as shown in Figure 3-3.

www.ti.com Load Current

Copyright © 2017, Texas Instruments Incorporated

Figure 3-3. Load Matching Resistors

The currents in these load matching resistances are added to the stacking interface currents to match the FET drive currents of the lower device:

$$I_{DLD} + I_{CTRD} = I_{DSG1} ag{5}$$

$$I_{CLD} + I_{CTRC} = I_{CHG1} ag{6}$$

These  $R_{xLD}$  load resistances receive the full  $V_{(FETON)}$  voltage and are unaffected by the clamp voltage for a predictable load current.

$$R_{\chi LD} = V(FETON)/I_{\chi LD}$$

(7)

Since  $I_{CTRx}$  provides some load,  $R_{DLD}$  and  $R_{CLD}$  will be larger than the  $R_{xGS}$  resistance of the lower device. The designer would solve for the equations and select a suitable load resistance from available values. Example

Load Current www.ti.com

calculations in Table 3-1 and Table 3-2 show that load matching resistors can improve the capacity mismatch caused by the FET load.

**Table 3-1. Example DSG Load Calculations**

| Parameter                                                | Source                                                       | Value             |

|----------------------------------------------------------|--------------------------------------------------------------|-------------------|

| V <sub>(FETON)</sub>                                     | Data sheet                                                   | 12 V              |

| R <sub>DGS</sub>                                         | Figure 5-1 R47                                               | 1 ΜΩ              |

| I <sub>DSG1</sub>                                        | Equation 1                                                   | 12 µA             |

| V <sub>CTR(MAXV)</sub>                                   | Data sheet                                                   | 4 V               |

| R <sub>CTRD</sub>                                        | Figure 5-1 R32                                               | 10 ΜΩ             |

| I <sub>CTRD</sub>                                        | Equation 3                                                   | 0.8 μΑ            |

| I <sub>DLD</sub> desired                                 | Equation 5                                                   | 11.2 µA           |

| Capacity difference without matching load                | Load mismatch current × 24 hours per day × 365 days per year | 98 mAH per year   |

| R <sub>DLD</sub> desired                                 | Equation 7                                                   | 1.07 ΜΩ           |

| R <sub>DLD</sub> selected                                | Standard 5% value                                            | 1.1 ΜΩ            |

| Nominal current error                                    | 12 × (1 / 1.07 – 1 / 1.1)                                    | 0.305 μΑ          |

| Capacity difference with 5% matching load resistor value | Load mismatch current × 24 hours per day × 365 days per year | 2.68 mAH per year |

**Table 3-2. Example CHG Load Calculations**

| Parameter                                                | Source                                                       | Value              |

|----------------------------------------------------------|--------------------------------------------------------------|--------------------|

| V <sub>(FETON)</sub>                                     | Data sheet                                                   | 12 V               |

| $V_{D2}$                                                 | Estimate from data sheet                                     | 0.4 V              |

| R <sub>CGS</sub>                                         | Figure 5-1 R48                                               | 3.3 ΜΩ             |

| I <sub>CHG1</sub>                                        | Equation 2                                                   | 3.52 µA            |

| V <sub>CTR(MAXV)</sub>                                   | Data sheet                                                   | 4 V                |

| R <sub>CTRC</sub>                                        | Figure 5-1 R33                                               | 10 ΜΩ              |

| ICTRC                                                    | Equation 3                                                   | 0.8 μΑ             |

| I <sub>CLD</sub> desired                                 | Equation 6                                                   | 2.72 μΑ            |

| Capacity difference without matching load                | Load mismatch current × 24 hours per day × 365 days per year | 24 mAH per year    |

| R <sub>CLD</sub> desired                                 | Equation 7                                                   | 4.41 MΩ            |

| R <sub>CLD</sub> selected                                | Standard 5% value                                            | 4.3 ΜΩ             |

| Nominal current error                                    | 12 × (1 / 4.41 – 1 / 4.3)                                    | –70.7 nA           |

| Capacity difference with 5% matching load resistor value | Load mismatch current × 24 hours per day × 365 days per year | –0.62 mAH per year |

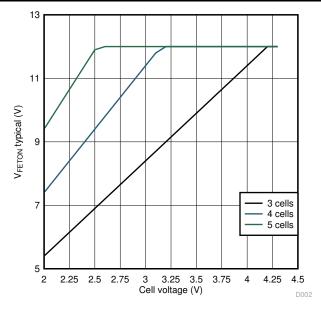

The previous calculations assume the  $V_{(FETON)}$  voltage is in regulation as would be the case with 5 cell stacks and high voltage cells. With lower cell counts and voltages, the FET drive voltage will drop out of regulation as shown in Figure 3-4. When each device supports the same number of cells, the voltages should match and not be a concern. When the devices have different numbers of cells, use the  $V_{(FETON)}$  from the normal system condition in calculations to equalize currents.

www.ti.com Load Current

Figure 3-4. FET Drive Voltage With Cell Variation

Troubleshooting FAQ www.ti.com

## 4 Troubleshooting FAQ

#### Q: What is the limit to how many devices you can stack?

**A:** The bq77905 has no technical limitation on the number of devices in a stack. However, keep in mind that the larger the stack becomes, the greater the noise impact on the CTRC/D signal strength and the greater the total delay time from the top to bottom of the stack. This delay time is not an increase in the individual DUT protections, but it is a minimal increase due to logic propagation across each device in the stack. Typically, this is only 1–10 ms per device added to the stack, so it must be decided if this is a small enough margin for the application.

# Q: What will happen if I make a lower device support more cells than an upper device (for example, if you made DUT#1 support 5 cells and DUT#4 support 3 cells)?

**A:** The system should function appropriately, but this is not recommended as doing so could impact CTRC/D signal strength across the stack. However, the tradeoff would be lower gate voltage on the FETs, so determine if one option is better than the other.

## Q: What changes need to be made for a DUT to support only 3 or 4 cells?

**A:** As mentioned in Section 1.1 and in the data sheet, the CCFG pin must be configured appropriately, and the unused cells must always be chosen as the upper-most cells and shorted to the immediate lower cell (for example, in an 8S cell stack configuration, C4 could be shorted to C3 for 4 cells in DUT#1).

### Q: How do I implement Load Detect for UV Fault Recovery on upper devices?

**A:** As shown in Figure 5-1, connect the LD pins of all devices to PACK– through a  $R_{LD}$  (R8, R18, R28, R44) equal to 300 kΩ and a blocking diode. Also, the  $R_{GS\_CHG}$  (R48) should be increased from the typical 1 MΩ to 3.3 MΩ. Refer to the data sheet ( SLUSCM3) for further detail and explanations.

### Q: How would I decrease the CHG FET turn off time without affecting the UV Load Detect?

**A:** Instead of decreasing the value of the  $R_{GS\_CHG}$  (R48), it is more effective to implement a CHG FET turn off speed circuit. Further detail is explained in Section 3 of the bq77905 Using Multiple FETs (SLUA773) Application Note.

## Q: With a small battery the cells on the bottom device have a lower voltage than the cells of an upper device. Why is this and how can it be avoided?

**A:** The bottom device has a greater load than the upper device due to the FET drive load of the gate-source resistors (Figure 5-1) R47 and R48 being smaller than the stacking interface load on the upper device, RCTR resistors R32 and R33 for example. See Section 3.

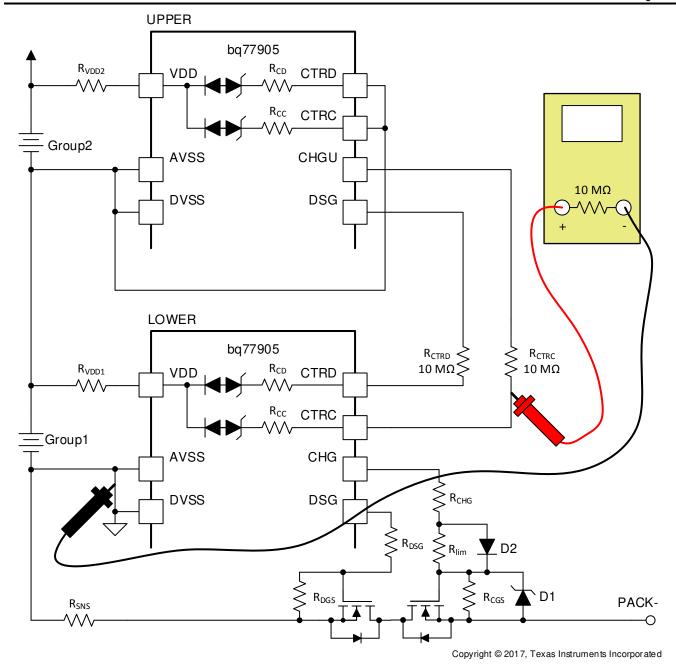

## Q: The FETs turn on, but the voltage measured at CTRC or CTRD indicates the FETs should be off. Why is this?

**A:** The CTRC and CTRD nodes have a high impedance source. When a meter is attached such as in Figure 4-1 the meter becomes part of the circuit forming a voltage divider and alters the voltage at CTRx. If the gate voltage is measured at the same time the FETs may be observed to turn off. Measuring CTRx with respect to VDD will reduce the influence of the meter. If the meter input can be set to high impedance, a better measurement will be obtained, but loading will still occur.

Figure 4-1. Measurement Loading Example on CTRC

References www.ti.com

## **5 References**

For additional information, refer to the following documents available at www.ti.com:

- bq77904 / bq77905: 3-5S Low Power Protector data sheet ( SLUSCM3)

- bq77905 EVM User's Guide (SLVUAN2)

- bq77905 Using Multiple FETs (SLUA773)

- bq77905 Separate Current Paths (SLUA772)

www.ti.com References

Copyright © 2016, Texas Instruments Incorporated

Figure 5-1. Schematic

## **6 Revision History**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| Changes from Revision A (July 2017) to Revision B (June 2021)                                 |      |  |

|-----------------------------------------------------------------------------------------------|------|--|

| Updated the numbering format for tables, figures and cross-references throughout the document |      |  |

| Changes from Revision * (July 2016) to Revision A (July 2017)                                 | Page |  |

| Added Load Current section                                                                    | 4    |  |

| Added FAQ about lower voltage in the lower device                                             | 10   |  |

| Added FAQ on CTRx measurement with image                                                      |      |  |

|                                                                                               |      |  |

## IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022, Texas Instruments Incorporated