# Embedded Scheduler in Cell Battery Monitor of the bq769x0

Vish Nadarajah

Battery Management System/Monitoring & Protection

## ABSTRACT

The Scheduler is the most critical digital embedded block inside the cell battery monitor IC, providing the crucial timing frame to the monitor. This application note expands on the parameters detailed in measurement – synchronizing the timing of the ADC modulator schedule during the Coulomb Counting and cell balancing. Understanding the operations of the Scheduler allows the user to implement optimized cell balancing algorithms, polling of the ADC via the host microcontroller.

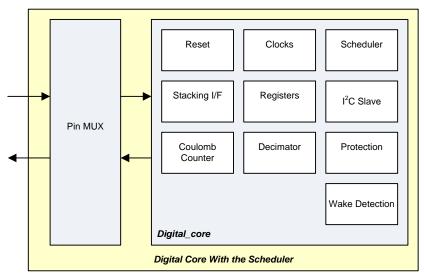

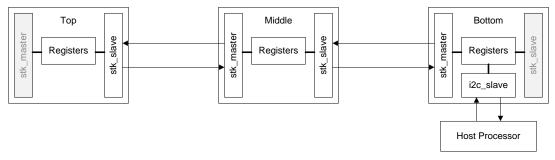

Figure 1. Embedded Scheduler as Part of the Digital Core

## Contents

| 1                                 | Operations of the Scheduler       | 2 |  |

|-----------------------------------|-----------------------------------|---|--|

| 2 Scheduler and the ADC System    |                                   |   |  |

|                                   | 2.1 Cell Balancing OFF            |   |  |

|                                   | 2.2 Passive Cell Balancing ON     |   |  |

| 3                                 | Scheduler and the Coulomb Counter | 8 |  |

| 4 Scheduler in Stacking Interface |                                   |   |  |

|                                   |                                   |   |  |

## List of Figures

| 1 | Embedded Scheduler as Part of the Digital Core       | 1 |

|---|------------------------------------------------------|---|

| 2 | 14-Bit ADC System                                    | 2 |

| 3 | Scheduler ADC Measurement Window Without Balancing   | 3 |

| 4 | Scheduler Time Frame Window During Without Balancing | 3 |

| 5 | Scheduler – Balance vs Measure                       | 5 |

| 6 | Passive Cell Balancing of 2 Cells Timing             | 5 |

|   |                                                      |   |

All trademarks are the property of their respective owners.

Operations of the Scheduler

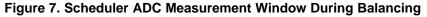

| 7  | Scheduler ADC Measurement Window During Balancing | 5 |

|----|---------------------------------------------------|---|

|    | Scheduler Time Frame Window During Balancing      |   |

| 9  | 16-Bit Delta Sigma Coulomb Counter                | 8 |

| 10 | Stacking Interface                                | 9 |

|    |                                                   |   |

### List of Tables

| 1 | Scheduling During Normal Mode Without Balancing        | 4 |

|---|--------------------------------------------------------|---|

| 2 | Scheduling for Normal Mode With Passive Cell Balancing | 7 |

## **1** Operations of the Scheduler

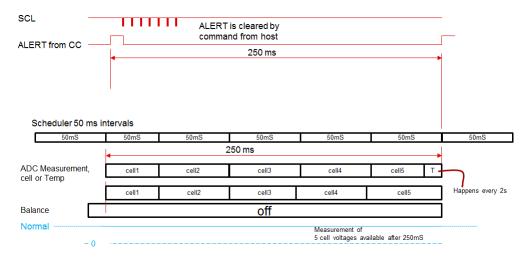

The ADC and Coulomb Counter are synchronized in the Scheduler to the 250 ms measurement period. The Scheduler is responsible for controlling the start and stop times of voltage measurements, coulomb counting, cell balancing, and stacked communications. The Scheduler is a state machine that operates on the 12.5 ms time slice from the internally-generated system clock block. The system clock is generated internally and runs at 256 kHz.

The Scheduler initiates a new frame every 250 ms. Every 2 seconds (8 frames), the Scheduler digitizes the temperature measurement information as illustrated in Figure 4. The Scheduler schedules each cell voltage to be measured 12.5 ms during passive balancing and 50 ms when passive balancing is turned off. The Scheduler provides the time slices for 5 voltages measured by the Decimator (VC1-VC5), and up to 10 additional voltages are stored in the register space (VC6-VC15). These voltages are measured in the middle and upper die of a stacked system and relayed to the bottom device via the stacked communications interface.

A fault condition will be detected approximately 0 to 250 ms after the event. For faults detected in the middle and top stacked devices, an additional communications delay is incurred. Cell voltages are transferred from the middle to bottom device and top to middle device once every 125 ms. Therefore, it can take from approximately 0 to 125 ms for a measurement to be transferred to the next lower device. In a 3-stacked system, this can be double for the top device. Finally, the comparison is done only once every 125 ms.

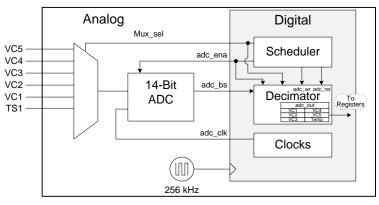

# 2 Scheduler and the ADC System

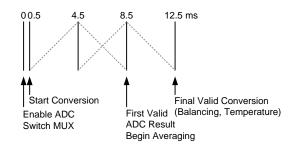

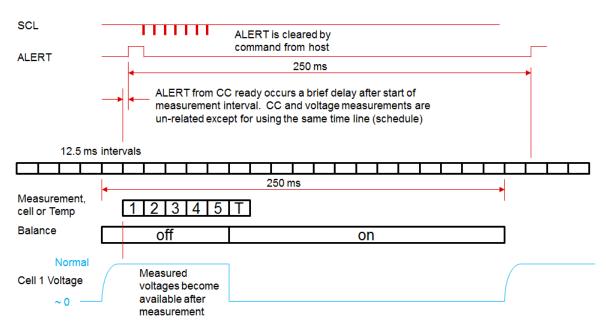

The *14-Bit ADC System* is represented in Figure 2. The digital block controls the clocks, enables, and select lines to the modulator and analog MUX'es. The modulator bit-stream is attenuated and decimated to produce a 14-bit result.

Figure 2. 14-Bit ADC System

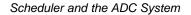

# 2.1 Cell Balancing OFF

When cell balancing is OFF, each ADC channel is measured over a 50-ms window, as shown in Figure 2. At the beginning of the cycle, the ADC is enabled, the channel MUX is switched, or both occur. The first 500  $\mu$ s of the cycle allow for settling before decimation begins. Eleven conversions are averaged over the window. At the end of the window, the average is stored as shown in Figure 3.

Measuring of 5 cell voltages is accomplished over one 250-ms period. Eight periods make up a 2-second super period. During the first 250 ms period of the 2-second super period, the cell voltage 5 measurement window is reduced to 37.5 ms and temperature is measured during the excess 12.5 ms. Table 1 shows the schedule during normal mode.

Figure 3. Scheduler ADC Measurement Window Without Balancing

Figure 4. Scheduler Time Frame Window During Without Balancing

Table 1 shows the schedule during normal mode.

| tick_cnt | time (ms) | Measure      | Stack                             | Volt Comp                       |

|----------|-----------|--------------|-----------------------------------|---------------------------------|

| 0        | 0.0       | VC1          | Start↑                            |                                 |

| 1        | 12.5      | $\downarrow$ | First stack communication at 0 ms |                                 |

| 2        | 25.0      | $\downarrow$ |                                   |                                 |

| 3        | 37.5      | $\downarrow$ |                                   |                                 |

| 4        | 50.0      | VC2          |                                   | Start↑                          |

| 5        | 62.5      | $\downarrow$ |                                   | First OV/UV comparison at 50 ms |

| 6        | 75.0      | $\downarrow$ |                                   |                                 |

| 7        | 87.5      | $\downarrow$ |                                   |                                 |

| 8        | 100.0     | VC3          |                                   |                                 |

| 9        | 112.5     | $\downarrow$ |                                   |                                 |

| 10       | 125.0     | $\downarrow$ | Start↑                            |                                 |

| 11       | 137.5     | $\downarrow$ |                                   |                                 |

| 12       | 150.0     | VC4          |                                   |                                 |

| 13       | 162.5     | $\downarrow$ |                                   |                                 |

| 14       | 175.0     | $\downarrow$ |                                   | Start↑                          |

| 15       | 187.5     | $\downarrow$ |                                   |                                 |

| 16       | 200.0     | VC5          |                                   |                                 |

| 17       | 212.5     | $\downarrow$ |                                   |                                 |

| 18       | 225.0     | $\downarrow$ |                                   |                                 |

| 19       | 237.5     | Temp         |                                   |                                 |

| 20       | 250.0     | VC1          | Start↑                            |                                 |

| 21       | 262.5     | $\downarrow$ |                                   |                                 |

| 22       | 275.0     | $\downarrow$ |                                   |                                 |

| 23       | 287.5     | $\downarrow$ |                                   |                                 |

| 24       | 300.0     | VC2          |                                   | Start↑                          |

| 25       | 312.5     | $\downarrow$ |                                   |                                 |

| 26       | 325.0     | $\downarrow$ |                                   |                                 |

| 27       | 337.5     | $\downarrow$ |                                   |                                 |

| 28       | 350.0     | VC3          |                                   |                                 |

| 29       | 362.5     | $\downarrow$ |                                   |                                 |

| 30       | 375.0     | $\downarrow$ | Start↑                            |                                 |

| 31       | 387.5     | $\downarrow$ |                                   |                                 |

| 32       | 400.0     | VC4          |                                   |                                 |

| 33       | 412.5     | $\downarrow$ |                                   |                                 |

| 34       | 425.0     | $\downarrow$ |                                   | Start↑                          |

| 35       | 437.5     | $\downarrow$ |                                   |                                 |

| 36       | 450.0     | VC5          |                                   |                                 |

| 37       | 462.5     | $\downarrow$ |                                   |                                 |

| 38       | 475.0     | $\downarrow$ |                                   |                                 |

| 39       | 487.5     | $\downarrow$ |                                   |                                 |

| 40       | 500.0     |              |                                   |                                 |

# Table 1. Scheduling During Normal Mode Without Balancing

# 2.2 Passive Cell Balancing ON

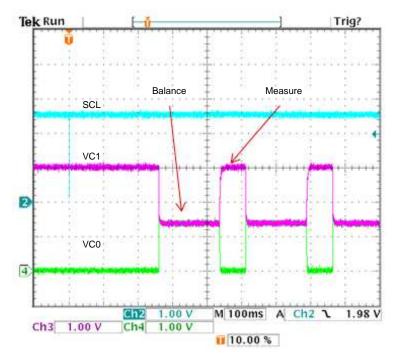

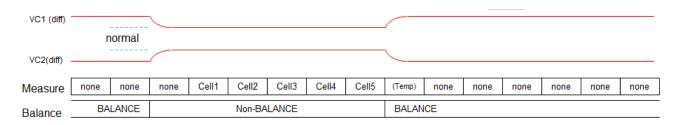

When passive cell balancing is ON, each cell is measured by ADC for 12.5 ms as well as temperature in the first 250 ms period of the 2 second period. The remaining time is allocated to balancing. The values in the balancing registers are masked during the measurement time.

Figure 5. Scheduler – Balance vs Measure

## Figure 6. Passive Cell Balancing of 2 Cells Timing

When temperature measurements on the TS pin are selected, the thermistor bias is enabled 37.5 ms before the measurement begins and is then disabled after the measurement window is done as shown in Figure 8 and Table 2.

Figure 8. Scheduler Time Frame Window During Balancing

Table 2 shows the Scheduler for normal mode with passive cell balancing.

| tick_cnt | time (ms) | Measure | Stack                   | Volt Comp                 |

|----------|-----------|---------|-------------------------|---------------------------|

| 0        | 0.0       | VC1     | Start∱                  |                           |

| 1        | 12.5      | VC2     |                         |                           |

| 2        | 25.0      | VC3     | First stack<br>comms at |                           |

| 3        | 37.5      | VC4     | 0 ms                    |                           |

| 4        | 50.0      | VC5     |                         | Start∱                    |

| 5        | 62.5      | Temp    |                         |                           |

| 6        | 75.0      | BAL     |                         | First OV/UV<br>comparison |

| 7        | 87.5      | BAL     |                         | at 50 ms                  |

| 8        | 100.0     | BAL     |                         |                           |

| 9        | 112.5     | BAL     |                         |                           |

| 10       | 125.0     | BAL     | Start∱                  |                           |

| 11       | 137.5     | BAL     |                         |                           |

| 12       | 150.0     | BAL     |                         |                           |

| 13       | 162.5     | BAL     |                         |                           |

| 14       | 175.0     | BAL     |                         | Start∱                    |

| 15       | 187.5     | BAL     |                         | -                         |

| 16       | 200.0     | BAL     |                         |                           |

| 17       | 212.5     | BAL     |                         |                           |

| 18       | 225.0     | BAL     | 2                       |                           |

| 19       | 237.5     | BAL     |                         |                           |

| 20       | 250.0     | VC1     | Start∱                  |                           |

| 21       | 262.5     | VC2     |                         |                           |

| 22       | 275.0     | VC3     |                         |                           |

| 23       | 287.5     | VC4     |                         |                           |

| 24       | 300.0     | VC5     |                         | Start∱                    |

| 25       | 312.5     | BAL     |                         |                           |

| 26       | 325.0     | BAL     |                         |                           |

| 27       | 337.5     | BAL     |                         |                           |

| 28       | 350.0     | BAL     |                         |                           |

| 29       | 362.5     | BAL     |                         |                           |

| 30       | 375.0     | BAL     | Start†                  |                           |

| 31       | 387.5     | BAL     |                         |                           |

| 32       | 400.0     | BAL     |                         |                           |

| 33       | 412.5     | BAL     |                         |                           |

| 34       | 425.0     | BAL     |                         | Start†                    |

| 35       | 437.5     | BAL     |                         |                           |

| 36       | 450.0     | BAL     |                         |                           |

| 37       | 462.5     | BAL     |                         |                           |

| 38       | 475.0     | BAL     |                         |                           |

| 39       | 487.5     | BAL     |                         |                           |

| 40       | 500.0     | BAL     |                         |                           |

# Table 2. Scheduling for Normal Mode With Passive Cell Balancing

A 12.5-ms measurement window is also used for all measurements when cell balancing is ON. This is shown in Table 2. When balancing is ON, the excess time in the 250 ms period is used for balancing.

## 3 Scheduler and the Coulomb Counter

Integrating 16-bit Delta-Sigma ADC, also called Coulomb Counter (CC), effectively measures accumulated charges "coulombs" across the sense resistor, using a 250-ms integration window generated by the *Scheduler*. The integration time (250 ms) is equivalent to the time needed for a single read through the decimation filter. The decimator comprises two FIR filters with a window function to generate the coefficients.

The CC integrates the values over a timeframe of 250 ms. After the initial BOOT (and CC\_ENABLE being set), the first CC\_READY occurs at around 400 ms. The first conversion will contain the integrated values obtained in the "250 ms frame" preceding CC\_READY. Prior to the CC\_READY flag going up, the CC registers are all cleared to ZEROs. Consecutive conversion of the CC happens at 250-ms intervals.

The Coulomb counting system is shown in Figure 9. The CC is controlled by the *Scheduler* via internal signals: the 'cc\_ena' and 'cc\_wr' signals. The 'cc\_ena' is the general enable signal and gates the clock to the block. When 'cc\_ena' is high, bit-stream counting commences. When 'cc\_wr' is pulsed, the current count is stored to the read-only results register and the count is reset. In addition, the 'cc\_ready' signal is raised. This signal generates an alert status via the Register block and is cleared by the 'cc\_ready\_clr' signal originating from the Register block. The clear signal is initiated by the host processor external to the bqMaximo device.

Figure 9. 16-Bit Delta Sigma Coulomb Counter

Two counting modes are available. In continuous counting, the scheduler holds 'cc\_ena' high while 'cc\_wr' is pulsed every 64000 cycles. In one-shot mode, the *Scheduler* raises 'cc\_ena' for only a single accumulation period.

The registered count is stored locally in the Coulomb Counter block and is read from either the I2C or stacking interfaces via the Register block. Each time 'cc\_wr' is pulsed the new result overwrites the previous result. There is no flag to detect this condition: It is the responsibility of the host processor to respond to the ready alert in a timely manner.

The digital block controls the clock and enable to the modulator. The modulator bit-stream is accumulated using a CC filter. The CC maintains a 16-bit signed count which initializes to –32000 (full-scale negative). When the counter is enabled, a bit-stream value of '1' bit causes the counter to increment. A single accumulation period is 64000 cycles (250 ms).

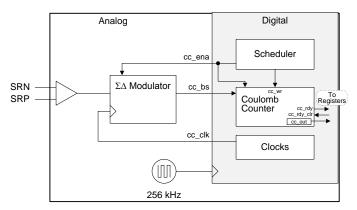

## 4 Scheduler in Stacking Interface

The master functionality in the bottom and middle die is initiated by the *Scheduler* of that device. The *Schedulers* in different devices run independently from each other and are not synchronized to one another.

Internally, up to 3 die can be daisy-chained together as in a multi-chip module (MCM) as depicted in Figure 10. In such a system – stacked MCMs as in bq769030 and bq76940 – the stacking interface is used to communicate control information up the stack (from bottom to the top die) and measurement data and status information flow down the stack (from top to bottom). Two bits in the EEPROM identify whether a device is standalone (non-stacked-bq76920), bottom, middle, or top.

The bottom device acts as a master when communicating with the middle or top device. The middle device acts as a slave when communicating with the bottom device, and as a master when communicating with the top device. The top device always acts as a slave.

Figure 10. Stacking Interface

The bottom device is responsible for testing all 15 voltages for overvoltage and undervoltage (OV / UV) faults. The state machine cycles through all 15 cell voltage registers, comparing each to the OV and UV limits. The 'ov\_detect' and 'uv\_detect' signals are cleared at the beginning of the comparison. At the end of the comparison, if any cell voltage reading is above the OV trip threshold, the OV timer is incremented. Likewise, if any cell voltage is below the UV trip threshold and above the UV ignore threshold (approximately 500 mV) 'uv\_detect' will be set and the UV timer will be incremented. If the detection signal is low, the timer is reset.

## **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

| Products<br>Audio<br>Amplifiers<br>Data Converters<br>DLP® Products | www.ti.com/audio<br>amplifier.ti.com<br>dataconverter.ti.com<br>www.dlp.com | Applications<br>Automotive and Transportation<br>Communications and Telecom<br>Computers and Peripherals<br>Consumer Electronics | www.ti.com/automotive<br>www.ti.com/communications<br>www.ti.com/computers<br>www.ti.com/consumer-apps |

|---------------------------------------------------------------------|-----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| DSP                                                                 | dsp.ti.com                                                                  | Energy and Lighting                                                                                                              | www.ti.com/energy                                                                                      |

| Clocks and Timers                                                   | www.ti.com/clocks                                                           | Industrial                                                                                                                       | www.ti.com/industrial                                                                                  |

| Interface                                                           | interface.ti.com                                                            | Medical                                                                                                                          | www.ti.com/medical                                                                                     |

| Logic                                                               | logic.ti.com                                                                | Security                                                                                                                         | www.ti.com/security                                                                                    |

| Power Mgmt                                                          | power.ti.com                                                                | Space, Avionics and Defense                                                                                                      | www.ti.com/space-avionics-defense                                                                      |

| Microcontrollers                                                    | microcontroller.ti.com                                                      | Video and Imaging                                                                                                                | www.ti.com/video                                                                                       |

| RFID                                                                | www.ti-rfid.com                                                             |                                                                                                                                  |                                                                                                        |

| OMAP Applications Processors                                        | www.ti.com/omap                                                             | TI E2E Community                                                                                                                 | e2e.ti.com                                                                                             |

| Wireless Connectivity                                               | www.ti.com/wirelessconne                                                    | ctivity                                                                                                                          |                                                                                                        |

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2016, Texas Instruments Incorporated