# Voltage Mode Boost Converter Small Signal Control Loop Analysis Using the TPS61030

Rick Zaitsu PMP - PPM Converters

#### **ABSTRACT**

A voltage-mode controlled boost converter running in continuous conduction mode is more difficult to stabilize than a buck converter due to the boost converter's inherent Right Half Plane-zero (RHP-zero). The boost converter's double-pole and RHP-zero are dependant on the input voltage, output voltage, load resistance, inductance, and output capacitance, further complicating the transfer function. Understanding the transfer function and having a method to stabilize the converter is important to achieve proper operation.

|      | Contents                                                                                                                                                                                                      |     |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 1    | Transfer Function of Boost Converter                                                                                                                                                                          | . 2 |

| 2    | Method for Stabilizing the TPS61030                                                                                                                                                                           | . 6 |

| 3    | Example 1; High Output Current (2 A) With Tantalum Capacitor                                                                                                                                                  | 11  |

| 4    | Example 2; High Output Current (2 A) With Ceramic Capacitor                                                                                                                                                   | 14  |

| 5    | Example 3; Low Output Current (I <sub>o</sub> = 0.4 A) With Ceramic Capacitor                                                                                                                                 | 17  |

| 6    | Conclusion                                                                                                                                                                                                    |     |

| Appe | ndix A State Space Averaging Method                                                                                                                                                                           | 19  |

|      | List of Figures                                                                                                                                                                                               |     |

| 1    | Boost Converter Block Diagram                                                                                                                                                                                 | . 2 |

| 2    | Bode plot of the Double-Pole Transfer Function                                                                                                                                                                | . 3 |

| 3    | Bode plot of the RHP-Zero Transfer Function                                                                                                                                                                   |     |

| 4    | Bode-Plot of Boost Converter                                                                                                                                                                                  |     |

| 5    | Block Diagram of a Typical Boost Converter                                                                                                                                                                    | . 5 |

| 6    | Bode-Plot Illustration of Stability Criteria                                                                                                                                                                  |     |

| 7    | Feedback network and Feed Forward Compensation Network                                                                                                                                                        | . 8 |

| 8    | Example of Transfer Function of Feedback Network and Feed Forward                                                                                                                                             |     |

| _    | Compensation Network                                                                                                                                                                                          |     |

| 9    | Flow Chart of Design Process                                                                                                                                                                                  |     |

| 10   | Block Diagram of Converter                                                                                                                                                                                    | 11  |

| 11   | Mathcad Calculated Bode-Plot of Transfer Function for High Current With Tantalum                                                                                                                              | 40  |

| 40   | Output Capacitor                                                                                                                                                                                              | 12  |

| 12   | Measured Bode-Plot and Load Transient Waveform With Tantalum Capacitor ( $V_{IN} = 3.0 \text{ V}$ , $V_0 = 3.6 \text{ V}$ , $I_0 = 2 \text{ A}$ , $C = 100 \mu\text{F} \times 2 \text{ tantalum capacitor}$ ) | 13  |

| 13   | Block Diagram of Converter                                                                                                                                                                                    | 14  |

| 14   | Mathcad Calculated Bode-Plot of Transfer Function for High Output Current and                                                                                                                                 |     |

| • •  | Ceramic Output Capacitor                                                                                                                                                                                      | 15  |

| 15   | Measured Bode-Plot and Load Transient Waveform With Ceramic Capacitor ( $V_{IN} = 3.0 \text{ V}, V_0 = 3.6 \text{ V}, I_0 = 2 \text{ A}, C = 100 \mu\text{F} \times 2 \text{ Ceramic Capacitor}$ )            | 16  |

| 16   | Block Diagram of Converter                                                                                                                                                                                    |     |

| 17   | Mathcad Calculated Bode-Plot of Transfer Function for Low Output Current and                                                                                                                                  | -   |

|      | Ceramic Output Capacitor                                                                                                                                                                                      | 18  |

| 18   | Measured Load Transient Waveform                                                                                                                                                                              | 18  |

Mathcad is a trademark of Parametric Technology Corporation.

#### 1 Transfer Function of Boost Converter

#### 1.1 Transfer Function of Power Stage

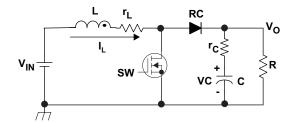

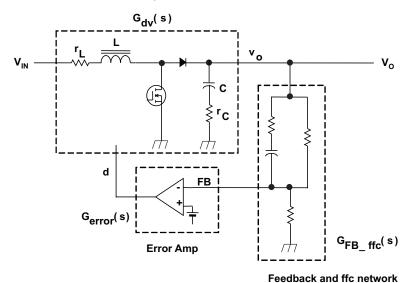

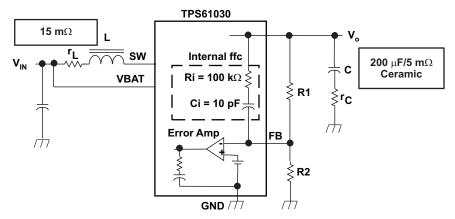

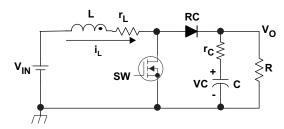

Figure 1 shows the block diagram of the boost converter. Using the *state space averaging model*, the small-signal transfer function from the duty cycle (D) of the switch to the boost converter output ( $v_o$ ) in continuous conduction mode (CCM) can be derived. Equation 1 through Equation 6 are well known simplified equations for this model as derived previously in application note (SLVA061) [1].

Figure 1. Boost Converter Block Diagram

$$G_{dv} = \frac{\hat{v}_{O}}{\hat{d}} \cong G_{do} \cdot \frac{\left(1 + \frac{s}{\omega_{Z1}}\right) \cdot \left(1 - \frac{s}{\omega_{RHP-zero}}\right)}{1 + \frac{s}{\omega_{O} \cdot Q} + \frac{s^{2}}{\omega_{O}^{2}}}$$

$$(1)$$

Where

$$G_{do} \approx \frac{V_{IN}}{(1-D)^2} = \frac{V_o^2}{V_{IN}}$$

(2)

$$\omega_{Z1} = \frac{1}{r_C \cdot C} \tag{3}$$

$$\omega_{\text{RHP-zero}} \approx \frac{(1-D)^2 \cdot (R - r_L)}{L} \approx \frac{R}{L} \cdot \left(\frac{V_{\text{IN}}}{V_o}\right)^2 \qquad \text{or} \qquad \left(f_{\text{RHP-zero}} \approx \frac{R}{2\pi \cdot L} \left(\frac{V_{\text{IN}}}{V_o}\right)^2\right) \tag{4}$$

$$\omega_0 \approx \frac{1}{\sqrt{L \cdot C}} \cdot \sqrt{\frac{r_L + (1 - D)^2 \cdot R}{R}} \approx \frac{1}{\sqrt{L \cdot C}} \cdot \frac{V_{IN}}{V_o} \quad \text{or} \quad \left( f_O \approx \frac{1}{2\pi\sqrt{LC}} \cdot \frac{V_{IN}}{V_o} \right) \tag{5}$$

$$Q \approx \frac{\frac{\omega_0}{\Gamma_L} + \frac{1}{C \times (R + r_c)}}$$

(6)

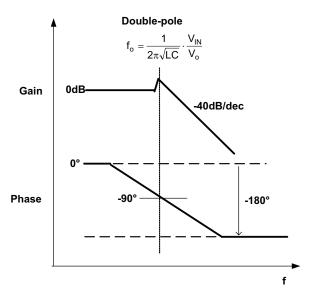

Equation 1 consists of a double-pole, RHP-zero and ESR-zero. For this discussion, the ESR-zero will be ignored because it is at a much higher frequency than the double-pole frequency and RHP-zero. Figure 2 shows a Bode plot of the double-pole transfer function.

Figure 2. Bode plot of the Double-Pole Transfer Function

The double pole frequency  $f_O$  depends on the input voltage ( $V_{IN}$ ) and the output voltage ( $V_o$ ) as well as inductance (L) and output capacitance (C).

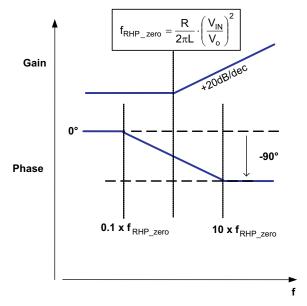

Figure 3 shows a Bode plot of the RHP-zero,  $f_{\rm RHP-zero}$  transfer function.

Figure 3. Bode plot of the RHP-Zero Transfer Function

It is also important to note that  $f_{\text{RHP-zero}}$  depends on load resistance (R) and inductance (L) as well as input voltage (V<sub>IN</sub>) and output voltage (V<sub>o</sub>). Complicating loop gain stabilization is the fact that while the RHP-zero phase begins to drop at  $0.1 \times f_{\text{RHP-zero}}$ , the gain increases at 20 dB/dec from  $f_{\text{RHP-zero}}$ . The following example helps illustrate the RHP-zero complexity.

Consider the following parameters:

$$\begin{split} L &= 10 \; \mu H, \\ C_o &= 100 \; \mu F \\ V_{IN} &= 3 \; V \\ V_o &= 3.6 \; V \\ I_o &= 2 \; A \; (R = 1.8 \; \Omega) \end{split}$$

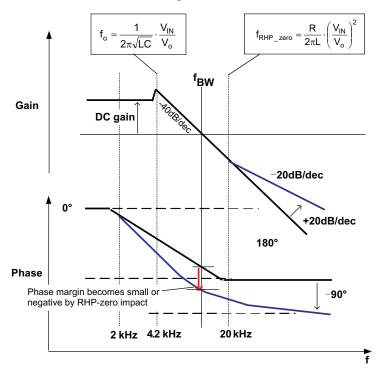

The frequency of  $f_{\rm O}$  and  $f_{\rm RHP-zero}$  are calculated using Equation 4 and Equation 5 as follows;

$$f_{RHP-zero} = \frac{1.8}{2\pi \times 10 \,\mu\text{H}} \times \left(\frac{3}{3.6}\right)^2 = 20 \,\text{kHz}$$

$$f_o = \frac{1}{2\pi \sqrt{10 \,\mu\text{H} \times 100 \,\mu\text{F}}} \times \frac{3}{3.6} = 4.2 \,\text{kHz}$$

(8)

As shown in Figure 4, even though the addition of the RHP-zero is at a higher frequency than the converter double pole, the RHP-zero phase drop starts a decade earlier, and therefore negatively impacts the potential phase margin of the converter's control loop. This is the nature of instability of a voltage-mode controlled boost converter running in CCM.

Figure 4. Bode-Plot of Boost Converter

As shown in Equation 7 and Equation 8, the  $f_{\rm O}$  and  $f_{\rm RHP-zero}$  depend on  $V_{\rm IN}$ ,  $V_{\rm o}$ , R ( $I_{\rm o}$ ), L, and C. A larger load current  $I_{\rm o}$  (smaller load resistance R) has a significant impact on  $f_{\rm RHP-zero}$ , bringing it closer to  $f_{\rm o}$ , which decreases stability margin.

#### 1.2 Complete CCM Boost Converter Power Stage Transfer Function

The simplified versions of Equation 1 through Equation 6 do not illustrate the effect of the output capacitor's ESR ( $r_c$  in Figure 1) and the inductors DCR ( $r_L$ ) as damping factors on the double pole. In order to get an accurate bode-plot, the full version of Equation 9 and Equation 10 are used. See the appendix for the derivation of the entire equation.

$$G_{dv}(s) = \frac{\Delta v_{O}(s)}{\Delta D} = c(sI - A)^{-1} \frac{\partial A}{\partial D} X(s) + \frac{\partial c}{\partial D} X(s) = \frac{(R + r_{C})(sCr_{C} + 1)\left\{-(sL + r_{L})(R + r_{C}) + D^{\prime 2} R^{2}\right\}}{P(s)\left\{D'R(D'R + r_{C}) + r_{L}(R + r_{C})\right\}} \cdot RV_{i}$$

(9)

Where.

$$P(s) = s^{2}LC(R + r_{c})^{2} + s\left\{L(R + r_{c}) + r_{L}C(R + r_{c})^{2} + D'Rr_{c}C(R + r_{c})\right\} + r_{L}(R + r_{c}) + D'R(D'R + r_{c}) \tag{10}$$

### 1.3 Complete Voltage-Mode Controlled CCM Boost Converter Transfer Function

Figure 5 shows the block diagram of a typical boost converter, consisting of the power stage, feedback and feed-forward compensation network, and error amplifier. The complete transfer function G(s) is given as;

$$G(s) = G_{dv}(s) \cdot G_{FB_{fc}}(s) \cdot G_{error}(s)$$

(11)

Where.

G<sub>dv</sub>(s); Transfer function of power stage of boost converter

GFB ffc(s); Transfer function of feedback network and feed forward compensation network

Gerror(s); Transfer function of error amp

Figure 5. Block Diagram of a Typical Boost Converter

#### 2 Method for Stabilizing the TPS61030

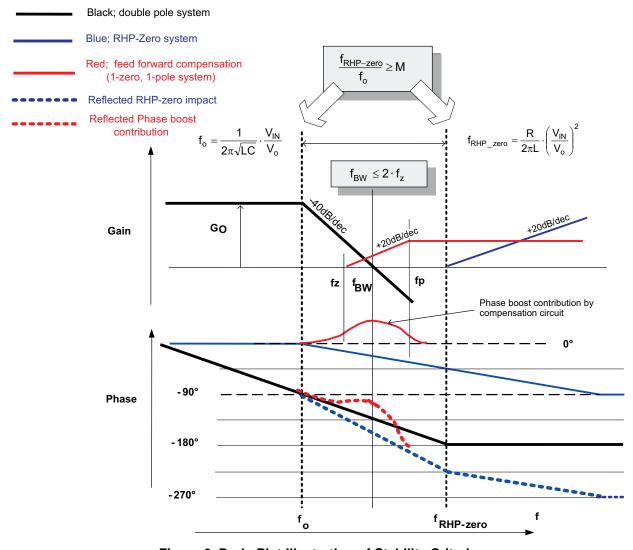

In order to maintain stability for boost converters with voltage mode control schemes, the following conditions must be met:

- 1.  $f_{\text{RHP-zero}}$  must be higher in frequency than  $f_{\text{O}}$  (by ratio M to be explained later) in order to prevent the RHP-zero's phase drop from affecting the power stage's double-pole.

- 2. The crossover frequency ( $f_{\text{BW}}$ ) must be set at or lower than the frequency of the maximum phase-boost effect generated by feed-forward compensation network with zero set at  $f_{\text{Z}}$ . If  $f_{\text{BW}}$  is set higher than the frequency of the maximum phase boost, the phase-boost effect becomes small while gain increases, reducing the stability margin.

To simplify the calculation, assume that the maximum phase-boost frequency is  $2 \times f_z$ . These conditions are illustrated in Figure 6.

Figure 6. Bode-Plot Illustration of Stability Criteria

# 2.1 [STEP 1] Select Output Capacitor

Before calculating the inductance, the minimum output capacitance C<sub>min</sub> is the larger of the minimum capacitance needed to provide the maximum acceptable ripple or minimum voltage dip due to a load transient. The total output ripple is the sum of the ESR ripple (Equation 12) and the output capacitor ripple (Equation 13). Subtracting the ESR ripple from the total acceptable ripple gives the maximum allowed output-capacitor ripple. Rearranging Equation 13 gives Equation 14, from which the minimum output capacitance to provide the maximum acceptable ripple is computed.

$$V_{o\_ripple\_ESR} = I_o \times ESR$$

(12)

$$V_{o\_ripple\_cap} = \frac{I_o \cdot T_{on}}{C} = \frac{I_o}{C} \cdot \left(1 - \frac{V_{IN}}{V_o}\right) \cdot \frac{1}{f}$$

(13)

$$C_{\text{min\_ripple}} = \frac{I_{o}}{V_{o\_ripple\_cap}} \cdot \left(1 - \frac{V_{IN}}{V_{o}}\right) \cdot \frac{1}{f}$$

(14)

The transient response should also be taken into account when selecting the output capacitance. The worst case output-voltage dip due to a load transient occurs when the output capacitor must supply the current for the transient until loop response takes over. So, if the transient duration (dt) and load current ( $i_{tran}$ ) is known, Equation 15 can be used to determine the minimum required capacitance to prevent output voltage dip ( $V_{O-dip}$ ) due to a load transient:

$$C_{min\_tran} = \frac{i_{tran}}{V_{o\_dip}} \cdot dt \approx \frac{i_{tran}}{V_{o\_dip}} \cdot \frac{1}{4 \times f_{BW}}$$

(15)

Where dt is approximated to  $1/4f_{BW}$  to simplify the calculation.

Increasing the output capacitance in most cases decreases the dip during load transients.

# 2.2 [STEP 2] Determine Inductance DCR

Similar to the output capacitor's ESR, the inductor's DCR ( $r_L$ ) has a significant impact on the boost converter power stage's transfer function. In lower output-current applications, relatively high DCR helps the stability by phase damping. The maximum allowable DCR is determined by the amount of loss that is acceptable, i.e., the maximum efficiency required at maximum load. The total power loss consists of the inductor AC and DC losses, SW (N-MOS FET) loss, Diode (P-MOS FET) loss, and control-circuitry power loss. To simplify the calculation, the designer can ignore the inductor's AC losses, compute the inductor's DC loss  $l_{\rm in}^2 \cdot r_L$  (by ignoring ripple component), and set the maximum acceptable inductor DC loss to 30% of the total power loss.

So, setting a target efficiency η,

$$r_{L\_MAX} = \frac{30\% \times P_{total-loss}}{I_{in}^2}$$

(16)

Where,

$$P_{total\_loss} = P_{out} \times \left(\frac{1}{\eta} - 1\right)$$

# 2.3 [STEP 3] Separating the Double-Pole and RHP-Zero Frequencies

Separating the double-pole and RHP-zero frequencies is the most important requirement for maintaining stability. M is the frequency separation ratio between  $f_{\text{RHP-zero}}$  and  $f_{\text{O}}$ , and provides a relative measure of phase drop between the two frequencies. Through empirical testing it has been determined that the phase damping received from tantalum output capacitors with ESR values between 20 m $\Omega$  to 100 m $\Omega$  allows a value of M=10. When using ceramic capacitors that have ESR values of a few m $\Omega$ , thus providing a little phase damping between the two frequencies, more frequency separation is required (M≥15). Note M=10 or M=15 are starting points and final stability should be verified by transient testing in the lab (as mentioned in [STEP 5]).

$$\frac{f_{RHP-zero}}{f_o} \ge M \tag{17}$$

Where,

M=10 (one decade) — for tantalum capacitors.

M=15 — for ceramic capacitors.

Using Equation 4 and Equation 5, we can get:

$$L \le C \cdot \left(\frac{R}{M} \cdot \frac{V_{IN}}{V_o}\right)^2 \tag{18}$$

When load resistance R is at its minimum (meaning  $I_o$  is MAX) and the input voltage is at its minimum, the  $f_o$  and  $f_{\text{RHP-zero}}$  are closest (as shown in Equation 4 and Equation 5) and open loop phase margin is at its minimum. Therefore, Equation 19 provides the maximum limitation of inductance.

$$L_{MAX} = C \cdot \left(\frac{R_{min}}{M} \cdot \frac{V_{IN\_min}}{V_o}\right)^2$$

(19)

#### 2.4 [STEP 4] Maximize Phase Boost Effect of Feed Forward Compensation Network

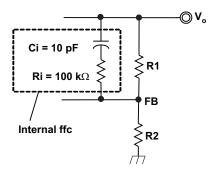

Figure 7 shows the feedback network and feed-forward compensation (ffc) network. The complete transfer function, zero frequency and pole frequency equations are shown in Equation 20 through Equation 22, respectively.

Figure 7. Feedback network and Feed Forward

$$G(s) = \frac{1 + sC_{i}(R1 + R_{i})}{1 + \frac{R1}{R2} + sC_{i}(R1 + R_{i} + \frac{R1R_{i}}{R2})}$$

$$fz = \frac{1}{2\pi C_{i}(R1 + R_{i})}$$

$$fp = \frac{1}{2\pi C_{i} \times \frac{R1R2 + R_{i}R2 + R1R_{i}}{R1 + R2}}$$

(21)

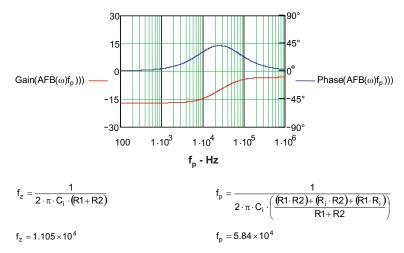

Figure 8 shows the calculated transfer function of this network when R1=1.24 MΩ, R2=200 kΩ, Ci=10 pF, and Ri=100 kΩ. Here Ri and Ci are the integrated ffc network shown in the TPS61030 data sheet. The calculated results are fz=11 kHz, fp=58 kHz, and the maximum phase boost frequency is around 25 kHz as shown in Figure 8. Note that  $f_z$  varies for different output voltages due to R1.

Figure 8. Example of Transfer Function of Feedback Network and Feed Forward Compensation Network

In order to simplify the calculation, assume the maximum frequency for phase boost from the feed-forward network is  $2 \times f_7$ .

$$f_{BW} \le 2 \cdot f_{Z}$$

(23)

Where:

$$f_{BW} \cong f_o \cdot 10^{\frac{G_o}{30}} \tag{24}$$

$$G_o(dB) = 20 \log \left( G_{do} \cdot \frac{5 \cdot R2}{R1 + R2} \right) = 20 \times \log \left( \frac{V_o^2}{V_{IN}} \cdot \frac{5 \cdot R2}{R1 + R2} \right)$$

(25)

Noting that the double-pole has a -40-dB/dec theoretical roll-off, but -30 dB/dec was used to approximate the damping effects of the output capacitor's ESR and the inductor's DCR.

Using Equation 5 and Equation 23 through Equation 25 we can get:

$$L \ge \frac{1}{C} \cdot \left( \frac{1}{2\pi} \cdot \frac{V_{IN}}{V_o} \cdot \frac{10^{\frac{G_o}{30}}}{2 \cdot f_Z} \right)^2 \tag{26}$$

As shown in Equation 5  $f_0$ ; therefore,  $f_{\rm BW}$ , becomes the highest frequency when input voltage  $V_{\rm IN}$  is at maximum. Therefore,  $L_{\rm min}$  is calculated when  $V_{\rm IN}$  is at maximum.

$$L_{min} = \frac{1}{C} \cdot \left( \frac{1}{2\pi} \cdot \frac{V_{IN\_MAX}}{V_o} \cdot \frac{10^{\frac{G_o}{30}}}{2 \cdot f_z} \right)^2$$

(27)

#### 2.5 [STEP 5] Evaluating the Stability Experimentally

The Bode plot obtained from loop gain measurements is important to consider for stability, but should be verified by transient-response test results. To ensure that the load step has frequency components up to the control loop bandwidth, the rise time of the current step should be faster than  $1/f_{\rm BW}$ . The transient-response test includes not only the small signal response, but also the large signal response behavior that occurs in normal applications, while the measured Bode plot shows only the small signal response.

The criteria for evaluating stability using a load-transient test is that if the output rings more than 3 times before settling, the converter has low phase margin and should be re-compensated.

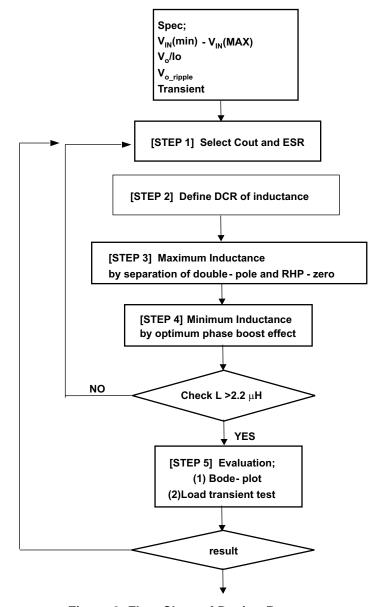

Figure 9 summarize the flow chart of design procedure for stability.

Figure 9. Flow Chart of Design Process

# 3 Example 1; High Output Current (2 A) With Tantalum Capacitor

Figure 10. Block Diagram of Converter

The parameters are:

$$V_{IN} = 3.0 \text{ V} - 3.3 \text{ V}$$

$$V_0 = 3.6 \text{ V}$$

$$I_0 = 2 A (7.2 W)$$

$V_{o\_ripple} = 5 \text{ mV (by capacitance)}$

Target efficiency 90% ( Ploss = 0.8 W, lin = 2.67 A at 3.0  $V_{IN}$ )

$V_{o\_transient} = 250 \text{ mV}$  (assume transient  $I_o = 0 \text{ A}$  to 2 A, and  $f_{BW} = 10 \text{ kHz}$  for calculation purpose below)

Calculating the minimum capacitance using the criteria of the output voltage ripple from Equation 14;

$$C_{\text{min\_ripple}} = \frac{I_o}{V_{o\_ripple\_cap}} \cdot \left(1 - \frac{V_{IN}}{V_o}\right) \cdot \frac{1}{f} = \frac{2}{5mV} \times \left(1 - \frac{3}{3.6}\right) \times \frac{1}{600kHz} \approx 100 \mu F$$

(28)

F.Y.I; Ripple caused by ESR is

$$V_{o \text{ ripple ESR}} = I_{o} \times ESR = 2 \text{ A} \times 25 \text{ m}\Omega = 50 \text{ mV}.$$

Calculating the minimum capacitance using the criteria of the transient output voltage dip from Equation 15;

$$C_{min\_tan} = \frac{i_{tran}}{V_{o\_dip}} \cdot \frac{1}{4f_{BW}} = \frac{2A}{250mV} \times \frac{1}{4 \times 10kHz} = 200 \mu F$$

(29)

From the result of Equation 28 and Equation 29, 200μF was chosen.

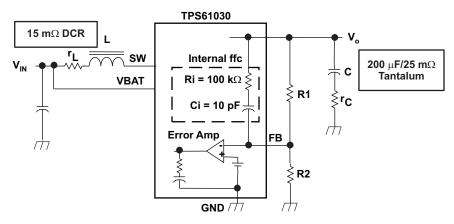

In Figure 10, the feedback network consists of R1=1.24 M $\Omega$  and R2=200 k $\Omega$ . TPS61030 has internal feed forward compensation network (Ri and Ci) across top resistor R1.

$$G_{o}(dB) = 20 \times log\left(\frac{V_{o}^{2}}{V_{i}} \times \frac{5 \times R2}{R1 + R2}\right) = 9.5(dB)$$

(30)

$$L_{MAX} = C \cdot \left(\frac{R_{min}}{10} \cdot \frac{V_{IN\_min}}{V_o}\right)^2 = 200 \,\mu\text{F} \times \left(\frac{1.8}{10} \times \frac{3}{3.6}\right)^2 = 4.5 \,\mu\text{H(MAX)} \tag{31}$$

$$L_{min} = \frac{1}{C} \cdot \left( \frac{1}{2\pi} \cdot \frac{V_{IN\_MAX}}{V_o} \cdot \frac{10^{\frac{Go}{30}}}{2 \cdot f_Z} \right)^2 = \frac{1}{200 \, \mu F} \times \left( \frac{1}{2\pi} \times \frac{3.3}{3.6} \times \frac{10^{\frac{G_o}{30}}}{2 \times 11 k} \right)^2 = 1 \mu H(min)$$

(32)

$$r_{L\_MAX} = \frac{P_{Inductance\_loss}}{I_{in\_MAX}^2} = \frac{0.24W}{2.67 \text{ A}^2} = 33 \text{ m}\Omega$$

(33)

Where,

$$P_{induc \ tan \ ce \ loss} = 30\% \times P_{LOSS} = 30\% \times 0.8 \ W = 0.24 \ W$$

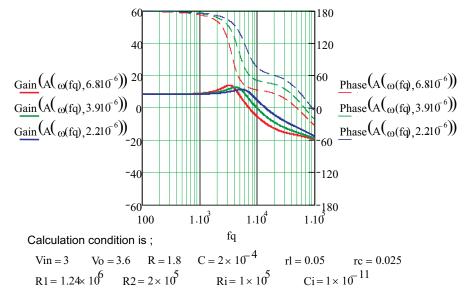

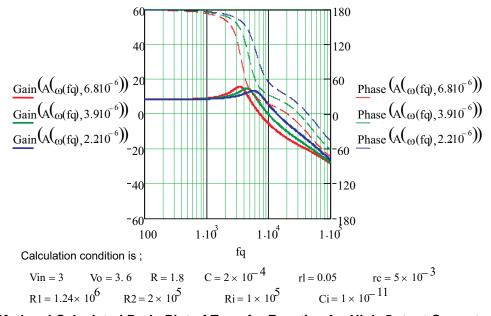

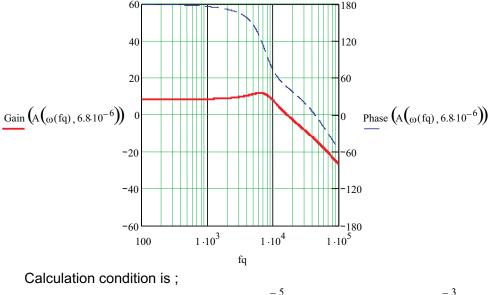

Using the stability design rules, the allowable inductance range is 1  $\mu$ H to 4.5  $\mu$ H. Using the efficiency design requirements, the allowable DCR ( $r_L$ ) of the inductor is less than 33 m $\Omega$ . Figure 11 shows a Mathcad<sup>TM</sup>-calculated Bode plot of the transfer function including the boost power stage, feedback network, feed forward compensation network, and error amp. The inductance values used for these calculations is 6.8  $\mu$ H, 3.9  $\mu$ H and 2.2  $\mu$ H to demonstrate how stability improves due to changing the inductance. The phase gain (M) achieved using these inductance values are as follows:

$L = 6.8 \mu H \text{ is M=8}$   $L = 3.9 \mu H \text{ is M=11}$  $L = 2.2 \mu H \text{ is M=15}$

The calculations consolidate the inductor's DCR and the  $\emph{ON}$  resistance of internal SW into one 50 m $\Omega$  resistor in order to simplify the calculation.

Figure 11. Mathcad Calculated Bode-Plot of Transfer Function for High Current With Tantalum Output Capacitor

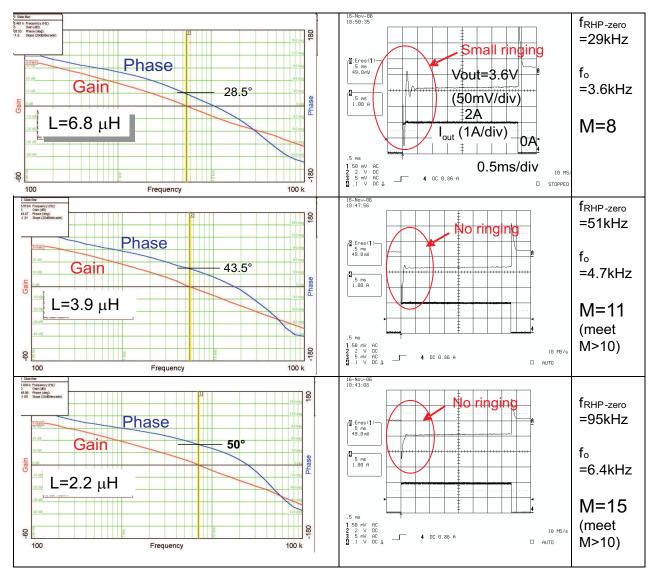

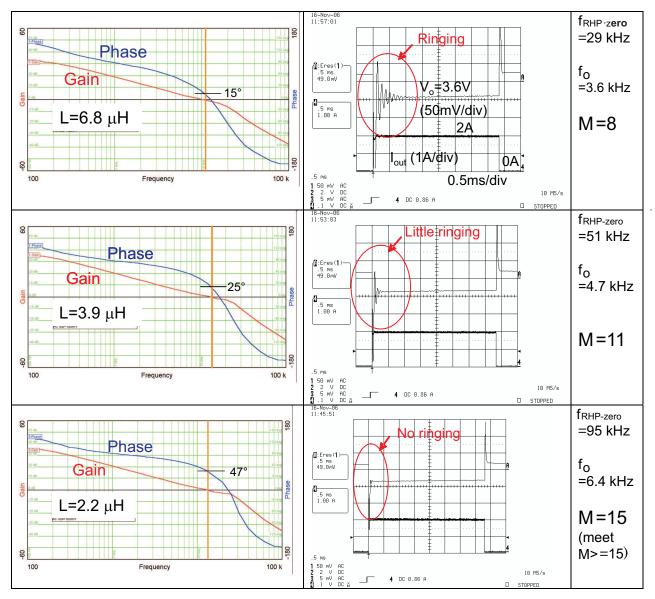

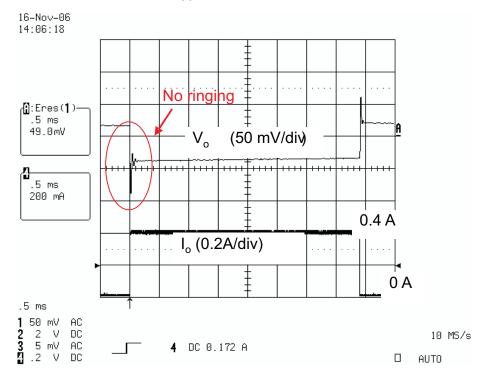

Figure 12 shows the measured Bode-plot of the transfer function and load-transient test waveform. When L=6.8  $\mu$ H (frequency separation ratio M=8), the transient response shows slight ringing while settling. This is a symptom of low phase margin. When L=3.9  $\mu$ H, which is M=11, the transient test shows good response with no ringing while settling. As shown in Equation 17, M>10 is reasonable to provide enough stability margin when a tantalum output capacitor used. 2.2  $\mu$ H shows acceptable phase margin as well. The iInductance DCR used in the test is around 15 m $\Omega$ .

Figure 12. Measured Bode-Plot and Load Transient Waveform With Tantalum Capacitor ( $V_{IN}$  = 3.0 V,  $V_o$  = 3.6 V,  $I_o$  = 2 A, C = 100  $\mu$ F  $\times$  2 tantalum capacitor)

#### 4 Example 2; High Output Current (2 A) With Ceramic Capacitor

Figure 13. Block Diagram of Converter

The next example uses the same parameters as the previous example but with a ceramic output capacitor.

$$V_{IN} = 3.0 \text{ V} - 3.3 \text{ V}$$

$V_o = 3.6 \text{ V}$

$I_o = 2 \text{ A}$

With ceramic capacitors on the output, special attention is needed for stability due to the low ESR. The target of the frequency separation is M>15 as shown by Equation 17.

Following the calculation process,

$$\begin{split} L_{MAX\_ceramic} &= C \cdot \left( \frac{R_{min}}{15} \cdot \frac{V_{IN\_min}}{V_o} \right)^2 = 2 \, \mu H \\ L_{min\_ceramic} &= \frac{1}{C} \cdot \left( \frac{1}{2\pi} \cdot \frac{V_{IN\_MAX}}{V_o} \cdot \frac{10^{\frac{Go}{30}}}{2 \cdot f_Z} \right)^2 = \frac{1}{200 \, \mu F} \times \left( \frac{1}{2\pi} \times \frac{3.3}{3.6} \times \frac{10^{\frac{G_o}{30}}}{2 \times 11 \, k\Omega} \right)^2 = 1 \, \mu H(min) \end{split} \tag{35}$$

From the calculation results, the range of inductance is 1  $\mu$ H to 2  $\mu$ H. Choose 2.2  $\mu$ H due to minimum inductance requirement in the data sheet.

Figure 14 shows a Mathcad-calculated Bode-plot of the transfer function with ESR=5 m $\Omega$  (assuming capacitor ESR and connection resistance total 5 m $\Omega$ ). The phase curve is steeper in Figure 14 than Figure 11, which means that the phase margin is smaller. Inductance values of 6.8  $\mu$ H, 3.9  $\mu$ H and 2.2  $\mu$ H were used to demonstrate how stability improves even though L=6.8  $\mu$ H (M=8) and L=3.9  $\mu$ H (M=11) do not satisfy the M>=15 guideline. The calculated Bode-plot curve in Figure 14 shows that the phase margin is 20° for L=6.8  $\mu$ H, and 30° for L=3.9  $\mu$ H. The 2.2- $\mu$ H (M=15) inductor provides a 45° phase margin shown in Figure 14.

Figure 14. Mathcad Calculated Bode-Plot of Transfer Function for High Output Current and Ceramic Output Capacitor

Figure 15 shows the measured Bode-plot of the transfer function and load-transient test waveform. To ensure that biasing has not reduced the effective output capacitance, two 100  $\mu$ F/6.3 V ceramic capacitors plus one 47  $\mu$ F/6.3 V ceramic capacitor in parallel were used to provide an effective 200  $\mu$ F of output capacitance.

L=6.8  $\mu$ H (M=8) and L=3.9  $\mu$ H (M=11) show ringing during settling time at transient test, indicating that the phase margin is too low. When L=2.2  $\mu$ H (M=15), no ringing was observed, indicating adequate phase margin.

Figure 15. Measured Bode-Plot and Load Transient Waveform With Ceramic Capacitor ( $V_{IN}$  = 3.0 V,  $V_o$  = 3.6 V,  $I_o$  = 2 A, C = 100  $\mu$ F × 2 Ceramic Capacitor)

#### 5 Example 3; Low Output Current ( $I_0 = 0.4 \text{ A}$ ) With Ceramic Capacitor

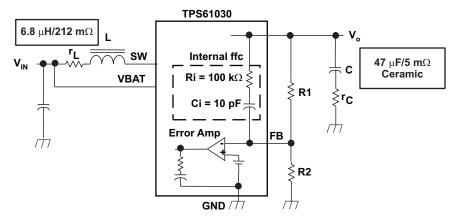

Figure 16. Block Diagram of Converter

$V_{IN} = 3.0 \text{ V} - 3.3 \text{ V}$   $V_0 = 3.6 \text{ V}$  $I_0 = 0.4 \text{ A} (R = 9 \Omega) (1.44 \text{ W})$

$V_{o\_ripple} = 5$  mV (by capacitance) Target efficiency 90% (  $P_{loss}$ =0.16 W,  $I_{lN}$ =0.53 A at 3.0  $V_{lN}$ )

$V_{o transient}$ =250 mV (assume transient  $I_{o}$ =0 A to 0.4 A, and  $f_{BW}$ =10kHz for calculation purpose below)

Following the design process;

$$C_{min\_ripple} = \frac{I_o}{V_{o\_ripple\_cap}} \cdot \left(1 - \frac{V_{IN}}{V_o}\right) \cdot \frac{1}{f} = \frac{0.4}{5mV} \times \left(1 - \frac{3}{3.6}\right) \times \frac{1}{600\,\text{kHz}} = 22\,\mu\text{F} \tag{36}$$

$$C_{min\_tran} = \frac{i_{tran}}{V_{o\_dip}} \cdot \frac{1}{4f_{BW}} = \frac{0.4 \, A}{250 \, mV} \times \frac{1}{4 \times 10 \, kHz} = 40 \, \mu F \tag{37}$$

From the result of Equation 36 and Equation 37, 47 µF ceramic capacitor available was chosen.

$$L_{MAX} = C \cdot \left(\frac{R_{min}}{15} \cdot \frac{V_{IN\_min}}{V_o}\right)^2 = 47 \,\mu\text{F} \times \left(\frac{9}{15} \times \frac{3}{3.6}\right)^2 = 12 \,\mu\text{H}(MAX) \tag{38}$$

$$L_{min} = \frac{1}{C} \cdot \left( \frac{1}{2\pi} \cdot \frac{V_{IN\_MAX}}{V_o} \cdot \frac{10^{\frac{Go}{30}}}{2 \cdot f_Z} \right)^2 = \frac{1}{47 \, \mu F} \times \left( \frac{1}{2\pi} \times \frac{3.3}{3.6} \times \frac{10^{\frac{G_o}{30}}}{2 \times 11 \, k\Omega} \right)^2 = 4 \, \mu H(min)$$

(39)

$$r_{L\_MAX} = \frac{P_{Inductance\_loss}}{I_{in\_MAX}^2} = \frac{0.048W}{0.53 \text{ A}^2} = 170 \text{ m}\Omega$$

$$(40)$$

Where,  $P_{inductance} = 30\% \times P_{LOSS} = 30\% \times 0.16 \text{ W} = 0.048 \text{ W}$

The calculated inductance range is 4  $\mu$ H to 12  $\mu$ H. For this discussion 6.8  $\mu$ H is chosen. The inductance used has a saturation current of 0.8 A ( $r_L$ =212  $m\Omega$ , higher than 170  $m\Omega$  but acceptable practically) to handle the maximum input current of 0.6 A. From Equation 1 through Equation 10, we know the inductor DCR ( $r_L$ ) has a damping effect similar to the capacitor  $r_C$ . In low power applications, the relatively large DCR ( $r_L$ ) helps to offset the instability caused by the low ESR ( $r_C$ ) of the ceramic capacitors.

Figure 17 shows a Bode plot of the Mathcad-calculated transfer function with inductor L=6.8  $\mu$ H, and rL=250 m $\Omega$  (after consolidating the inductance DCR and SW *ON* resistance) and ceramic output capacitor of 47  $\mu$ F/5 m $\Omega$ . The expected phase margin is 50°.

Figure 17. Mathcad Calculated Bode-Plot of Transfer Function for Low Output Current and Ceramic Output Capacitor

Figure 18 shows the measured transient response. The inductor used is 6.8  $\mu$ H, 0.81 A\_sat, 212 m $\Omega$ , Based on the transient waveform, the application is stable.

Figure 18. Measured Load Transient Waveform

Conclusion www.ti.com

#### 6 Conclusion

A transfer function for a voltage-mode boost converter in continuous-conduction mode was developed using state space averaging model. From the transfer function, the challenges of stabilizing a voltage-mode boost converter were explained, and a design procedure for achieving loop stability was provided.

#### Appendix A State Space Averaging Method

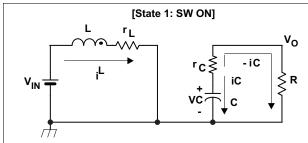

Deriving Transfer function using state space averaging method.

State 1 [SW: ON, RC: OFF]

$$V_{in} = L \frac{di_L}{dt} + i_L r_L.$$

(A1)

$$\begin{cases} V_{in} = L \frac{di_L}{dt} + i_L r_L. & \text{(A1)} \\ i_C = C \frac{dv_C}{dt}. & \text{(A2)} \\ v_C = -i_C (R + r_C). & \text{(A3)} \\ v_C = v_C + r_C & \text{(A4)} \end{cases}$$

$$v_C = -i_C (R + r_C). \tag{A3}$$

$$v_O = v_C + r_C i_C. \tag{A4}$$

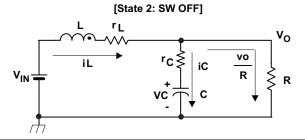

State 2 [SW: OFF, RC: ON]

$$V_{in} = L\frac{di_L}{dt} + r_L i_L + v_O$$

(A5)

$$i_C = C \frac{dv_C}{dt} \,. \tag{A6}$$

$$i_L = i_C + \frac{v_O}{R}. \tag{A7}$$

$$v_O = v_C + r_C i_C. (A8)$$

Appendix A www.ti.com

By State Space Averaging Method, the state averaging equations are described as follows.

$$\begin{cases} \frac{dX}{dt} = AX + bV_{in} \\ v_O = cX. & \text{where } X = \begin{bmatrix} i_L \\ v_C \end{bmatrix}. \end{cases}$$

(A9)

The state equation is derived as below.

$$\begin{cases}

\frac{d}{dt} \begin{bmatrix} i_L \\ v_C \end{bmatrix} = \begin{bmatrix} -\frac{1}{L} (r_L + \frac{D'R \cdot r_C}{R + r_C}) - \frac{D'R}{L(R + r_C)} \\ \frac{D'R}{C(R + r_C)} - \frac{1}{C(R + r_C)} \end{bmatrix} \begin{bmatrix} i_L \\ v_C \end{bmatrix} + \begin{bmatrix} \frac{1}{L} \\ 0 \end{bmatrix} V_{in} \\

V_O = \begin{bmatrix} \frac{D'R \cdot r_C}{R + r_C} & \frac{R}{R + r_C} \end{bmatrix} \begin{bmatrix} i_L \\ v_C \end{bmatrix}

\end{cases}$$

(A10)

AC analysis (small signal transfer function)

Gdv transfer function from Duty to Output voltage is derived as follows.

$$G_{dv}(s) = \frac{\Delta v_{O}(s)}{\Delta D} = c(sI - A)^{-1} \frac{\partial A}{\partial D} X(s) + \frac{\partial c}{\partial D} X(s) = \frac{(R + r_{C})(sCr_{C} + 1)\left\{-(sL + r_{L})(R + r_{C}) + D'^{2}R^{2}\right\}}{P(s)\left\{D'R(D'R + r_{C}) + r_{L}(R + r_{C})\right\}} \cdot RV_{i}$$

Where:

$$P(s) = s^{2}LC(R + r_{C})^{2} + s \left\{ L(R + r_{C}) + r_{L}C(R + r_{C})^{2} + D'Rr_{C}C(R + r_{C}) \right\} + r_{L}(R + r_{C}) + D'R(D'R + r_{C})$$

#### A.1 Reference

1. *Understanding Boost Power Stages in Switchmode Power Supplies* (<u>SLVA061</u>), Everett Rogers, Texas Instruments, March 1999.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

**Applications Products Amplifiers** amplifier.ti.com Audio www.ti.com/audio Data Converters Automotive www.ti.com/automotive dataconverter.ti.com DLP® Products Broadband www.dlp.com www.ti.com/broadband DSP Digital Control dsp.ti.com www.ti.com/digitalcontrol Clocks and Timers www.ti.com/clocks Medical www.ti.com/medical Military Interface www.ti.com/military interface.ti.com Optical Networking Logic logic.ti.com www.ti.com/opticalnetwork Power Mgmt power.ti.com Security www.ti.com/security Telephony Microcontrollers microcontroller.ti.com www.ti.com/telephony Video & Imaging www.ti-rfid.com www.ti.com/video RF/IF and ZigBee® Solutions www.ti.com/lprf Wireless www.ti.com/wireless

> Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2009, Texas Instruments Incorporated