# High-Vin, High-Efficiency Power Solution Using DC/DC Converter with DVFS

Ambreesh Tripathi

PMP - DC/DC Low-Power Converters

#### **ABSTRACT**

This reference design is intended for users designing with the TMS320C6742, TMS320C6746, TMS320C6748, or OMAP-L132/L138 processor. Using sequenced power supplies, this reference design describes a system having a 12-V input voltage and a high-efficiency dc/dc converter with integrated FETs and dynamic voltage and frequency scaling (DVFS) for a small, simple design.

Sequenced power supply architectures are becoming commonplace in high-performance microprocessor and digital signal processor (DSP) systems. To save power and increase processing speeds, processor cores have smaller geometry cells and require lower supply voltages than the system bus voltages. Power management in these systems requires special attention. This application report addresses these topics and suggests solutions for output voltage sequencing.

|   | Contents                                        |   |

|---|-------------------------------------------------|---|

| 1 | Introduction                                    | 2 |

| 2 | Power Requirements                              | 2 |

| 3 | Features                                        | 3 |

| 4 | Bill of Materials                               | 6 |

|   | List of Figures                                 |   |

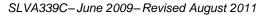

| 1 | PMP4976 Reference Design Schematic              | 2 |

| 2 | Optional Circuit for DVDD_A, DVDD_B, and DVDD_C |   |

| 3 | Sequencing in Start-up Waveform                 |   |

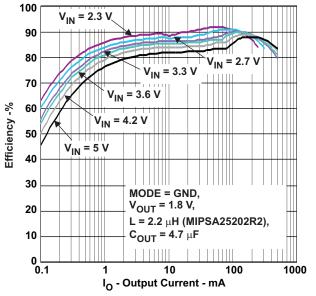

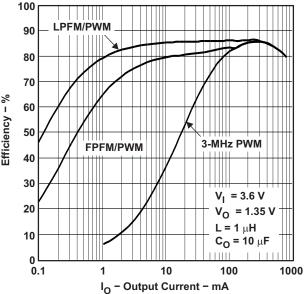

| 4 | Efficiency vs Output Current                    | 7 |

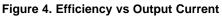

| 5 | Efficiency vs Output Current                    | 7 |

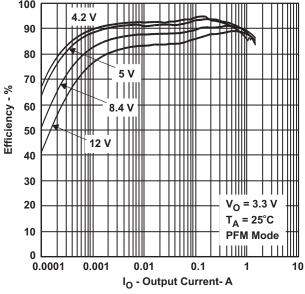

| 6 | Efficiency vs Output Current                    |   |

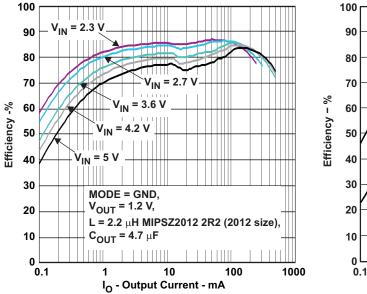

| 7 | Efficiency vs Output Current                    | 7 |

|   | List of Tables                                  |   |

| 1 | General Requirements                            | 2 |

| 2 | PMP4976 Bill of Materials                       |   |

NanoFree is a trademark of Texas Instruments. All other trademarks are the property of their respective owners.

Introduction www.ti.com

#### 1 Introduction

In dual voltage architectures, coordinated management of power supplies is necessary to avoid potential problems and ensure reliable performance. Power supply designers must consider the timing and voltage differences between core and input/output (I/O) voltage supplies during power-up and power-down operations.

Sequencing refers to the order, timing, and differential in which the two voltage rails are powered up and down. A system designed without proper sequencing may be at risk for two types of failures. The first of these represents a threat to the long-term reliability of the dual voltage device, whereas the second is more immediate, with the possibility of damaging interface circuits in the processor or system devices such as memory, logic, or data converter integrated circuits (IC).

Another potential problem with improper supply sequencing is bus contention. Bus contention is a condition in which the processor and another device both attempt to control a bidirectional bus during power up. Bus contention may also affect I/O reliability. Power supply designers must check the requirements regarding bus contention for individual devices.

The power-on sequencing for the OMAP-L132/L138, TMS320C6742, TMS320C6746, and TMS320C6748 are shown in Table 1. None of the supplies for these devices require a specific voltage ramp rate as long as the 3.3-V rail does not exceeds the 1.8-V rail by more than 2 V.

In order to reduce the power consumption of the processor core, dynamic voltage and frequency scaling (DVFS) is used in the reference design. DVFS is a power management technique used while active processing is going on in the system-on-chip (SoC), which matches the operating frequency of the hardware to the performance requirement of the active application scenario. Whenever clock frequencies are lowered, operating voltages are also lowered to achieve power savings. In the reference design, the TPS62353 is used, which can scale its output voltage.

# 2 Power Requirements

The power requirements are as specified in Table 1.

VOLTAGE (1) (2) **SEQUENCING** TIMING **Imax PIN NAME TOLERANCE** (mA) ORDER **DELAY** (V) 1 (3) I/O RTC CVDD 1.2 1 -25%, +10% Core CVDD(4) 1.0 / 1.1 / 1.2 600 -9.75%, +10% 2 I/O RVDD, PLL0\_VDDA, 1.2 200 -5%, +10% 3 PLL1\_VDDA, SATA\_VDD, USB\_CVDD, USB0\_VDDA12 I/O USB0\_VDDA18, USB1\_VDDA18, 1.8 180 ±5% 4 DDR DVDD18, SATA VDDR, DVDD18 I/O USB0\_VDDA33, USB1\_VDDA33 3.3 24 +5% 5 I/O DVDD3318\_A, DVDD3318\_B, 1.8 / 3.3 50 / 90<sup>(5)</sup> 4/5 ±5% DVDD3318 C

**Table 1. General Requirements**

<sup>(1)</sup> If 1.8-V LVCMOS is used, power rails up with the 1.8-V rails. If 3.3-V LVCMOS is used, power it up with the ANALOG33 rails (VDDA33\_USB0/1).

<sup>(2)</sup> No specific voltage ramp rate is required for any of the supplies LVCMOS33 (USB0\_VDDA33, USB1\_VDDA33) as long as STATIC18 (USB0\_VDDA18, USB1\_VDDA18, DDR\_DVDD18, SATA\_VDDR, DVDD18) never exceeds more than 2 V.

<sup>(3)</sup> If RTC is not used/maintained on a separate supply, it can be included in the STATIC12 (fixed 1.2 V) group.

<sup>(4)</sup> If using CVDD at fixed 1.2 V, all 1.2-V rails may be combined.

<sup>(5)</sup> If DVDD3318\_A, B, and C are powered independently, maximum power for each rail is 1/3 above maximum power.

www.ti.com Features

#### 3 Features

The design uses the following high-efficiency dc/dc converters with integrated FETs.

|                              | HIGH EFFICIENCY (With DVFS) |  |  |

|------------------------------|-----------------------------|--|--|

| INPUT VOLTAGE                | ~12 V/3.3 V                 |  |  |

| OUTPUT VOLTAGES              |                             |  |  |

| Core 1.2 V at 600 mA         | TPS62353                    |  |  |

| Fixed 1.2 V + VRTC at 251 mA | TPS62232                    |  |  |

| 1.8 V at 230 mA              | TPS62231                    |  |  |

| 3.3 V at 115 mA              | TPS62111                    |  |  |

In the preceding table, VRTC is included in the STATIC12 (fixed 1.2-V) group.

#### **TPS62353**

- · 88% efficiency at 3-MHz operation

- Output peak current up to 800 mA

- 3-MHz fixed frequency operation

- · Best in class load and line transient

- ±2% PWM dc voltage accuracy

- · Efficiency optimized Power-Save mode

- Transient optimized Power-Save mode

- Fixed 1.2-V output eliminates need for external voltage-setting resistors

- Available in a 10-pin QFN (3 × 3 mm) 12-pin NanoFree™ (CSP) packaging

## TPS62231 and TPS62232

- 3-MHz switch frequency

- Up to 94% efficiency

- · Output peak current up to 500 mA

- Small external output filter components (1 μH/4.7 μF)

- Small 1 × 1,5 × 0,6 mm 3 SON package

- · Fixed 1.8-V and 1.2-V output, respectively, eliminates need for external voltage-setting resistors

#### **TPS62111**

- High-efficiency synchronous step-down converter with up to 95% efficiency

- Up to 1.5-A output current

- High efficiency over a wide load-current range due to PFM/PWM operation mode

- Fixed 3.3-V output eliminates need for external voltage-setting resistors

More information on the devices can be found in the respective product data sheets.

- TPS62111; literature number SLVS585

- TPS62231 and TPS62232; literature number, SLVS941

- TPS62353; literature number SLVS540

Features www.ti.com

Figure 1. PMP4976 Reference Design Schematic

www.ti.com Features

Proper sequencing is ensured in the design with the use of a NPN transistor and a P-channel MOSFET. As required, Core 1.2 V at 600 mA comes first, and is followed by Static 1.2 V + VRTC at 251 mA. Then comes Static 1.8 V at 230 mA, which in turn pulls down the gate of a P-channel MOSFET with the use of a NPN transistor. Last, Static 3.3 V at 115 mA comes up.

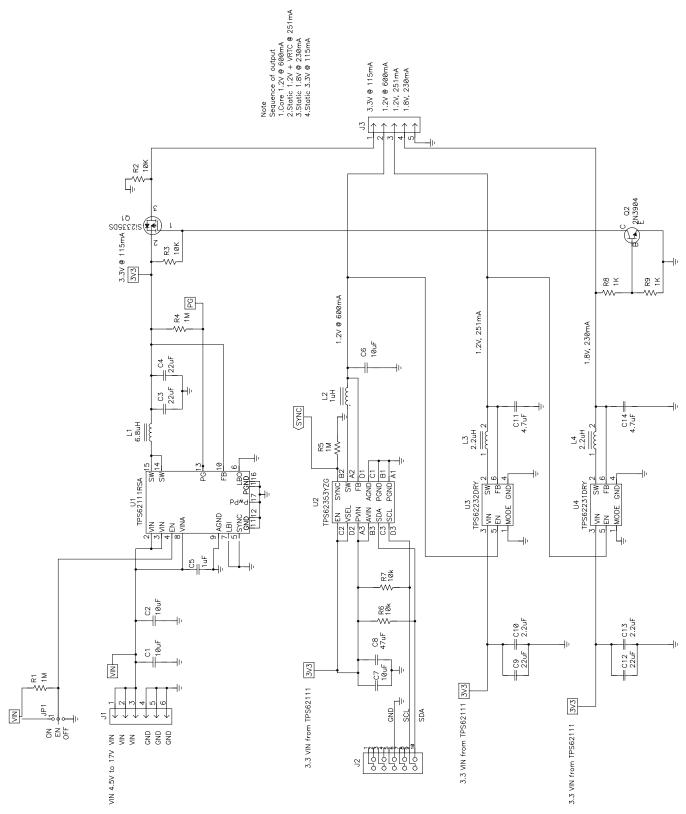

- (1) Use three such LDOs to power up DVDDA, DVDDB, and DVDDC. (It can be either 1.8 V or 3.3 V.)

- (2)  $Rx = 0.499 M\Omega$ ,  $Ry = 1 M\Omega$  for Vout = 1.8 V

- (3)  $Rx = 1.8 M\Omega$ ,  $Ry = 1 M\Omega$  for Vout = 3.3 V

- (4) For proper sequencing of output, the enable of the LDOs are fed either from a 1.2-V output from TPS62232 if DVDDX is 1.8 V or from a 1.8-V output from TPS62231 if DVDDX is 3.3 V.

Figure 2. Optional Circuit for DVDD\_A, DVDD\_B, and DVDD\_C

Bill of Materials www.ti.com

## 4 Bill of Materials

Table 2. PMP4976 Bill of Materials

| Count | RefDes | Value       | Description                                                           | Size               | Part Number     | MFR         | AREA        |

|-------|--------|-------------|-----------------------------------------------------------------------|--------------------|-----------------|-------------|-------------|

| 2     | C1     | 10 μF       | Capacitor, Ceramic, 25V, X5R, 20%                                     | 1206               | C3216X5R1E106   | TDK         | 15390       |

|       | C2     | 10 μF       | Capacitor, Ceramic, 25V, X5R, 20%                                     | 1206               | C3216X5R1E106   | TDK         | 15390       |

| 2     | C3     | 22 µF       | Capacitor, Ceramic, 10V, X5R, 20%                                     | 1206               | C3216X5R1A226   | TDK         | 15390       |

|       | C4     | 22 µF       | Capacitor, Ceramic, 10V, X5R, 20%                                     | 1206               | C3216X5R1A226   | TDK         | 15390       |

| 1     | C5     | 1 μF        | Capacitor, Ceramic, 25V, X7R, 10%                                     | 603                | C1608X7R1E105K  | TDK         | 5650        |

| 2     | C6     | 10 μF       | Capacitor, Ceramic, 6.3V, X5R, 10%                                    | 603                | C1608X5R0J106KT | TDK         | 5650        |

|       | C7     | 10 μF       | Capacitor, Ceramic, 6.3V, X5R, 10%                                    | 603                | C1608X5R0J106KT | TDK         | 5650        |

| 1     | C8     | 47 µF       | Capacitor, Ceramic, 10V, X5R, 20%                                     | 1812               | C4532X5R1A476M  | TDK         | 43,360      |

| 2     | C9     | 22 µF       | Capacitor, Ceramic, 10V, X5R, 20%                                     | 1210               | Std             | Std         | 83,600      |

| 2     | C10    | 2.2 µF      | Capacitor, Ceramic, 6.3V, X5R, 20%                                    | 402                | JDK105BJ225MV   | Taiyo Yuden | 2800        |

| 2     | C11    | 4.7 µF      | Capacitor, Ceramic, 6.3V, X5R, 20%                                    | 402                | JDK105BJ475MV   | Taiyo Yuden | 2800        |

|       | C12    | 22 µF       | Capacitor, Ceramic, 10V, X5R, 20%                                     | 1210               | Std             | Std         | 83,600      |

|       | C13    | 2.2 µF      | Capacitor, Ceramic, 6.3V, X5R, 20%                                    | 402                | JDK105BJ225MV   | Taiyo Yuden | 2800        |

|       | C14    | 4.7 µF      | Capacitor, Ceramic, 6.3V, X5R, 20%                                    | 402                | JDK105BJ475MV   | Taiyo Yuden | 2800        |

| 1     | J1     | PTC36SAAN   | Header, Male 6-pin, 100mil spacing, (36-pin strip)                    | 0.100 inch × 6     | PTC36SAAN       | Sullins     | 70000       |

| 1     | J2     | 2510-6002UB | Connector, Male Straight 2×10 pin, 100mil spacing, 4 Wall             | 0.338 × 0.788      | 2510-6002UB     | 3M          | 301.02<br>4 |

| 1     | J3     | PEC36SAAN   | Header, Male 5-pin, 100mil spacing, (36-pin strip)                    | 0.100 inch × 5     | PEC36SAAN       | Sullins     | 60000       |

| 1     | JP1    | PTC36SAAN   | Header, 3-pin, 100mil spacing, (36-pin strip)                         | 0.100 × 3          | PTC36SAAN       | Sullins     | 34100       |

| 1     | L1     | 6.8 µH      | Inductor, SMT, 3.0A, 97 mΩ                                            | 0.276 × 0.276 inch | HA3808-AL       | Coilcraft   | 90000       |

| 1     | L2     | 1 μH        | Inductor, SMT, 1.6A, ±30%                                             | 0.118 × 0.118      | LPS3010-102NLC  | Coilcraft   | 26,560      |

| 2     | L3     | 2.2 µH      | Inductor, SMT, 0.7A, 230-mΩ                                           | 805                | MIPSZ20120D2R2  | FDK         | 10160       |

|       | L4     | 2.2 µH      | Inductor, SMT, 0.7A, 230-mΩ                                           | 805                | MIPSZ20120D2R2  | FDK         | 10160       |

| 1     | Q1     | Si2335DS    | MOSFET, P-ch, -12 V, 4 A, 51 mΩ                                       | SOT23              | Si2335DS        | Vishay      | 14105       |

| 1     | Q2     | 2N3904      | Transistor, NPN, 40V, 200mA, 625mW                                    | TO-92              | 2N3904          | Fairchild   | 37800       |

| 1     | R1     | 1M          | Resistor, Chip, 1/16-W, 1%                                            | 603                | Std             | Std         | 9100        |

| 2     | R2     | 10K         | Resistor, Chip, 1/16W, x%                                             | 603                | Std             | Std         | 5,650       |

|       | R3     | 10K         | Resistor, Chip, 1/16W, x%                                             | 603                | Std             | Std         | 5,650       |

| 1     | R4     | 1M          | Resistor, Chip, 1/16W, x%                                             | 603                | Std             | Std         | 5,650       |

| 1     | R5     | 1M          | Resistor, Chip, 1/16W, 1%                                             | 603                | Std             | Std         | 5650        |

| 2     | R6     | 10k         | Resistor, Chip, 1/16W, 1%                                             | 603                | Std             | Std         | 5650        |

|       | R7     | 10k         | Resistor, Chip, 1/16W, 1%                                             | 603                | Std             | Std         | 5650        |

| 2     | R8     | 1K          | Resistor, Chip, 1/16W, x%                                             | 603                | Std             | Std         | 5,650       |

|       | R9     | 1K          | Resistor, Chip, 1/16W, x%                                             | 603                | Std             | Std         | 5,650       |

| 1     | U1     | TPS62111RSA | IC, Synchronous Step-Down Converter, 17V, 1.2A                        | QFN-16             | TPS62111RSA     | TI          | 54289       |

| 1     | U2     | TPS62353YZG | IC, 3MHz Synchronous Step Down Converter with I <sup>2</sup> C, 800mA | CSP-12             | TPS62353YZG     | ТІ          | 12,000      |

| 1     | U3     | TPS62232DRY | IC, 3MHz Ultra Small Step Down Converter, x.x V                       | QFN                | TPS62232DRY     | TI          | 6020        |

| 1     | U4     | TPS62231DRY | IC, 3MHz Ultra Small Step Down Converter, x.x V                       | QFN                | TPS62232DRY     | TI          | 6020        |

Notes: 1. These assemblies are ESD sensitive, ESD precautions shall be observed.

<sup>2.</sup> These assemblies must be clean and free from flux and all contaminants. Failure to use clean flux is unacceptable.

<sup>3.</sup> These assemblies must comply with workmanship standards IPC-A-610 Class 2.

<sup>4.</sup> Reference designators marked with an asterisk ("\*\*") cannot be substituted. All other components can be substituted with equivalent MFG's components.

www.ti.com Bill of Materials

## 4.1 Test Results

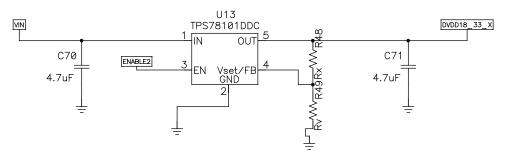

The start-up waveform Figure 3 specifies the sequencing order that is required.

Figure 3. Sequencing in Start-up Waveform

Figure 5. Efficiency vs Output Current

Revision History www.ti.com

Figure 6. Efficiency vs Output Current

Figure 7. Efficiency vs Output Current

# **Revision History**

# Changes from B Revision (January, 2011) to C Revision

Page

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

#### IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

## Products Applications

Audio www.ti.com/audio Communications and Telecom www.ti.com/communications **Amplifiers** amplifier.ti.com Computers and Peripherals www.ti.com/computers dataconverter.ti.com Consumer Electronics www.ti.com/consumer-apps **Data Converters DLP® Products** www.dlp.com **Energy and Lighting** www.ti.com/energy DSP dsp.ti.com Industrial www.ti.com/industrial Clocks and Timers www.ti.com/clocks Medical www.ti.com/medical

Interface

interface.ti.com

Security

www.ti.com/security

Logic

logic.ti.com

Space, Avionics and Defense

www.ti.com/space-avionics-defense

Power Mgmt power.ti.com Transportation and Automotive www.ti.com/automotive

Microcontrollers microcontroller.ti.com Video and Imaging www.ti.com/video

RFID <u>www.ti-rfid.com</u>

OMAP Mobile Processors www.ti.com/omap

Wireless Connctivity www.ti.com/wirelessconnectivity

TI E2E Community Home Page e2e.ti.com

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2011, Texas Instruments Incorporated