# Powering the NXP i.MX 6Solo, 6DualLite with the TPS6521815 PMIC

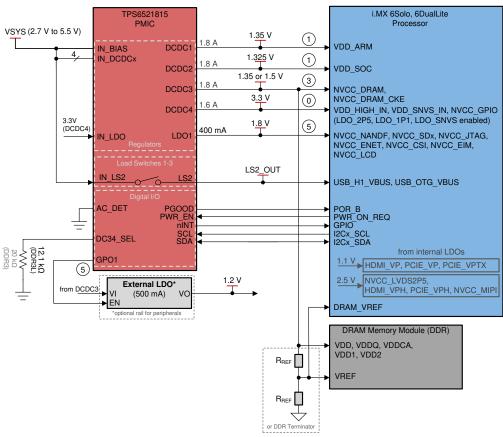

# System Power Block Diagram

# Can you change PMICs?

Using a multi-rail power management IC (PMIC) for an applications processor is common, but typically the vendor recommends the PMIC that should be used for each processor. Even if the suggested PMIC is not ideal for the needs of the processor, often the complexity makes it difficult to swap out the PMIC for another solution. The purpose of this tech note is to show that the TPS6521815 PMIC can provide power for the i.MX 6Solo and 6DualLite processors.

#### Why the TPS6521815?

The TPS6521815 device has an input range from 2.7 to 5.5 V, making it appropriate for system-on-module applications powered from a 3.3-V or 5-V DC supply or a Li-Ion battery. The device has four step-down converters that provide the 1.35-V and 1.325-V power rails required for the ARM® and SoC cores, the 1.35-V (or 1.5-V) rail required for DDR3L (or DDR3) memory, and a 3.3-V rail required for I/Os. A low-dropout (LDO)

regulator provides 1.8-V for an SD Card, NAND Flash, and JTAG I/Os. The TPS6521815 automatically sequences these rails in the correct power-up sequence for the i.MX 6Solo and 6DualLite processors.

## How do you make the switch?

The TPS6521815 output voltages and sequencing order are determined by an EEPROM-backed register map, which can be programmed using the BOOSTXL-TPS65218 socketed booster pack. Samples of the TPS6521815RSLR can be programmed during the prototype phase of product development and soldered down on the TPS65218EVM-100 or the prototype PCB of the final product to evaluate the performance of the PMIC. To order pre-programmed samples of the TPS6521815RSLR for the NXP i.MX 6Solo, 6DualLite processor that match this tech note, contact the programming services organization at ARROW.

### Table 1. i.MX 6Solo and 6DualLite Power Requirements

| TPS6521815           |                             |                           |                       | i.MX 6Solo/6DualLite                                                           |                                                  |                                                       |

|----------------------|-----------------------------|---------------------------|-----------------------|--------------------------------------------------------------------------------|--------------------------------------------------|-------------------------------------------------------|

| POWER-UP<br>SEQUENCE | POWER<br>SUPPLY<br>(OUTPUT) | OUTPUT<br>CURRENT<br>[mA] | OUTPUT<br>VOLTAGE [V] | POWER SUPPLY (INPUT)                                                           | VOLTAGE RATING [V]                               | MAX CURRENT [mA]                                      |

| 1                    | DCDC1                       | 1800                      | 1.35 <sup>(1)</sup>   | VDD_ARM                                                                        | Minimum: 1.275<br>Maximum: 1.5                   | 1320 (i.MX 6Solo)<br>844-2200 (i.MX<br>6DualLite) (2) |

| 1                    | DCDC2                       | 1800                      | 1.325 <sup>(1)</sup>  | VDD_SOC                                                                        | Minimum: 1.275<br>Maximum: 1.5                   | 878-1260 <sup>(2)</sup>                               |

| 3                    | DCDC3                       | 1800                      | 1.35 (or 1.5)         | NVCC_DRAM, NVCC_DRAM_CKE                                                       | Minimum: 1.283<br>Typical: 1.35<br>Maximum: 1.45 | 1000                                                  |

| 0                    | DCDC4                       | 1600                      | 3.3                   | VDD_HIGH_IN, VDD_SNVS_IN,<br>NVCC_GPIO <sup>(3)</sup>                          | Minimum: 2.9<br>Maximum: 3.3                     | 125 + Maximum IO current                              |

| 5                    | LDO1                        | 200                       | 1.8                   | NVCC_NANDF, NVCC_SDx, NVCC_JTAG,<br>NVCC_ENET, NVCC_CSI, NVCC_EIM,<br>NVCC_LCD | Minimum: 1.65<br>Maximum: 3.6                    | N/A                                                   |

| 5                    | Ext. LDO (4)                | 500                       | 1.2                   | 1.2-V peripheral(s)                                                            | N/A                                              | N/A                                                   |

| N/A                  | LS2                         | 100                       | 5                     | USB_H1_VBUS, USB_OTG_VBUS                                                      | Minimum: 4.4<br>Maximum: 5.25                    | 25                                                    |

This set-point is based on the use case where VDD\_ARM LDO and VDD\_SOC are enabled. LDO VDD\_ARM and VDD\_SOC voltages can be modified by the processor after power-on using I2C, a feature named dynamic voltage scaling (DVS or DVFS) such that VDD\_ARM\_IN and VDD\_SOC\_IN are 125 mV greater than the LDO output set-point.

#### **Table 2. Adjacent Tech Notes**

| Processor            | Title                                                                 |  |

|----------------------|-----------------------------------------------------------------------|--|

| i.MX 7Solo and 7Dual | Powering the NXP i.MX 7 Processor with the TPS6521815 PMIC            |  |

| i.MX 8M Mini         | Powering the NXP i.MX 8M Mini with the TPS6521815 and LP8733-Q1 PMICs |  |

#### References

Texas Instruments, *TPS6521815 Power Management for ARM® Cortex™-A8/A9 SOCs and FPGAs* Data Sheet

Texas Instruments, *Power Supply Design for NXP i.MX 6 Using the TPS65023* Application Report, SLVA943, Feb. 2018

NXP Semiconductors, i.MX 6Solo/6DualLite Family of Applications Processors for Industrial Products Data Sheet (IMX6SDLIEC), Rev. 8, 09/2017

NXP Semiconductors, *i.MX 6DualLite Power Consumption Measurement* Application Note (AN4576), Rev. 1, 3/2013

# 0.1 Trademarks

ARM is a registered trademark of Arm Limited.

All other trademarks are the property of their respective owners.

<sup>(2)</sup> The maximum current for the VDD\_ARM and VDD\_SOC core rails is determined from the Use case 1—dual-core Dhrystone benchmark and Typical max power sections in the AN4576 Application Note and the Maximum Supply Currents section in the IMX6SDLIEC data sheet.

<sup>(3)</sup> LDO\_2P5, LDO\_1P1, and LDO\_SNVS internal LDO regulators are enabled to generate voltages for all NVCC power inputs as well as the HDMI\_VPH and PCIE\_VPH supply voltages.

<sup>(4)</sup> The external LDO is optional. When needed, it is controlled by an automatically sequenced GPIO of the TPS6521815.

www.ti.com Revision History

# **Revision History**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| Changes from Original (March 2019) to A Revision                                   |                                                |  |  |  |  |

|------------------------------------------------------------------------------------|------------------------------------------------|--|--|--|--|

| Updated part number from TPS65248D0 to TPS6521815                                  | 1                                              |  |  |  |  |

| Updated Block Diagram based on complete design                                     | 1                                              |  |  |  |  |

| Updated i.MX 6Solo and 6DualLite Power Requirements Table based on complete design | 2                                              |  |  |  |  |

| L                                                                                  | Jpdated Block Diagram based on complete design |  |  |  |  |

# IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022, Texas Instruments Incorporated