# AN-1259 SCANSTA112 Designer's Reference

### ABSTRACT

This application note primarily applies to the SCANSTA112. The feature set of the SCANSTA112 is a superset of that of the SCANSTA111. Much of the content of this application note applies to both devices. With its richer feature set, the SCANSTA112 provides significant additional capability to the system designer. Using this capability is the subject of this application note.

#### Contents

| 1       | Introd | uction                                                 | . 3 |

|---------|--------|--------------------------------------------------------|-----|

| 2       | Bound  | lary Scan Chain Configurations                         | . 3 |

|         | 2.1    | Single Boundary Scan Chain Configuration               | . 4 |

|         | 2.2    | Partitioned Boundary Scan Chain Configuration          | . 6 |

| 3       | SCAN   | STA112 Selection and Addressing                        | . 8 |

|         | 3.1    | SCANSTA112 Primary Operating Modes                     | . 9 |

|         | 3.2    | Choosing the SCANSTA112 Operating Mode                 | 10  |

|         | 3.3    | Setting the Primary Operating Mode                     | 10  |

|         | 3.4    | Addressing Protocols in Scanbridge Mode                | 11  |

|         | 3.5    | Stitcher Mode                                          | 13  |

| 4       | SCAN   | ISTA112 Scan Chain Modes                               | 14  |

|         | 4.1    | Normal Scan Chain Mode                                 | 14  |

|         | 4.2    | Full Transparent Scan Chain Mode                       | 16  |

|         | 4.3    | Transparent LSP Scan Chain Mode                        | 17  |

| 5       | Prima  | ry Operating Modes and Scan Chain Modes                | 18  |

|         | 5.1    | Scanbridge Normal Scan Chain Mode                      | 18  |

|         | 5.2    | Scanbridge Full Transparent Scan Chain Mode            | 18  |

|         | 5.3    | Stitcher Normal Scan Chain Mode                        | 19  |

|         | 5.4    | Stitcher Full Transparent Scan Chain Mode              | 19  |

|         | 5.5    | Primary Operating Mode/Scan Chain Mode Summary         | 20  |

| 6       | Opera  | tional Mode and Reset Summary                          | 21  |

| 7       | SCAN   | STA112 State Machines                                  | 23  |

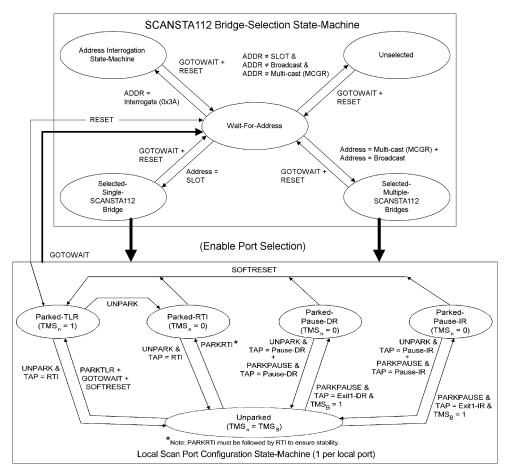

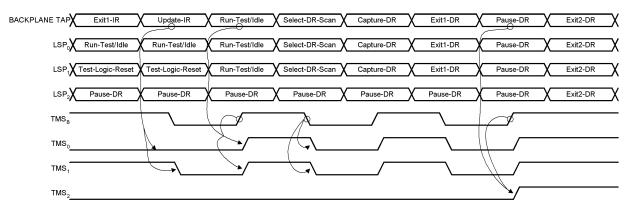

|         | 7.1    | SCANSTA112 Selection State Machine                     | 23  |

|         | 7.2    | Multiple Addressing                                    | 25  |

|         | 7.3    | Addressing Modes                                       | 26  |

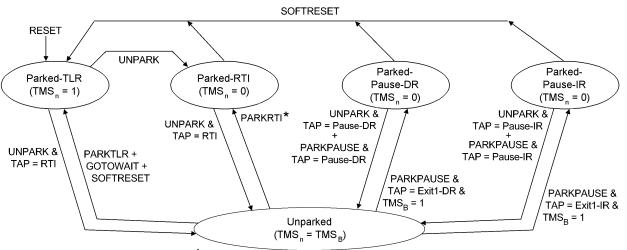

|         | 7.4    | SCANSTA112 Local Scan Port Configuration State Machine | 27  |

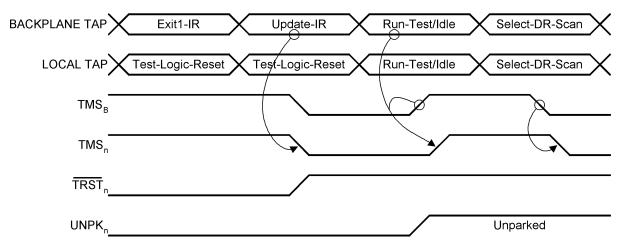

|         | 7.5    | State Machine Interaction                              | 30  |

| 8       | Regis  | ter Set                                                | 31  |

|         | 8.1    | Register Descriptions                                  | 31  |

| 9       | SCAN   | ISTA112 Instruction Set                                | 37  |

|         | 9.1    | SCANSTA112 Instruction Types                           | 38  |

|         | 9.2    | Instruction Descriptions                               | 39  |

| 10      | Additi | onal Features                                          | 43  |

|         | 10.1   | Master Port Selection                                  | 43  |

|         | 10.2   | LSP Output Enable                                      | 44  |

|         | 10.3   | BIST Support                                           | 44  |

|         | 10.4   | SOFTRESET                                              | 45  |

| Instrum |        |                                                        |     |

Texas Instruments, TI are trademarks of Texas Instruments. All other trademarks are the property of their respective owners.

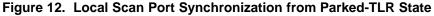

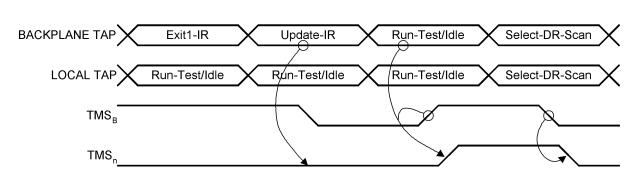

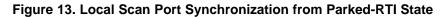

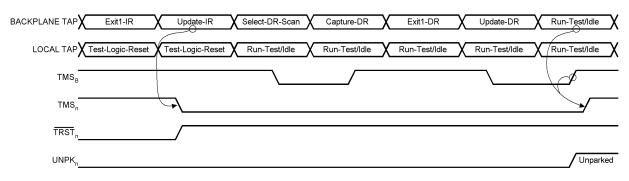

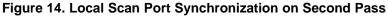

| 10.5  | Port Synchronization                        | 45 |

|-------|---------------------------------------------|----|

| 10.6  | Power-Off High Impedance Inputs and Outputs | 47 |

| 10.7  | TRST                                        | 47 |

| 10.8  | TRI-STATE Indicator Outputs                 | 47 |

| 10.9  | Pass-Through Pins                           | 47 |

| 10.10 | LSP TCK Gating                              | 49 |

| 10.11 | GPIO Connections                            | 49 |

| 10.12 | Address Mask                                | 50 |

| 10.13 | Address Interrogation                       | 50 |

| Terms | and Abbreviations                           | 52 |

|       |                                             |    |

# List of Figures

| 1  | Example of a Simple Boundary Scan Chain                            | 4  |

|----|--------------------------------------------------------------------|----|

| 2  | TAP Controller State Machine                                       | 5  |

| 3  | Example of a Partitioned Boundary Scan Chain                       | 8  |

| 4  | Timing Diagram – $TDO_B/TCK_B$ Re-synchronization                  | 16 |

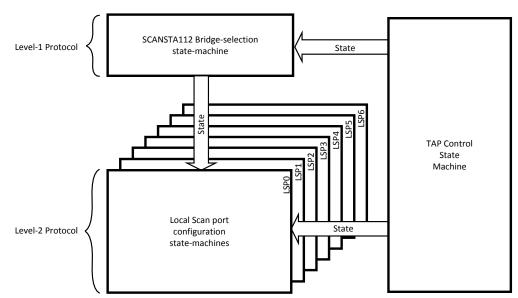

| 5  | SCANSTA112 State Machines                                          | 24 |

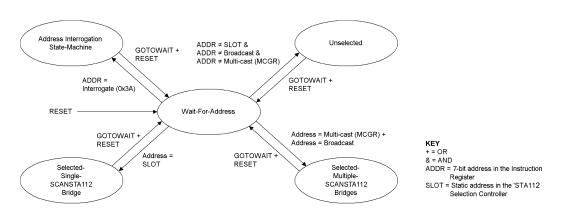

| 6  | State Machine for SCANSTA112 Selection Controller                  | 25 |

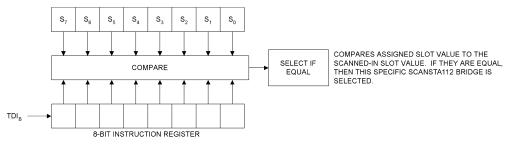

| 7  | Direct Addressing: Device Address Loaded into Instruction Register | 26 |

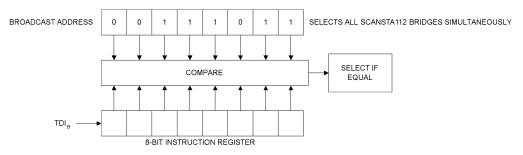

| 8  | Broadcast Addressing: Address Loaded into Instruction Register     | 26 |

| 9  | Multi-Cast Addressing: Address Loaded into Instruction Register    | 27 |

| 10 | Local SCANSTA112 Port Configuration State Machine                  | 28 |

| 11 | Relationship Between SCANSTA112 State Machines                     | 30 |

| 12 | Local Scan Port Synchronization from Parked-TLR State              | 45 |

| 13 | Local Scan Port Synchronization from Parked-RTI State              | 46 |

| 14 | Local Scan Port Synchronization on Second Pass                     | 46 |

| 15 | Synchronization of the Three Local Scan Ports                      | 46 |

| 16 | Address Interrogation State Machine                                | 52 |

#### List of Tables

| 1  | Primary Operating Mode Summary                                                                    | 20 |

|----|---------------------------------------------------------------------------------------------------|----|

| 2  | Reset effect when IgnoreReset is deasserted (set to 0)                                            | 21 |

| 3  | Reset effect when IgnoreReset is asserted (set to 1)                                              | 22 |

| 4  | Initial Register Values                                                                           | 22 |

| 5  | SCANSTA112 Address Modes                                                                          | 26 |

| 6  | Register Summary                                                                                  | 31 |

| 7  | Multi-Cast Group Register Addressing                                                              | 32 |

| 8  | Mode Register Control of LSP <sub>n</sub>                                                         |    |

| 9  | Test Clock Configuration                                                                          |    |

| 10 | Mode Register Bits                                                                                |    |

| 11 | Shared GPIO Register Bits                                                                         |    |

| 12 | Control Register                                                                                  |    |

| 13 | SCANSTA112 Instructions, Opcodes, and Target Registers                                            |    |

| 14 | Mapping of Pass-Through Pins with MPsel <sub>B1/76</sub> at Logic 0 and LSP <sub>0</sub> Selected | 48 |

| 15 | Mapping of Pass-Through Pins with MPsel <sub>B1/B0</sub> at Logic 0 and LSP <sub>1</sub> Selected | 48 |

| 16 | Gated LSP Drive States                                                                            | 49 |

| 17 | Glossary                                                                                          | 52 |

|    |                                                                                                   |    |

2

### 1 Introduction

In 1990 the IEEE approved a draft standard specifying a test access port for integrated circuits. The initial work for this standard had been performed by a working group made up of primarily European and North American companies interested in addressing printed circuit (PC) board test problems. This working group was called the Joint Test Action Group, or JTAG.

The draft standard was motivated by the fact that the problem of testing PC boards had become, over time, increasingly intractable. Component densities on PC boards had increased. Making connections to integrated circuits on such boards for test purposes had become more difficult. The draft standard was designed to define a standard technique for improving the testability of PC boards.

The draft standard that grew out of the work of JTAG was *IEEE Standard 1149.1-1990*, "IEEE Standard Test Access Port and Boundary Scan Architecture", sometimes called IEEE 1149.1, boundary scan, or JTAG. The current version of this standard as of this writing is *IEEE Standard 1149.1-2001*.

The standard specifies the structure and function of a secondary I/O port used to access the pins of an integrated circuit for testing purposes. This secondary I/O port is called the Test Access Port or TAP. It is often referred to as the IEEE 1149.1 TAP, the JTAG TAP, or the boundary scan TAP.

Access to the pins of the integrated circuits on a PC board affords the system designer a powerful capability to test the integrity of connections on the board or between boards. It also enables in-system programming of programmable devices on the board. The JTAG TAP provides an interface to programmable devices through which they can be reprogrammed.

In its most basic form the IEEE 1149.1 standard envisions a single, one-bit serial link connecting all the boundary scan-enabled devices on a PC board. The data output of one device is connected to the data input of the next. The clock and control lines are common to all devices. All boundary scan-enabled devices are designed to support this basic architecture. This is the simplest way to connect a one-bit interface from device to device and for small, simple PC boards it is an appropriate architecture.

For PC boards with many devices this simple architecture can become unwieldy. It is often desirable to address a limited set of the devices on a PC board through the JTAG TAP. Sometimes it is necessary to address only a single device. This is frequently the case for in-system programming of programmable logic devices. Addressing only a subset of the boundary scan-enabled devices on a PC board is not possible with the most basic IEEE 1149.1 boundary scan architecture. A support device for the IEEE 1149.1 test access port that enables such addressing is required.

Texas Instruments<sup>™</sup> manufactures two devices to address this requirement: the SCANSTA111 and the SCANSTA112. Both devices enable partitioning and multiplexing of IEEE 1149.1 boundary scan chains. The SCANSTA112 7-Port Multidrop IEEE 1149.1 (JTAG) Multiplexer provides seven local scan ports. The SCANSTA111 Multidrop Addressable IEEE 1149.1 Port provides three local scan ports. Operation of the two devices is similar.

Both of these devices partition a single scan chain into multiple local scan chains. The devices are addressable so that more than one JTAG multiplexer can be used with a single master scan chain. Multiple PC boards, each with an IEEE 1149.1 TAP and with one or more SCANSTA111s or SCANSTA112s on board, can utilize a single backplane test bus for system-level IEEE 1149.1 TAP access. This simplifies the design of a system to implement boundary scan.

Before we describe the application of the SCANSTA112 in a boundary scan system, we will describe the basic operation of a single boundary scan chain. This will provide background for the application of the SCANSTA112.

# 2 Boundary Scan Chain Configurations

A boundary scan-enabled system may be designed with a single boundary scan chain or with multiple boundary scan chains. A design with multiple boundary scan chains requires a JTAG multiplexer such as the SCANSTA112. The architectures of both the single and multiple boundary scan chain systems are described in this section.

#### Boundary Scan Chain Configurations

### 2.1 Single Boundary Scan Chain Configuration

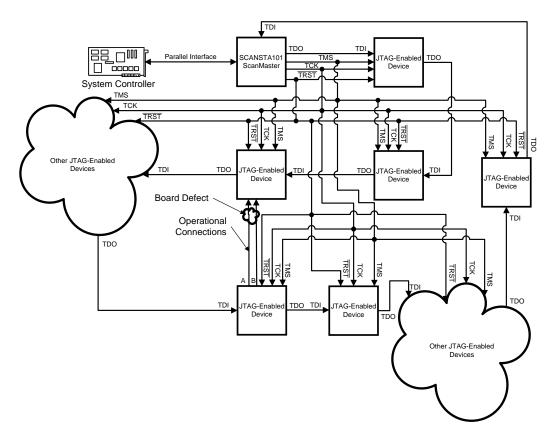

When the IEEE 1149.1 boundary scan chain is not partitioned by a scan chain multiplexer, the connections for the test access port (TAP) are made as shown in Figure 1. As the figure indicates, there are five signals associated with the TAP. These are Test Clock TCK, Test Mode Select TMS, Test Data In TDI, Test Data Out TDO, and Test Reset TRST. The TRST signal is optional according to the IEEE 1149.1 standard.

Figure 1. Example of a Simple Boundary Scan Chain

A boundary scan controller provides the TCK signal. It also drives the TMS signal, the TDO signal, and the TRST signal. The boundary scan chain output returns to the boundary scan controller through the TDI signal. The term boundary scan controller is used in this document to refer to the master boundary scan device that controls all boundary scan operations over the IEEE 1149.1 TAP. In Figure 1 the boundary scan controller is a TI<sup>™</sup> SCANSTA101 ScanMaster.

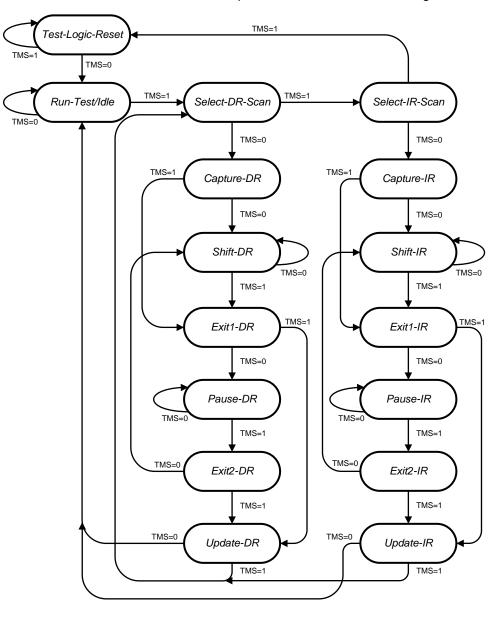

Each boundary scan-enabled device includes a state machine called the TAP controller. The sequence of states through which this state machine can be transitioned is shown in Figure 2. The configuration and operation of the TAP is determined by the state of the TAP controller. By sequencing the TAP controller through a set of desired states the boundary scan controller causes the system to perform the desired operations using the IEEE 1149.1 TAP.

In Figure 2 the names of the states are abbreviated. *Data-Register* is abbreviated *DR* and *Instruction Register* is abbreviated *IR*. Thus the state name referred to as *Shift-Data-Register* in the text is shown as *Shift-DR* in Figure 2.

Referring again to Figure 1, note that the TCK, TMS, and TRST signals are routed to all the boundary scan-enabled devices in parallel. When the asynchronous reset TRST signal is asserted the TAP controllers of all the boundary scan-enabled devices go to the *Test-Logic-Reset* state at the same time. Each of the boundary scan-enabled devices receives TCK transitions at the same time. Each device is required to write data to its TDO output on the falling edge of TCK when it is in the *Shift-Instruction-Register* or *Shift-Data-Register* state. Each device detects the state of the TMS input and the TDI input on the rising edge of TCK. Since all the devices are clocked by the same signal they all remain in synchronous operation when they are in boundary scan test mode.

Since all the boundary scan-enabled devices receive the same TMS signals, all their TAP controllers transition from one state to the next as shown in Figure 2 in lockstep. The entire boundary scan chain has a single TAP controller state. The TAP controller is reset for the entire boundary scan chain by asserting TRST or by holding the TMS signal high for five successive TCK pulses (this is called a five-high TMS reset). Following the reset, the TAP controller is in the *Test-Logic-Reset* state. The boundary scan chain by assertion controller drives the value on the TMS line to sequence the TAP controller through its various states.

Figure 2. TAP Controller State Machine

#### Boundary Scan Chain Configurations

www.ti.com

As noted, the TAP controllers of all the devices in the scan chain go through the same sequence of states. For example, starting from the *Test-Logic-Reset* state, when the boundary scan controller drives on the TMS line a bit sequence of 01100 on five successive TCK pulses the TAP controller is sequenced to the *Shift-Instruction-Register* state.

As indicated in Figure 1 the TDI line of the first device in the scan chain is connected to the TDO line from the boundary scan controller. The TDO line of this first device is connected to the TDI line of the next device. This continues until the last device in the scan chain has its TDO line connected to the TDI line of the boundary scan controller. The boundary scan controller presents bits to the TDI pin of the first device. They are shifted through a register inserted in the scan chain by the first device until the register is full, at which point the bits are shifted out of the TDO pin of this device to the TDI pin of the next one.

As an example, consider the case where the TAP controller is in the *Shift-Instruction-Register* state. Then each boundary scan-enabled device inserts its instruction register into the scan chain. The bits received at the TDI input of the first device are shifted through the instruction registers of each device in the chain at each TCK pulse as long as the TMS line is driven with a 0. When the boundary scan controller eventually drives the TMS line with a 1, the TAP controller enters the *Exit1-Instruction-Register* state. If the boundary scan controller continues to drive a 1 on the TMS line, the TAP controller enters the *Update-Instruction-Register* state. In this state the instructions loaded into the instruction register become active. The boundary scan-enabled devices respond to these instructions in device-specific ways to perform the desired boundary scan operations.

This is the architecture of a basic system with a single boundary scan chain. This architecture is fine for systems with only a few boundary scan-enabled devices with simple connections between them. It is less than optimal for systems with many boundary scan-enabled devices. It is especially cumbersome when some devices must be accessed extensively and repeatedly through the TAP. A programmable logic device, for example, will often require execution of many boundary scan operations in order to program it. Programming a programmable logic device that is part of a long boundary scan chain requires shifting many additional bits into the scan chain beyond just those required to program the device. In some cases, the software tools used to generate the programming sequences for these devices cannot automatically generate sequences including these additional required bits. When the software tools fail to automate the process of producing the required sequences, manual changes to the programming files are required. This is time-consuming and error-prone.

A better approach to the boundary scan architecture in a complex system is a partitioned scan chain. The SCANSTA112 makes it possible to partition a single long scan chain into multiple shorter local scan chains. We will describe the architecture of such a partitioned boundary scan system next.

### 2.2 Partitioned Boundary Scan Chain Configuration

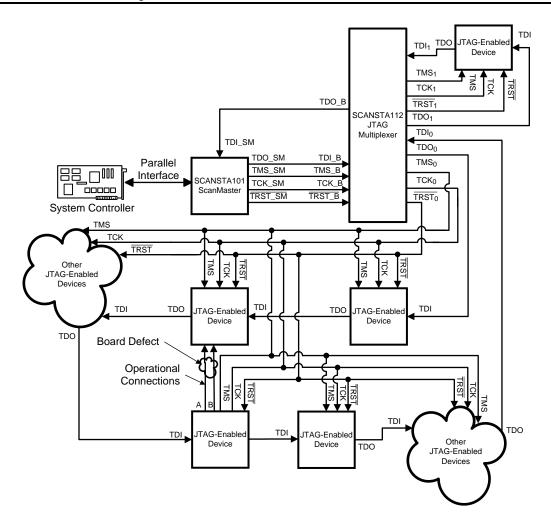

As noted, in systems with many boundary scan-enabled devices, and especially in systems with programmable devices, partitioning the scan chain can simplify the development of boundary scan test sequences and improve the throughput of boundary scan operations. The SCANSTA112 JTAG multiplexer can be used to partition the scan chain. The SCANSTA112 provides seven local scan ports (LSPs) to which local scan chains may be attached.

An example system using the SCANSTA112 JTAG Multiplexer for scan chain partitioning is shown in Figure 3. As the figure indicates, the backplane TAP lines of the SCANSTA112 (TCK<sub>B</sub>, TMS<sub>B</sub>, TDO<sub>B</sub>, TDI<sub>B</sub>, and TRST<sub>B</sub>) are connected to the master boundary scan TAP in the system. The boundary scan controller controls this TAP. The boundary scan controller can send instructions through the master TAP to the SCANSTA112. These instructions can be used to address and configure the SCANSTA112; to select which local scan ports (LSPs) are to be active; and to perform boundary scan operations using both the SCANSTA112 and the scan chains attached to its LSPs.

The SCANSTA112 can also operate in a pin-controlled mode as opposed to being controlled over the IEEE 1149.1 TAP as described above. Control of the SCANSTA112 in pin-controlled mode is accomplished by the SB/S pin, the LSPsel<sub>(0-6)</sub> pins, and the TRANS pin. Both the IEEE 1149.1 TAP-controlled and pin-controlled modes of operation are described in this application note.

In general, the primary mode of operation where the SCANSTA112 is controlled by the backplane TAP is called ScanBridge mode. The mode where the SCANSTA112 is controlled by the device pins is called stitcher mode. This represents an oversimplification of the description of the primary operating modes since there is considerable overlap between them. A more complete description is presented in Section 3.1.

There are multiple scan chains in the system shown in Figure 3. Each is attached to a local scan port (LSP) of the SCANSTA112. The system supports various boundary scan operations. For example, a programmable logic device can be programmed using its LSP while the TAP controllers of all the other scan chains are held in *Test-Logic-Reset* state. Boundary scan operations on a scan chain on one LSP may be conducted while the TAP controllers of all the scan chains on other LSPs remain in *Test-Logic-Reset* state. The TAP controllers on one or more LSPs can also be held in other stable states such as *Run-Test-Idle* while boundary scan operations are performed on other scan chains. Multiple local scan chains can be chained together through the multiplexer. A highly-configurable boundary scan chain can be implemented using the SCANSTA112.

As Figure 3 indicates, each LSP is equipped with all five boundary scan TAP signals. For each LSP, the TCK, TMS, and TRST lines are connected to all the devices in the corresponding local scan chain as if the local scan chain were the only scan chain present in the system. The TDO line of the LSP is connected to the TDI line of the first device in the local scan chain. In each local scan chain the TDO signal from one device is connected to the TDI signal of the next just as in the basic boundary scan chain in Figure 1. The TDO line of the device at the end of the local scan chain is attached to the TDI line of the LSP.

The SCANSTA112 is normally configured so that it appears to the boundary scan controller to be part of the selected local scan chain. It can also be configured as a transparent multiplexer in what is referred to as transparent scan chain mode. In transparent scan chain mode, the boundary scan controller is not aware that the SCANSTA112 is in the system. All the configuration modes available for the SCANSTA112 will be discussed in this application note.

It is possible to configure a system with multiple SCANSTA112 JTAG Multiplexers, each providing multiple LSPs. Such a system can be either flat or hierarchical.

Each SCANSTA112 in a flat system is assigned a unique address using the address pins on the device  $S_{(0-7)}$ . To initiate boundary scan operations in a system with multiple SCANSTA112s the boundary scan controller first addresses one or more SCANSTA112s using their assigned addresses. Once the desired SCANSTA112 or group of SCANSTA112s has been addressed the boundary scan controller configures their LSPs. The boundary scan controller then initiates boundary scan operations on the selected LSPs.

A hierarchical system can provide further partitioning of the boundary scan chain. The backplane TAP of one SCANSTA112 is driven from one of the LSPs of another SCANSTA112. Such a hierarchical system provides expanded flexibility. A hierarchical system also provides an expanded address space for the SCANSTA112s. It is only required that SCANSTA112s at lower levels in the hierarchy have addresses unique within the group of SCANSTA112s attached to the same LSP.

The SCANSTA112 is designed to support multiple levels of hierarchical connections. Implementation of such a hierarchical system is a natural extension of the implementation of a flat system with multiple SCANSTA112s.

The first step in performing boundary scan operations on a system using the SCANSTA112 to partition the scan chain is to select the SCANSTA112 or group of SCANSTA112s to use for the boundary scan operations. The sequence of operations for selecting a SCANSTA112 or a group of SCANSTA112s depends upon the design of the system. In particular, it depends upon the primary operating mode of the SCANSTA112. We next describe the various scenarios for the selection of SCANSTA112s in a system.

SCANSTA112 Selection and Addressing

Figure 3. Example of a Partitioned Boundary Scan Chain

# 3 SCANSTA112 Selection and Addressing

There are several possible scenarios for the selection of SCANSTA112s in a system. To determine which scenarios are to be used in a given system we consider the number of SCANSTA112s in the system, how they are arranged, and how they are to be used.

If there is more than one SCANSTA112 in a system, a user might wish to select a single SCANSTA112 and communicate only with devices accessible through that SCANSTA112. The user may wish to program a single programmable device on a given LSP of a given SCANSTA112; the user may wish to perform boundary scan operations on a single local scan chain on one of the SCANSTA112s; or the user may wish to perform boundary scan operations on multiple local scan chains all connected to one of the SCANSTA112s. In any of these cases, the user must first select the correct SCANSTA112 before boundary scan operations can begin.

Alternatively, the user might wish to select all the SCANSTA112s in the system at once. Consider the case where a system consists of a number of identical printed circuit boards on a backplane, each equipped with a SCANSTA112. Suppose that the same boundary scan operation is to be performed on all the boards in the system simultaneously: a board test, programming of a programmable device, or some other boundary scan operation. In this case the user will wish to select all the SCANSTA112s in the

system simultaneously and allow them all to perform the required operation on their respective boards. Note that even though all the SCANSTA112s in the system are to be selected at once, they cannot all be allowed to drive the backplane TDI line, to which they are all connected, at once. The SCANSTA112 features a special addressing mode to permit addressing all the SCANSTA112s in a system while preventing contention on the backplane TDI line.

Finally, the user might wish to select some, but not all, of the SCANSTA112s in the system and perform boundary scan operations only through the selected devices. A system with some PC boards of one type and some of another type on the same backplane, each equipped with a SCANSTA112, might call for this selection scenario. In this case the user might select the SCANSTA112s on all PC boards of one type for boundary scan operations. The unselected SCANSTA112s would not participate in these boundary scan operations. Note that this mode of operation also requires special consideration to prevent contention between multiple drivers on the backplane TDI line. The SCANSTA112 has a special addressing mode to accommodate this type of operation while preventing contention on the backplane TDI line.

The two primary operating modes of the SCANSTA112 are called ScanBridge mode and stitcher mode. The selection scenarios that require selection of a SCANSTA112 or a group of SCANSTA112s from among multiple SCANSTA112s in a system require the use of ScanBridge primary operating mode. In the next section we describe both primary operating modes.

# 3.1 SCANSTA112 Primary Operating Modes

The SCANSTA112 features two primary operating modes, ScanBridge mode and stitcher mode. We will postpone for the moment describing how the primary operating mode is selected and focus first on the differences in operation of the SCANSTA112 when it is in each of these primary operating modes.

The most important difference between these modes is that when a SCANSTA112 is in stitcher mode, it is always selected and always in its operational mode.

Consider a system in which there is only one SCANSTA112. In such a system it is not necessary to select a single SCANSTA112 from a set of SCANSTA112s because, obviously, there is only one SCANSTA112 to select. A SCANSTA112 in stitcher mode is always selected. This may be the desired behavior in a system with a single SCANSTA112.

Now compare such a system, with a single SCANSTA112, to a system with multiple SCANSTA112s. If all the SCANSTA112s in such a system were in stitcher primary operating mode, and were thus always selected, multiple SCANSTA112s might try to drive the backplane TDI line simultaneously, resulting in bus contention. Such a system will not work properly if the SCANSTA112s are in stitcher mode.

In a system with a single SCANSTA112 there is only one SCANSTA112 to drive the backplane TDI line. In such a system the SCANSTA112 may be used in stitcher primary operating mode, where it is always selected. A system like this, with a single SCANSTA112, really represents the only situation where the stitcher primary operating mode should be used.

Even when there is only one SCANSTA112 in a system, ScanBridge mode may still be used. So why would a system designer ever use stitcher mode?

Stitcher mode can simplify boundary scan operations by eliminating the need to configure the SCANSTA112 (here we assume that there is only one SCANSTA112 in the system) over the IEEE 1149.1 TAP. In stitcher mode the default configuration of the SCANSTA112, including which LSPs are selected and whether or not the SCANSTA112 is in transparent mode, is determined by logic values at the pins of the device. These logic values can be hardwired or can be supplied by any logic device in the system. This means that in stitcher mode the operation of the SCANSTA112 may be, though it need not be, entirely controlled by logic values on the SCANSTA112's pins. This can simplify operations over the IEEE 1149.1 TAP.

When the SCANSTA112 is operated in stitcher mode it is not necessary to send any commands to the SCANSTA112 to configure it. All the required configuration can be done by setting the appropriate logic values on the SCANSTA112's pins.

#### SCANSTA112 Selection and Addressing

ScanBridge mode may be used whether there is a single SCANSTA112 in a system or more than one. When the SCANSTA112 operates in ScanBridge mode it is not always selected the way it is in stitcher mode. In fact, when the SCANSTA112s in a system are operated in ScanBridge mode all boundary scan operations must begin by selecting the SCANSTA112s which will participate in them — even if there is only one SCANSTA112 in the system. After the desired SCANSTA112s are selected, the desired LSPs must be configured and unparked. The additional configuration steps required when the SCANSTA112s are operated in ScanBridge mode increases the complexity of the required boundary scan sequences; but this increased complexity also provides increased flexibility which is often necessary for efficient boundary scan operation.

# 3.2 Choosing the SCANSTA112 Operating Mode

The criteria for selecting the SCANSTA112 primary operating mode are simple. If there is more than one SCANSTA112 in a system, use ScanBridge mode. If there is only one SCANSTA112 in a system, either ScanBridge or stitcher mode may be used.

Stitcher mode permits the user to do everything that can be done in a system with a single SCANSTA112. Since the SCANSTA112 may be controlled entirely from dedicated control pins in stitcher mode this may simplify boundary scan operations.

In ScanBridge mode the SCANSTA112 can be addressed, so it can also be deselected. This makes ScanBridge mode suitable for use in applications where there is more than one SCANSTA112 in the system.

All the device functionality available in stitcher mode is also available in ScanBridge mode. In ScanBridge mode the SCANSTA112 must be configured by instructions delivered via the backplane TAP. Additional functionality which is not available in stitcher mode is available in ScanBridge mode.

The requirements for configuring and operating the SCANSTA112 in each of its two primary modes will be discussed next. We begin with how to set the primary operating mode.

# 3.3 Setting the Primary Operating Mode

The primary operating mode, either ScanBridge or stitcher, is ultimately controlled by the value of bit 2 in the control register. The registers of the SCANSTA112 will be described in a later section of this application note. For now it is sufficient to note that the control register is one of the optional registers permitted by the IEEE 1149.1 standard. It is an 8-bit read/write register, the contents of which control several important operating characteristics of the SCANSTA112.

If bit 2 of the control register is a 1, the SCANSTA112 operates in ScanBridge mode. If it is a 0, the SCANSTA112 operates in stitcher mode. The default value of bit 2 in the control register is set to the value present on the SB/S pin when the SCANSTA112 is powered up. The value on the SB/S pin will set the primary operating mode of the SCANSTA112 when it is powered up. For example, if the SB/S pin on a SCANSTA112 is tied to a static 1 (high) then the SCANSTA112 will always enter ScanBridge mode immediately upon power up.

After the SCANSTA112 has been powered up in stitcher mode there are two ways to set the SCANSTA112 to ScanBridge mode without cycling power to it.

- Drive the SB/S pin to a logic 1 (high) and reset the SCANSTA112. The reset can be accomplished by using the RESET pin, by using the TRST pin on the master backplane TAP, or by issuing a five-high TMS reset. The IgnoreReset bit in the control register, bit 0, when set to 1 will cause the SCANSTA112 to ignore the latter two reset methods listed above. The control register will be described later.

- 2. Write a 1 to bit 2 of the control register, the ScanBridge/Stitcher mode bit. This is not possible when the SCANSTA112 is in full transparent scan chain mode. As will be discussed below, the control register is not accessible in full transparent scan chain mode.

If the SB/S pin on the SCANSTA112 is tied to a static 0 (low) then the SCANSTA112 will always enter stitcher mode immediately upon power up. The SB/S pin should only be tied low in systems containing a single SCANSTA112.

After the SCANSTA112 has been powered up in ScanBridge mode there are two ways to set the SCANSTA112 to stitcher mode without cycling power to it.

1. Drive the SB/S pin to a logic 0 (low) and reset the SCANSTA112. The reset can be accomplished by

using the RESET pin, by using the TRST pin on the master backplane TAP, or by issuing a five-high TMS reset. The IgnoreReset bit in the control register, bit 0, when set to 1 will cause the SCANSTA112 to ignore the latter two reset methods listed above. The control register will be described later.

2. Write a 0 to bit 2 of the control register, the ScanBridge/Stitcher mode bit. This is not possible when the SCANSTA112 is in full transparent scan chain mode. As will be discussed below, the control register is not accessible in full transparent scan chain mode.

We will next describe the method for addressing one or more SCANSTA112s in a system. Note that this applies only to SCANSTA112s operating in ScanBridge mode. After the addressing operation in ScanBridge mode is described, we will describe the subsequent required operations in both primary operating modes.

# 3.4 Addressing Protocols in Scanbridge Mode

When the SCANSTA112 is operating as part of a scan chain defined by its LSPs it is said to be in operational state. In this state the SCANSTA112 is compliant to the IEEE 1149.1 standard except that the TDO output line may be at TRI-STATE (set to a high-impedance, non-driving state) even when the TAP controller is in the *Shift-Data-Register* or *Shift-Instruction-Register* states, as described below.

In ScanBridge mode the SCANSTA112 supports a two-level configuration protocol in addition to its operational state. In other words, in ScanBridge mode the SCANSTA112 sometimes behaves in a way that is not compliant to the IEEE 1149.1 standard. This behavior is necessary to permit the SCANSTA112 to perform its designed function of multiplexing boundary scan TAP signals. This behavior is referred to as the Level 1 and Level 2 protocols.

Level 1 protocol describes the required actions to address and select the desired SCANSTA112 when it is in ScanBridge mode.

Level 2 protocol applies after the SCANSTA112 has been addressed using the Level 1 protocol. Level 2 protocol describes the instructions delivered over the backplane TAP which are required to configure the multiplexing function and enable the connection (UNPARK) between the local scan chain and the backplane bus via a LSP.

# 3.4.1 Level 1 Protocol — Addressing the SCANSTA112

In a system with multiple SCANSTA112s, all the SCANSTA112s must operate in ScanBridge mode.

Consider the scenario where the user wishes to select only a single SCANSTA112 from multiple SCANSTA112s in a system. Each of the SCANSTA112s must be assigned a unique slot address. The boundary scan controller will begin the sequence of boundary scan operations by addressing the desired SCANSTA112 using its unique slot address.

The slot address of the SCANSTA112 is set by logic values on the  $S_{(0-7)}$  slot address pins. The logic values on these pins form an 8-bit slot address. The usable address space is shown in Table 5.

Before the SCANSTA112 is addressed its TAP controller is not active. Its TAP is instead under the control of a higher-level state machine as described in Section 7.1.

The selection state machine starts out in the *Wait-for-Address* state. In this state the SCANSTA112 compares the value shifted into its instruction register with its slot address. When the SCANSTA112 detects that it has been addressed, it becomes available to receive configuration instructions over the backplane TAP.

A second scenario is one in which all the SCANSTA112s in the system are to be selected. In this scenario, instead of selecting a SCANSTA112 by using its unique slot address, all the SCANSTA112s in the system are selected simultaneously using the predefined broadcast address (see Table 5). The addressing operation is similar to that described above except that the address to be compared is the broadcast address and not the unique address of a single SCANSTA112.

#### SCANSTA112 Selection and Addressing

www.ti.com

When all the SCANSTA112s in the system are selected using the broadcast address, contention on the backplane TDI line is avoided by tri-stating (setting to a high-impedance, non-driving state) the TDO output drivers of all the SCANSTA112s. Boundary scan operations may be performed by scanning instructions into the instruction registers of all the SCANSTA112s and their associated LSPs. Results of boundary scan tests may be accumulated in each SCANSTA112 in its Linear Feedback Shift Register (LFSR). Reading results back from the SCANSTA112s will require that each SCANSTA112 be addressed singly, so a system that uses broadcast addressing must also provide unique slot addresses for each SCANSTA112.

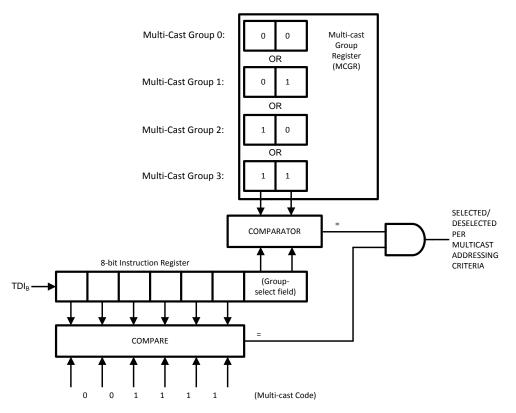

A user may also wish to select some, but not all, of the SCANSTA112s in the system. In this scenario, instead of selecting a SCANSTA112 by using its unique slot address, a subset of the SCANSTA112s in the system are selected simultaneously using one of four predefined multi-cast group addresses. The addressing operation is similar to that described above except that the address to be compared is one of the four multi-cast addresses (see Table 5) rather than the unique address of a single SCANSTA112. The multi-cast address to which each SCANSTA112 will respond is determined by the contents of its Multi-Cast Group Register (MCGR). Setting the value of the Multi-Cast Group Register in each SCANSTA112 will require that each SCANSTA112 be addressed singly, so a system that uses multi-cast addressing must also provide unique addresses for each of the SCANSTA112s.

When a set of SCANSTA112s in the system are selected using a multi-cast group address, contention on the backplane TDI line is avoided as in broadcast address selection by tri-stating the TDO output drivers of all the selected SCANSTA112s. Boundary scan operations may be performed by scanning instructions into the instruction registers of each of the selected SCANSTA112s and their associated LSPs. Results of boundary scan tests may be accumulated in each selected SCANSTA112 in its LFSR as in the broadcast addressing scenario described above. Reading back the results from each selected SCANSTA112 also requires that each SCANSTA112 be addressed individually as in the broadcast addressing scenario.

Once the Level 1 protocol has been carried out and the desired SCANSTA112(s) have been selected, the desired LSPs for each SCANSTA112 must be selected and unparked. This is accomplished by the Level 2 protocol described next.

### 3.4.2 Level 2 Protocol — Selecting and Unparking the Local Scan Chains

After a SCANSTA112 operating in ScanBridge mode has been addressed its LSPs must be selected and unparked before boundary scan operations on those LSPs can begin. The contents of the mode registers (mode register 0, mode register 1, and mode register 2) of a SCANSTA112 operating in ScanBridge mode control the selection of LSPs. A detailed description of the mode registers appears in Section 8.1. For now, however, we will focus on the operations required on the backplane TAP to select and configure the desired LSPs.

Upon power up or reset the contents of the mode registers are reset to their default values. See Table 4 for the default register values. The default register values insert LSP<sub>0</sub> into the scan chain.

Immediately after the SCANSTA112 is addressed all the LSPs, including the selected  $LSP_0$ , will be parked in the *Test-Logic-Reset* state. Prior to beginning boundary scan operations the boundary scan controller must select any additional desired LSPs (and deselect  $LSP_0$  if it is not to be used) and unpark the selected local scan chains.

Selection of the desired LSPs is accomplished by writing the appropriate values into the mode registers. The mode registers are accessed over the backplane TAP when the boundary scan controller issues the MODESEL, MODESEL1, or MODESEL2 instruction to the SCANSTA112. Note that at this point in the configuration sequence, when no LSPs have yet been unparked, the scan chain comprises only the SCANSTA112.

The effect of the values written to the various mode registers is discussed in Section 8.1. Writing the appropriate values into the mode registers selects the desired LSPs, but the selected LSPs are still parked at this point in the configuration sequence. In order to begin boundary scan operations the boundary scan controller issues the UNPARK instruction to the SCANSTA112 over the backplane TAP. As before, at this point in the configuration sequence the scan chain comprises only the SCANSTA112.

Once the backplane TAP sequences through the *Update-Instruction-Register* state after the UNPARK instruction is received, the selected LSPs are ready to be unparked. The LSPs actually enter the unparked state when the TAP controller sequences through the *Run-Test/Idle* state. At this point the LSP TMS lines and the state of the LSP TAP controllers begin to follow the backplane TAP. The TDO and TDI lines of the selected LSPs are connected through the SCANSTA112 to form the desired boundary scan chain. The configuration of the scan chain at this point depends upon which LSPs have been selected. This is shown in more detail in Table 8.

Upon completion of the required actions described by the Level 1 and 2 protocols the SCANSTA112 is in its operational state. When the SCANSTA112 is in its operational state, boundary scan data (sometimes referred to as scan vectors) are moved from the backplane TAP to one or more selected local scan chains.

In ScanBridge primary operating mode, the boundary scan controller must address the SCANSTA112, configure the local scan ports, and issue the UNPARK instruction over the backplane TAP prior to the start of boundary scan operations on the local scan chains. These initial instructions only affect the operation of the SCANSTA112 itself. These initial instructions can be inserted into the boundary scan test sequence automatically by most commercially available Automatic Test Pattern Generation (ATPG) tools. In an ATPG tool, this is called ScanBridge support.

The ScanBridge primary operating mode provides the same functionality as the (obsolete) SCANPSC110 and the SCANSTA111. These devices do not include a mode analogous to the stitcher mode.

When the SCANSTA112 is operated in stitcher mode it is always addressed, so the Level 1 and Level 2 protocols referred to above are not used. In stitcher mode the SCANSTA112 is always addressed and is always in its operational state. The relation of stitcher mode to the Level 1 and Level 2 protocols is described next.

### 3.5 Stitcher Mode

Stitcher mode provides a method of skipping the requirements of the Level 1 and 2 protocols of the ScanBridge mode of operation. If the SB/S pin is set to logic 0 (low) then the SCANSTA112 will be set to stitcher mode upon power up or reset.

After the SCANSTA112 is powered up or reset in stitcher mode it is not necessary to address it. In stitcher mode the SCANSTA112 always behaves as if it has been addressed. When in stitcher mode the SCANSTA112 goes directly to the operational state.

The stitcher mode is intended to permit the user to utilize the multiplexing capability of the SCANSTA112 with vector generation and delivery tools that do not feature ScanBridge support. A sequence generated by an ATPG tool without ScanBridge support may be used in a scan chain that includes a SCANSTA112 by using stitcher mode. When a SCANSTA112 is used in stitcher mode, such a boundary scan sequence may be used as is, without manual edits. Manual edits would be required to use the same sequence in a scan chain including a SCANSTA112 operating in ScanBridge mode.

In stitcher mode the selection of active LSPs is controlled by the LSP select register. This register is loaded at power up or reset with the logic values present on the LSPsel<sub>(0-6)</sub> pins. After the SCANSTA112 is powered up or reset in stitcher mode, the selected LSPs will be unparked and their TAP controllers will immediately follow the backplane TAP.

Mode registers 0-2 are not used to select LSPs when the SCANSTA112 is operated in stitcher mode. The desired LSPs are selected by the logic levels at the LSPsel<sub>(0-6)</sub> pins which set the values in the LSP select register. It is possible to change the contents of the LSP select register by writing directly to the register if it is accessible. This will change the LSP selection.

When the LSP selection is changed, local scan chains that are no longer selected will be parked in the *Run-Test/Idle* state after cycling through the *Test-Logic-Reset* state. Local scan chains that were previously parked will be re-synchronized with the backplane TAP and unparked when the backplane TAP sequences through the state in which they were parked.

The registers of the SCANSTA112 are accessible when the SCANSTA112 is set to normal, as opposed to full transparent, scan chain mode (scan chain modes are described in Section 4). In normal scan chain mode the registers of the SCANSTA112 can be written or read via the backplane TAP whether the SCANSTA112 is in stitcher or ScanBridge primary operating mode.

Writing the mode registers using the MODESEL, MODESEL1, and MODESEL2 instructions has no effect when the SCANSTA112 is in stitcher mode.

In stitcher mode, transparent scan chain mode is initiated by writing the TRANS bit of the control register rather than by using the TRANSPARENTENABLE and TRANSPARENTn instructions used in ScanBridge mode. (Scan chain modes are described in Section 4).

When the SCANSTA112 is used in stitcher mode it is normally configured by means of the device pins rather than by instructions from the boundary scan controller. This is the primary utility of stitcher mode. It should be noted, however, that many of the SCANSTA112 instructions available in ScanBridge mode are still available in stitcher mode. This gives the system designer increased flexibility in using the SCANSTA112.

In addition to reading and writing registers of the SCANSTA112, all the instructions that park and unpark the LSPs are available when the SCANSTA112 is in stitcher mode as long as it is not in full transparent mode.

There are differences in the operation of some instructions in stitcher mode. For example, while the SCANSTA112 is in stitcher mode the PARKTLR instruction will move the LSP TAPs to the *Test-Logic-Reset* state but will then idle them in the *Run-Test/Idle* state. The LSP TAPs will remain in the *Run-Test/Idle* state until the SCANSTA112 receives the UNPARK instruction and the backplane TAP is sequenced through the *Run-Test/Idle* state. The TLR\_TRST and TLR\_TRST\_6 pins have no effect when the PARKTLR instruction is used in stitcher mode because the local scan chains are really parked in *Run-Test/Idle*. The operation of the TLR\_TRST and TLR\_TRST\_6 bits in the control register and the associated SCANSTA112 pins is described in Section 7.5.

### 4 SCANSTA112 Scan Chain Modes

In each of the two primary operating modes, ScanBridge mode and stitcher mode, two scan chain modes are available. These are normal (not transparent) mode and full transparent mode. In ScanBridge primary operating mode an additional scan chain mode called transparent LSP mode is available.

The selected scan chain mode determines the configuration of the scan chain as seen from the boundary scan controller. We first describe the effect of each of these scan chain modes on the scan chain configuration and on the SCANSTA112.

### 4.1 Normal Scan Chain Mode

In normal scan chain mode the SCANSTA112 is itself part of the scan chain. This implies the following.

- 1. A register in the SCANSTA112 is inserted in the scan chain between the backplane TDI input and the first selected LSP TDO output. This register may be the instruction register, the boundary register, the bypass register, or any other register which can be inserted into the scan chain by the SCANSTA112.

- 2. The SCANSTA112 TAP controller sequences through the same series of states as the TAP controllers of the selected LSPs. When a five-high TMS reset is issued by the boundary scan controller, for example, the SCANSTA112 is also set to *Test-Logic-Reset* state. This will normally reset all the registers in the SCANSTA112 to their default values. Sometimes this reset behavior is undesired. A bit in the control register can be set to prevent unwanted resets of the SCANSTA112. The effects of this IgnoreReset bit will be described in more detail later.

- 3. A one-bit register is inserted between the TDI input of each LSP and the TDO output to the next LSP when multiple LSPs are chained together. This one-bit register re-synchronizes the LSP TDO transitions to the backplane TCK transitions on each pass through the SCANSTA112. It also delays the data sequence passing from the TDI of one LSP to the TDO of the next by one TCK period.

- 4. A single bit register is inserted between the TDI input of the final LSP in the chain and the TDO output to the backplane. This one-bit register re-synchronizes the backplane TDO transitions to the backplane TCK transitions. It also delays the data sequence passing from the TDI of the final LSP to the backplane TDO by one TCK period.

When the SCANSTA112 is in normal scan chain mode the scan chain may take on the following configuration:

Instruction Shift:  $\text{TDI}_B \rightarrow \text{SCANSTA112}$  IR (8-bit)  $\rightarrow \text{LSP}_{B1} \rightarrow \text{PAD} \rightarrow \text{LSP}_{01} \rightarrow \text{PAD} \rightarrow \text{LSP}_n \rightarrow \text{PAD} \rightarrow \text{TDO}_B$

| Data Shift: $TDI_B \rightarrow S$ | SCANSTA112 DR - | $\rightarrow LSP_{B1} \rightarrow PAD -$ | $\rightarrow LSP_{01} \rightarrow PAD$ | $\rightarrow LSP_n \rightarrow PAD \rightarrow T$ | ГDO <sub>в</sub> |

|-----------------------------------|-----------------|------------------------------------------|----------------------------------------|---------------------------------------------------|------------------|

|-----------------------------------|-----------------|------------------------------------------|----------------------------------------|---------------------------------------------------|------------------|

Note that in these examples, with  $LSP_{B0}$  is selected as the master backplane TAP and  $LSP_{B1}$  operates as  $LSP_{00}$ .

In normal scan chain mode the SCANSTA112 can be controlled via the backplane TAP. If the boundary scan controller is to issue an instruction to the SCANSTA112 while in this mode, it sequences the TAP controller to the *Shift-Instruction-Register* state. In this state the instruction register of the SCANSTA112 and the instruction registers of all the devices on the selected LSPs are placed in the scan chain. The boundary scan controller can now shift in the instructions required to perform the desired boundary scan operation through the backplane TDI pin of the SCANSTA112. This can include instructions meant for the SCANSTA112 itself.

The SCANSTA112 is located at the beginning of the scan chain so instructions destined for the SCANSTA112 are shifted in at the end of the instruction sequence. When the boundary scan controller subsequently sequences the TAP controller to the *Update-Instruction-Register* state the instructions shifted into all the instruction registers, including the instruction register of the SCANSTA112, are captured and executed. In this mode the boundary scan controller can control the operation of the SCANSTA112 just as it controls the operation of all the other devices in the scan chain.

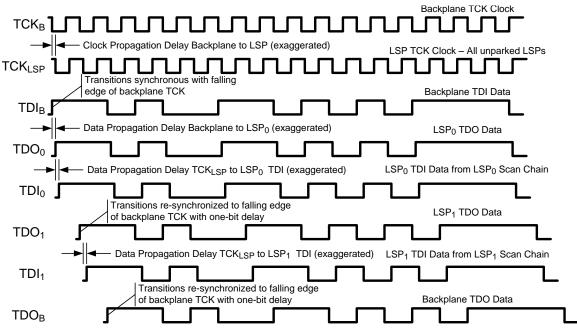

The insertion of the pad bit between the TDI input of the final LSP in the chain and the TDO output to the backplane insures that, from the perspective of the boundary scan controller, data transitions on the backplane TDO line occur on the falling edges of the backplane TCK. Figure 4 shows a timing diagram illustrating this point. In a basic boundary scan chain with no SCANSTA112, the TDO lines of all the devices in the scan chain change state on the falling edge of the TCK line. The TCK line is supplied to all the devices in parallel, so the transitions of each TDO line occur at approximately the same time.

When the SCANSTA112 is inserted in the scan chain it buffers the TCK line to all the selected LSP TCK lines. This introduces a delay between the backplane TCK signal and the TCK signal seen by all the devices in the LSP scan chain. These devices change their TDO lines on the falling edges of the TCK signal they see, which comes from the LSP of the SCANSTA112. At the TDO output of the SCANSTA112 there may be sufficient delay between the falling edge of the backplane TCK signal, which is being driven by the boundary scan controller, and the transitions of the TDO output to violate the timing conditions of the boundary scan controller.

Assuming that its own setup and hold time margins are met, the SCANSTA112 can re-time its TDO data to the backplane TCK. It detects the input data on the TDI line from the final LSP on the rising edge of the backplane TCK signal. This input data will have been set up by the last device in the local scan chain on the previous falling edge of the LSP TCK signal, which is delayed from the backplane TCK signal. The SCANSTA112 then transfers this data to the backplane TDO output on the **next** falling edge of the backplane TCK line. The result, from the viewpoint of the boundary scan controller, is that the backplane TCK line. This provides setup and hold times, again from the point of view of the boundary scan controller, approximately equal to 1/2 clock period even though the setup time from the point of view of the backplane is delayed by one bit from the TDO data from the last device in the scan chain. This is the pad bit added by the SCANSTA112 to re-synchronize the data.

Using the SCANSTA112 in normal mode requires that the boundary scan controller insert bits into the scan data stream to fill up the selected register in the SCANSTA112 and the pad bits inserted in the scan chain. This may require the user to modify an automatically generated test sequence with a text editor — or perhaps even with a hex editor. This may be something the user does not wish to undertake. Full transparent mode can be used to simplify the test sequence requirements. It may be necessary in full transparent mode to reduce the TCK frequency in order to satisfy the setup and hold time requirements of the boundary scan controller.

Figure 4. Timing Diagram – TDO<sub>B</sub>/TCK<sub>B</sub> Re-synchronization

# 4.2 Full Transparent Scan Chain Mode

In full transparent scan chain mode there are no pad bits or SCANSTA112 registers in the scan chain. Full transparent mode allows for the use of test sequences that were generated for a scan chain without the SCANSTA112 register and the pad bit. Such test sequences might come from an automatic test pattern generator or from software that generates programming sequences for a programmable logic device without ScanBridge support. When the SCANSTA112 is operated in full transparent scan chain mode such test sequences may be used without modification.

As an example, when the SCANSTA112 is operated in full transparent scan chain mode the scan chain may take on the following configuration:

$\text{TDI}_{\text{B}} \rightarrow \text{LSP}_{\text{B1}} \rightarrow \text{LSP}_{\text{01}} \rightarrow \text{LSP}_{\text{n}} \rightarrow \text{TDO}_{\text{B}}$

Note that in this example LSP<sub>B0</sub> is selected as the backplane TAP and LSP<sub>B1</sub> operates as LSP<sub>00</sub>.

Conversely, as indicated above, when the SCANSTA112 is in normal scan chain mode the scan chain may take on the following configuration:

Instruction Shift:  $TDI_B \rightarrow SCANSTA112 \text{ IR } (8\text{-bit}) \rightarrow LSP_{B1} \rightarrow PAD \rightarrow LSP_{01} \rightarrow PAD \rightarrow LSP_n \rightarrow PAD \rightarrow TDO_B$

Data Shift:  $\text{TDI}_B \rightarrow \text{SCANSTA112} \text{ DR} \rightarrow \text{LSP}_{B1} \rightarrow \text{PAD} \rightarrow \text{LSP}_{01} \rightarrow \text{PAD} \rightarrow \text{LSP}_n \rightarrow \text{PAD} \rightarrow \text{TDO}_B$

In full transparent scan chain mode the SCANSTA112 register does not appear in the scan chain. The pad bits also do not appear. The scan chain, from the perspective of the boundary scan controller, appears to consist only of the selected local scan chains. Note that any one, or more than one, local scan chains can be selected prior to initiating the full transparent scan chain mode of the SCANSTA112. The multiplexer function of the SCANSTA112 is thus still available.

When full transparent scan chain mode is activated, the selected LSP<sub>n</sub> lines will follow the backplane TAP lines.  $\overline{\text{TRST}_{\overline{n}}}$  will be a buffered version of  $\overline{\text{TRST}_{\overline{B}}}$ ,  $\overline{\text{TCK}_{n}}$  will be a buffered version of  $\overline{\text{TCK}_{B}}$ ,  $\overline{\text{TMS}_{n}}$  will be a buffered version of  $\overline{\text{TCK}_{B}}$ ,  $\overline{\text{TMS}_{n}}$  will be a buffered version of  $\overline{\text{TDO}_{B}}$ ,  $\overline{\text{TDO}_{n}}$  for the first LSP will be a buffered version of  $\overline{\text{TDO}_{B}}$  will be a buffered version of  $\overline{\text{TDO}_{B}$  will be a buffered version of  $\overline{\text{TDO}_{B}}$  will be a buffered version of  $\overline{\text{TDO}_{B}$  will be a buffered version of  $\overline{\text{TDO$

TRIST<sub>B0</sub>, TRIST<sub>B1</sub>, and TRIST<sub>(0-3)</sub> will be asserted when the state machine is not in either the *Shift-Data-Register* or *Shift-Instruction-Register* states. This is consistent with the IEEE 1149.1 standard. The unselected LSPs will be placed in the *Parked-TLR* state, and their clocks will be gated (driven to a static 0) after 512 TCK<sub>B</sub> clock cycles.

When the SCANSTA112 is in ScanBridge primary operating mode and one of the transparent mode instructions (TRANSPARENTENABLE or TRANSPARENTn) is shifted into the instruction register, the SCANSTA12 enters full transparent scan chain mode. After the instruction is scanned in, the tap controller goes through the *Update-Instruction-Register* state at which point  $\overline{\text{TRST}}_n$  will go high, and  $\text{TMS}_n$  will go low. This will force the targets connected to the LSP<sub>n</sub> ports to go into the *Run-Test/Idle* state. Then, when the SCANSTA112 state machine goes into the *Run-Test/Idle* state, all of the LSP<sub>n</sub> signals will follow the backplane TAP signals. This is identical to the method that is typically used to unpark a LSP. The TAP controller must be sequenced through the state in which the LSPs are parked in order to unpark them and allow them to follow the backplane TAP state.

The SCANSTA112 will remain in transparent mode until it is reset. Once in full transparent mode, the SCANSTA112 will not respond to a five-high TMS reset but it will respond to assertion of the  $\overline{\text{TRST}}_{\overline{B}}$  line if the IgnoreReset bit in the control register is not set.

The SCANSTA112 can be used in a scan chain mode that provides a compromise between normal scan chain mode and full transparent scan chain mode. This is the transparent LSP scan chain mode, which is discussed next.

# 4.3 Transparent LSP Scan Chain Mode

Transparent LSP scan chain mode provides improved scan chain performance relative to both normal mode and full transparent mode. In this mode no pad bits are placed in the chain between unparked LSPs that are chained together. A register in the SCANSTA112 and the pad bit of the final selected LSP are included in the scan chain. This mode offers two advantages over full transparent mode: it is capable of higher speeds than full transparent mode; and the boundary scan controller can control the SCANSTA112 via the backplane TAP in this mode.

In transparent LSP mode the chain may take on the following configuration:

Instruction:  $\text{TDI}_B \rightarrow \text{SCANSTA112}$  IR (8-bit)  $\rightarrow \text{LSP}_a \rightarrow \text{LSP}_n \rightarrow \text{PAD} \rightarrow \text{TDO}_B$

Data Shift:  $\text{TDI}_B \rightarrow \text{SCANSTA112} \text{ DR} \rightarrow \text{LSP}_a \rightarrow \text{LSP}_n \rightarrow \text{PAD} \rightarrow \text{TDO}_B$

Note that in the transparent LSP mode no additional pad bits are inserted between LSPs that are chained together. Compare the chain configurations shown above to those for normal scan chain mode and full transparent scan chain mode.

The transparent LSP scan chain mode is only available when the SCANSTA112 is operating in its ScanBridge primary mode. In ScanBridge mode LSP selection is controlled by the values in mode registers 0-2. Transparent LSP scan chain mode is enabled by setting mode register 1 bit 7 to a 1. This bit has no effect when the SCANSTA112 is in stitcher mode.

Using the transparent LSP mode may require manual edits to boundary scan test sequences generated using ATPG tools. The SCANSTA112 register contents and the trailing pad bit can be inserted easily into a test sequence described by a Serial Vector Format (SVF) file. The additional bits can be set to static values. For example, the instruction to the SCANSTA112 can always be FF hex (11111111), which is the opcode for the BYPASS instruction. The required static bit patterns are specified by the HIR (Header-Instruction-Register), HDR (Header-Data-Register), TIR (Trailer-Instruction-Register), and TDR (Trailer-Data-Register) instructions in the SVF file. These bit patterns are automatically prepended or appended to each boundary scan transaction by the boundary scan controller so they do not need to be added explicitly to each boundary scan transaction. In normal mode when multiple LSPs are chained together, it may be necessary to edit each boundary scan transaction in order to put the pad bits in the right place in the bit sequence because there is a pad bit between each LSP's TDI and the TDO of the following LSP.

Primary Operating Modes and Scan Chain Modes

### 5 Primary Operating Modes and Scan Chain Modes

Both normal scan chain mode and transparent scan chain mode can be used in either the ScanBridge or stitcher primary operating mode. The interaction of the scan chain mode and the primary operating mode is described in this section.

### 5.1 Scanbridge Normal Scan Chain Mode

In order for the SCANSTA112 to operate in ScanBridge primary operating mode the SB/S bit in the control register must be set to 1. Since this bit is set to the value of the SB/S pin on power up or reset, this pin must be high when the power up or reset occurs in order for the SCANSTA112 to go into the ScanBridge mode by default. When the SCANSTA112 is powered up or reset in ScanBridge mode the values on the TRANS and LSPsel<sub>(0-6)</sub> pins are ignored. The SCANSTA112 must be configured via the backplane TAP in ScanBridge mode.

Once the SCANSTA112 has been addressed, selection of the LSPs is performed by writing the values of the mode registers 0-2. These registers are inserted into the boundary scan chain by writing the MODESEL, MODESEL1, or MODESEL2 instruction to the SCANSTA112. The selected LSPs become unparked when the backplane TAP controller cycles through the *Run-Test/ldle* state after the boundary scan controller has issued the UNPARK instruction to the SCANSTA112. In ScanBridge mode both the setting of the LSP select register and the LSPsel<sub>(0-6)</sub> pins are ignored.

### 5.2 Scanbridge Full Transparent Scan Chain Mode

In ScanBridge mode the SCANSTA112 must be addressed and its LSPs selected using the Level 1 and 2 protocols describe earlier. To use full transparent scan chain mode with the ScanBridge primary operating mode, a single SCANSTA112 must first be selected according to the Level 1 protocol and one or more LSPs must be selected according to the Level 2 protocol. This requires that the instruction sequences required by the Level 1 and Level 2 protocols be issued by the boundary scan controller over the backplane TAP.

Once a SCANSTA112 has been selected and its LSPs selected and unparked, an instruction to the SCANSTA112 via the backplane TAP enables transparent scan chain mode. The TRANSPARENTn or TRANSPARENTENABLE instruction will enable transparent scan chain mode for a SCANSTA112 in ScanBridge mode.

The TRANSPARENTENABLE instruction puts the SCANSTA112 in transparent scan chain mode with the scan chain defined by the contents of the mode registers. The TRANSPARENTn instruction puts the SCANSTA112 in transparent scan chain mode with a single LSP, LSP<sub>n</sub>, overriding the contents of the mode registers.

Transparent scan chain mode will override any other active mode. In particular, it will override transparent LSP scan chain mode.

In transparent scan chain mode the TAP signals on the selected LSP(s) become buffered versions of the backplane signals. In this mode the TAPs on the LSPs can be reset by a five-high TMS reset and the SCANSTA112 will not respond to the reset.

The sequence of operations to activate transparent scan chain mode on a single LSP by issuing the TRANSPARENTn instruction are as follows. The example uses LSP<sub>0</sub>. The example assumes that the SCANSTA112s in the system are operating in ScanBridge mode.

- 1. Scan the address of the desired SCANSTA112 into the instruction register (address a SCANSTA112).

- 2. Scan the TRANSPARENTO instruction into the instruction register to enable full transparent scan chain mode on LSP<sub>0</sub>. Full transparent mode will be enabled when the TAP controller enters the *Run-Test/Idle* state at the end of this shift operation. At this point  $\overline{\text{TRST}}_{\overline{0}}$ ,  $\text{TDO}_{0}$ ,  $\text{TMS}_{0}$  and  $\text{TCK}_{0}$  become buffered versions of  $\overline{\text{TRST}}_{\overline{B}}$ ,  $\text{TDI}_{B}$ ,  $\text{TMS}_{B}$  and  $\text{TCK}_{B}$  and  $\text{TDO}_{B}$  becomes a buffered version of  $\text{TDI}_{0}$ .

Transparent mode will persist until the SCANSTA112 is reset. The GOTOWAIT and SOFTRESET instructions will not work in this mode. The SCANSTA112 will respond to the  $\text{TRST}_{\overline{B}}$  or RESET signals and will be reset when either of these signals is asserted. When the SCANSTA112 is reset it returns to the default primary operating mode. If this default primary operating mode is ScanBridge mode the SCANSTA112 will also return to normal scan chain mode.

It is possible to mask the  $\overline{\text{TRST}}_{\overline{B}}$  reset so that the SCANSTA112 will not respond to it when in ScanBridge transparent mode. When the IgnoreReset bit in the control register is set the SCANSTA112 will not respond to the  $\overline{\text{TRST}}_{\overline{B}}$  reset. When the IgnoreReset bit is set, the TAPs on the LSPs can be reset by the  $\overline{\text{TRST}}_{\overline{B}}$  reset and the SCANSTA112 will not be reset.

If the IgnoreReset bit in the control register is to be set, it must be set before the SCANSTA112 is put into transparent scan chain mode. When the SCANSTA112 is in transparent scan chain mode the control register is not accessible.

The boundary scan controller cannot control the SCANSTA112 via any of the backplane TAP lines when the SCANSTA112 is in full transparent mode and the IgnoreReset bit is set. The only way to reset the SCANSTA112 in this condition is to assert the RESET pin low or to cycle the power. This pin was not available in the SCANSTA111, so the SCANSTA111 could always be reset in transparent mode by a TRST<sub>B</sub> reset. For applications that expect the SCANSTA112 to behave in the same manner as the SCANSTA111 it is suggested the TRST<sub>B</sub> and the RESET pins be connected together. When this connection is made, asserting the TRST<sub>B</sub> reset will always reset the SCANSTA112 even if the IgnoreReset bit in the control register is set.

# 5.3 Stitcher Normal Scan Chain Mode

When a single SCANSTA112 in a system is operated in stitcher mode, its internal registers may still be accessible to the boundary scan controller. When the SCANSTA112 is in stitcher primary mode and in normal scan chain mode, the boundary scan chain consists of the currently selected internal SCANSTA112 register, plus the LSPs that are selected via the LSP select register, plus the pad bits associated with the selected LSPs.

When the SCANSTA112 is in stitcher primary operating mode, the selection of normal scan chain mode or full transparent scan chain mode is determined by the value of the TRANS bit in the control register. This value is initialized by the value on the TRANS pin of the SCANSTA112 at power up or reset. If the TRANS pin is low at power up or reset, the TRANS bit in the control register will be initialized to 0 and the SCANSTA112 will go into stitcher normal scan chain mode.

As previously described, the LSP select register contents are initialized as the value of the respective LSPsel<sub>(0-6)</sub> pins upon power up or reset. These values may be changed by selecting the LSP select register using the LSPSEL instruction and loading new values into this register via the TDO pin. This changes the scan chain configuration to match the new set of LSPs in the LSP select register.

The control register may be modified in the same manner as the LSP select register by issuing the CONTROLSEL instruction. Some of the bits in the control register, such as the TRANS bit, assume default values on power up or reset according to the values on the SCANSTA112 input pins (see Table 4). Setting the TRANS bit in the control register to 1 when the SCANSTA112 is in stitcher normal mode will cause it to go to stitcher full transparent mode.

# 5.4 Stitcher Full Transparent Scan Chain Mode

When the SCANSTA112 is in stitcher primary operating mode the TRANS bit in the control register controls the activation of transparent mode. In stitcher mode the selection of normal or full transparent mode may be made by setting the logic value on the TRANS pin. The logic value on this pin is detected and used to set the value of the TRANS bit in the control register when the device is powered up or reset.

If the TRANS pin on the SCANSTA112 is a 1 at power up or reset the SCANSTA112 will be set to transparent scan chain mode if it is in stitcher primary operating mode. The TRANS bit in the control register is still set by the value on the TRANS pin at power up or reset even when the SCANSTA112 is in ScanBridge primary operating mode, but the register value is ignored when the SCANSTA112 is in ScanBridge primary operating mode.

The SCANSTA112 can also be set to stitcher full transparent mode from stitcher normal mode. Setting the SCANSTA112 to transparent mode is accomplished by setting the TRANS bit in the control register to 1. This is only effective in stitcher mode. The TRANS bit is ignored in ScanBridge mode. This should only be done after the desired LSPs are selected and any other register changes are completed because after the SCANSTA112 is set to full transparent scan chain mode the LSP select register will no longer be accessible.

Primary Operating Modes and Scan Chain Modes

Stitcher transparent mode is used when the SCANSTA112 is to function as an pin-controlled JTAG multiplexer. No SCANSTA112 registers or pad bits are placed into the scan chain. This mode of operation allows the use of most automatically generated test sequences without the need to manually edit them.

Setting the TRANS bit in the control register to 1 places the SCANSTA112 into the stitcher transparent mode. Prior to setting this bit, when the SCANSTA112 is not in full transparent mode, its TAP controller is controlled by the backplane TMS line just as the LSP TAP controllers are. When the control register in the SCANSTA112 is written with a new value which sets the TRANS bit to 1, and the TAP controllers move into the *Update-Data-Register* state, the internal instruction, data, and pad bit registers of the SCANSTA112 are removed from the chain, putting it into transparent mode. The TAP controllers of all unparked local scan chains will be in the *Update-Data-Register* state and will follow the backplane TAP controller. Data scanned in on the TDO line when the SCANSTA112 is in transparent mode will be presented directly to the TDI line of the first selected local scan chain. The SCANSTA112 will no longer respond to boundary scan instructions on the backplane TAP.

As in ScanBridge transparent mode, the TAPs on the LSPs can be reset by way of the five-high TMS reset and the SCANSTA112 will not respond to the reset. When the IgnoreReset bit in the control register is set, the TAPs on the LSPs can be reset by way of  $\overline{\text{TRST}}_{\overline{B}}$  reset and the SCANSTA112 will not respond to the reset. Note that the IgnoreReset bit in the control register must be set prior to activating the transparent scan chain mode since the control register is not accessible once this mode is activated. In stitcher transparent mode, as in ScanBridge transparent mode, when the IgnoreReset bit is set the only method of resetting the SCANSTA112 is to assert the RESET pin low or to cycle the power.

Once the SCANSTA112 is put in transparent mode, this mode can only be exited by a reset. Assertion of the  $\overline{\text{TRST}}_{\overline{B}}$  pin will reset the SCANSTA112 if the IgnoreReset bit in the control register is not set. If this bit is set then the SCANSTA112 may only be reset by asserting RESET or by a power cycle. Whenever the SCANSTA112 is in transparent mode, five-high TMS resets are ignored.

After the SCANSTA112 is reset the default values of the control register and LSP select register bits will be set from the external device pins as they were on power up. If the SCANSTA112 SB/S pin is still held low at this point, the SCANSTA112 will again enter stitcher mode. Depending upon the value at the TRANS pin, which is transferred to the TRANS bit in the control register, the SCANSTA112 will enter either normal or transparent stitcher mode. It is therefore possible for the SCANSTA112 to be reset in transparent stitcher mode and immediately enter transparent stitcher mode again, depending upon the values imposed at the device pins.

### 5.5 Primary Operating Mode/Scan Chain Mode Summary

The interactions between the device pins, the two primary operating modes, and the three scan chain modes is somewhat complex. The interactions of the primary operating and scan chain modes, the SCANSTA112 pins, and the SCANSTA112 registers are summarized in Table 1

| Primary Operating Mode              | ScanBridge Mode                                             | Stitcher Mode                                             |

|-------------------------------------|-------------------------------------------------------------|-----------------------------------------------------------|

| SB/S pin                            | Sets SB/S bit in control register on power<br>up or reset   | Sets SB/S bit in control register on power<br>up or reset |

| SB/S bit in control register        | 1 sets ScanBridge mode                                      | 0 sets stitcher mode                                      |

| $S_{(0-7)}$ slot address pins       | Used for address matching (Level 1 protocol)                | Not used                                                  |

| TRANS pin                           | Sets TRANS bit in control register on power up or reset     | Sets TRANS bit in control register on power up or reset   |