### DS15BA101,DS15EA101,DS25BR110

Extending the Signal Path Over Data Transmission Lines Using LVDS Signal

Conditioning

Literature Number: SNLA209

# SIGNAL PATH designer®

Tips, tricks, and techniques from the analog signal-path experts

#### No. 110

Feature Article....1-7

LVDS Buffers ......2

High-Speed Differential Amps and ADCs .....4

Video Cable Equalizer .....6

Design Tools ......8

### **Extending the Signal Path Over Data Transmission Lines**

— By Lee Sledjeski, Applications Engineer

fter using an ADC to convert an RF signal to the digital domain, this signal often needs to be sent across a backplane or cable to an FPGA for additional processing. As sampling speeds continue to increase, the challenge becomes driving this signal more than a few dozen centimeters without bit errors. This article examines how to solve the challenges of extending high-speed signal paths over FR-4 traces and copper cables.

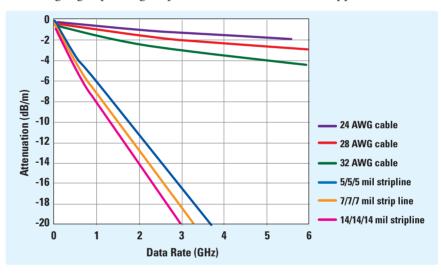

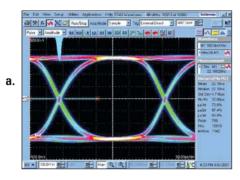

Figure 1. Transmission Media Loss (Differential) Shows the Low Pass Filter Effect

As an example of these high-speed signal challenges, consider the graph in *Figure 1*. When a 2.5 Gbps NRZ signal transitions every bit cycle it generates the equivalent of a 1.25 GHz clock signal. This component of the 2.5 Gbps signal sees up to 10 dB loss after just 1 meter of  $100\Omega$  differential FR-4 stripline. It takes as much as 10 meters of twinaxial cable to generate a similar media loss. This transmission loss creates jitter that eventually closes the signal "eye" or sampling window as seen in *Figure 2a*.

For high-speed signals, a low pass filter (*Figure 1*) represents the transmission media. The highest frequency that passes through the media with less than 3 dB of attenuation defines the filter bandwidth. Signal components within the

### LVDS Plus Signal Conditioning Solves Your Signal Integrity Problems

### 3.125 Gbps LVDS Buffers with Pre-Emphasis and Equalization

### DS25BR100/110/120 Features

- 17 ps typ jitter (2.5 Gbps, 2<sup>23</sup>-1 pattern)

- Programmable pre-emphasis and equalization

- Wide range input accepts LVDS, CML, and LVPECL

- Integrated  $100\Omega$  input and output termination

- 7K ESD protection on LVDS pins

|            |                            |        |         |                     | <b>200 →</b> 2000 |                          |                                 |                           |                 |                            |

|------------|----------------------------|--------|---------|---------------------|-------------------|--------------------------|---------------------------------|---------------------------|-----------------|----------------------------|

| Product ID | LVDS<br>Buffer<br>Function | Inputs | Outputs | Input Compatibility | Output            | Pre-<br>emphasis<br>(dB) | Receive<br>Equalization<br>(dB) | Max<br>Speed/Ch<br>(Mbps) | Packaging       | Comments                   |

| DS25BR100  | Single                     | 1      | 1       | LVDS/LVPECL/CML     | LVDS              | 0/6                      | 3/6                             | 3125                      | LLP-8           | Int termination, 8 kV ESD  |

| DS25BR110  | Single                     | 1      | 1       | LVDS/LVPECL/CML     | LVDS              | —                        | 0/3/6/9                         | 3125                      | LLP-8           | Int termination, 8 kV ESD  |

| DS25BR120  | Single                     | 1      | 1       | LVDS/LVPECL/CML     | LVDS              | 0/3/6/9                  | -                               | 3125                      | LLP-8           | Int termination, 8 kV ESD  |

| DS90LV804  | Quad                       | 4      | 4       | LVDS/LVPECL/CML     | LVDS              | —                        | -                               | 800                       | LLP-32          | Int termination, 15 kV ESD |

| DS90LV004  | Quad                       | 4      | 4       | LVDS/LVPECL/CML     | LVDS              | 0/2/4/6                  | -                               | 1500                      | TQFP-48         | Int termination, 15 kV ESD |

| DS15BR400  | Quad                       | 4      | 4       | LVDS/LVPECL/CML     | LVDS              | 0/6                      | -                               | 2000                      | LLP-32, TQFP-48 | Int termination, 15 kV ESD |

| DS15BR401  | Quad                       | 4      | 4       | LVDS/LVPECL/CML     | LVDS              | 0/6                      | —                               | 2000                      | LLP-32, TQFP-48 | 15 kV ESD                  |

**Signal Conditioning**

Ideal for use in routers, switches, storage, medical imaging, video security, and image capture and processing

🛋 3 x 3 x 0.8 mm LLP-8

For samples, datasheets, and more information, contact us today at:

lvds.national.com

# SIGNAL PATH designer

### **Extending the Signal Path Over Data Transmission Lines**

media bandwidth pass through with minimal attenuation. Furthermore, the media attenuates the amplitude of signal components and harmonics beyond the -3 dB point or transmission line bandwidth. Data-dependent jitter due to Inter-Symbol Interference (ISI) results from this non-linear, frequency-dependent loss. Therefore, signal conditioning refers to the compensation techniques used to mitigate the effects of high-frequency transmission losses. Conditioning input and output signals enhance the performance and extend the signal-path distance.

### Input and Output Signal Conditioning

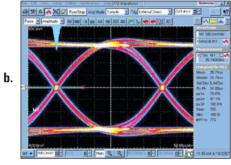

2.5 Gbps NRZ PRBS-7 after 70" Differential FR-4 Stripline V:100 mV/DIV, H:75 ps/DIV

Figure 2a. 2.5 Gbps NRZ Signal After 70 Inches of FR-4 Without Equalization

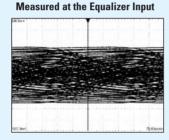

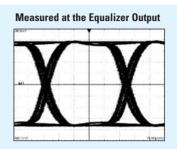

Signal integrity designers use equalizers to condition input signals. The equalizer circuit goal is to reverse the signal losses incurred during transmission by "flattening" the frequency response of the system and thereby reducing the distortion or "smearing" that the signal encounters. The equalizer flattens the transmission frequency response by acting as a high-pass filter that approximately complements the low-pass effect of the transmission medium within the signal's frequency band. As a general rule of thumb, the equalization should flatten the frequency response up to the frequency produced by the highest transition density data pattern possible. For example, a 2.5 Gbps data rate signal in a 1-0-1-0 NRZ pattern would require a flat frequency response out to 2.5 GHz (Figure 1). When properly tuned, equalization can significantly reduce the ISI effects from the transmission media as shown in Figure 2b. Even for 29.5" stripline, attenuation

Equalized 2.5 Gbps NRZ PRBS-7 after 70" Differential FR-4 Stripline V:100 mV/DIV, H:75 ps/DIV

Figure 2b. 2.5 Gbps NRZ Signal After 70 Inches of FR-4 With Equalization (b)

approaches -6 dB at 2.5 Gbps, and it is safe to say that reliable communication across the transmission link requires some equalization.

High-speed devices such as the DS25BR110 feature a receiver input equalization circuit to reduce the effects of frequency dependent losses caused by the transmission medium (*Figure 2*). Four levels of EQ control ranging from 0 to 16 dB allow for easy optimization of signal quality across a broad range of typical transmission media lengths.

Transmitter output signal conditioning is used to produce a similar overall net effect. While input equalization acts to cancel frequency-dependent losses, output Pre-Emphasis (PE) alters the frequency content of a clean, unattenuated signal with the expectation that the transmission media attached to the driver will attenuate the signal. This results in a clean signal at the receiver positioned on the far end of the transmission line. By applying PE to the output waveform, the highest frequency components of the signal are emphasized at the driving device. Because signal conditioning requirements increase with higher data rates, multiple levels from 0 to 9 dB can be selected to optimize the signal integrity at the receiver for most common PCB and copper cable transmission distances (Figure 3).

### **Setting Pre-Emphasis and Equalization**

Signal conditioning is designed to compensate for the low-pass filter effect of the transmission medium. As a starting point, adjust the level to match the loss of

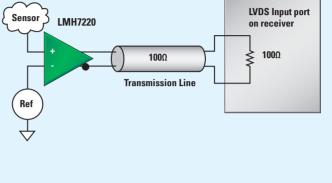

### **High-Speed Comparator and High-Bandwidth A/D Converters with LVDS Outputs**

### Low-Power Comparator and ADCs for High-IF Sampling Systems

#### LMH7220 Features

- 2.9 ns propagation delay (100 mV overdrive)

- 0.6 ns rise/fall times

- Supply voltage: 2.7V to 12V

- · Supply current: 6.8 mA

- Temperature range: -40°C to 125°C

- LVDS output

- Available in TSOT-6 packaging

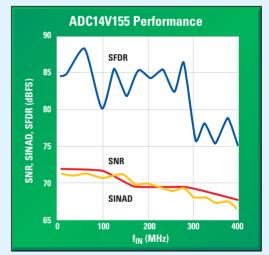

#### ADC12V170 and ADC14V155 Features

- 1.1 GHz full power bandwidth

- Dual 3.3V, 1.8V supply operation

- Dual data rate parallel LVDS outputs

- Pinout equivalent to ADC12C170 and ADC14155 with CMOS outputs

- Clock duty cycle stabilizer

- Internal sample-and-hold circuit

- Internal precision 1.0V reference

- Available in LLP-48 packaging (7 x 7 x 0.8mm)

| Product ID | Resolution<br>(Bits) | Speed<br>(MSPS) | Output Format     | Power (mW) | SNR (dB) | SFDR (dB) | Packaging |

|------------|----------------------|-----------------|-------------------|------------|----------|-----------|-----------|

| ADC14V155  | 14                   | 155             | DDR Parallel LVDS | 951        | 71.7     | 86.9      | LLP-48    |

| ADC12V170  | 12                   | 170             | DDR Parallel LVDS | 781        | 67.2     | 85.8      | LLP-48    |

| ADC14155   | 14                   | 155             | CMOS              | 967        | 71.3     | 87.0      | LLP-48    |

| ADC12C170  | 12                   | 170             | CMOS              | 715        | 67.2     | 85.4      | LLP-48    |

For FREE samples, datasheets, and more information, visit: signalpath.national.com

# SIGNAL PATH designer

### **Extending the Signal Path Over Data Transmission Lines**

DS25BR120 Pre-Emphasis: OFF 3.125 Gbps with a PRBS7 pattern Output load: 4" FR-4 100  $\Omega$  differential trace

DS25BR120 Pre-Emphasis: ON (6 dB setting) 3.125 Gbps with a PRBS7 pattern Output load: 20" FR-4 100Ω differential trace

your transmission line at the primary frequency of interest, tweaking one level up and down to ensure optimal quality of the received waveform eye pattern. When considering signal conditioning, the primary frequency of interest is normally the data rate divided by 2 (e.g., for a 2.5 Gbps signal use  $2.5 \div 2=1.25$  GHz, for a 1 Gbps signal use 500 MHz). This is the frequency of the data pattern with the highest level of attenuation. A network analyzer is the easiest way to generate a loss graph like that in *Figure 1*. If a network analyzer is unavailable, it is also possible to send a sine wave at the frequency of interest across your transmission line and use the attenuation value as your loss value.

Input EQ, output signal conditioning, or a combination of both can be used to compensate for lossy transmission lines. Each method has advantages and disadvantages and the choice of which one to use depends on the application and personal preference. Output PE has the advantage of being easily measurable. Its effect is visible at the receiver and can be easily monitored and adjusted. Receive EQ is often used in crosstalk-sensitive and low-power applications since it does not add extra energy to the transmission line. In very lossy applications where EQ or PE alone is not sufficient, both input and output signal conditioning may need to be used in combination, e.g. 9 dB of pre-emphasis with 9 dB of receive equalization.

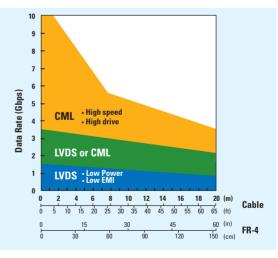

### Should I use LVDS or CML?

Discrete LVDS implementations can be used effectively to data rates in excess of 3 Gbps. Current Mode Logic (CML) is the I/O of choice at speeds of 3.5 Gbps (*Figure 4*) and beyond. LVDS generally has lower power and less EMI and is well-defined as an interface standard. CML is capable of higher speeds and typically has higher drive strength than LVDS. Either signaling technology can often be used at rates between 1 and 3.125 Gbps so a good translation strategy is important for optimal signal integrity.

Figure 4: Typical LVDS and CML Applications

For successful level translation, the driver's differential output voltage (V<sub>OD</sub>) and common mode voltage (V<sub>CM</sub>) must fall within the receiver's input range. For LVDS the V<sub>OD</sub> (as defined in the EIA/TIA-644A standard) is the voltage difference across the driver outputs with a 100 $\Omega$  resistive load.

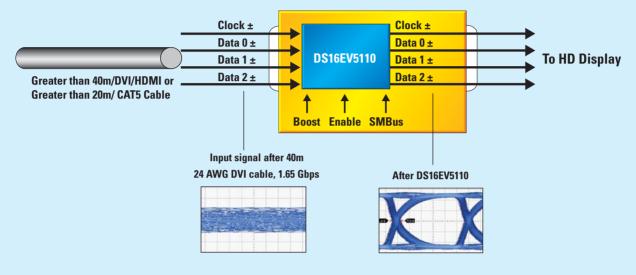

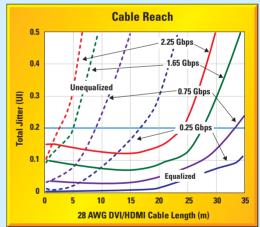

### Industry's Lowest Jitter Video Cable Equalizer

## DS16EV5110 Enables Superior Picture Quality for 1080p Deep-Color Video Applications and Extends HDMI and DVI Cable Reach Beyond 40 Meters

#### **DS16EV5110 Features**

- Significantly extends reach of HDMI, DVI, and CAT5 cables

- · Settable boost for optimal equalization

- Low total jitter: 0.13 UI on 30m 24 AWG DVI cable

- Low power: 475 mW

- Clock channel LOS and output enable for power savings

- Serial Management Bus (SMBus) provides extra design flexibility

- Available in tiny 7 mm x 7 mm LLP-48 packaging

Ideal for use in HDMI, DVI, and CAT 5 cable extenders, switchers, digital routers and switches, projectors, and high-definition displays

For samples, datasheets, and more information, contact us today at:

lvds.national.com

"Designing Long-Reach Applications with DVI HDMI and PCI Express Cable Standards" www.national.com/nationalty

# **SIGNAL PATH** | *designer*

### **Extending the Signal Path Over Data Transmission Lines**

Other differential standards specify the output voltage amplitude as a peak to peak number. As an example, a 400 mV LVDS  $V_{OD}$  is exactly equal in amplitude to an 800 mV peak-to-peak CML output, but located at a different offset voltage with respect to GND.

LVDS receiver devices offer the greatest flexibility of any differential technology because their wide input common mode range easily accepts the signal swings of 1.2V/1.5V/2.5V CML and LVPECL differential I/O. This allows for a direct DC connection between most differential outputs and LVDS inputs, minimizing the added PCB real estate and cost of multiple AC-coupling capacitors.

The LVDS transmitter output V<sub>OD</sub> is specified to be 250 mV minimum (500 mV peak-to-peak) for high performance with low EMI and low-power consumption. Adding output signal conditioning enables LVDS to drive extended lengths of cable or large backplanes. The LVDS output rides on a 1.2V common mode voltage developed from an internal bandgap reference and can be DC coupled to many LVPECL inputs. CML inputs with а limited common mode range, however, require an AC-coupled interface because the LVDS output voltage swing does not meet the minimum common mode requirements for most CML inputs.

Many LVDS and CML buffer chips offer preemphasis and/or receive equalization to boost signals coming from ADCs, DACs, FPGAs, and DSPs, and some have multiplexing functions for switching/ redundancy applications. A low-power solution for redundancy, multiplexing, and signal distribution can be achieved with a combination of highperformance LVDS crosspoint switches and high-speed FPGA CML I/O. Programming CML outputs for 600 mV to 800 mV will reduce transmit power expended by the FPGA integrated SerDes, lower the overall EMI signature of the interface, and provide the optimum signal for LVDS inputs with EQ.

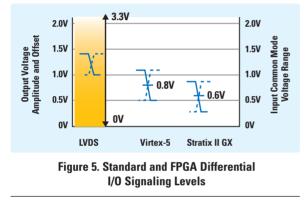

The latest generation FPGAs with CML I/O have common-mode output voltages lower than the nominal 1.2V stated in the LVDS standard (*Figure 5*). The extended input common mode range allows the high-speed FPGA I/O to interoperate with LVDS devices.

#### **Driving Over 20 Meters**

LVDS and CML signal conditioners are capable of extending signal paths up to a maximum of 20m at multi-Gbps speeds. For longer distances, Ethernet can be used but requires additional protocol and timing overhead to fit the signal path raw data into Ethernet packets. Alternatively, a cable driver and adaptive equalizer can be used to extend serialized data up to 100s of meters. The DS15BA101/EA101 is a 1.5 Gbps cable extension chipset for  $100\Omega$ twisted pair and  $50\Omega$  coaxial cables up to hundreds of meters. Unlike many other signal conditioners with equalization, this chipset automatically compensates for various cable lengths and types. Adaptive equalization is critical to the success of long distance cable driving. The adaptive nature of the equalizer ensures minimal added signal noise and jitter caused during the amplification of high-frequency energy. An evaluation reference design, number DriveCable02EVK, is available for quick evaluation and design implementation.

#### Conclusion

Today many signal paths contain separate signal acquisition and processing modules. As sampling speeds increase, it becomes harder to transfer the signal-path data between modules due to the lossy effects of the transmission medium. In fact, even if the transmission distance is constant, losses and therefore jitter increases as signaling speed increases. Luckily, it is easy to estimate and overcome these loss effects through the use of signal conditioners with pre-emphasis and equalization. ■

### **Design Tools**

### WEBENCH® Signal Path Designer® Tools

Design, simulate, and optimize amplifier circuits in this FREE online design and prototyping environment allowing you to:

- Synthesize an anti-alias filter

- Select the best amplifier/ADC combo for your system specs

- Make trade-offs based on SNR, SFDR, supply voltage

- Simulate real-world operating conditions using SPICE

- Receive samples in 24 hours

webench.national.com

### **WaveVision 4.1 Evaluation Board**

Test and evaluate A/D converters with National's easy-to use WaveVision 4.1 evaluation board. Each evaluation board comes complete with USB cable and support software.

#### Features and benefits:

- Plug-n-play ADC evaluation board

- USB 2.0 interface to PC

- PC-based data capture

- Easy data capture and evaluation

- Highlighted harmonic and SFDR frequencies

- Easy waveform examination

- Produces and displays FFT plots

- Dynamic performance parameter readout with FFT

- Produces and displays histograms

#### **National Semiconductor**

2900 Semiconductor Drive Santa Clara, CA 95051 1 800 272 9959

Mailing address: PO Box 58090 Santa Clara, CA 95052

Visit our website at: signalpath.national.com

For more information, send email to: new.feedback@nsc.com

### Don't miss a single issue!

Subscribe now to receive email alerts when new issues of Signal Path Designer<sup>®</sup> are available:

#### signalpath.national.com/designer

Also, be sure to check out our Power Designer! View online today at: power.national.com/designer

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

|                       | Products               |                                 | Applications                  |                                   |

|-----------------------|------------------------|---------------------------------|-------------------------------|-----------------------------------|

|                       | Audio                  | www.ti.com/audio                | Communications and Telecom    | www.ti.com/communications         |

|                       | Amplifiers             | amplifier.ti.com                | Computers and Peripherals     | www.ti.com/computers              |

|                       | Data Converters        | dataconverter.ti.com            | Consumer Electronics          | www.ti.com/consumer-apps          |

|                       | DLP® Products          | www.dlp.com                     | Energy and Lighting           | www.ti.com/energy                 |

|                       | DSP                    | dsp.ti.com                      | Industrial                    | www.ti.com/industrial             |

|                       | Clocks and Timers      | www.ti.com/clocks               | Medical                       | www.ti.com/medical                |

|                       | Interface              | interface.ti.com                | Security                      | www.ti.com/security               |

|                       | Logic                  | logic.ti.com                    | Space, Avionics and Defense   | www.ti.com/space-avionics-defense |

|                       | Power Mgmt             | power.ti.com                    | Transportation and Automotive | www.ti.com/automotive             |

|                       | Microcontrollers       | microcontroller.ti.com          | Video and Imaging             | www.ti.com/video                  |

|                       | RFID                   | www.ti-rfid.com                 |                               |                                   |

|                       | OMAP Mobile Processors | www.ti.com/omap                 |                               |                                   |

| Wireless Connectivity |                        | www.ti.com/wirelessconnectivity |                               |                                   |

|                       |                        |                                 | u Hama Dawa                   | a O a Al a a m                    |

**TI E2E Community Home Page**

e2e.ti.com

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2011, Texas Instruments Incorporated