# Supporting Functional Safety Using SafeTI<sup>™</sup> Diagnostic Library

R. Manoj, Girish Gajwani

#### ABSTRACT

The application report illustrates the use of the safety library towards enabling diagnostics or tests on diagnostics applicable to the Hercules<sup>™</sup> safety microcontrollers and TPS65381 Power Management Integrated Chip (PMIC).

#### Contents

| 1      | Introdu | iction                                                                                       | 2  |

|--------|---------|----------------------------------------------------------------------------------------------|----|

| 2      | Suppor  | rting Functional Safety – Hercules MCU and TPS65381-PMIC Using the SafeTI Diagnostic Library | 3  |

| 3      | Safety  | Measures for PESSRAL                                                                         | 7  |

| Append | A xib   | Introduction to Elevator Control System                                                      | 14 |

#### List of Figures

| 1 | Software Stack With SafeTI Diagnostic Library                                                                                                                        | 3  |

|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2 | The Hercules Safety MCU Architecture Implements Hardware-Based Safety Features to Create a "Safe Island" From Which Faults in the Rest of the System Can be Detected | 4  |

| 3 | Interfacing of the TPS65381 Device With Hercules Microcontroller                                                                                                     | 5  |

| 4 | Simplified Elevator Control System                                                                                                                                   | 15 |

#### List of Tables

|   |                                        | _  |

|---|----------------------------------------|----|

|   | Acronyms Used in This Document         |    |

| 2 | Safety Measures for PESSRAL            | 7  |

| 3 | TPS65381 External Watchdog Support API | 12 |

| 4 | BIST Support API                       | 12 |

| 5 | CRC Support API                        | 12 |

| 6 | NRES Error Monitoring API              | 12 |

|   | MUX Diagnostics API                    |    |

|   |                                        |    |

SafeTI, Hercules are trademarks of Texas Instruments. Cortex is a registered trademark of ARM Limited. All other trademarks are the property of their respective owners.

#### 1 Introduction

Functional safety is part of the overall system or equipment operating in response to its inputs in a predictable manner from a safety perspective. The objective of functional safety is to minimize the likelihood of unacceptable risk of physical injury or damage to health of people, directly or indirectly. Different industries have their own specific standards that they can impose from a customer requirement or mandatory legislative perspective on safety critical systems(a system whose malfunction can result in death or serious injury to people) so as to reduce safety critical risk.

As more and more control systems are based on programmable electronic systems (PES), it is critical to meet functional safety requirements and expectations for PES.

Selection of the right mix of components (such as microcontrollers, power management IC for the design and development of PES) is a very important. A right choice can reduce the efforts needed to meet the functional safety targets.

The TI Hercules Safety MCU family is a high performance MCU family targeting general purpose functional safety applications. Hercules MCUs are also an integral part of many SafeTI functional safety design packages (www.ti.com/safeti). SafeTI design packages help enable compliance with safety standards by including semiconductor components, safety documents, tools and software, complementary embedded processing and analog components, quality manufacturing process and a safety development process. System level management of the external error response can often be simplified through the use of a TI TPS6538x power supply and effective safety companion devices developed for use with the Hercules family.

#### 1.1 Acronyms and Descriptions

| Acronym | Description                                                              |  |  |  |

|---------|--------------------------------------------------------------------------|--|--|--|

| AMUX    | Analog MUX                                                               |  |  |  |

| API     | Application programmable interface                                       |  |  |  |

| CRC     | Cyclic redundancy check                                                  |  |  |  |

| DWD     | Digital watchdog                                                         |  |  |  |

| DMUX    | Digital MUX                                                              |  |  |  |

| DWWD    | Digital windowed watchdog                                                |  |  |  |

| ESM     | Error signaling module                                                   |  |  |  |

| LBIST   | Logic built-in self test                                                 |  |  |  |

| PBIST   | Programable built-in self test                                           |  |  |  |

| PMIC    | Power management integrated circuit (IC)                                 |  |  |  |

| PES     | Programmable electronic systems                                          |  |  |  |

| PESSRAL | Programmable electronic systems in safety-related applications for Lifts |  |  |  |

| SECDED  | Single error correction and double error detection                       |  |  |  |

| WDTI    | Watchdog trigger input                                                   |  |  |  |

| FEE     | Flash emulate EEPROM                                                     |  |  |  |

| ABIST   | Analog Built In Self Test                                                |  |  |  |

| PLL     | Phase locked loop                                                        |  |  |  |

#### Table 1. Acronyms Used in This Document

# 2 Supporting Functional Safety – Hercules MCU and TPS65381-PMIC Using the SafeTI Diagnostic Library

This application report shows a possible mapping of the Hercules Safety MCU diagnostic features to the SafeTI diagnostic Library API, which can be used in an application to do the diagnostics or to provide the test of the diagnostic feature itself.

This application report is an example only. The designs shown are not warranted to comply with any specific functional safety standard, product safety standard, or security standard, a responsibility typically belonging to the OEM. This document cannot be used as a reference design ISO 22201:2009 PERSSRAL.

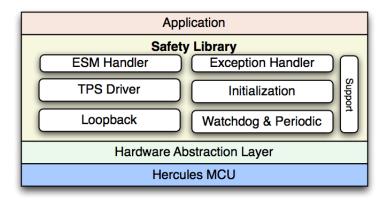

The Hercules MCU together with TPS65381 PMIC offer safety features in hardware [3] and the software stack(as shown in Figure 1), provides the software API that can efficiently be used in the control systems for detection and management of detected faults in the Hercules Safety MCU. As an example, the Elevator Control System found in Appendix A illustrates the various components in a real work use.

Figure 1. Software Stack With SafeTI Diagnostic Library

# 2.1 TI Hercules MCU Safety Overview

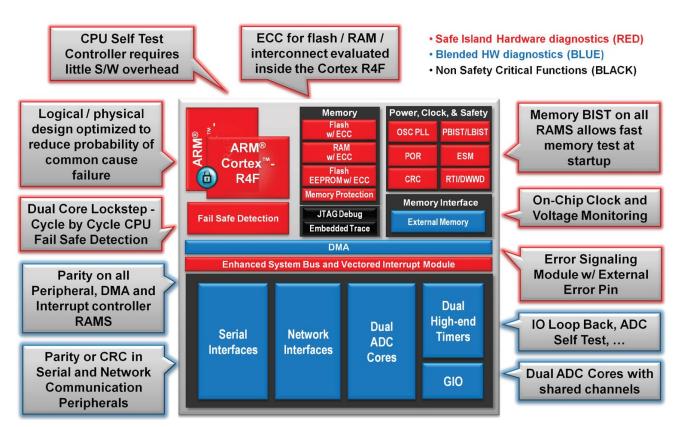

The Hercules MCU family of processors share a common safety architecture concept called a "Safe Island" philosophy. The basic concept involves a balance between application of hardware diagnostics and software diagnostics to manage functional safety, while balancing cost considerations. In the safe island approach, a core set of elements are allocated, continuously operating hardware safety mechanisms. This core set of elements, including power and clock, reset, CPU, Flash memory, SRAM and associated interconnect, is needed to help assure any functionally correct execution of software. Once correct operation of these elements is confirmed, software execution can begin on these elements in order to provide software-based diagnostics on other device elements, such as peripherals. The Hercules architecture also provides various safety mechanisms and technical recommendations for the use of safety mechanisms.

All microcontrollers of the Hercules family have an associated Safety Manual [3] that provides information needed to assist in the creation of a safety critical system. This document contains:

- An overview of the superset product architecture

- An overview of the development process utilized to reduce systematic failures

- An overview of the safety architecture for management of random failures

- The details of architecture partitions, implemented safety mechanisms

Figure 2. The Hercules Safety MCU Architecture Implements Hardware-Based Safety Features to Create a "Safe Island" From Which Faults in the Rest of the System Can be Detected

Supporting Functional Safety – Hercules MCU and TPS65381-PMIC Using the SafeTI Diagnostic Library

# 2.2 TPS65381 Power Management IC Overview

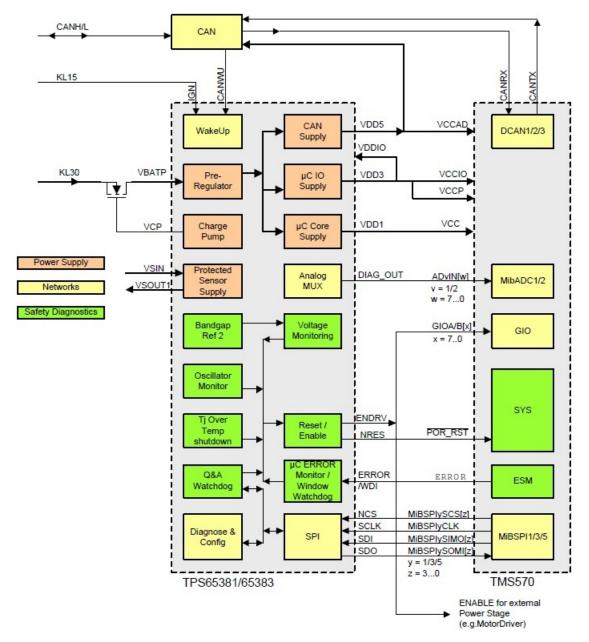

The TPS65381 [4] is a companion SafeTI chip for the Hercules microcontroller family, that includes certain functional-safety related features. It is a multi-rail power supply designed to supply microcontrollers in safety-critical applications, such as those found in automotive.

The device monitors undervoltage and overvoltage on all regulator outputs, battery voltage, and internal supply rails. A second band-gap reference, independent from the main band-gap reference, monitors for under and overvoltage, to avoid any drifts in the main band-gap reference being undetected. In addition, the device implements regulator current limits and temperature protections. The TPS6538x functional safety architecture features a question-answer watchdog, MCU error-signal monitor, check-mode for MCU error-signal monitor, clock monitoring on internal oscillators, self-check on clock monitor, CRC on non-volatile memory, and a reset circuit for the MCU. A built-in self-test (BIST) allows for monitoring the device functionality at start-up. Figure 3 shows an interfacing of TPS65381 with the Hercules microcontroller in an automotive use case.

Supporting Functional Safety – Hercules MCU and TPS65381-PMIC Using the SafeTI Diagnostic Library

www.ti.com

### 2.3 SafeTI Diagnostic Library and Compliance Support Package (CSP)

The SafeTI Diagnostic Library serves as the software implementation of the safety manual for the microcontroller. It provides interfaces to several safety mechanisms that are described in the safety manual. Based on the final system requirements, the system integrator can use these APIs to incorporate appropriate mechanisms in the final system to meet safety requirements [7].

The Diagnostic library is a collection of functions with access to safety functions and response handlers for various safety mechanisms. The Diagnostic library runs in the context of the caller's protection environment and responses are handled in the context of interrupt or exception. The Diagnostic library also provides the TPS6538x driver package for the Hercules Safety MCU, which provides driver level API to interface the Hercules MCU with TPS6538x power supply chip and make use of the various TPS6538x device features such as voltage monitoring, watchdog monitoring, error monitoring. Table 3 through Table 7 show the example API provided the TPS6538x driver package.

The SafeTI Diagnostic library also has a compliance support package (CSP) release. This release provides the necessary documentation and reports to assist customers using the SafeTI Hercules Diagnostic Library to help meet safety requirements.

### 3 Safety Measures for PESSRAL

Table 2 is partial illustration only; use this as a guideline when you are developing your system and is not intended to be exhaustive or complete in nature.

| Component and Functional<br>Safety Requirement                                                                                                                                                                | Measures to be Taken                                                                                                                                                                                                                           | Mapping to Hercules<br>Safety Manual [1] | Mapping to Hercules<br>SafeTI Diagnostic<br>Library for test of<br>the diagnostic | API Usage                                                                                                                                                                                                                                               | Comments                                                                                                                                                                                                                                                            |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|-----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Structure: Any system can be<br>divided into three subsystems:<br>an input subsystem, Logic<br>subsystem, and output<br>subsystem. The structure<br>should be such that it can<br>capture any random failure. | Single channel implementation<br>supporting self-test and<br>monitoring using the self-test<br>controller. The other way to<br>satisfy this feature is to use<br>two channels of subsystems,<br>which may not be a cost<br>effective solution. | CPU2A/B                                  | SL_Selftest_STC                                                                   | <ul> <li>This Diagnostic Library API can be used to:</li> <li>Run CPU LBIST</li> <li>Verify STC logic by running self-test diagnostics</li> <li>Fault injection for the STC</li> </ul>                                                                  | The CPU self-test controller (STC) is used to test the ARM-CPU core using the deterministic logic built-in self-test (LBIST) controller as the test engine.                                                                                                         |

| Processing Units: Processing<br>units form the core of the Logic<br>subsystem, and any failure in<br>the processing unit can lead to<br>incorrect results, Such a failure<br>must be detectable.              | CPU compare module<br>(CCMR4) for the lockstep<br>architecture in Hercules.                                                                                                                                                                    | CPU1                                     | SL_SelfTest_<br>CCMR4F                                                            | <ul> <li>This SafeTI Diagnostic Library API can be used to:</li> <li>Verify CCM logic by running self-test diagnostics</li> <li>Fault injection on: <ul> <li>CCM compare error output signal</li> <li>CCM self-test error signal</li> </ul> </li> </ul> | Hercules architecture implements two instances<br>of the Cortex®-R4F CPU that are running in lock<br>step to detect faults that may result in unsafe<br>operating conditions. The CCM-R4F detects<br>faults and signals them to an error signaling<br>module (ESM). |

| Invariant memories ranges:<br>Invariant memories (like Flash)<br>store important information<br>(like Instruction Opcode for<br>logic execution). A bit error can<br>lead to severe system fault.             | e Flash) Double Error Detection<br>ation (SECDED) for L2FMC and<br>e for TCRAM, signature verification<br>error can on any memory subsystem<br>using cyclic redundancy check<br>(CRC)<br>b bit<br>able and<br>B RAM,<br>on, can<br>e<br>shange | FLA1                                     | SL_SelfTest_Flash                                                                 | Capability to run:<br>• Single bit error correction self test<br>• Double bit error detection self test<br>• Fault injection using 2-bit error                                                                                                          | The Flash memory can be protected by SECDED. The main program memory is protected by the SECDED circuit inside of the Cortex R4 CPU                                                                                                                                 |

| Any bit flip in the invariant<br>memory must be detectable<br>and correctable. Single bit                                                                                                                     |                                                                                                                                                                                                                                                | FLA5A/B                                  | SL_CRC_Calculate                                                                  | Signature verification of the memory contents.                                                                                                                                                                                                          | The CRC controller is a module that is used to perform CRC to verify the integrity of the memory system.                                                                                                                                                            |

| errors must be correctable and<br>2-bit failures must be<br>detectable. Sometimes RAM,<br>based on the application, can<br>store static tables.Once<br>initialized they do not change                         |                                                                                                                                                                                                                                                | RAM1                                     | SL_SelfTest_SRAM                                                                  | Capability to run:<br>• Single bit error correction self test<br>• Double bit error detection self- test<br>• Fault injection using 2-bit error                                                                                                         | TCRAM interface module features dedicated for SECDED support.                                                                                                                                                                                                       |

| so it can be considered as invariant memory.                                                                                                                                                                  |                                                                                                                                                                                                                                                | RAM9                                     | SL_CRC_Calculate                                                                  | Signature verification of the memory contents.                                                                                                                                                                                                          | The CRC controller is a module that is used to perform CRC to verify the integrity of memory system.                                                                                                                                                                |

#### Table 2. Safety Measures for PESSRAL

Safety Measures for PESSRAL

www.ti.com

| Component and Functional<br>Safety Requirement                                                                                                                                              | Measures to be Taken                                                                          | Mapping to Hercules<br>Safety Manual [1] | Mapping to Hercules<br>SafeTI Diagnostic<br>Library for test of<br>the diagnostic | API Usage                                                                                                                                                                                                         | Comments                                                                                                                                                                                                                                                          |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|------------------------------------------|-----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Variable memory ranges: RAM<br>can be considered as one of<br>the variable memories. It may<br>store importation data<br>structures of system like task<br>control blocks (TCB) of an       | SECDED for L2FMC and<br>TCRAM, signature verification<br>on any memory subsystem<br>using CRC | FEE1                                     | SL_SelfTest_FEE                                                                   | Capability to run:<br>• Single bit error correction self test<br>• Double bit error detection self test<br>• Fault injection using 2-bit error                                                                    | The FEE memory can be protected by SECDED.<br>The main program memory is protected by the<br>SECDED circuit inside of the Cortex-R4 CPU.                                                                                                                          |

| operating system. A bit error<br>can lead to severe system<br>fault. Any bit flip in the variant                                                                                            |                                                                                               | FEE2A/B                                  | SL_CRC_Calculate                                                                  | Signature verification of the memory contents.                                                                                                                                                                    | The CRC controller is a module that is used to perform CRC to verify the integrity of memory system.                                                                                                                                                              |

| memory must be detectable<br>and correctable. Single bit<br>errors must be correctable and<br>ODD 2-bit failures must be<br>detectable.                                                     |                                                                                               | RAM1                                     | SL_SelfTest_SRAM                                                                  | Capability to run: <ul> <li>Single bit error correction self test</li> <li>Double bit error detection self test</li> <li>Fault injection using 2-bit error</li> </ul>                                             | TCRAM interface module features dedicated for SECDED support.                                                                                                                                                                                                     |

|                                                                                                                                                                                             |                                                                                               | RAM9                                     | SL_CRC_Calculate                                                                  | Signature verification of the memory contents                                                                                                                                                                     | The CRC controller is a module that is used to perform CRC to verify the integrity of the memory system.                                                                                                                                                          |

|                                                                                                                                                                                             |                                                                                               | RAM7A/B                                  | SL_SelfTest_PBIST                                                                 | Executes PBIST tests on RAM groups with different algorithms                                                                                                                                                      | The programmable built-in self-test (PBIST)<br>controller architecture provides a run-time-<br>programmable memory BIST engine for varying<br>levels of coverage across many embedded<br>memory instances.                                                        |

| Clock: Many system<br>peripherals like ADC, SPI, and<br>so forth are driven by                                                                                                              | Low-power oscillator clock detect                                                             | CLK1                                     | ESM_Application_<br>Callback                                                      | • ESM_Application_Callback of the diagnostic<br>library captures ESM errors related to LPOCLK the<br>clock monitor esm error.                                                                                     | The low-power oscillator clock detector<br>(LPOCLKDET) is a safety diagnostic that can be<br>used to detect failure of the primary clock                                                                                                                          |

| peripheral clocks that are<br>generated using a main<br>system clock. Failure in clock<br>generation and incorrect clock<br>variations can lead to system<br>failure and must be detectable | PLL Slip Detector                                                                             | CLK2                                     | ESM_Application_<br>Callback                                                      | • ESM_Application_Callback of the diagnostic<br>library captures ESM errors related to PLL Slip<br>error .                                                                                                        | The PLL logic includes an embedded diagnostic that can detect a slip of the PLL output clock. Error response and indication is dependent on the programming of the PLL control registers that are located in the system module.                                   |

|                                                                                                                                                                                             | Dual Clock Comparator CLK                                                                     | CLK3                                     | ESM_Application_<br>Callback                                                      | • ESM_Application_Callback of the diagnostic<br>library captures ESM errors related to clock<br>comparison.                                                                                                       | The DCC can be used to detect incorrect frequencies and drift between clock sources.                                                                                                                                                                              |

|                                                                                                                                                                                             |                                                                                               | CLK5A/B                                  | N/A                                                                               | N/A                                                                                                                                                                                                               | The Hercules platform supports the use of an internal watchdog that has a separate time base. It has two modes of operation: digital watchdog (DWD) and digital windowed watchdog (DWWD). HALCoGen provides API for configuration and usage of internal watchdogs |

|                                                                                                                                                                                             | External Watchdog                                                                             | CLK5C                                    | Watchdog Support<br>API for External<br>Watchdog (see<br>Table 3)                 | <ul> <li>The API supports:</li> <li>Handling of the complete watchdog configuration</li> <li>Sending of the watchdog responses to the TPS65381 device</li> <li>Fault Injection by sending a bad answer</li> </ul> | TPS65381 device include a closed-loop digital watchdog.                                                                                                                                                                                                           |

# Table 2. Safety Measures for PESSRAL (continued)

| Component and Functional<br>Safety Requirement                                                                                             | Measures to be Taken                            | Mapping to Hercules<br>Safety Manual [1]                                | Mapping to Hercules<br>SafeTI Diagnostic<br>Library for test of<br>the diagnostic | API Usage                                                                                                                                                                                                                                                                                                                                                                   | Comments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|--------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|-------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Program sequence: Incorrect<br>execution flow of a program or<br>the wrong program sequence<br>must be detectable                          | Watchdog with separate time base                | CLK5B                                                                   | N/A                                                                               | N/A                                                                                                                                                                                                                                                                                                                                                                         | The Hercules platform supports the use of an internal watchdog that has a separate time base. It has two modes of operation: digital watchdog (DWD) and digital windowed watchdog (DWWD). HALCoGen provides API for configuration and usage of internal watchdogs                                                                                                                                                                                                                                                                                                              |

|                                                                                                                                            | External Watchdog                               | CLK5C                                                                   | Watchdog support<br>API for external<br>watchdog (see<br>Table 3)                 | <ul> <li>The API supports:</li> <li>Handling of the complete watchdog configuration</li> <li>Sending of the watchdog responses to the TPS65381 device</li> <li>Injection of the watchdog (by sending of a bad answer)<br/>For meeting this requirement it may be best to use the watchdog Q&amp;A configuration.</li> </ul>                                                 | <ul> <li>TPS65381 device include a closed-loop digital watchdog. This watchdog requires that specific trigger messages be passed between the MCU and the TPS65381 device at specific timing intervals in order to enable operation of the safing path or external power stages through the ENDRV pin. The TPS65381-Q1 device has two different watchdog timer configurations for the external MCU to send the watchdog trigger:</li> <li>Watchdog trigger input configuration (WDTI configuration).</li> <li>Question-answer configuration (Q&amp;A configuration).</li> </ul> |

| Input/output and<br>communication links: Failure in<br>the input output and<br>communication links must be<br>detectable as it can lead to | Information redundancy techniques               | GIO2, PWM2, MSP3,<br>ADC3, HET2, SPI3,<br>IC2, SCI2,<br>LIN2,CAN2, FRY4 | N/A                                                                               | N/A                                                                                                                                                                                                                                                                                                                                                                         | Information redundancy techniques can be<br>applied via software as an additional runtime<br>diagnostic on GIO function.<br>HALCoGen provides supporting API to<br>implement this diagnostic.                                                                                                                                                                                                                                                                                                                                                                                  |

| failure in end systems                                                                                                                     | Boot time input self test                       | ADC1                                                                    | SL_SelfTest_ADC                                                                   | Capability to run     _ Self test on given ADC input PIN                                                                                                                                                                                                                                                                                                                    | The Hercules MibADC module implements an<br>input self-test engine that can detect short to<br>ADREFLO,ADREFHI or open input.                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                            | Boot time and periodic<br>converter calibration | ADC2A/B                                                                 | SL_adcCalibration                                                                 | <ul> <li>Calibration API can be used for:</li> <li>Calibration that improves converter accuracy</li> <li>Software comparison of the conversion of known reference values from the calibration logic provides a diagnostic on the converter functionality.</li> <li>Repeated execution of the calibration routine can be used to detect drift during application.</li> </ul> | ADC includes specific hardware that allows<br>application program to calibrate the ADC. The<br>calibration can be performed periodically and the<br>calibrated offset can be stored so as to analyze<br>if there is serious deviation in the calibrated<br>offset.                                                                                                                                                                                                                                                                                                             |

|                                                                                                                                            | Boot time PBIST check of<br>MibADC SRAM         | ADC5A/B                                                                 | SL_SelfTest_PBIST                                                                 | Execute PBIST tests on RAM groups with different algorithms                                                                                                                                                                                                                                                                                                                 | The PBIST controller architecture provides a<br>run-time-programmable memory BIST engine for<br>varying levels of coverage across many<br>embedded memory instances.                                                                                                                                                                                                                                                                                                                                                                                                           |

Table 2. Safety Measures for PESSRAL (continued)

| Component and Functional Safety Requirement                                                                                                                                                                                                         | Measures to be Taken                                                                                           | Mapping to Hercules<br>Safety Manual [1] | Mapping to Hercules<br>SafeTI Diagnostic<br>Library for test of<br>the diagnostic | API Usage                                                                                                                                                                                                                                                                                   | Comments                                                                                                                                                                                                                                                                                                                         |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|------------------------------------------|-----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TPS65381 Error Monitoring:<br>TPS65381 device has the<br>capability to monitor error pin<br>of an external MCU and take<br>appropriate actions. Error<br>monitoring failure can lead to<br>incorrect operation of the end<br>system                 | Self test on TPS error monitoring                                                                              | N/A                                      | TPS_TestError<br>PinMonitoring                                                    | The API creates an error in Hercules MCU and verifies that the TPS error pin monitoring is working.                                                                                                                                                                                         | TPS65381 can be configured to monitor nerror<br>pin output on the MCU.                                                                                                                                                                                                                                                           |

| TPS65381 analog and logical<br>functional units: Any failure in<br>analog and digital functional<br>units must be detectable                                                                                                                        | Self test on the analog and logical functional units                                                           | N/A                                      | BIST support API<br>(see Table 4)                                                 | API enables the configuration and usage of the built in self tests on logical and analog functions in TPS65381                                                                                                                                                                              | TPS65381 has several analog and logical<br>functional units correct functioning of these units<br>is necessary as an important aspect of the<br>safety of the end system.                                                                                                                                                        |

| TPS65381 configuration<br>registers: Configuration<br>registers in the TPS65381<br>device have to be protected<br>appropriately. A runaway code<br>can overwrite the TPS65381<br>configuration registers resulting<br>in failure of the end system. | Usage of the CRC diagnostic<br>on configuration registers is<br>recommended                                    | N/A                                      | CRC Support API<br>(seeTable 5)                                                   | <ul> <li>Provides API for:</li> <li>EEPROM(used for storing analog trim values) CRC check.</li> <li>Calculation of the predetermined golden CRC value.</li> <li>Getting CRC error status</li> <li>Injecting fault in CRC golden value which results in failure in the CRC check.</li> </ul> | The CRC controller is a diagnostic module that<br>performs CRC to verify the integrity of the SPI-<br>mapped register space. The responsibility of the<br>CRC controller is to calculate the signature for a<br>set of data and then compare the calculated<br>signature value against a predetermined good-<br>signature value. |

|                                                                                                                                                                                                                                                     | Usage of write protection on<br>configuration registers is<br>recommended.                                     | N/A                                      | TPS_Protect<br>Configuration<br>Registers                                         | The API can be used to enable or disable write<br>protection on the configuration registers                                                                                                                                                                                                 | TPS65381 device supports SW_LOCK<br>command that can be used to enable the write-<br>access lock. A register cannot be written after<br>write-access lock protection is set. The lock is<br>cleared by software or by a power-on reset.                                                                                          |

|                                                                                                                                                                                                                                                     | Usage of register read back<br>and comparison is<br>recommended.                                               | N/A                                      | TPS_RegReadback<br>Compare                                                        | The API can be called periodically during the<br>operation of the system to check and verify that the<br>TPS65381 configuration has not unintentionally<br>changed.                                                                                                                         | Every time the TPS65381 driver changes, the configuration registers in the TPS65381 device update a data structure that stores the current configuration register settings. The readback compare reads the configuration register values (from the TPS65381 device) and compares them against the stored data structure.         |

| TPS65381 ENDRV pin Failure:<br>ENDRV pin of the TPS device<br>is the enable output signal for<br>peripherals such as Motor<br>drive IC. The failure in the<br>ENDRV pin operation can<br>result in incorrect operation of<br>the end system.        | Periodic read back of the<br>ENDRV pin failure information<br>for taking corrective actions is<br>recommended. | N/A                                      | TPS_GetENDRV_<br>ErrorStatus                                                      | The API returns error status information if any in the ENDRV pin operation.                                                                                                                                                                                                                 | The ENDRV pin features a read-back circuit to<br>compare the external ENDRV level with the<br>internally applied ENDRV level. This is to detect<br>any possible failures in the ENDRV pullup or<br>pulldown components. A failure can be detected<br>by the MCU through the SPI register<br>SAFETY_STAT_4, bit 1.                |

# Table 2. Safety Measures for PESSRAL (continued)

| Component and Functional Safety Requirement                                                                                                                                                                                                                                                                                                                   | Measures to be Taken                                                                                                                                                                                                                    | Mapping to Hercules<br>Safety Manual [1] | Mapping to Hercules<br>SafeTI Diagnostic<br>Library for test of<br>the diagnostic | API Usage                                                                                                                                        | Comments                                                                                                                                                                                           |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|-----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TPS65381 NRES pin failure:<br>Cold-reset (NPOR_RST)<br>output signal for µC. In some<br>systems, the NRES pin is<br>connected to the NPOR_RST<br>pin of the MCU. The TPS<br>resets the MCU in case of<br>severe errors by active low<br>signal on the NRES pin. The<br>incorrect operation of the<br>NRES pin leads to improper<br>functioning of the system. | Enable NRES monitoring and<br>do a periodic check of NRES<br>Error.(When the NRES_ERR<br>flag is set, there is a difference<br>in the external NRES pin level<br>and configured NRES level<br>from the TPS65381 device)                 | N/A                                      | NRES Error<br>Monitoring API (see<br>Table 6)                                     | Capability to configure and use NRES pin error monitoring                                                                                        | The NRES pin features a readback of the external NRES level. The value can be read on the DIAG_OUT pin and in the SPI register SAFETY_STAT_3, bit 5.                                               |

| TPS65381 analog and digital<br>signals: Incorrect values on the<br>analog voltages and digital<br>signals in TPS device may<br>cause a failure in the end<br>system.                                                                                                                                                                                          | Analog and digital MUX<br>diagnostics must be used as a<br>periodic and boot-time safety<br>diagnostics. Redundant<br>monitoring of the safety critical<br>voltage and important digital<br>signals of TPS65381 device is<br>necessary. | N/A                                      | MUX Diagnostics API<br>(see Table 7)                                              | <ul> <li>Capability to:</li> <li>Enable or disable analog or digital signal on MUX_OUT pin.</li> <li>Check enable AMUX signal limits.</li> </ul> | TPS65381 device analog and digital MUX facilitates external pin interconnect tests by feeding back to the input pin state, internal module self-test status, or safety-critical comparator output. |

#### Safety Measures for PESSRAL

www.ti.com

# Table 3. TPS65381 External Watchdog Support API

| API                                | Description                                                                                                                                              |

|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| TPS_WatchdogInit                   | API to set up and initialize TPS watchdog                                                                                                                |

| TPS_SetWatchdogMode                | Set Watchdog configuration in either Q and A mode or in WDTI mode                                                                                        |

| TPS_ConfigureWatchdogWindows       | Configure watchdog windows                                                                                                                               |

| TPS_ConfigureWatchdogReset         | Enable or disable watchdog reset                                                                                                                         |

| TPS_UpdateActiveWDToken            | Update active Watchdog Token in the TPS device. The updated token is used to send appropriate watchdog answer to the TPS device.                         |

| TPS_SendWdgResponse                | The API is used for sending watchdog answer to the TPS device. The API sends the correct response to the TPS device based on the currently active token. |

| TPS_GetWatchdogFailureStatus       | The API provides the status of the watchdog failure status flag                                                                                          |

| TPS_ClearWatchdogFailureStatusFlag | The API clears the watchdog fail status bit in the register SAFETY_ERR_STAT TPS register                                                                 |

| TPS_GetWatchdogAnswerCount         | The API provides watchdog failure count information                                                                                                      |

| TPS_GetWatchdogErrorType           | The API provides failure status information of the watchdog                                                                                              |

| TPS_GetWatchdogFailCount           | The API provides watchdog failure count information                                                                                                      |

| TPS_WDSetTokenSeedValue            | Set Token Seed value for the watchdog                                                                                                                    |

| TPS_WDSetTokenFDBCKValue           | Set Token Feedback value for the watchdog                                                                                                                |

| TPS_FaultInjectWD                  | Inject fault in watchdog                                                                                                                                 |

## Table 4. BIST Support API

| API                        | Description                                                           |

|----------------------------|-----------------------------------------------------------------------|

| TPS_ConfigureBISTatStartup | The API enables and disables BIST at startup                          |

| TPS_StartBIST              | The API starts the built-in self-test ABIST/LBIST (manually starting) |

| TPS_GetBISTRunningStatus   | The API gets the built in self-test running status                    |

| TPS_GetABISTTestStatus     | The API gets the built in self-test running status                    |

| TPS_GetLBISTTestStatus     | The API gets the built in self-test running status                    |

# Table 5. CRC Support API

| API                                       | Description                                                                                                   |

|-------------------------------------------|---------------------------------------------------------------------------------------------------------------|

| TPS_ConfigureSafetyCheckControl           | Sets the safety check control register flags                                                                  |

| TPS_StartEECRCCheck                       | The API starts EEPROM CRC check                                                                               |

| TPS_InitializeDatastringforCRCCaclcuation | The API initializes the 64-bit data string for 8-bit CRC calculation                                          |

| TPS_CalculateCRC8                         | Calculate the CRC 8 value of the TPS65381 configuration registers (stored as 64-bit data)                     |

| TPS_GetCRCErrorStatus                     | The API is used to get the error status of Configuration register CRC calculation and EEPROM CRC calculation. |

| TPS_GetEECRCCheckRunningStatus            | The API gets the EE CRC check running status                                                                  |

| TPS_FaultInjectCRC                        | Inject CRC fault                                                                                              |

| TPS_UpdateRegisterSafetyCfgCRC            | Update SAFETY_CFG_CRC register                                                                                |

# Table 6. NRES Error Monitoring API

| API                         | Description                                                                    |

|-----------------------------|--------------------------------------------------------------------------------|

| TPS_ConfigureNRESMonitoring | Configure NRES pin monitoring                                                  |

| TPS_ConfigureNRESMonitoring | The API provides failure information of NRES pin (read back state of NRES PIN) |

# Table 7. MUX Diagnostics API

| API                              | Description                                                                               |

|----------------------------------|-------------------------------------------------------------------------------------------|

| TPS_EnableAMUXSignal             | Enable particular AMUX (analog signal to be enabled on the MUX output) signal             |

| TPS_DisableMUXDiagnostic         | Disable MUX diagnostics                                                                   |

| TPS_CheckEnabledAMUXSignalLimits | Check enabled AMUX signal limits (check to see if the analog signal is within the limits) |

| TPS_EnableDMUXSignal             | Enable particular DMUX signal                                                             |

# References

- 1. TMS570LS12x/11x 16/32-Bit RISC Flash Microcontroller Technical Reference Manual (SPNU515)

- 2. RM46x 16/32-Bit RISC Flash Microcontroller Technical Reference Manual (SPNU514)

- 3. Safety Manual for RM46x Hercules<sup>™</sup> ARM<sup>®</sup>- Based Safety Critical Microcontrollers User's Guide (<u>SPNU551</u>)

- 4. TPS65381-Q1 Multi-Rail Power Supply for Microcontrollers in Safety Applications Data Manual (<u>SLVSBC4</u>)

- 5. <u>ISO 22201:2009</u> Design and development of programmable electronic systems in safety-related applications for lifts

- 6. ISO 26262-1:2011 Road vehicles -- Functional safety

- 7. <u>SafeTI Diagnostic Library</u> including Hercules Safety MCU Diagnostic Library and TPS65381 PMIC Driver

# Introduction to Elevator Control System

### A.1 Elevator Control System

#### CAUTION

Appendix A provides a high level, simplified illustration of a typical elevator control system. It is NOT intended to be complete, nor reflect customer-specific application needs or mandatory legislative compliance requirements that might apply to specific installation, a responsibility of the OEM and/or system integrator.

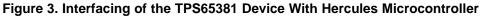

An elevator control system is responsible for coordinating all aspects of elevator service such as travel speed, accelerating, decelerating, door opening speed, leveling and hall lantern signals. It accepts inputs (button signals) and produces outputs (elevator cars moving, doors opening, and so forth).

#### A.1.1 Elevator Control System Components

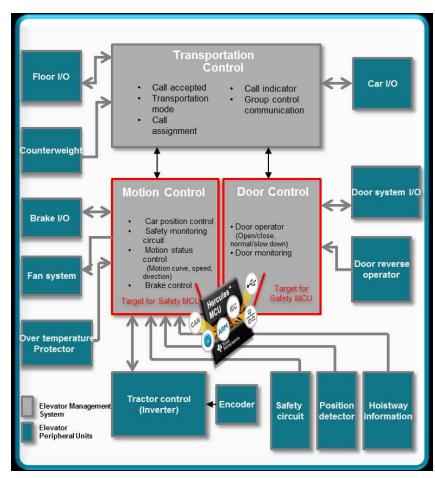

The elevator as a control system has a number of components (as shown in Figure 4). These can basically be divided into the following:

- Inputs

- Outputs

- Controllers

Inputs that include:

- Sensors (magnetic, infrared, and so forth)

- Buttons (hall buttons, floor request buttons, and so forth)

- Key controls

- System controls

Outputs that include:

- Actuators (door opening device, electric motors, brakes)

- Bells (emergency bell, and so forth)

- Displays (load bell, and so forth)

Controllers in elevators enable operations such as command control, visual monitoring, and so forth, which ensures that the elevators are functioning efficiently. Different types of controllers are available:

- Relay-based controllers

- PLC controller (uses microcontrollers)

Figure 4. Simplified Elevator Control System

# IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022, Texas Instruments Incorporated