# TMS320C6472/TMS320TCI6486 Throughput

Brighton Feng, Tom Johnson, Yanmin Wu

Digital Signal Processing Solutions

### **ABSTRACT**

The TMS320C6472/TMS320TCI6486 has six C64x+ Megamodule cores that run at 500 MHz, 625 MHz, or 700 MHz. This document has been written based on the performance of the C6472/TCI6486 device running at 500 MHz and 625 MHz. Each megamodule has 32KB of L1D SRAM, 32KB of L1P SRAM, and 608KB of LL2 SRAM and all six cores share 768KB of SL2 SRAM. A 32-bit 533-MHz DDR2 SDRAM interface is provided on the DSP to support up to 512MB of external memory. The C6472/TCI6486 also has an Enhanced DMA engine and a high-bandwidth DMA switch fabric capable of connecting all of these entities.

Memory access performance is very critical for software running on the DSP. On the C6472/TCl6486 DSP, all memories can be accessed by DSP cores and by multiple DMA masters. Each DSP core is capable of performing up to 128 bits of load/store operations per cycle. When accessing L1D SRAM, the DSP core can access the memory at up to 8 GBps at a 500-MHz core clock frequency, or 10 GBps at a 625-MHz core clock frequency.

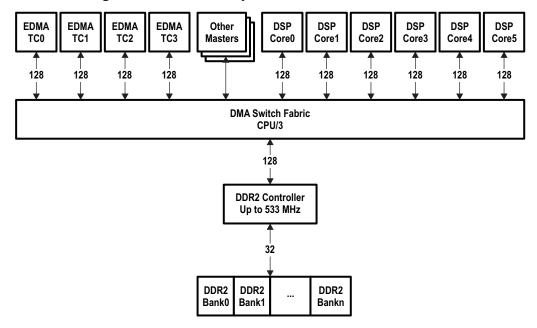

The DMA switch fabric is a 128-bit bus structure operating at the clock rate of CPU/3. It can sustain data throughput up to 2.666 GBps at a 500 MHz core clock rate or 3.333 GBps at a 625-MHz core clock rate per connection. Since this DMA switch fabric supports multiple, concurrent connections, each connection may achieve this theoretical limit as long as there are no conflicts.. The DMA switch fabric interconnects the C64x+ megamodule cores (including their local memories), external DDR2 memory, EDMA controllers and peripheral interfaces.

The C6472/TCl6486 device contains high-bandwidth peripheral interfaces such as Gigabit Ethernet, Serial RapidIO®, TSIP, UTOPIA, and DDR2. Sustaining high throughput through these interfaces is very critical to meeting system and application requirements.

This document provides designers a basis for estimating memory access performance based on throughput measurements under various operating conditions. Some factors affecting memory access performance are discussed. It also addresses throughput to/from the interfaces to memories of the C6472/TCI6486 device. This can be used to estimate transport performance of the C6472/TCI6486 device to facilitate system design.

For a detailed functional description of the megamodule and peripherals, see the corresponding C6472/TCl6486 peripheral user's guides. For AC timings and register offsets, see the *TMS320TCl6486 Communications Infrastructure Digital Signal Processor* data manual (SPRS300) or the *TMS320C6472 Fixed-Point Digital Signal Processor* data manual (SPRS612).

## Contents

| 1                                                                                                      | Related Documentation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                  |

|--------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| 2                                                                                                      | Abbreviations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                  |

| 3                                                                                                      | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                  |

| 4                                                                                                      | TMS320C6472/TMS320TCI6486 Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                  |

| 5                                                                                                      | System Interconnect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                  |

|                                                                                                        | 5.1 Data Switch Fabric Connections                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                  |

| 6                                                                                                      | Transfer Throughput                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                  |

|                                                                                                        | 6.1 EDMA Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                  |

| _                                                                                                      | 6.2 EDMA Throughput                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                  |

| 7                                                                                                      | Peripheral Interface Throughput                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                  |

|                                                                                                        | 7.1 EMAC Throughput                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                  |

|                                                                                                        | 7.2 SRIO Throughput                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                  |

|                                                                                                        | 7.3 TSIP Throughput                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                  |

|                                                                                                        | 7.4 UTOPIA Throughput                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                  |

| 8                                                                                                      | CPU Memory Access Performance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                  |

| U                                                                                                      | 8.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                  |

|                                                                                                        | 8.2 DSP Core or EDMA and IDMA For Memory Copy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                  |

|                                                                                                        | 8.3 DSP Core Memory Access Performance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                  |

| 9                                                                                                      | EDMA Access Performance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                  |

|                                                                                                        | 9.1 DMA Transfer Overhead                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                  |

|                                                                                                        | 9.2 EDMA Performance of the Four Transfer Controllers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                  |

|                                                                                                        | 9.3 EDMA Bandwidth versus Transfer Flexibility                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 36                                                                               |

| 10                                                                                                     | Performance of Multiple Masters Sharing Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 39                                                                               |

|                                                                                                        | 10.1 Performance of Multiple Masters Sharing SL2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 40                                                                               |

|                                                                                                        | 10.2 Performance of Multiple Masters Sharing DDR2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 43                                                                               |

|                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                  |

|                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                  |

|                                                                                                        | List of Figures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                  |

| 1                                                                                                      | C6472/TCI6486 Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                  |

| 1 2                                                                                                    | C6472/TCI6486 Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Ş                                                                                |

|                                                                                                        | C6472/TCI6486 Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Ş                                                                                |

| 2                                                                                                      | C6472/TCI6486 Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 9<br>17                                                                          |

| 2                                                                                                      | C6472/TCI6486 Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 17<br>17                                                                         |

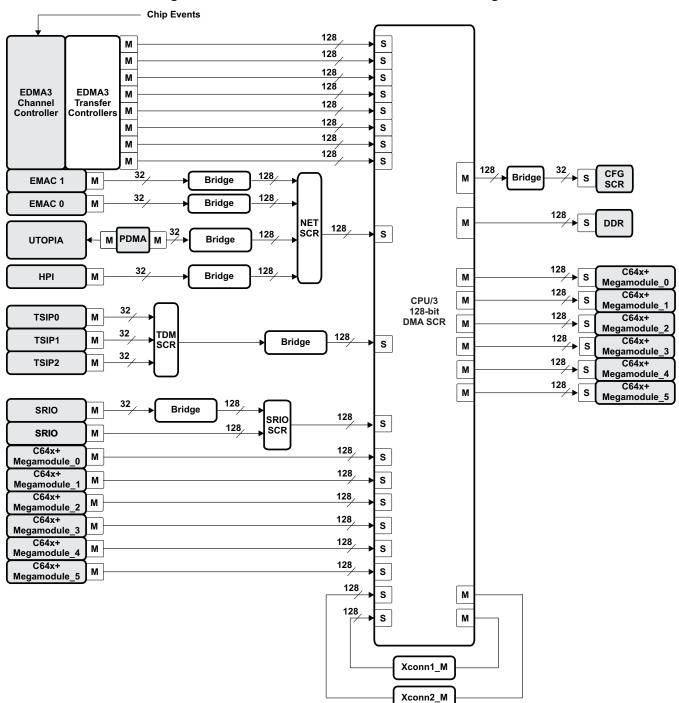

| 2<br>3<br>4                                                                                            | C6472/TCI6486 Block Diagram  DMA Switched Central Resource Block Diagram  SRIO Throughput - 3.125 Gbps  SRIO Throughput - 2.5 Gbps  SRIO Throughput - 1.25 Gbps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 17<br>17<br>18                                                                   |

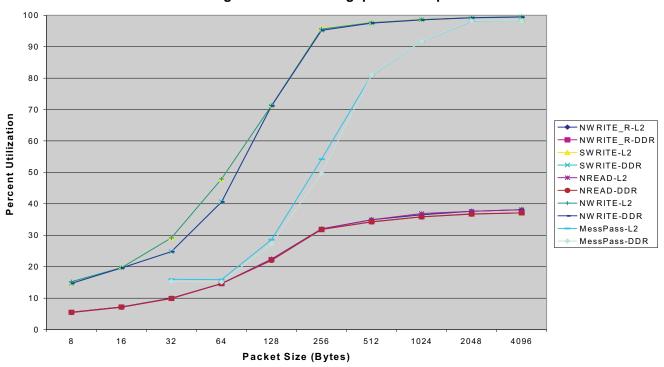

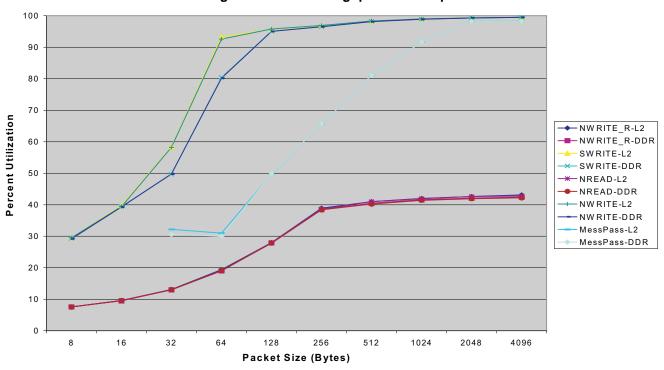

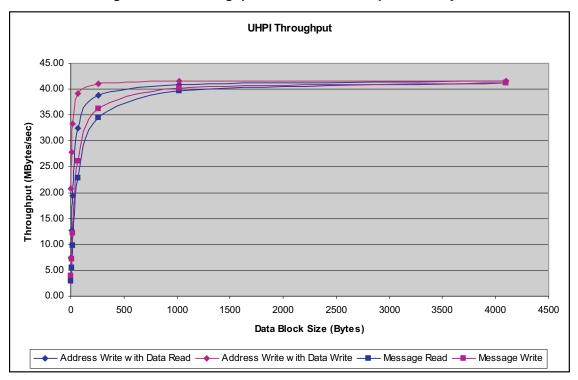

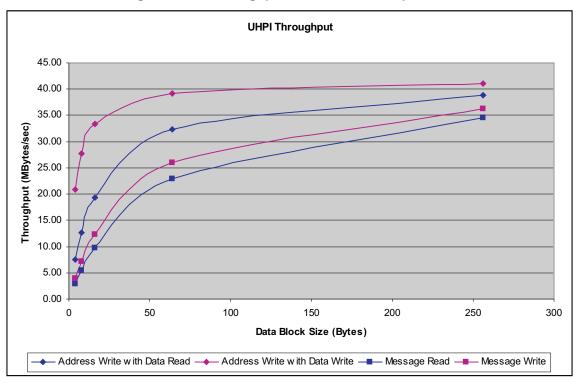

| 2<br>3<br>4<br>5                                                                                       | C6472/TCI6486 Block Diagram  DMA Switched Central Resource Block Diagram  SRIO Throughput - 3.125 Gbps  SRIO Throughput - 2.5 Gbps  SRIO Throughput - 1.25 Gbps  HPI Throughput for Data Blocks Up to 4096 Bytes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 17<br>17<br>18<br>22                                                             |

| 2<br>3<br>4<br>5<br>6<br>7                                                                             | C6472/TCI6486 Block Diagram  DMA Switched Central Resource Block Diagram  SRIO Throughput - 3.125 Gbps  SRIO Throughput - 2.5 Gbps  SRIO Throughput - 1.25 Gbps  HPI Throughput for Data Blocks Up to 4096 Bytes  HPI Throughput for Data Blocks Up to 256                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 17<br>17<br>18<br>22<br>22                                                       |

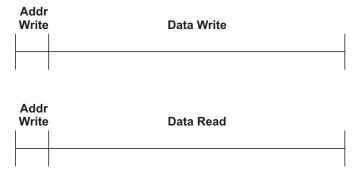

| 2<br>3<br>4<br>5<br>6<br>7<br>8                                                                        | C6472/TCI6486 Block Diagram  DMA Switched Central Resource Block Diagram  SRIO Throughput - 3.125 Gbps  SRIO Throughput - 2.5 Gbps  SRIO Throughput - 1.25 Gbps  HPI Throughput for Data Blocks Up to 4096 Bytes  HPI Throughput for Data Blocks Up to 256  Block Write and Read Timelines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 17<br>17<br>18<br>22<br>23                                                       |

| 2<br>3<br>4<br>5<br>6<br>7<br>8<br>9                                                                   | C6472/TCI6486 Block Diagram  DMA Switched Central Resource Block Diagram  SRIO Throughput - 3.125 Gbps  SRIO Throughput - 2.5 Gbps  SRIO Throughput - 1.25 Gbps  HPI Throughput for Data Blocks Up to 4096 Bytes  HPI Throughput for Data Blocks Up to 256  Block Write and Read Timelines  Message Protocol Write and Read Timelines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 17<br>17<br>18<br>22<br>23<br>23                                                 |

| 2<br>3<br>4<br>5<br>6<br>7<br>8<br>9                                                                   | C6472/TCI6486 Block Diagram  DMA Switched Central Resource Block Diagram  SRIO Throughput - 3.125 Gbps  SRIO Throughput - 2.5 Gbps  SRIO Throughput - 1.25 Gbps  HPI Throughput for Data Blocks Up to 4096 Bytes  HPI Throughput for Data Blocks Up to 256  Block Write and Read Timelines  Message Protocol Write and Read Timelines  TMS320C6472/TMS320TCI6486 Memory System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 9<br>17<br>18<br>22<br>22<br>23<br>23                                            |

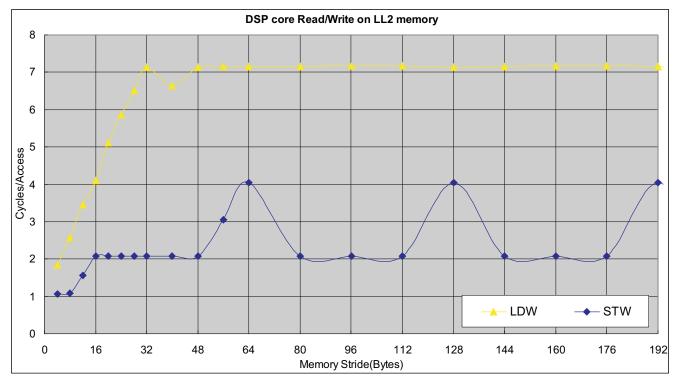

| 2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10                                                             | C6472/TCI6486 Block Diagram  DMA Switched Central Resource Block Diagram  SRIO Throughput - 3.125 Gbps  SRIO Throughput - 2.5 Gbps  SRIO Throughput - 1.25 Gbps  HPI Throughput for Data Blocks Up to 4096 Bytes  HPI Throughput for Data Blocks Up to 256  Block Write and Read Timelines  Message Protocol Write and Read Timelines  TMS320C6472/TMS320TCI6486 Memory System  LL2 Memory Access Performance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 22<br>23<br>23<br>26<br>30                                                       |

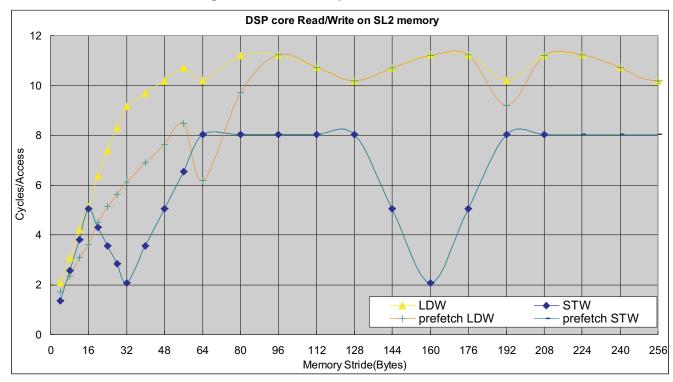

| 2<br>3<br>4<br>5<br>6<br>7<br>8<br>9                                                                   | C6472/TCI6486 Block Diagram  DMA Switched Central Resource Block Diagram  SRIO Throughput - 3.125 Gbps  SRIO Throughput - 2.5 Gbps  SRIO Throughput - 1.25 Gbps  HPI Throughput for Data Blocks Up to 4096 Bytes  HPI Throughput for Data Blocks Up to 256  Block Write and Read Timelines  Message Protocol Write and Read Timelines  TMS320C6472/TMS320TCI6486 Memory System  LL2 Memory Access Performance  SL2 Memory Access Performance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 22<br>23<br>23<br>26<br>30                                                       |

| 2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10                                                             | C6472/TCl6486 Block Diagram  DMA Switched Central Resource Block Diagram  SRIO Throughput - 3.125 Gbps  SRIO Throughput - 2.5 Gbps  SRIO Throughput - 1.25 Gbps  HPI Throughput for Data Blocks Up to 4096 Bytes  HPI Throughput for Data Blocks Up to 256  Block Write and Read Timelines  Message Protocol Write and Read Timelines  TMS320C6472/TMS320TCl6486 Memory System  LL2 Memory Access Performance  SL2 Memory Access Performance  SL2 Access Performance Compared to LL2                                                                                                                                                                                                                                                                                                                                                                                                                                                | 22<br>23<br>23<br>26<br>30                                                       |

| 2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12                                                 | C6472/TCI6486 Block Diagram  DMA Switched Central Resource Block Diagram  SRIO Throughput - 3.125 Gbps  SRIO Throughput - 2.5 Gbps  SRIO Throughput - 1.25 Gbps  HPI Throughput for Data Blocks Up to 4096 Bytes  HPI Throughput for Data Blocks Up to 256  Block Write and Read Timelines  Message Protocol Write and Read Timelines  TMS320C6472/TMS320TCI6486 Memory System  LL2 Memory Access Performance  SL2 Memory Access Performance  SL2 Access Performance Compared to LL2                                                                                                                                                                                                                                                                                                                                                                                                                                                | 9<br>17<br>18<br>22<br>23<br>23<br>26<br>30<br>31                                |

| 2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13                                           | C6472/TCI6486 Block Diagram  DMA Switched Central Resource Block Diagram  SRIO Throughput - 3.125 Gbps  SRIO Throughput - 2.5 Gbps  SRIO Throughput - 1.25 Gbps  HPI Throughput for Data Blocks Up to 4096 Bytes  HPI Throughput for Data Blocks Up to 256  Block Write and Read Timelines  Message Protocol Write and Read Timelines  TMS320C6472/TMS320TCI6486 Memory System  LL2 Memory Access Performance  SL2 Memory Access Performance  SL2 Access Performance Compared to LL2  DDR2 Memory Read Access Performance - Large Strides                                                                                                                                                                                                                                                                                                                                                                                           | 22<br>23<br>23<br>24<br>30<br>31<br>32                                           |

| 2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13                                           | C6472/TCI6486 Block Diagram  DMA Switched Central Resource Block Diagram  SRIO Throughput - 3.125 Gbps  SRIO Throughput - 2.5 Gbps  SRIO Throughput - 1.25 Gbps  HPI Throughput for Data Blocks Up to 4096 Bytes  HPI Throughput for Data Blocks Up to 256  Block Write and Read Timelines  Message Protocol Write and Read Timelines  TMS320C6472/TMS320TCI6486 Memory System  LL2 Memory Access Performance  SL2 Memory Access Performance  SL2 Access Performance Compared to LL2  DDR2 Memory Read Access Performance - Large Strides  DDR2 Memory Read Access Performance - Small Strides                                                                                                                                                                                                                                                                                                                                      | 17<br>17<br>18<br>22<br>23<br>26<br>30<br>31<br>32<br>33                         |

| 2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14                                     | C6472/TCI6486 Block Diagram  DMA Switched Central Resource Block Diagram  SRIO Throughput - 3.125 Gbps  SRIO Throughput - 2.5 Gbps  SRIO Throughput for Data Blocks Up to 4096 Bytes  HPI Throughput for Data Blocks Up to 256  Block Write and Read Timelines  Message Protocol Write and Read Timelines  TMS320C6472/TMS320TCI6486 Memory System  LL2 Memory Access Performance  SL2 Memory Access Performance  SL2 Access Performance Compared to LL2  DDR2 Memory Read Access Performance - Large Strides  DDR2 Memory Write Access Performance - Small Strides  DDR2 Memory Write Access Performance - Large Strides                                                                                                                                                                                                                                                                                                           | 17<br>17<br>18<br>22<br>23<br>23<br>23<br>31<br>32<br>33<br>33                   |

| 2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14<br>15<br>16<br>17                   | C6472/TCI6486 Block Diagram  DMA Switched Central Resource Block Diagram  SRIO Throughput - 3.125 Gbps  SRIO Throughput - 2.5 Gbps  SRIO Throughput - 1.25 Gbps  HPI Throughput for Data Blocks Up to 4096 Bytes  HPI Throughput for Data Blocks Up to 256  Block Write and Read Timelines  Message Protocol Write and Read Timelines  TMS320C6472/TMS320TCI6486 Memory System  LL2 Memory Access Performance  SL2 Memory Access Performance  SL2 Access Performance Compared to LL2.  DDR2 Memory Read Access Performance - Large Strides  DDR2 Memory Write Access Performance - Small Strides  DDR2 Memory Write Access Performance - Large Strides  DDR2 Memory Write Access Performance - Large Strides                                                                                                                                                                                                                        | 17<br>17<br>18<br>22<br>23<br>23<br>23<br>31<br>32<br>33<br>34<br>34             |

| 2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14<br>15<br>16<br>17<br>18             | DMA Switched Central Resource Block Diagram  SRIO Throughput - 3.125 Gbps  SRIO Throughput - 2.5 Gbps  SRIO Throughput - 1.25 Gbps  HPI Throughput for Data Blocks Up to 4096 Bytes  HPI Throughput for Data Blocks Up to 256  Block Write and Read Timelines  Message Protocol Write and Read Timelines  TMS320C6472/TMS320TCI6486 Memory System  LL2 Memory Access Performance  SL2 Memory Access Performance  SL2 Access Performance Compared to LL2.  DDR2 Memory Read Access Performance - Large Strides  DDR2 Memory Write Access Performance - Large Strides  DDR2 Memory Write Access Performance - Large Strides  DDR2 Memory Write Access Performance - Small Strides  DDR2 Memory Write Access Performance - Small Strides  Effect of ACNT on EDMA Bandwidth                                                                                                                                                             | 17<br>17<br>18<br>22<br>23<br>23<br>23<br>31<br>32<br>33<br>34<br>34<br>37       |

| 2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14<br>15<br>16<br>17<br>18             | C6472/TCl6486 Block Diagram  DMA Switched Central Resource Block Diagram  SRIO Throughput - 3.125 Gbps  SRIO Throughput - 2.5 Gbps  SRIO Throughput - 1.25 Gbps  HPI Throughput for Data Blocks Up to 4096 Bytes  HPI Throughput for Data Blocks Up to 256  Block Write and Read Timelines  Message Protocol Write and Read Timelines  TMS320C6472/TMS320TCl6486 Memory System  LL2 Memory Access Performance  SL2 Memory Access Performance Compared to LL2  DDR2 Memory Read Access Performance - Large Strides  DDR2 Memory Write Access Performance - Small Strides  DDR2 Memory Write Access Performance - Large Strides  DDR2 Memory Write Access Performance - Large Strides  DDR2 Memory Write Access Performance - Large Strides  DDR2 Memory Write Access Performance - Small Strides  Effect of ACNT on EDMA Bandwidth  Linear 2D Transfers                                                                              | 17<br>17<br>18<br>22<br>23<br>23<br>23<br>31<br>32<br>33<br>34<br>37<br>38       |

| 2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14<br>15<br>16<br>17<br>18<br>19<br>20 | C6472/TC16486 Block Diagram  DMA Switched Central Resource Block Diagram  SRIO Throughput - 3.125 Gbps  SRIO Throughput - 1.25 Gbps  SRIO Throughput - 1.25 Gbps  HPI Throughput for Data Blocks Up to 4096 Bytes  HPI Throughput for Data Blocks Up to 256  Block Write and Read Timelines  Message Protocol Write and Read Timelines  TMS320C6472/TMS320TC16486 Memory System  LL2 Memory Access Performance  SL2 Memory Access Performance  SL2 Access Performance Compared to LL2  DDR2 Memory Read Access Performance - Large Strides  DDR2 Memory Write Access Performance - Small Strides  DDR2 Memory Write Access Performance - Large Strides  DDR2 Memory Write Access Performance - Small Strides  DDR2 Memory Write Access Performance - Small Strides  Effect of ACNT on EDMA Bandwidth  Linear 2D Transfers  Effect of Index on EDMA Transfers                                                                        | 17<br>17<br>18<br>22<br>23<br>23<br>23<br>23<br>33<br>34<br>32<br>37<br>38<br>39 |

| 2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14<br>15<br>16<br>17<br>18             | C6472/TC16486 Block Diagram  DMA Switched Central Resource Block Diagram  SRIO Throughput - 3.125 Gbps  SRIO Throughput - 2.5 Gbps  SRIO Throughput - 1.25 Gbps  HPI Throughput for Data Blocks Up to 4096 Bytes  HPI Throughput for Data Blocks Up to 256  Block Write and Read Timelines  Message Protocol Write and Read Timelines  TMS320C6472/TMS320TC16486 Memory System  LL2 Memory Access Performance  SL2 Memory Access Performance Compared to LL2  DDR2 Memory Read Access Performance - Large Strides  DDR2 Memory Write Access Performance - Small Strides  Effect of ACNT on EDMA Bandwidth  Linear 2D Transfers  Effect of Index on EDMA Transfers  SL2 Memory Architecture and Access Paths | 17<br>17<br>18<br>22<br>23<br>23<br>23<br>31<br>32<br>33<br>34<br>37<br>38       |

Copyright © 2008–2009, Texas Instruments Incorporated

## www.ti.com

## **List of Tables**

| 1  | DMA SCR Connection Matrix                                                             | 10         |

|----|---------------------------------------------------------------------------------------|------------|

| 2  | EDMA Maximum Measured Throughput                                                      | 12         |

| 3  | RGMII Throughput                                                                      | 13         |

| 4  | GMII Throughput                                                                       | 13         |

| 5  | 10 Mbps RMII/S3MII Throughput                                                         | 14         |

| 6  | 100 Mbps RMII/S3MII Throughput                                                        | 14         |

| 7  | SRIO Two-Board Throughput (Gbps) - 3.125 Gbps                                         | 16         |

| 8  | SRIO Two-Board Throughput (Gbps) - 2.5 Gbps                                           | 16         |

| 9  | SRIO Two-Board Throughput (Gbps) - 1.25 Gbps                                          | 16         |

| 10 | UTOPIA Throughput                                                                     | 20         |

| 11 | HPI Bandwidth and Utilization for Simple Block Accesses                               | 21         |

| 12 | HPI Bandwidth and Utilization for Message Protocol Accesses                           | 21         |

| 13 | Theoretical Bus Bandwidth at 500 MHz                                                  | 27         |

| 14 | Theoretical Bus Bandwidth at 625 MHz                                                  | 27         |

| 15 | Maximum Throughput of Memory Endpoints at 500 MHz                                     | 27         |

| 16 | Maximum Throughput of Memory Endpoints at 625 MHz                                     | 28         |

| 17 | DSP Core, EDMA, and IDMA Transfer Bandwidth Comparison                                | 28         |

| 18 | EDMA Transfer Overhead (Cycles)                                                       | 35         |

| 19 | IDMA Transfer Overhead (Cycles)                                                       | 35         |

| 20 | Transfer Controller Attributes                                                        | 36         |

| 21 | Throughput Comparison Between TCs on a 500-MHz C6472/TCI6486 Device                   | 36         |

| 22 | Throughput Comparison Between TCs on a 625-MHz C6472/TCI6486 Device                   | 36         |

| 23 | Data Organization in SL2 Banks                                                        | 40         |

| 24 | Performance of Multiple DSP Cores Sharing SL2 at 500 MHz                              | 41         |

| 25 | Performance of Multiple DSP Cores Sharing SL2 at 625 MHz                              | 41         |

| 26 | Performance of Multiple DMA Masters Sharing SL2 at 500 MHz                            | 42         |

| 27 | Performance of Multiple DMA Masters Sharing SL2 at 625 MHz                            | 42         |

| 28 | Memory Organization in DDR2 Banks                                                     | 43         |

| 29 | Worst-Case Multiple Master Access to DDR2                                             | 44         |

| 30 | Best-Case Multiple Master Access to DDR2                                              | 44         |

| 31 | Performance of Multiple DSP Cores Sharing DDR2 at 500 MHz                             | 45         |

| 32 | Performance of Multiple DSP Cores Sharing DDR2 at 625 MHz                             | 45         |

| 33 | Performance of Multiple EDMA Masters Sharing DDR2(DDR2 at 533 MHz and CPU at 500 MHz) | 47         |

| 34 | Performance of Multiple EDMA Masters Sharing DDR2(DDR2 at 533 MHz and CPU at 625 MHz) | 48         |

| 35 | Probability of Multiple Masters Accessing the Same DDR2 Bank                          | 49         |

| 36 | Data Buffer Organization to Minimize Row Switch Overhead                              | 49         |

| 37 | Effect of Priority When Multiple TCs Access DDR2                                      | <b>5</b> 0 |

| 38 | Effect of BPRIO When Multiple TCs Access DDR2                                         | 51         |

TMS320C64x is a trademark of Texas Instruments. RapidIO is a registered trademark of RapidIO Trade Association. All other trademarks are the property of their respective owners.

Related Documentation www.ti.com

## 1 Related Documentation

For details about the C64x+ Megamodule, see the *TMS320C64x+ DSP Megamodule Reference Guide* (SPRU871).

For configuration of the EMAC interface, see the TMS320C6472/TMS320TCI6486 DSP Ethernet Media Access Controller (EMAC)/Management Data Input/Output (MDIO) Module User's Guide (SPRUEF8).

For configuration of the SRIO interface, see the *TMS320C6472/TMS320TCl648x DSP Serial RapidIO (SRIO) User's Guide* (SPRUE13).

For configuration of the TSIP interface, see the *TMS320C6472/TMS320TCI6486 DSP Telecom Serial Interface Port (TSIP) User's Guide* (SPRUEG4).

For configuration of the Utopia interface, see the TMS320C6472/TMS320TCI6486 DSP Universal Test and Operations PHY Interface for ATM 2 (UTOPIA2) User's Guide (SPRUEG2).

For configuration of the EDMA3, see the *TMS320C6472/TMS320TCI648x DSP Enhanced DMA (EDMA3) Controller User's Guide* (SPRU727).

For configuration of the HPI, see the *TMS320C6472/TMS320TCI6486 DSP Host Port Interface (HPI) User's Guide* (SPRUEG1).

For more information about the EDMA3 performance on the TCI6482 device, see the *TMS320TCI6482 EDMA3 Performance* application report (SPRAAG8).

## 2 Abbreviations

**ATM** — Asynchronous Transfer Mode

**CC** — EDMA Channel Controller

**CODEC** — Coder/Decoder

**CPU** — Central Processing Unit

**DMA** — Direct Memory Access

**DDR** — Double-Data Rate

**DSP** — Digital Signal Processor

**EDMA** — Enhanced Direct Memory Access

**EMIF** — External Memory Interface

FIFO — First-In First-Out

**GMII** — Gigabit Media Independent Interface

**HPI** — Host Port Interface

**IDMA** — Internal DMA

L1D — Level-1 Data Memory

**L1P** — Level-1 Program Memory

**LDW** — Load Word

LL2 — Local Level-2 Memory

MAC — Media Access Control

**MII** — Media Independent Interface

**MPHY** — Multi-PHY

www.ti.com Abbreviations

PDMA — Pseudo-Direct Memory Access

PHY — Physical Interface

PLL — Phase-Locked Loop

**RGMII** — Reduced Gigabit Media Independent Interface

RMII — Reduced Media Independent Interface

Rx — Receive

**S3MII** — Source-Synchronous Serial Independent Interface

**SCR** — Switched Central Resource

**SDRAM** — Synchronous Dynamic Random Access Memory

**SL2** — Shared Level-2 Memory

**SPHY** — Single-PHY

**SRAM** — Static Random Access Memory

SRIO — Serial RapidIO

**STW** — Store Word

TC — EDMA Transfer Controller

TR — Transfer Request

TSIP — Telephony Serial Interface Port

Tx — Transmit

UTOPIA — Universal Test and Operations PHY Interface for ATM

Introduction www.ti.com

## 3 Introduction

This document presents the expected throughput of the C6472/TCl6486 device between defined endpoints. Endpoints are peripherals, C64x+ megamodules, or memories. This throughput data was compiled by configuring the endpoints or transport mechanisms in various modes and then transferring blocks of data. By measuring the time required to transport this data, the throughput between the endpoints was then determined.

An overview of the TMS320C6472/TMS320TCI6486 device and a detailed discussion of the system interconnect is provided to help explain the throughput results obtained. The EDMA subsystem is also discussed in detail. After these introductory topics, throughput metrics are presented for the primary peripheral interfaces. The remainder of this document addresses throughput from the perspective of the C64x+ processors.

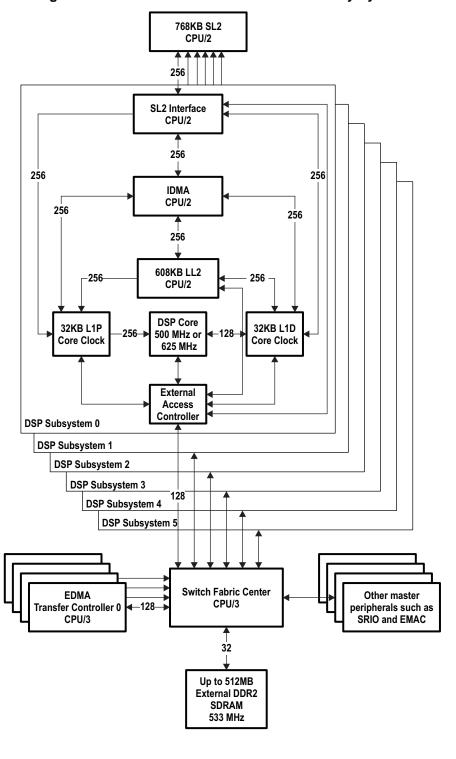

### 4 TMS320C6472/TMS320TCI6486 Overview

The TMS320C6472/TMS320TCI6486 device is a fixed-point, digital signal processor (DSP) optimized for telephony infrastructure and video transcoding applications. It has six TMS320C64x<sup>™</sup> megamodules for data processing and each contains large tightly-coupled SRAM memories to handle large amounts of channel data during CODEC processing. The C6472/TCI6486 device also includes a large shared SRAM memory.

Each of the C64x+ megamodules processes multiple operations each clock cycle. Therefore, the data access bandwidth into these cores is very high and stalls must be minimized. Each megamodule contains a large amount of closely-coupled memory organized as a two-level memory system. The Level-1 program and data memories (L1P and L1D) on each C64x+ megamodule are 32KB each. The Level 2 memory (LL2) on each megamodule is shared between program and data space and is 608KB. Additionally, the C6472/TCl6486 device contains 768KB of on-chip L2 memory that is shared by all six megamodules (SL2).

In addition to the high-performance megamodules and their memories, the C6472/TCl6486 device has multiple high-throughput interfaces. The high-throughput interfaces are:

- Three Telecom Serial Interface Ports (TSIP) each supporting 1024 bi-directional TDM 8-bit timeslots, each operating at 64 Kbps.

- A 16-bit/8-bit UTOPIA slave port supporting up to 800 Mbps bi-directional.

- Two 10/100/1000 Ethernet Media Access Controllers (EMAC) each supporting up to 1 Gbps bi-directional.

- A Serial RapidIO (SRIO) interface with two 1x lanes each operating at 1.25, 2.5 or 3.125 Gbps bi-directional.

- A 32-bit DDR2-533 SDRAM interface with up to 2133 Mbps of throughput.

- A 16-bit multiplexed host-port interface (HPI16) with up to 41.7 Mbps of throughput.

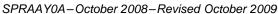

Figure 1 shows the C6472/TCI6486 device functional block diagram.

DDR2 DDR2 32 **DSP Subsystem 5** Memory **SDRAM** Controller DSP Subsystem 4 **DSP Subsystem 3** PLL3 and PLL3 **DSP Subsystem 2** Controller **DSP Subsystem 1** Serial DSP Subsystem 0 RapidIO 32K Bytes L2 SRAM/Cache .1P SRAM/Cache 608K Bytes Direct-Mapped 4-Way Set Assoc. Boot ROM TSIP0 L1P Memory Controller (Memory Protect/Bandwidth Mgmt) TSIP1 TSIP2 C64x+ DSP Core Instruction Fetch **Control Registers** UTOPIA (16/8) ◀ L2 Controlle and Exception Controller Power Control 16-/32-bit **SPLOOP Buffer** Instruction Dispatch Switched Central Resource (SCR EMAC0 Instruction In-Circuit Emulation Decode g **RGMII** Shared Data Path A Data Path B m GMII B Register File A Register File MII d nternal DMA (IDMA) A31-A16 B31-B16 RMII B15-B0 Interrupt SS-SMII SL2 RAM 768K-Bytes System MDIO .M1 .M2 .S1 .D1 .D2 .S2 .L2 ХX XX PLL2 and PLL2 Controller L1D Memory Controller (Memory Protect/Bandwidth Mgmt) EMAC1 RGMII SS-SMII RMII 32K-Bytes Total L1D SRAM/Cache 2-Way Set-Associative HPI (16-bit) I2C **EDMA 3.0** Power-Down PLL1 and GPIO16 L1 Controlle Logic Timer x [6-1] **Boot Configuration** Timer x [0-5] (Shared)

Figure 1. C6472/TCI6486 Block Diagram

System Interconnect www.ti.com

## 5 System Interconnect

The system interconnect, also referred to as a DMA switch fabric, implemented in the C6472/TCl6486 device is known as a Switched Central Resource (SCR). The SCR combined with bridges and the Enhanced DMA (EDMA) module provides the transport between the endpoints. Bridges at some SCR bus interfaces support interconnect to endpoints in a different clock domain or those with a different bus width.

The modules on the C6472/TCl6486 device are interconnected through two switch fabrics, one for data transfers and one for configuration transfers. Each of the switch fabrics individually allows for low-latency, concurrent data transfers between these modules. The data switch fabric is the only one considered in this document, as it carries all of the high-bandwidth data transfers.

Endpoints can be classified into two categories: masters and slaves. Masters are capable of initiating read and write transfers in the system to slave ports. Slaves, on the other hand, cannot initiate transfers. Masters include the C64x+ megamodules, the EDMA transfer controllers, and the EMAC, TSIP, HPI, UTOPIA, and SRIO peripherals. Slaves include the DDR2 EMIF, the C64x+ megamodule local memories, and the shared memory. The EDMA transfer engine must be used to perform slave-to-slave transfers. The EDMA transfer controllers (TC0 through TC3) connect to the switch fabric as masters (each TC has two master ports connecting with the switch fabric) so that they can transfer between slave endpoints.

The switch fabric provides arbitration between system masters when they attempt to access the same slave simultaneously. As long as two masters are communicating with two separate slaves, the transfers can be concurrent.

The data SCR is a high-throughput interconnect used to move blocks of data across the chip very quickly. The data SCR connects masters to slaves via 128-bit data buses running at the CPU frequency divided by 3 (CPU/3). (CPU/3 is the DSP core clock generated by PLL1 and then divided by 3 in the PLL1 controller.) Endpoints that have a 128-bit data bus interface running at this speed can connect directly to the data SCR; other endpoints require a bridge.

Bridges connected to the data SCR perform bus width conversion when the endpoint has a bus width other than 128 or clock domain arbitration when the endpoint bus operates at a frequency other than CPU/3. For example, TSIP modules require a bridge to convert their 32-bit data bus interface into a 128-bit interface so that they can connect to the data SCR. Bridges also support queuing of transfer requests to allow optimized data transport.

## 5.1 Data Switch Fabric Connections

Figure 2 shows the connections between slaves and masters through the data SCR. Masters are shown on the left and slaves on the right. The C64x+ megamodules have both slave and master ports on the data SCR. Also note in Figure 2 that the EMAC, UTOPIA, and HPI peripherals all share a single port on the data SCR. This affects the throughput of each when more than one is active.

Not all masters on the C6472/TCl6486 DSP may connect to all slaves directly. This implementation was chosen to manage the complexity of the data SCR routing. Allowed connections are summarized in Table 1. This table shows which master-slave connections are direct (Y) and which are *logical* (C). Logical connections are actually chained connections through the cross-connect bridges, Xconn1, and Xconn2. Direct connections always yield higher throughput rates and less latency.

Note that TC0 and TC1 do not connect directly to the megamodule memories but they must use the cross-connect bridges, whereas TC2 and TC3 connect directly to the megamodule memories. TC2 and TC3, therefore, have higher performance when transferring data blocks into and out from the megamodule memories.

www.ti.com System Interconnect

Figure 2. DMA Switched Central Resource Block Diagram

System Interconnect www.ti.com

# Table 1. DMA SCR Connection Matrix<sup>(1)</sup> (2) (3)

|                                    |        |      |                      |                      | S                    | LAVES                |                      |                      |          |          |

|------------------------------------|--------|------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------|----------|

| MASTERS                            | CFGSCR | DDR2 | C64x+<br>Megamodule0 | C64x+<br>Megamodule1 | C64x+<br>Megamodule2 | C64x+<br>Megamodule3 | C64x+<br>Megamodule4 | C64x+<br>Megamodule5 | Xconn1_S | Xconn2_S |

| EDMA3<br>Transfer<br>Controller0_R | Υ      | Y    | С                    | С                    | С                    | С                    | С                    | С                    | Y        | N        |

| EDMA3<br>Transfer<br>Controller0_W | Υ      | Y    | С                    | С                    | С                    | С                    | С                    | С                    | Y        | N        |

| EDMA3<br>Transfer<br>Controller1_R | Υ      | Y    | С                    | С                    | С                    | С                    | С                    | С                    | N        | Y        |

| EDMA3<br>Transfer<br>Controller1_W | Υ      | Y    | С                    | С                    | С                    | С                    | С                    | С                    | N        | Y        |

| EDMA3<br>Transfer<br>Controller2_R | Υ      | Y    | Y                    | Y                    | Υ                    | Y                    | Y                    | Y                    | N        | N        |

| EDMA3<br>Transfer<br>Controller2_W | Υ      | Υ    | Y                    | Y                    | Y                    | Y                    | Y                    | Y                    | N        | N        |

| EDMA3<br>Transfer<br>Controller3_R | N      | Υ    | Y                    | Y                    | Y                    | Y                    | Y                    | Y                    | N        | N        |

| EDMA3<br>Transfer<br>Controller3_W | N      | Y    | Υ                    | Y                    | Υ                    | Y                    | Y                    | Y                    | N        | N        |

| EMAC0                              | Y      | Υ    | Υ                    | Y                    | Υ                    | Y                    | Y                    | Y                    | N        | N        |

| EMAC1                              | Y      | Υ    | Υ                    | Y                    | Υ                    | Y                    | Y                    | Y                    | N        | N        |

| UTOPIA                             | Y      | Υ    | Υ                    | Y                    | Υ                    | Y                    | Y                    | Y                    | N        | N        |

| HPI                                | Y      | Υ    | Υ                    | Y                    | Υ                    | Y                    | Y                    | Y                    | N        | N        |

| 3x TSIP                            | N      | Υ    | Υ                    | Y                    | Υ                    | Y                    | Y                    | Y                    | N        | N        |

| RapidIO                            | Υ      | Υ    | Υ                    | Υ                    | Υ                    | Y                    | Y                    | Υ                    | N        | N        |

| C64x+<br>Megamodule0               | N      | Y    | N                    | С                    | С                    | С                    | С                    | С                    | Y        | N        |

| C64x+<br>Megamodule1               | N      | Υ    | С                    | N                    | С                    | С                    | С                    | С                    | Y        | N        |

| C64x+<br>Megamodule2               | N      | Y    | С                    | С                    | N                    | С                    | С                    | С                    | Y        | N        |

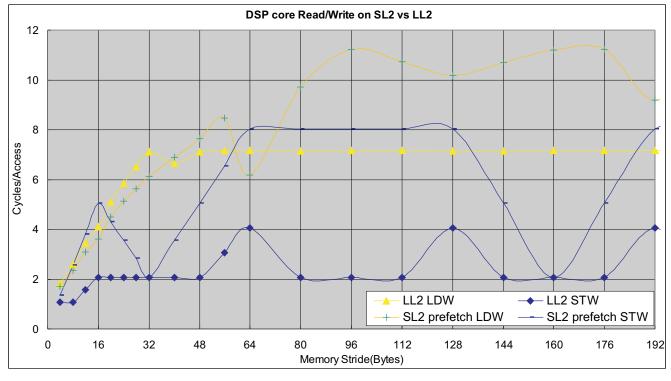

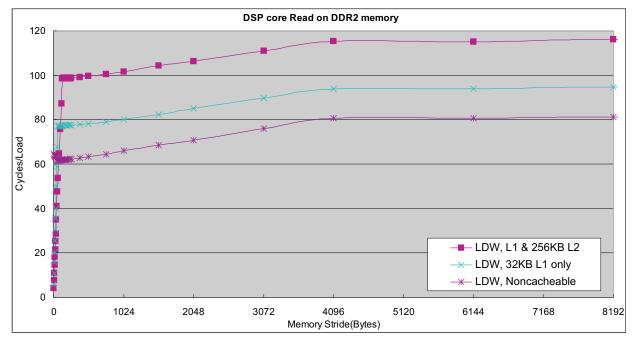

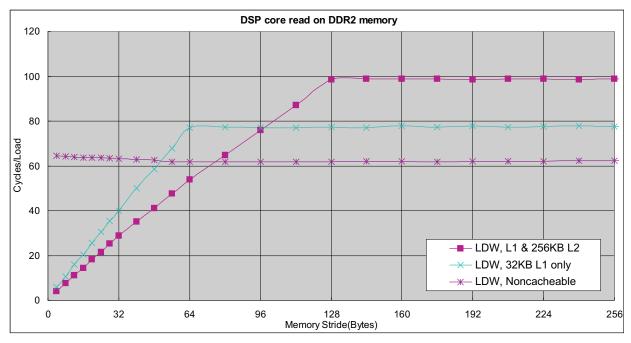

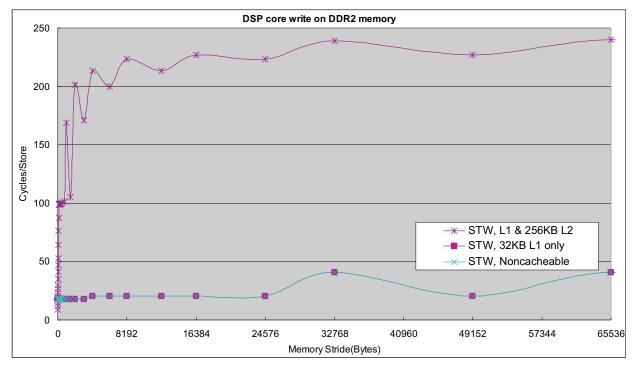

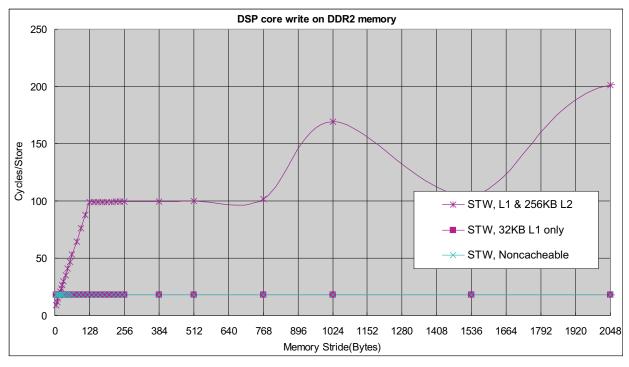

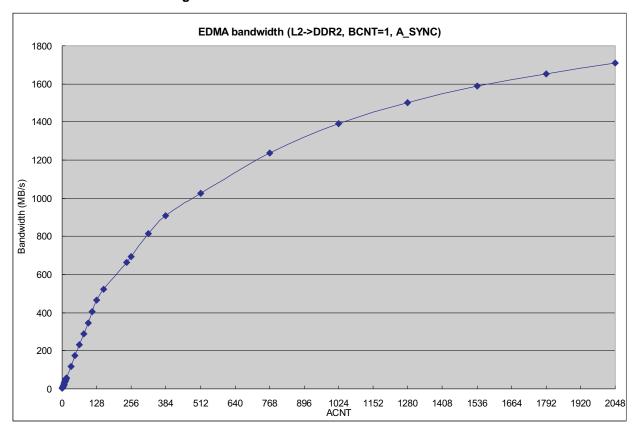

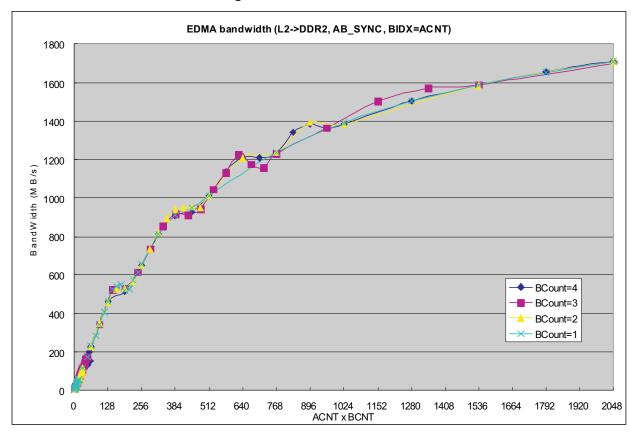

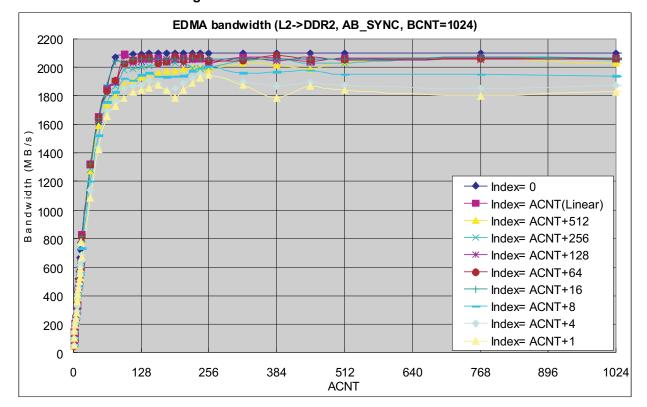

| C64x+<br>Megamodule3               | N      | Υ    | С                    | С                    | С                    | N                    | С                    | С                    | N        | Y        |