# Migrating From KeyStone I to KeyStone II

High-Performance Multicore Processors

### ABSTRACT

This guide describes the main System-on-Chip (SoC) level and peripheral changes that need to be considered when migrating a KeyStone I-based system design to a KeyStone II-based system design.

In this guide, KeyStone I includes all TMS320TCI661x devices and KeyStone II includes all TCI663xK2y devices. Any differences within KeyStone I or KeyStone II devices are described explicitly.

**NOTE:** The information in this document should be used in conjunction with information in the device-specific Keystone Architecture data manual that applies to the part number of your device.

### Contents

| 1 | SoC-Level Migration                          | 3  |

|---|----------------------------------------------|----|

|   | Peripheral-Level Migration                   |    |

|   | Related Documentation From Texas Instruments |    |

| 4 | References                                   | 56 |

### List of Figures

| 1 | TCI6630K2L Device Nomenclature Example                  | 3  |

|---|---------------------------------------------------------|----|

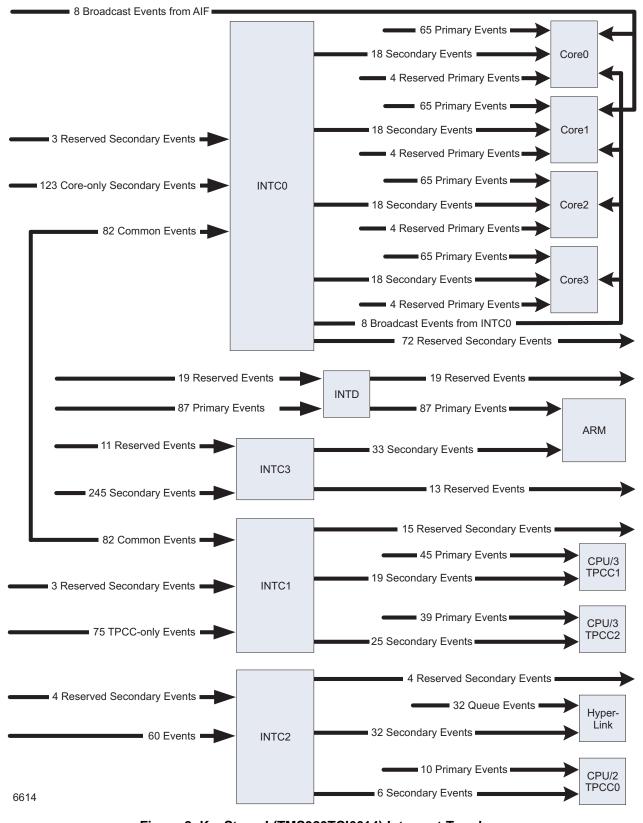

|   | KeyStone I (TMS320TCI6614) Interrupt Topology           |    |

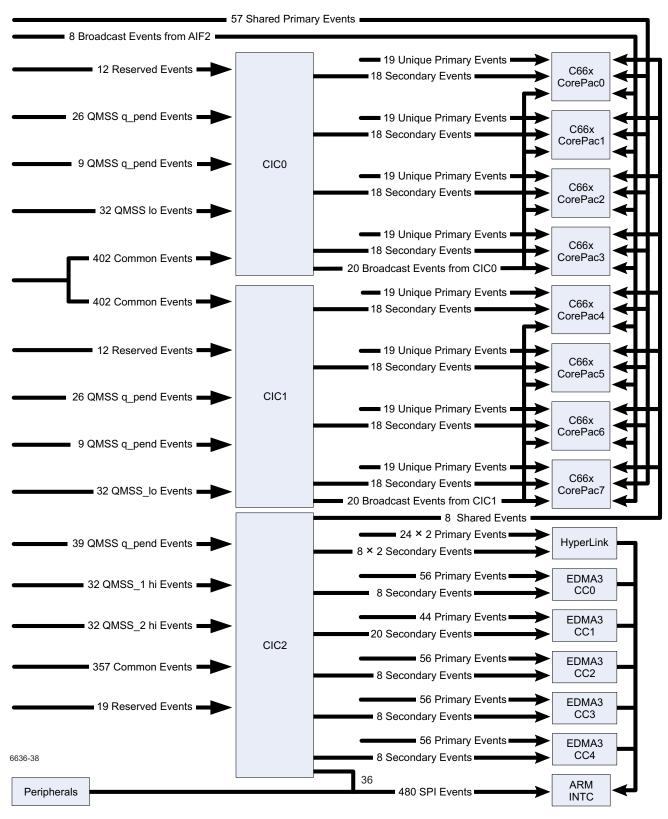

| 3 | KeyStone II (TCI6638K2K) Interrupt Topology             |    |

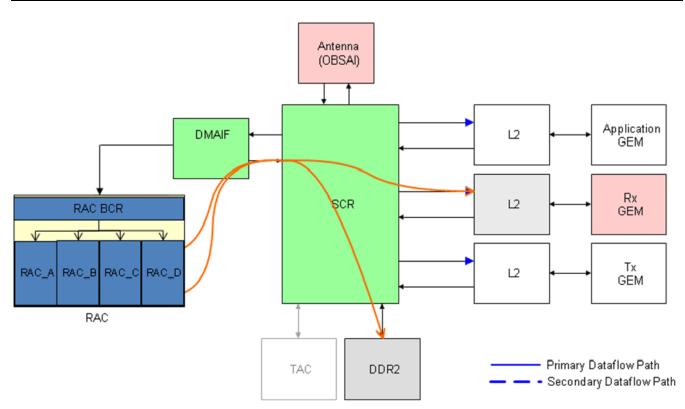

| 4 | KeyStone II RAC Data Flow                               | 46 |

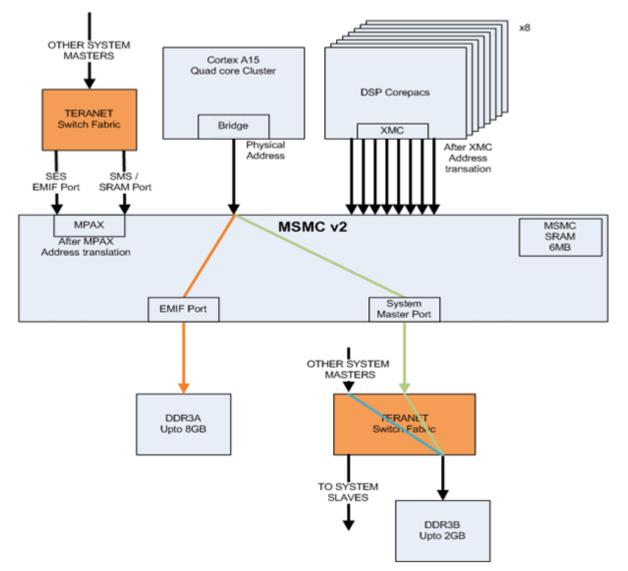

| 5 | DDR3 Connectivity in KeyStone II Devices                | 48 |

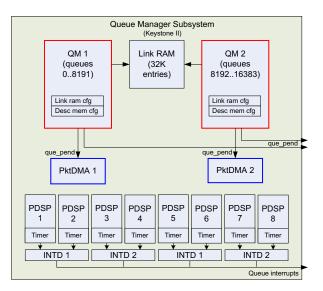

| 6 | Queue Manager Subsystem for KeyStone II                 | 50 |

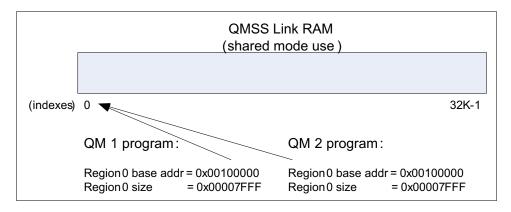

| 7 | Queue Manager Linking RAM — Shared Mode for KeyStone II | 51 |

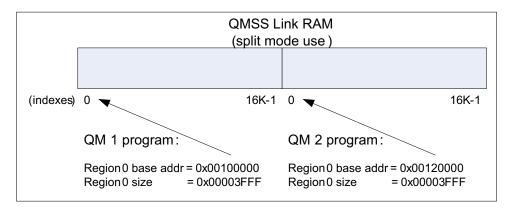

| 8 | Queue Manager Linking RAM — Split Mode for KeyStone II  | 51 |

### List of Tables

| 1  | Architectural Differences Between KeyStone I and KeyStone II Devices | . 5 |

|----|----------------------------------------------------------------------|-----|

| 2  | KeyStone II Memory Map View From ARM, DSP, and System Masters        | . 8 |

| 3  | KeyStone I to KeyStone II (TCI6638K2K) Memory Map Changes            | . 9 |

| 4  | KeyStone I (TMS320TCI6614) Events Interconnection Matrix             | 16  |

| 5  | KeyStone II (TCI6638K2K) Events Interconnection Matrix               | 24  |

| 6  | Power Domain Changes                                                 | 35  |

| 7  | Clock Domain Changes                                                 | 36  |

| 8  | Master ID Changes                                                    | 37  |

| 9  | Privilege ID Changes                                                 |     |

| 10 | Clock Changes                                                        | 42  |

| 11 | EDMA3 CC Changes (KeyStone II vs. KeyStone I)                        | 44  |

| 12 | EDMA3 TC Changes (KeyStone II vs. KeyStone I)                        | 44  |

| 13 | Recommended Logical QM Mapping                                       | 53  |

1

| 14 Possible PDSP Firmware Loading | 14 | Possible PDSP Firmware Loading | 53 |

|-----------------------------------|----|--------------------------------|----|

|-----------------------------------|----|--------------------------------|----|

# Trademarks

TMS320 is a trademark of Texas Instruments.

ARM, Cortex are registered trademarks of ARM Limited (or its subsidiaries) in the EU and/or elsewhere. All rights reserved.

2

# 1 SoC-Level Migration

### 1.1 SoC-Level Migration Overview

This section describes the main SoC-level changes that must be considered when migrating a KeyStone Ibased system design to a KeyStone II-based system design.

In this migration section, KeyStone I includes all TMS320TCI661x devices and KeyStone II includes all TCI663x devices. Any differences within KeyStone I or KeyStone II devices are explicitly mentioned.

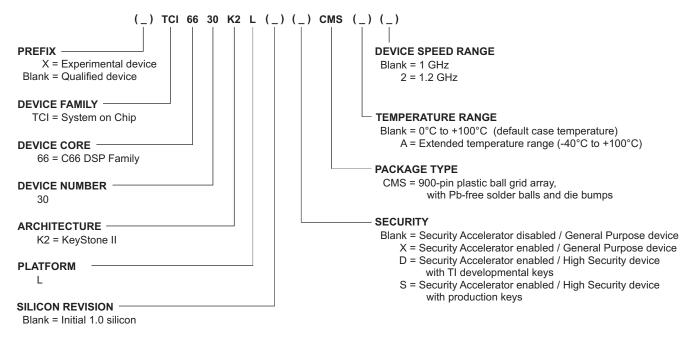

There are some changes in KeyStone I and KeyStone II device nomenclature. The prefix of TMS320<sup>™</sup> found on KeyStone I device nomenclature has been dropped from KeyStone II devices due to the architecture (KeyStone II, such as K2) and platform names (such as K, H, L, an so forth) are suffixed to the part numbers on the KeyStone II devices. The example of the TCI6630K2L device nomenclature is shown in Figure 1.

Figure 1. TCI6630K2L Device Nomenclature Example

3

# 1.2 Acronyms Used in This Document

| Accronym | Definition                                                                          |

|----------|-------------------------------------------------------------------------------------|

| ACC      | Accumulator Firmware                                                                |

| ARM      | Advanced RISC Machines                                                              |

| AID      | Antenna Interface Digital Front End                                                 |

| AIF      | Antenna Interface                                                                   |

| AIL      | Antenna Interface CPRI/OBSAI Link                                                   |

| BCP      | Bit Coprocessor                                                                     |

| BCR      | Receive Accelerator Coprocessor Broadcaster                                         |

| CC       | Channel Controllers                                                                 |

| CFG      | Configuration                                                                       |

| CPPI     | Communications Port Programming Interface (previous name for Multicore Navigator)   |

| DSP      | Digital Signal Processor                                                            |

| DDR      | Dual Data Rate                                                                      |

| EMIF     | External Memory Interface Controller                                                |

| EDMA     | Enhanced Direct Memory Access                                                       |

| FDQ      | Free Descriptor Queue                                                               |

| FFTC     | Fast Fourier Transform Coprocessor                                                  |

| GPIO     | General Purpose Input/Output                                                        |

| I2C      | Inter Integrated Circuit                                                            |

| INTC     | Interrupt Controller                                                                |

| INTD     | Interrupt Distributor                                                               |

| IPC      | Inter Processor Communication                                                       |

| IQN      | IQNet Subsystem Antenna Interface                                                   |

| MSMC     | Multicore Shared Memory Controller                                                  |

| MPU      | Memory Protection Unit                                                              |

| OSR      | On-Chip Standalone RAM                                                              |

| OTP      | One Time Programmable Memory                                                        |

| PA       | Packet Accelerator                                                                  |

| PBIST    | Programmable Built-In Self-Test                                                     |

| PCIE     | Peripheral Component Interconnect Express                                           |

| PDSP     | Packet Data Structure Processor (used to run firmware to aid in QMSS functionality) |

| PLL      | Phase Locked Loop                                                                   |

| PKTDMA   | Packet DMA (previously called CPPI-DMA or C-DMA)                                    |

| PSC      | Power Sleep Controller                                                              |

| QoS      | Quality of Service Firmware                                                         |

| QM, QMSS | Queue Manager, Queue Manager Subsystem                                              |

| RAC      | Receive Accelerator Coprocessor                                                     |

| RSA      | Rake Search Accelerator                                                             |

| SA       | Security Accelerator                                                                |

| SGMII    | Serial Gigabit Media Independent Interface                                          |

| SMP      | Symmetric Multi-Processing                                                          |

| SPI      | Serial Peripheral Interface                                                         |

| SRAM     | Static Random Access Memory                                                         |

| STM      | System Trace Module                                                                 |

| тс       | Transfer Controllers                                                                |

| TAC      | Transmit Accelerator Coprocessor                                                    |

| TAC FL   | Transmit Accelerator Coprocessor Functional Library                                 |

| ТСР      | Turbo Coprocessor                                                                   |

SoC-Level Migration

| Accronym | Definition                              |

|----------|-----------------------------------------|

| ТЕТВ     | TI Embedded Trace Buffer                |

| UART     | Universal Asynchronous Receive/Transmit |

| VFP      | Vector Floating Point                   |

| XGE      | 10 Gigabit Ethernet                     |

# 1.3 Architectural Differences

Table 1 gives the architecture-related points, which should be considered for migrating a system using KeyStone I devices to a system using KeyStone II devices. For more details specific to individual KeyStone I and KeyStone II devices, see the device-specific data manuals.

### Table 1. Architectural Differences Between KeyStone I and KeyStone II Devices

| IP Block                           | KeyStone I                   | KeyStone II                | Minimal to Moderate SW Changes (MMRs Added /<br>Changed or Added Functionality)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | New SW to<br>Support New<br>HW Block |  |

|------------------------------------|------------------------------|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|--|

| Core and Memory Subsystem          |                              |                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                      |  |

| C66x DSP Core                      | 4x                           | 4x, 8x <sup>(1)</sup>      | Completely software compatible                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                      |  |

| ARM Cortex-A8 core <sup>(2)</sup>  | 1x                           | No                         | Required                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                      |  |

| ARM Cortex-A15 core                | No                           | 2x, 4x <sup>(3)</sup>      | Required                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                      |  |

| MSMC                               | 1x                           | 1x                         | MMRs added to support additional cores                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                      |  |

| DDR3 EMIF (64-bit)                 | 1x                           | 1x, 2x <sup>(4)</sup>      | <ol> <li>Programming changed due to PHY and EMIF<br/>controller changes</li> <li>Changes to SDRAM settings to support up to<br/>DDR3-1600</li> <li>Support for data obfuscation</li> <li>DDR3A EMIF is connected to MSMC port, hence<br/>need MPAX setup to access EMIF MMRs (similar to<br/>TMS320TCl6618 device)</li> <li>But DDR3B EMIF is connected to TeraNet, hence<br/>doesn't need any MPAX setup to access EMIF MMRs.</li> <li>DDR3B has a storage capacity of 2 GB. The<br/>complete 2 GB is accessible from both DSP and ARM.<br/>The system masters can access only the first 512 MB<br/>of DDR3B memory.</li> </ol> |                                      |  |

| Memory                             |                              |                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                      |  |

| L1P per DSP core (cache /<br>SRAM) | 32 Kbytes                    | 32 Kbytes                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                      |  |

| L1D per DSP core (cache /<br>SRAM) | 32 Kbytes                    | 32 Kbytes                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                      |  |

| L2 per DSP core (cache /<br>SRAM)  | 1 Mbytes                     | 1 Mbytes                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                      |  |

| L1P cache per ARM core             | 32 Kbytes <sup>(5)</sup>     | 32 Kbytes                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                      |  |

| L1D cache per ARM core             | 32 Kbytes <sup>(6)</sup>     | 32 Kbytes                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                      |  |

| SL2 cache for all 4 ARM cores      | 256<br>Kbytes <sup>(7)</sup> | 1, 4 Mbytes <sup>(8)</sup> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                      |  |

| MSMC SRAM                          | 2 Mbytes                     | 2, 6 Mbytes <sup>(9)</sup> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                      |  |

<sup>(1)</sup> 8 C66x CorePac are available only in TCI6636K2H and TCI6638K2K.

- <sup>(2)</sup> One ARM Cortex-A8 is present in TMS320TCI6612 and TMS320TCI6614.

- <sup>(3)</sup> 4 ARM Cortex-A15s are available only in TCI6636K2H and TCI6638K2K.

- <sup>(4)</sup> DDR3A and DDR3B are available only in TCI6636K2H and TCI6638K2K.

- <sup>(5)</sup> Applicable only for TMS320TCI6612 and TMS320TCI6614.

- <sup>(6)</sup> Applicable only for TMS320TCI6612 and TMS320TCI6614.

- <sup>(7)</sup> Applicable only for TMS320TCI6612 and TMS320TCI6614.

- <sup>(8)</sup> 4Mbytes are available only in TCI6636K2H and TCI6638K2K.

- <sup>(9)</sup> 6Mbits of MSMC is available only in TCI6636K2H and TCI6638K2K.

### Table 1. Architectural Differences Between KeyStone I and KeyStone II Devices (continued)

| P Block KeyStone I KeyS             |                    | KeyStone II                                                                                  | Minimal to Moderate SW Changes (MMRs Added /<br>Changed or Added Functionality)                                                                                                             | New SW to<br>Support New<br>HW Block |

|-------------------------------------|--------------------|----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| DDR3A memory (max)                  | 8 Gbytes           | 8 Gbytes <sup>(10)</sup>                                                                     |                                                                                                                                                                                             |                                      |

| DDR3B memory (max) <sup>(11)</sup>  | No                 | 2 Gbytes (for<br>ARM and DSP<br>cores) and 512<br>Mbytes (system<br>masters) <sup>(10)</sup> |                                                                                                                                                                                             |                                      |

| DSP Boot ROM                        | 128 Kbytes         | 128 Kbytes                                                                                   |                                                                                                                                                                                             |                                      |

| ARM Boot ROM                        | No                 | 256 Kbytes                                                                                   |                                                                                                                                                                                             |                                      |

| OTP memory                          | No <sup>(12)</sup> | 4 Kbits                                                                                      |                                                                                                                                                                                             |                                      |

| OSR <sup>(13)</sup>                 | No                 | 1Mbytes                                                                                      |                                                                                                                                                                                             |                                      |

| Hardware Coprocessors               | ,                  |                                                                                              | *                                                                                                                                                                                           | +                                    |

| RAC                                 | 2x                 | 1x, 4x <sup>(14)</sup>                                                                       | RAC subsystem programming changed due to<br>Receive Accelerator Coprocessor Broadcaster (BCR)<br>(RAC broadcaster)                                                                          | Required for<br>BCR support          |

| TAC <sup>(15)</sup>                 | 1x                 | 1x                                                                                           | Capacity is tripled, software changes needed to support new features                                                                                                                        |                                      |

| FFTC                                | 3x                 | 2x, 6x <sup>(16)</sup>                                                                       | Software changes needed for 8-bit support                                                                                                                                                   |                                      |

| Bit Coprocessor (BCP)               | 1x                 | 1x                                                                                           | Completely software compatible                                                                                                                                                              |                                      |

| TCP3d                               | 3x                 | 2x, 4x <sup>(17)</sup>                                                                       | Completely software compatible                                                                                                                                                              |                                      |

| TCP3e                               | 1x                 | No                                                                                           | TCP3e is integrated in the BCP so not required external                                                                                                                                     |                                      |

| VCP2                                | 4x                 | 4x, 8x <sup>(18)</sup>                                                                       | Completely software compatible                                                                                                                                                              |                                      |

| RSA1                                | 4x                 | 8x, 16x <sup>(19)</sup>                                                                      | Completely software compatible                                                                                                                                                              |                                      |

| Multicore Navigator                 | -!                 | •                                                                                            | •                                                                                                                                                                                           | -!                                   |

| Queue manager subsystem +<br>PKTDMA | 1x                 | 2x                                                                                           | <ol> <li>Double no. of queues (8K to 16K)</li> <li>Descriptor size doubled (512K to 1M)</li> <li>2 Queue Managers and 2 Infrastructure DMAs</li> <li>Queue event mapping changed</li> </ol> |                                      |

| EDMA3                               |                    |                                                                                              |                                                                                                                                                                                             |                                      |

| EDMA3CC                             | Зх                 | 3x, 5x <sup>(20)</sup>                                                                       | <ol> <li>More EDMA3CC instances added</li> <li>Larger PaRAM sizes</li> <li>Event mapping changed</li> </ol>                                                                                 |                                      |

| EDMA3TC                             | 10x                | 10x, 14x <sup>(21)</sup>                                                                     | More EDMA3TC instances added                                                                                                                                                                |                                      |

| Network Coprocessor <sup>(22)</sup> |                    |                                                                                              | ·                                                                                                                                                                                           |                                      |

| Packet Accelerator (PA)             | 1x                 | 1x                                                                                           | Completely software compatible                                                                                                                                                              |                                      |

| Security Accelerator (SA)           | 1x                 | 1x                                                                                           | Capacity doubled                                                                                                                                                                            |                                      |

<sup>(10)</sup> With ECC capability. ECC is enhanced with a Read-Modify-Write sub-block which enables support for ECC generation in sub 64-bit accesses.

- <sup>(11)</sup> DDR3B is available only in TCI6636K2H and TCI6638K2K.

- <sup>(12)</sup> 4 Kbits of OTP memory is available only for TMS320TCI6612 and TMS320TCI6614.

- <sup>(13)</sup> 1Mbits of OSR is available only in TCI6630K2L and TCI6631K2L.

- $^{(14)}\,$  4 RAC1.2 are available only in TCI6636K2H and TCI6638K2K.

- (15) TCI6630K2L and TCI6631K2L have TAC2.2 instead of TAC2.1 used in others. TAC2.2 has 2 SGCP, 1 FEI and 1 BEI, whereas TAC2.1 had 6 SGCP, 3 FEI and 1 BEI

- <sup>(16)</sup> 6 FFTC are available only in TCI6636K2H and TCI6638K2K.

- <sup>(17)</sup> 4 TCP3d are available only in TCI6636K2H and TCI6638K2K.

- <sup>(18)</sup> 8 VCP2 are available only in TCI6630K2H and TCI6638K2K.

- <sup>(19)</sup> TCI6631 has no RSA1, TCI6630 has 8 RSA1 and TCI6636K2H and TCI6638K2K have 16 RSA1.

- $^{(20)}\,\,$  5 EDMA3CC are available only in TCI6636K2H and TCI6638K2K.

- <sup>(21)</sup> 14 EDMA3TCs are available only in TCI6636K2H and TCI6638K2K.

- <sup>(22)</sup> NetCP 1.5 is available only in TCI6630K2L and TCI6631K2L.It has the PA1.5 and SA1.3 whereas others use PA1.1 and SA1.2

### Table 1. Architectural Differences Between KeyStone I and KeyStone II Devices (continued)

| IP Block                                     | Block KeyStone I KeyStone II Changed or Added Functionality) |                            | New SW to<br>Support New<br>HW Block                                                                                                                                             |                                                        |

|----------------------------------------------|--------------------------------------------------------------|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|

| Gigabit Ethernet Switch<br>Subsystem (SGMII) | 1 x 2                                                        | 1 x 4                      | Support for 4 ports vs. 2 ports                                                                                                                                                  | Required<br>support for new<br>time sync<br>operations |

| Peripherals                                  | ••                                                           |                            |                                                                                                                                                                                  |                                                        |

| AIF2 <sup>(23)</sup>                         | 1 x 6                                                        | 1 x 6                      | 1) Changes needed to support additional AT events (from 11 to 24 events)                                                                                                         |                                                        |

|                                              |                                                              |                            | 2) SerDes related changes to MMRs                                                                                                                                                |                                                        |

| IQNet2                                       | No                                                           | 1x <sup>(24)</sup>         |                                                                                                                                                                                  | Required                                               |

| SRIO                                         | 1 x 4                                                        | 1 x 4 <sup>(25)</sup>      | SerDes related changes to MMRs                                                                                                                                                   |                                                        |

| PCIe                                         | 1 x 2                                                        | 1 x 2, 2x1 <sup>(26)</sup> | SerDes related changes to MMRs                                                                                                                                                   |                                                        |

| HyperLink                                    | 1 x 2                                                        | 2 x 4 <sup>(27)</sup>      | <ol> <li>SerDes related changes to MMRs,</li> <li>Some KeyStone II devices have 2 HyperLink<br/>modules, where as KeyStone I devices have only 1<br/>HyperLink module</li> </ol> |                                                        |

| XGE <sup>(28)</sup>                          | No                                                           | 1 x 2                      |                                                                                                                                                                                  | Required                                               |

| UART                                         | 1x                                                           | 2x, 4x <sup>(29)</sup>     | Completely software compatible                                                                                                                                                   |                                                        |

| SPI                                          | 1x <sup>(30)</sup>                                           | 3x <sup>(31)</sup>         | Support for additional chip selects (4 vs. 2) per SPI module                                                                                                                     |                                                        |

| 12C                                          | 1x                                                           | Зx                         | Completely software compatible                                                                                                                                                   |                                                        |

| GPIO                                         | 1x16,<br>1x32 <sup>(32)</sup>                                | 1x32, 2x32 <sup>(33)</sup> | Support for 32 GPIO pins vs. 16 pins                                                                                                                                             |                                                        |

| Timer64                                      | 8x <sup>(34)</sup>                                           | 14x, 20x <sup>(35)</sup>   | Completely sofware compatible                                                                                                                                                    |                                                        |

| Semaphore                                    | 1x                                                           | 1x                         | <ol> <li>More semaphores added (64 vs. 32)</li> <li>Support for additional cores</li> </ol>                                                                                      |                                                        |

| EMIF16 <sup>(36)</sup>                       | 1x                                                           | 1x                         | Completely sofware compatible                                                                                                                                                    |                                                        |

| USIM <sup>(37)</sup>                         | 1x                                                           | 1x                         | Completely sofware compatible                                                                                                                                                    |                                                        |

| USB3                                         | No                                                           | 1x                         |                                                                                                                                                                                  | Required                                               |

| System Components                            | • • •                                                        |                            | 1                                                                                                                                                                                |                                                        |

| PLL controller + On-chip PLLs                | LL controller + On-chip PLLs 3x 5x                           |                            | 1) one additional PLL for DDR3B and one more for ARM subsystem <sup>(38)</sup>                                                                                                   |                                                        |

|                                              |                                                              |                            | 2) programming identical to DDR3A PLL                                                                                                                                            |                                                        |

| PSC                                          |                                                              |                            | <ol> <li>More power and clock domains added</li> <li>LPSC allocations changed</li> </ol>                                                                                         |                                                        |

|                                              |                                                              |                            | 3) Software needs to be modified to use the respective power/clock domains for peripheral power on and clocking                                                                  |                                                        |

<sup>(23)</sup> AIF2 is available only in TCI6636K2H and TCI6638K2K and KeyStone I devices.

<sup>(24)</sup> IQN2 is available only in TCI6630K2L and TCI6631K2L.

- <sup>(25)</sup> SRIO is not available only in TCI6630K2L and TCI6631K2L.

- <sup>(26)</sup> 2 PCles (with 1 lane) are available only in TCI6630K2I and TCI6631K2L. Others have 1 PCle (with 2 lanes).

- <sup>(27)</sup> 2 HyperLink are available only in TCI6636K2H and TCI6638K2K.

- <sup>(28)</sup> XGE is available only in TCI6636K2H and TCI6638K2K.

- <sup>(29)</sup> 4 UARTs are available only in TCI6630K2L and TCI6631K2L.

- <sup>(30)</sup> KeyStone I SPI supports 2 CSs.

- <sup>(31)</sup> TCI6630K2L and TCI6631K2L support 5 CSs for SPI0 and SPI2 and 3 CSs for SPI1.

- <sup>(32)</sup> 32 GPIOs are available for TMS320TCI6612 and TMS320TCI6614.

- $^{\rm (33)}$  64 GPIOs are available only in TCI6630K2L and TCI6631K2L.

- <sup>(34)</sup> 12 Timers are available for TMS320TCI6612 and TMS320TCI6614.

- <sup>(35)</sup> 20 Timers are available only in TCI6636K2H and TCI6638K2K.

- <sup>(36)</sup> EMIF16 is available only in the following KeyStone I(TMS320TCI6612 and TMS320TCI6614) and KeyStone II devices.

- <sup>(37)</sup> USIM is available only in the following KeyStone I(TMS320TCI6612 and TMS320TCI6614) and KeyStone II devices.

- <sup>(38)</sup> Applicable only for TCI6636K2H and TCI6638K2K.

### Table 1. Architectural Differences Between KeyStone I and KeyStone II Devices (continued)

| IP Block                                     | KeyStone I                          | KeyStone II                                    | Minimal to Moderate SW Changes (MMRs Added /<br>Changed or Added Functionality)                                                                                                          | New SW to<br>Support New<br>HW Block |

|----------------------------------------------|-------------------------------------|------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| BOOTCFG (Chip-level registers)               |                                     |                                                | <ol> <li>New chip-level MMRs added</li> <li>Some existing MMRs also changed (for example no<br/>KICK protection for IPC registers, support for added<br/>cores, and so forth)</li> </ol> |                                      |

| Bootmode                                     |                                     |                                                | Bootmode pin allocations changed                                                                                                                                                         |                                      |

| INTC + GIC (for ARM)                         | 3x or 4x <sup>(39)</sup><br>(INTCs) | 2x, 3x (INTCs)<br>and 1x (GIC) <sup>(40)</sup> | 1) More INTC instantiations         2) Interrupt allocations changed                                                                                                                     |                                      |

| Debug Subsystem + System<br>TETB             | 1x                                  | 1x                                             | Software change needed to support additional cores and added features                                                                                                                    | System TETB is a new HW block        |

| ARM Subsystem ETB (16<br>KB) <sup>(41)</sup> | No                                  | 1x                                             |                                                                                                                                                                                          | Required                             |

| DSP TETB (4 KB)                              | 4x                                  | 8x                                             | Completely software compatible                                                                                                                                                           |                                      |

| Tracer                                       | 16x                                 | 32x                                            | Tracer allocations changed                                                                                                                                                               |                                      |

| MPU                                          | 6x                                  | 16x                                            | MPU allocations changed                                                                                                                                                                  |                                      |

| Security Manager                             | 1x                                  | 1x                                             | Completely software compatible                                                                                                                                                           |                                      |

| Smart Reflex                                 | 1x                                  | 1x, 2x <sup>(42)</sup>                         | Completely software compatible                                                                                                                                                           |                                      |

<sup>(39)</sup> INTC3 is used for routing interrupts to ARM and is available only in TMS320TCI6612 and TMS320TCI6614.

<sup>(40)</sup> 3 INTC are available only for TCI6636K2H and TCI6638K2K.

<sup>(41)</sup> Applicable only for KeyStone II devices.

<sup>(42)</sup> 2 Smart Reflex are available only for TCI6636K2H and TCI6638K2K.

### 1.4 Memory Map

Both KeyStone I and KeyStone II devices feature on-chip internal memories, allowing efficient handling of varied partitions of internal program and data information. Both devices feature several different types of cache memory, allowing significant flexibility in using this memory to enhance algorithm performance. Both devices also provide an on-chip ROM, which contains the bootloader program. The memory map has changed considerably moving from KeyStone I to KeyStone II devices. For more details about the device memory map, see the device-specific data manuals. For KeyStone II devices, the device memory map is viewed differently from the ARM® (ARM A15 CorePac), the DSP CorePacs, and the system masters (SoC level). The view of the device memory map from these different entities is summarized in Table 2.

| Table 2. KeyStone II Memory Map View From ARM, DSP, and System Masters |

|------------------------------------------------------------------------|

|------------------------------------------------------------------------|

| Start Address  | End Address    | ARM View                                        | DSP View (After XMC) <sup>(1)</sup>              | SoC view (After MPAX) <sup>(2)</sup> |

|----------------|----------------|-------------------------------------------------|--------------------------------------------------|--------------------------------------|

| 0x00_0000_0000 | 0x00_0003_FFFF | ARM ROM                                         | DSP Internal                                     | ARM ROM                              |

| 0x00_0004_0000 | 0x00_0100_0000 | Reserved                                        | DSP Internal                                     | Reserved                             |

| 0x00_0100_0000 | 0x00_0100_FFFF | ARM Internal                                    | DSP Internal                                     | Reserved                             |

| 0x00_0101_0000 | 0x00_010F_FFFF | Reserved                                        | DSP Internal                                     | Reserved                             |

| 0x00_0110_0000 | 0x00_0110_FFFF | ARM Internal                                    | DSP Internal                                     | Reserved                             |

| 0x00_0111_0000 | 0x00_01BF_FFFF | Reserved                                        | DSP Internal                                     | Reserved                             |

| 0x00_01C0_0000 | 0x00_20FF_FFFF | CFG/DMA Space                                   | CFG/DMA Space                                    | CFG/DMA Space                        |

| 0x00_2100_0000 | 0x00_2100_01FF | DDR3A CFG <sup>(3)</sup>                        | DDR3A CFG                                        | DDR3A CFG                            |

| 0x00_2100_0200 | 0x00_5FFF_FFF  | CFG/DMA Space                                   | CFG/DMA Space                                    | CFG/DMA Space                        |

| 0x00_6000_0000 | 0x00_7FFF_FFF  | DDR3B(Aliased from<br>0x8000_0000 - 0x9FFF_FFF) | DDR3B (Aliased from<br>0x8000_0000 - 0x9FFF_FFF) | DDR3B                                |

<sup>(1)</sup> For DSP CorePac to access 40 bit address space, the XMC MPAX has to be programmed accordingly

- <sup>(2)</sup> For System masters to access 40 bit address space, the MSMC MPAX has to be programmed accordingly

- (3) DDR3A configuration space access requires re-mapping of 0x2100\_0000 0x2100\_01FF to 0x01\_2100\_0000 0x01\_2100\_01FF using XMC MPAX for DSP CorePac accesses and MSMC MPAX for System master accesses

| Start Address  | End Address    | ARM View             | DSP View (After XMC) <sup>(1)</sup> | SoC view (After MPAX) <sup>(2)</sup> |

|----------------|----------------|----------------------|-------------------------------------|--------------------------------------|

| 0x00_8000_0000 | 0x00_FFFF_FFF  | DDR3B <sup>(4)</sup> | DDR3B                               | DDR3A                                |

| 0x01_2100_0000 | 0x01_2100_01FF | Reserved             | DDR3A CFG                           | DDR3A CFG                            |

| 0x08_0000_0000 | 0x09_FFFF_FFF  | DDR3A                | DDR3A                               | DDR3A                                |

### Table 2. KeyStone II Memory Map View From ARM, DSP, and System Masters (continued)

<sup>(4)</sup> To enable ARM to boot Linux kernel from DDR3A without setting up MMU/LPAE, DDR3A can be mapped into the lower 32 bit address space, by setting the bootstrap pin ddr3a\_map\_en = 1. If this pin is set, the address from 0x00\_8000\_0000 - 0x00\_FFFF\_FFFF will be aliased at 0x08\_0000\_0000 - 0x08\_7FFF\_FFFF

The differences in the device memory map between KeyStone I and KeyStone II devices are shown in Table 3. Some software modifications may be required when migrating applications from KeyStone I devices to KeyStone II devices. For more details about the memory map of individual KeyStone I and KeyStone II devices, see the device-specific data manuals.

### Table 3. KeyStone I to KeyStone II (TCI6638K2K) Memory Map Changes

| Logical 32-E | Bit Address | Physical 40-Bit | Address      |       |                                                  |             |

|--------------|-------------|-----------------|--------------|-------|--------------------------------------------------|-------------|

| Start        | End         | Start           | End          | Bytes | KeyStone II(TCI6638K2K)                          | KeyStone I  |

| 0000 0000    | 0003 FFFF   | 00 0000 0000    | 00 0003 FFFF | 256K  | COREPAC_INTERNAL/<br>BOOT_ROM_ARM <sup>(1)</sup> | Reserved    |

| 0100 0000    | 017F FFFF   | 00 0100 0000    | 00 017F FFFF | 8 M   | COREPAC_INTERNAL <sup>(2)</sup>                  | Reserved    |

| 01D6 8000    | 01D6 807F   | 00 01D6 8000    | 00 01D6 807F | 128   | CPT_L2_4_CFG                                     | CPT_RAC_FEI |

| 01D7 0000    | 01D7 007F   | 00 01D7 0000    | 00 01D7 007F | 128   | CPT_L2_5_CFG                                     | CPT_RAC_CFG |

| 01D7 8000    | 01D7 807F   | 00 01D7 8000    | 00 01D7 807F | 128   | CPT_L2_6_CFG                                     | CPT_TAC_BE  |

| 01D8 0000    | 01D8 007F   | 00 01D8 0000    | 00 01D8 007F | 128   | CPT_L2_7_CFG                                     | Reserved    |

| 01D8 8000    | 01D8 807F   | 00 01D8 8000    | 00 01D8 807F | 128   | CPT_RAC_FEI_CFG                                  | Reserved    |

| 01D9 0000    | 01D9 007F   | 00 01D9 0000    | 00 01D9 007F | 128   | CPT_RAC_CFG1_CFG                                 | Reserved    |

| 01D9 8000    | 01D9 807F   | 00 01D9 8000    | 00 01D9 807F | 128   | CPT_TAC_BE_CFG                                   | Reserved    |

| 01DA 0000    | 01DA 007F   | 00 01DA 0000    | 00 01DA 007F | 128   | CPT_QM_CFG2_CFG                                  | Reserved    |

| 01DA 8000    | 01DA 807F   | 00 01DA 8000    | 00 01DA 807F | 128   | CPT_RAC_CFG2_CFG                                 | Reserved    |

| 01DB 0000    | 01DB 007F   | 00 01DB 0000    | 00 01DB 007F | 128   | CPT_DDR3B_CFG                                    | Reserved    |

| 01DB 8000    | 01DB 807F   | 00 01DB 8000    | 00 01DB 807F | 128   | CPT_BCR_CFG_CFG                                  | Reserved    |

| 01DC 0000    | 01DC 007F   | 00 01DC 0000    | 00 01DC 007F | 128   | CPT_TPCC0_4_CFG                                  | Reserved    |

| 01DC 8000    | 01DC 807F   | 00 01DC 8000    | 00 01DC 807F | 128   | CPT_TPCC1_2_3_CFG                                | Reserved    |

| 01DD 0000    | 01DD 007F   | 00 01DD 0000    | 00 01DD 007F | 128   | CPT_INTC_CFG                                     | Reserved    |

| 01DD 8000    | 01DD 807F   | 00 01DD 8000    | 00 01DD 807F | 128   | CPT_MSMC4_CFG                                    | Reserved    |

| 01DE 0000    | 01DE 007F   | 00 01DE 0000    | 00 01DE 007F | 128   | CPT_MSMC5_CFG                                    | Reserved    |

| 01DE 0080    | 01DE 00FF   | 00 01DE 0080    | 00 01DE 00FF | 128   | CPT_MSMC6_CFG                                    | Reserved    |

| 01DE 0100    | 01DE 017F   | 00 01DE 0100    | 00 01DE 017F | 128   | CPT_MSMC7_CFG                                    | Reserved    |

| 01DE 8000    | 01DE 807F   | 00 01DE 8000    | 00 01DE 807F | 128   | CPT_SPI_ROM_<br>EMIF16_CFG                       | Reserved    |

| 01E8 0000    | 01E8 3FFF   | 00 01E8 0000    | 00 01E8 3FFF | 16K   | ARM_CFG                                          | Reserved    |

| 01E8 4000    | 01E8 43FF   | 00 01E8 4000    | 00 01E8 43FF | 1K    | MSMC_PBIST_CTL                                   | Reserved    |

| 0218 0000    | 021A FFFF   | 00 0218 0000    | 00 021A FFFF | 192k  | Reserved                                         | TAC Control |

| 021C 4000    | 021C 43FF   | 00 021C 4000    | 00 021C 43FF | 1K    | TCP3D_C_CFG                                      | Reserved    |

| 021C 6000    | 021C 63FF   | 00 021C 6000    | 00 021C 63FF | 1K    | TCP3D_D_CFG                                      | Reserved    |

| 021D F000    | 021DF07F    | 00 021D F000    | 00 021DF07F  | 128   | USIM_CFG                                         | Reserved    |

| 021E 0000    | 021E 00FF   | 00 021E 0000    | 00 021E 00FF | 256   | OTP_CFG                                          | TCP3E (8K)  |

| 021F 0800    | 021F 0FFF   | 00 021F 0800    | 00 021F 0FFF | 2K    | FFTC_E_CFG                                       | Reserved    |

| 021F 1000    | 021F 17FF   | 00 021F 1000    | 00 021F 17FF | 2K    | FFTC_F_CFG                                       | Reserved    |

<sup>(1)</sup> This memory region is used for ARM boot ROM at chip-level and CorePac internal space inside CorePac. Where ARM boots from is hardcoded inside ARM IP.

<sup>(2)</sup> Addresses starting at 0x0100 0000 will be used for en\_cfg\_space and 0x0110 0000 will be used for stm space internal to ARM.

# Table 3. KeyStone I to KeyStone II (TCI6638K2K) Memory Map Changes (continued)

| Logical 32-E |                        | Physical 40-Bit |                              |        |                         |                          |

|--------------|------------------------|-----------------|------------------------------|--------|-------------------------|--------------------------|

| •            | End                    | -               | End                          | Buttoo | Keyetene II/TCICC29K2K) | KeyStenel                |

| Start        |                        | Start           |                              | Bytes  | KeyStone II(TCI6638K2K) | KeyStone I               |

| 021F 8000    | 021F 87FF              | 00 021F 8000    | 00 021F 87FF                 | 2K     | FFTC_C_CFG              | Reserved                 |

| 021FC000     | 021F C7FF              | 00 021FC000     | 00 021F C7FF                 | 2K     | FFTC_D_CFG              | Reserved                 |

| 0228 0000    | 0228 007F              | 00 0228 0000    | 00 0228 007F                 | 128    | TIMER8_CFG              | Reserved <sup>(3)</sup>  |

| 0229 0000    | 0229 007F              | 00 0229 0000    | 00 0229 007F                 | 128    | TIMER9_CFG              | Reserved                 |

| 022A 0000    | 022A 007F              | 00 022A 0000    | 00 022A 007F                 | 128    | TIMER10_CFG             | Reserved                 |

| 022B 0000    | 022B 007F              | 00 022B 0000    | 00 022B 007F                 | 128    | TIMER11_CFG             | Reserved                 |

| 022C 0000    | 022C 007F              | 00 022C 0000    | 00 022C 007F                 | 128    | TIMER12_CFG             | Reserved                 |

| 022D 0000    | 022D 007F              | 00 022D 0000    | 00 022D 007F                 | 128    | TIMER13_CFG             | Reserved                 |

| 022E 0000    | 022E 007F              | 00 022E 0000    | 00 022E 007F                 | 128    | TIMER14_CFG             | Reserved                 |

| 022F 0000    | 022F 007F              | 00 022F 0000    | 00 022F 007F                 | 128    | TIMER15_CFG             | Reserved                 |

| 022F 0080    | 022F 00FF              | 00 022F 0080    | 00 022F 00FF                 | 128    | TIMER16_CFG             | Reserved                 |

| 022F 0100    | 022F 017F              | 00 022F 0100    | 00 022F 017F                 | 128    | TIMER17_CFG             | Reserved                 |

| 022F 0180    | 022F 01FF              | 00 022F 0180    | 00 022F 01FF                 | 128    | TIMER18_CFG             | Reserved                 |

| 022F 0200    | 022F 027F              | 00 022F 0200    | 00 022F 027F                 | 128    | TIMER19_CFG             | Reserved                 |

| 0232 0000    | 0232 3FFF              | 00 0232 0000    | 00 0232 3FFF                 | 16K    | PCIE_SERDES_CFG         | GPIO: 02320000 to        |

| 0232 4000    | 0232 5FFF              | 00 0232 4000    | 00 0232 5FFF                 | 8K     | AIF2_SERDES_B4_CFG      | 023200FF. Rest reserved. |

| 0232 6000    | 0232 7FFF              | 00 0232 6000    | 00 0232 7FFF                 | 8K     | AIF2_SERDES_B8_CFG      | -                        |

| 0232 8000    | 0232 8FFF              | 00 0232 8000    | 00 0232 8FFF                 | 4K     | DDR3B_PHY_CFG           |                          |

| 0232 9000    | 0232 9FFF              | 00 0232 9000    | 00 0232 9FFF                 | 4K     | DDR3A_PHY_CFG           |                          |

| 0232 A000    | 0232 AFFF              | 00 0232 A000    | 00 0232 AFFF                 | 4K     | NETCP_SERDES_CFG        |                          |

| 0232 B000    | 0232 BFFF              | 00 0232 B000    | 00 0232 BFFF                 | 4K     | HyperLink0_SERDES_CFG   | _                        |

| 0232 C000    | 0232 CFFF              | 00 0232 D000    | 00 0232 DFFF                 | 4K     | SRIO_SERDES_CFG         | -                        |

| 0232 D000    | 0232 DFFF              | 00 0232 D000    | 00 0232 DFFF                 | 4K     | HyperLink1_SERDES_CFG   | _                        |

| 0232 E000    | 0232 EFFF              | 00 0232 E000    | 00 0232 EFFF                 | 4K     | XGE_SERDES_CFG          | _                        |

| 0232 F000    | 0232 EFFF              | 00 0232 E000    | 00 0232 EFFF                 | 4K     | USB_PHY_CFG             | _                        |

| 0233 0400    | 0232 1111<br>0233 07FF | 00 0232 1 000   | 00 0232 1111<br>00 0233 07FF | 1K     | Smart Reflex 1          | Reserved                 |

| 0234 0000    | 0233 0711<br>0234 00FF | 00 0233 0400    | 00 0233 0711<br>00 0234 00FF | 256    | VCP2_E_CFG              | Reserved                 |

| 0234 0000    | 0234 0011<br>0234 40FF | 00 0234 0000    | 00 0234 0011<br>00 0234 40FF | 256    | VCP2_F_CFG              | Reserved                 |

| 0234 4000    | 0234 40FF              | 00 0234 4000    | 00 0234 40FF                 | 256    | VCP2_C_CFG              | Reserved                 |

|              |                        |                 |                              |        |                         |                          |

| 0234 C000    | 0234 C0FF              | 00 0234 C000    | 00 0234 C0FF                 | 256    | VCP2_H_CFG              | Reserved                 |

| 0238 8000    | 0238 83FF              | 00 0238 8000    | 00 0238 83FF                 | 1K     | MPU5_CFG                | Reserved                 |

| 0238 8400    | 0238 87FF              | 00 0238 8400    | 00 0238 87FF                 | 1K     | MPU6_CFG                | Reserved                 |

| 0238 8800    | 0238 8BFF              | 00 0238 8800    | 00 0238 8BFF                 | 1K     | MPU7_CFG                | Reserved                 |

| 0238 8C00    | 0238 8FFF              | 00 0238 8C00    | 00 0238 8FFF                 | 1K     | MPU8_CFG                | Reserved                 |

| 0238 9000    | 0238 93FF              | 00 0238 9000    | 00 0238 93FF                 | 1K     | MPU9_CFG                | Reserved                 |

| 0238 9400    | 0238 97FF              | 00 0238 9400    | 00 0238 97FF                 | 1K     | MPU10_CFG               | Reserved                 |

| 0238 9800    | 0238 9BFF              | 00 0238 9800    | 00 0238 9BFF                 | 1K     | MPU11_CFG               | Reserved                 |

| 0238 9C00    | 0238 9FFF              | 00 0238 9C00    | 00 0238 9FFF                 | 1K     | MPU12_CFG               | Reserved                 |

| 0238 A000    | 0238 A3FF              | 00 0238 A000    | 00 0238 A3FF                 | 1K     | MPU13_CFG               | Reserved                 |

| 0238 A400    | 0238 A7FF              | 00 0238 A400    | 00 0238 A7FF                 | 1K     | MPU14_CFG               | Reserved                 |

| 0240 0000    | 0243 FFFF              | 00 0240 0000    | 00 0243 FFFF                 | 256K   | Reserved                | debug_SS_config          |

| 0248 0000    | 0248 3FFF              | 00 0248 0000    | 00 0248 3FFF                 | 16K    | ADTF4_CFG               | Reserved                 |

| 0249 0000    | 0249 3FFF              | 00 0249 0000    | 00 0249 3FFF                 | 16K    | ADTF5_CFG               | Reserved                 |

| 024A 0000    | 024A 3FFF              | 00 024A 0000    | 00 024A 3FFF                 | 16K    | ADTF6_CFG               | Reserved                 |

| 024B 0000    | 024B 3FFF              | 00 024B 0000    | 00 024B 3FFF                 | 16K    | ADTF7_CFG               | Reserved                 |

<sup>(3)</sup> Timers 8-11 are applicable only for TMS320TCI6614 and TMS320TCI6612

# Table 3. KeyStone I to KeyStone II (TCI6638K2K) Memory Map Changes (continued)

| Logical 32-E | Bit Address | Physical 40-Bit | Address      |       |                            |                                                          |

|--------------|-------------|-----------------|--------------|-------|----------------------------|----------------------------------------------------------|

| Start        | End         | Start           | End          | Bytes | KeyStone II(TCI6638K2K)    | KeyStone I                                               |

| 024C 0800    | 024C 0BFF   | 00 024C 0800    | 00 024C 0BFF | 1K    | PBIST_CTL1_CFG             | Reserved                                                 |

| 0250 0000    | 0250 7FFF   | 00 0250 0000    | 00 0250 7FFF | 32K   | SEC_MGR_CFG                | SEC_CTL (0250 0000 to<br>0250 007F, Rest is<br>reserved) |

| 0252 0000    | 0252 03FF   | 00 0252 0000    | 00 0252 03FF | 1K    | Reserved                   | SEC_KEY_MGR                                              |

| 0253 0400    | 0253 047F   | 00 0253 0400    | 00 0253 047F | 128   | I2C1_CFG                   | Reserved                                                 |

| 0253 0800    | 0253 087F   | 00 0253 0800    | 00 0253 087F | 128   | I2C2_CFG                   | Reserved                                                 |

| 0253 0C00    | 0253 0C3F   | 00 0253 0C00    | 00 0253 0C3F | 64    | UART0_CFG                  | Reserved                                                 |

| 0253 1000    | 0253 103F   | 00 0253 1000    | 00 0253 103F | 64    | UART1_CFG                  | Reserved                                                 |

| 0254 0000    | 0255 FFFF   | 00 0254 0000    | 00 0255 FFFF | 128K  | BCP_CFG                    | UART (up to 0254003F,<br>Rest is reserved)               |

| 0256 0000    | 0257 FFFF   | 00 0256 0000    | 00 0257 FFFF | 128K  | GIC_CFG                    | Reserved                                                 |

| 0258 0000    | 025F FFFF   | 00 0258 0000    | 00 025F FFFF | 512K  | TAC_CFG                    | Reserved                                                 |

| 0260 BF00    | 0260 BFFF   | 00 0260 BF00    | 00 0260 BFFF | 256   | GPIO_CFG                   | Reserved                                                 |

| 0268 0000    | 026F FFFF   | 00 0268 0000    | 00 026F FFFF | 512K  | USB_MMR_CFG                | Reserved                                                 |

| 0270 8000    | 0270 FFFF   | 00 0270 8000    | 00 0270 FFFF | 32K   | EDMA4_CC_CFG               | Reserved                                                 |

| 0272 8000    | 0272 FFFF   | 00 0272 8000    | 00 0272 FFFF | 32K   | EDMA3_CC_CFG               | Reserved                                                 |

| 027B 0000    | 027B 03FF   | 00 027B 0000    | 00 027B 03FF | 1K    | EDMA3_TC0_CFG              | Reserved                                                 |

| 027B 8000    | 027B 83FF   | 00 027B 8000    | 00 027B 83FF | 1k    | EDMA3_TC1_CFG              | Reserved                                                 |

| 027B 8400    | 027B 87FF   | 00 027B 8400    | 00 027B 87FF | 1K    | EDMA4_TC0_CFG              | Reserved                                                 |

| 027B 8800    | 027B 8BFF   | 00 027B 8800    | 00 027B 8BFF | 1K    | EDMA4_TC1_CFG              | Reserved                                                 |

| 027C 0000    | 027C 03FF   | 00 027C 0000    | 00 027C 03FF | 1K    | BCR_CFG                    | Reserved                                                 |

| 027D 4000    | 027D 7FFF   | 00 027D 4000    | 00 027D 7FFF | 16K   | TBR_SYS_ARM                | Reserved                                                 |

| 0281 0000    | 0281 3FFF   | 00 0281 0000    | 00 0281 3FFF | 16k   | TETB4_CFG                  | Reserved                                                 |

| 0282 0000    | 0282 3FFF   | 00 0282 0000    | 00 0282 3FFF | 16k   | TETB5_CFG                  | Reserved                                                 |

| 0283 0000    | 0283 3FFF   | 00 0283 0000    | 00 0283 3FFF | 16k   | TETB6_CFG                  | Reserved                                                 |

| 0284 0000    | 0284 3FFF   | 00 0284 0000    | 00 0284 3FFF | 16k   | TETB7_CFG                  | Reserved                                                 |

| 0285 0000    | 0285 7FFF   | 00 0285 0000    | 00 0285 7FFF | 32k   | DBG_TBR_SYS                | TETB4 (system trace)                                     |

| 02A0 0000    | 02AF FFFF   | 00 02A0 0000    | 00 02AF FFFF | 1M    | QM_CFG1 and QM_CFG2        | QM_SS_CFG                                                |

| 02B0 0000    | 02BF FFFF   | 00 02B0 0000    | 00 02BF FFFF | 1M    | QM_CFG2 Linking RAM        | Reserved                                                 |

| 02C0 0000    | 02C5 FFFF   | 00 02C0 0000    | 00 02C5 FFFF | 384K  | RAC_C_CFG                  | Reserved                                                 |

| 02C8 0000    | 02CD FFFF   | 00 02C8 0000    | 00 02CD FFFF | 384K  | RAC_D_CFG                  | Reserved                                                 |

| 02F0 0000    | 02FF FFFF   | 00 02F0 0000    | 00 02FF FFFF | 1M    | XGE_CFG                    | Reserved                                                 |

| 0300 0000    | 030F FFFF   | 00 0300 0000    | 00 030F FFFF | 1M    | DBG_CFG                    | Reserved                                                 |

| 0C00 0000    | 0C1F FFFF   | 00 0C00 0000    | 00 0C1F FFFF | 2M    | MSMC SRAM                  | MSMC SRAM                                                |

| 0C20 0000    | 0C5F FFFF   | 00 0C20 0000    | 00 0C5F FFFF | 4M    | MSMC SRAM                  | Reserved                                                 |

| 1480 0000    | 148F FFFF   | 00 1480 0000    | 00 148F FFFF | 1M    | COREPAC4_SDMA - L2<br>SRAM | Reserved                                                 |

| 14E0 0000    | 14E0 7FFF   | 00 14E0 0000    | 00 14E0 7FFF | 32K   | COREPAC4 L1P SRAM          | Reserved                                                 |

| 14F0 0000    | 14F0 7FFF   | 00 14F0 0000    | 00 14F0 7FFF | 32K   | COREPAC4 L1D SRAM          | Reserved                                                 |

| 1580 0000    | 158F FFFF   | 00 1580 0000    | 00 158F FFFF | 1M    | COREPAC5_SDMA - L2<br>SRAM | Reserved                                                 |

| 15E0 0000    | 15E0 7FFF   | 00 15E0 0000    | 00 15E0 7FFF | 32K   | COREPAC5 L1P SRAM          | Reserved                                                 |

| 15F0 0000    | 15F0 7FFF   | 00 15F0 0000    | 00 15F0 7FFF | 32K   | COREPAC5 L1D SRAM          | Reserved                                                 |

| 1680 0000    | 168F FFFF   | 00 1680 0000    | 00 168F FFFF | 1M    | COREPAC6_SDMA - L2<br>SRAM | Reserved                                                 |

| 16E0 0000    | 16E0 7FFF   | 00 16E0 0000    | 00 16E0 7FFF | 32K   | COREPAC6 L1P SRAM          | Reserved                                                 |

| 16F0 0000    | 16F0 7FFF   | 00 16F0 0000    | 00 16F0 7FFF | 32K   | COREPAC6 L1D SRAM          | Reserved                                                 |

# Table 3. KeyStone I to KeyStone II (TCI6638K2K) Memory Map Changes (continued)

| Logical 32-         | Bit Address | Physical 40-Bit | Address      |       |                            |                                                                         |  |

|---------------------|-------------|-----------------|--------------|-------|----------------------------|-------------------------------------------------------------------------|--|

| Start               | End         | Start           | End          | Bytes | KeyStone II(TCI6638K2K)    | KeyStone I                                                              |  |

| 1780 0000           | 178F FFFF   | 00 1780 0000    | 00 178F FFFF | 1M    | COREPAC7_SDMA - L2<br>SRAM | Reserved                                                                |  |

| 17E0 0000           | 17E0 7FFF   | 00 17E0 0000    | 00 17E0 7FFF | 32K   | COREPAC7 L1P SRAM          | Reserved                                                                |  |

| 17F0 0000           | 17F0 7FFF   | 00 17F0 0000    | 00 17F0 7FFF | 32K   | COREPAC7 L1D SRAM          | Reserved                                                                |  |

| 2020 0000           | 205F FFFF   | 00 2020 0000    | 205F FFFF    | 4M    | Reserved                   | RAC_B Data (FEI)                                                        |  |

| 2070 0000           | 207F FFFF   | 00 2070 0000    | 00 207F FFFF | 1M    | TCP3D_C_DATA               | Reserved                                                                |  |

| 2090 0000           | 209F FFFF   | 00 2090 0000    | 00 209F FFFF | 1M    | TCP3D_D_DATA               | TCP3E Data (2090 0000 to<br>2090 3FFF, Rest is<br>reserved)             |  |

| 20BF 0000           | 20BF FFFF   | 00 20BF 0000    | 00 20BF FFFF | 64K   | Reserved                   | SPI (20BF 0000 to 20BF<br>01FF, Rest is Reserved)                       |  |

| 2100 0000           | 2100 03FF   | 00 2100 0000    | 00 2100 03FF | 1K    | Reserved                   | DDR3-EMIF Config                                                        |  |

| 2100 0400           | 2100 05FF   | 00 2100 0400    | 00 2100 05FF | 512   | SPI0 Slave                 | Reserved                                                                |  |

| 2100 0600           | 2100 07FF   | 00 2100 0600    | 00 2100 07FF | 512   | SPI1 Slave                 | Reserved                                                                |  |

| 2100 0800           | 2100 09FF   | 00 2100 0800    | 00 2100 09FF | 512   | SPI2 Slave                 | Reserved                                                                |  |

| 2100 0A00           | 2100 0AFF   | 00 2100 0A00    | 00 2100 0AFF | 256   | EMIF16_CONFIG              | Reserved                                                                |  |

| 2101 0000 2101 01FF |             | 01 2101 0000    | 01 2101 01FF | 512   | DDR3A_CONFIG               | Reserved                                                                |  |

| 2102 0000           | 2103 FFFF   | 00 2102 0000    | 00 2103 FFFF | 128K  | DDR3B_CONFIG               | Reserved                                                                |  |

| 2140 0100           | 2140 01FF   | 00 2140 0100    | 00 2140 01FF | 256   | HyperLink1_CONFIG          | Reserved                                                                |  |