# Electrostatic Discharge (ESD) Protective Semiconductor Packing Materials and Configurations

Cles Troxtell and James Huckabee

Standard Linear & Logic

#### ABSTRACT

The Texas Instruments Standard Linear & Logic (SLL) Business Group uses an industry-recognized material system to ensure that semiconductor devices are adequately protected from electrostatic discharge (ESD) damage during shipping and distribution. Packing materials are selected and tested in accordance with internal specifications that meet or exceed current industry standards. The methods employed ensure correct component materials are used at each factory location. End users of the standard components often need to peruse many TI and industry publications to understand the ESD-protective configurations. This application report documents the tape-and-reel ESD configurations and provides a cogent explanation of the methods employed to test, evaluate, and deploy proper ESD-protective packing-material configurations.

#### Contents

| Introduction                                                              | 3  |

|---------------------------------------------------------------------------|----|

| Background                                                                | 3  |

| Standards for Protection of Devices from ESD During Shipping and Handling | 3  |

| Specific ESD Requirements for Packing Materials                           | 4  |

| Stick Magazine                                                            | 4  |

|                                                                           | 5  |

| Tape and Reel                                                             |    |

| Typical ESD-Protective Packing-Material Configurations                    | 6  |

| Stick Magazine                                                            | 6  |

| Tray                                                                      | 7  |

| Tape and Reel                                                             | 8  |

| Static Voltage Test on Loaded Tape-and-Reel Material                      | 9  |

| Test Requirements for Material Properties Confirmation                    |    |

| Conclusions                                                               | 14 |

| Acknowledgments                                                           | 14 |

| References                                                                | 14 |

| Glossary                                                                  | 15 |

Trademarks are the property of their respective owners.

### List of Figures

| 1  | Shipping Magazine                                        | 5  |

|----|----------------------------------------------------------|----|

| 2  | Matrix Tray With Devices in Place                        | 5  |

| 3  | Typical Reel Loaded With Carrier Tape                    | 6  |

| 4  | Bag/Magazine Packing Example                             | 7  |

| 5  | Tray Packing-Material Example                            | 7  |

| 6  | Tape-and-Reel Packaging Example                          | 8  |

| 7  | Tape-and-Reel Configuration                              | 9  |

| 8  | Six Locations Used to Expose the Units to a ±20-kV Field | 10 |

| 9  | Charged-Plate Placement                                  | 10 |

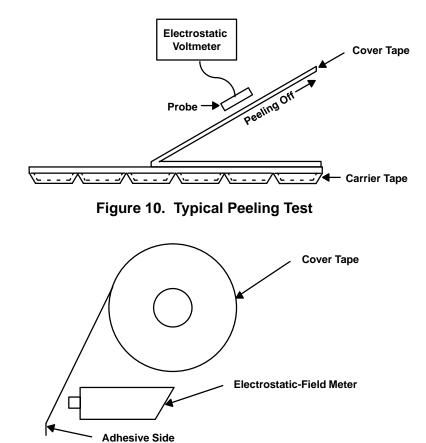

| 10 | Typical Peeling Test                                     | 11 |

| 11 | Typical Unrolling Test                                   | 11 |

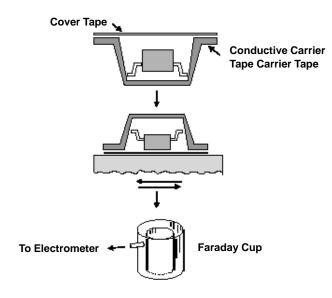

| 12 | Typical Cover-Tape Charge-Generation Test                | 12 |

### List of Tables

| 1 | Measured Surface Resistivity of Carrier Tape | 13 |

|---|----------------------------------------------|----|

| 2 | Static Properties                            | 13 |

## Introduction

The purpose of this application report is to describe in detail the methods used to test, evaluate, and deploy proper packing materials that protect against electrostatic discharge (ESD) damage to semiconductor devices. This application report provides customers with answers to the most frequently asked questions and allows them to review different ESD-protective packing configurations and how those configurations apply to the devices they receive and use.

ESD sources addressed are those of the environment and ESD that might be created by interactions between the packing material and the environment or devices the material contains.

## Background

The invention of the transistor, and later, the integrated circuit, led to the development of improved methods for packing, shipping, and handling of electronic devices. The semiconductor design and manufacturing process often results in specific devices having varying degrees of susceptibility to damage from ESD. Manufacturers must design their assembly processes to ensure that the devices are protected from ESD during the manufacturing process. Additionally, the materials used to pack the devices for delivery to customers must not only adequately protect the devices mechanically, but also prevent damage from inadvertent exposures to high-intensity static fields.

## Standards for Protection of Devices from ESD During Shipping and Handling

The electronics industry has published accepted standards to ensure reasonable conformance among multiple manufacturers of devices.

The general requirements for packing containers are presented in EIA-383, Preparation for Delivery of Electrical and Electronic Components.

EIA-541 (June 24, 1988), Packaging Material Standards for ESD Sensitive Items, provides general and specific requirements for ESD properties of packing material. General requirements for maintaining antistatic and resistivity properties of packing materials, including conditions for verification of ESD properties of the packing materials, are presented.

Specific technical requirements for packing materials for magazines, bags and pouches, flexible cushioning materials, chipboard and corrugated cartons and boxes, loose filled, small molded and irregular-shaped materials, rigid foams, carrier foam, and lead-insertion foam are identified. JESD625-A (December 1999), Requirements for Handling Electrostatic-Discharge-Sensitive (ESDS) Devices, provides the minimum requirements for ESD-control methods and materials used to protect electronic devices that are susceptible to damage, including degradation of performance, from electrostatic discharge.

Together, EIA-541 and JESD625-A detail the ESD requirements from the earliest steps in the assembly process to the final packing, shipping, and handling of the finished device.

Texas Instruments internal ESD specification (QSS 014-001) is based on the requirements of JESD625 and references EIA-541.

# Specific ESD Requirements for Packing Materials

Two ESD properties must be exhibited by packing materials:

- Provide ESD protection

- Limit triboelectric charging to levels that do not result in device damage

ESD protection must be a barrier or enclosure that limits penetration of an electrostatic field so that its effects are attenuated sufficiently to prevent damage to the contained devices. These material properties are commonly called shielding.

Triboelectric charging must be prevented by using materials that minimize the charge when rubbed against, or separated from, themselves or similar materials. These material properties are commonly called antistatic.

JESD625-A requires that "All ESDS devices shall be packed in an ESD protective packaging when not at an ESD protected area or workstation," and further states that "Packing and filler materials for ESDS devices shall be antistatic or static dissipative."

The packing materials that provide ESD protection for the devices fall into two general categories that are defined in EIA-383. The unit container and the first-level intermediate container are discussed in this report. These containers incorporate all the necessary ESD protection for the devices. In addition, filler or dunnage can be included, as needed, in either of the containers.

The unit container has intimate contact with the device package body and/or leads. In most cases, an automated pick-and-place process places the device is in its container.

Texas Instruments uses several different containers, which are described in the following paragraphs.

#### **Stick Magazine**

The stick magazine (also called shipping tube) was developed in the early days of the IC industry. The magazine is used in the manufacturing plant and for transport/storage from the manufacturer of the electronic devices to the customer. Magazines also are used to feed devices to automatic placement machines for surface and through-hole board mounting. Multiple stick magazines are placed in next-level intermediate containers (boxes or bags) in standard packing quantities. Figure 1 shows an example of a stick magazine.

Magazines are constructed of rigid, clear or translucent polyvinylchloride (PVC) material that is extruded as applicable standard outlines that meet current industry standards. The magazine protects the device during shipping and handling. The magazine dimensions provide proper device location and orientation for standard industry automated assembly equipment.

As extruded, PVC is an insulator and is subject to triboelectric charging. The extruded magazines receive a surface treatment to lower the surface resistivity of the PVC. EIA-541 defines a static dissipative material as having a surface resistivity equal to or greater than  $1.0 \times 10^5 \Omega$  per square, but less than  $1.0 \times 10^{12} \Omega$  per square.

Figure 1. Shipping Magazine

Magazine manufacturers coat individual tubes with an antistatic solution, usually by dipping the tubes in a liquid solution then drying them.

End pins or end plugs retain devices in the magazine. The pins and plugs are PVC and are treated to ensure that surface resistivity is within the static-dissipative range.

#### **Matrix Tray**

Matrix trays are constructed of carbon powder or carbon-fiber materials that are selected based on the maximum temperature rating of the specific tray. TI trays that are designed for use with devices that require exposure to high temperatures (moisture-sensitive devices) have temperature ratings of 150°C, or more.

Trays are molded into rectangular JEDEC-standard outlines containing matrices of uniformly spaced pockets. The pocket cradles the device for protection during shipping and handling. The spacing provides exact device locations for standard industry automated-assembly equipment used for pick-and-place board-assembly processes. Figure 2 is an example of a typical matrix tray.

Figure 2. Matrix Tray With Devices in Place

### Tape and Reel

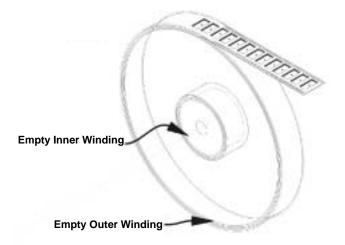

The tape-and-reel configuration is used for transport/storage from the manufacturer of the devices to the customer, and for use in the customer's manufacturing plant (see Figure 3). The configuration is designed for feeding devices to automatic-placement machines for surface mounting on board assemblies. The configuration can be used for all SMT packages and provides device lead isolation during shipping, handling, and processing. The complete configuration consists of a carrier tape with sequential individual cavities that each holds one device, and a cover tape sealed onto the carrier tape to retain the devices in the cavity. In most cases, single reels of devices are inserted into intermediate boxes prior to shipping.

## **Typical ESD-Protective Packing-Material Configurations**

#### Stick Magazine

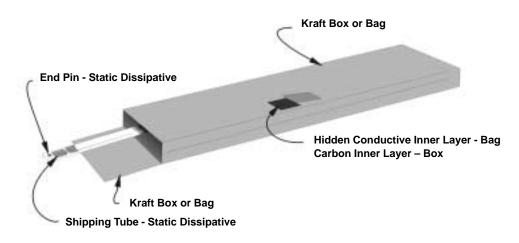

Individual devices are inserted into single magazines and secured with appropriate end pins or plugs. Then, multiple magazines are inserted into the intermediate container—in this case, a two-layer carbon-lined bag.

Protection from ESD is provided by ensuring that packing materials in proximity to the devices are not static generative and the entire intermediate container forms a Faraday shield to protect all the enclosed devices from external static voltages. In this configuration, the magazine, end pins, and inner surface of the bag are static-dissipative surfaces. Surface resistivity for these materials is specified to be within the range of  $1 \times 10^5 \Omega$  per square to  $1 \times 10^{12} \Omega$  per square. The static shield is formed by applying a carbon-based conductive coating to the hidden inner layer of the two-layer bag. The conductive coating has a maximum surface resistivity of  $1 \times 10^4 \Omega$  per square. Figure 4 shows the basic magazine packing-material configuration.

Some devices shipped in magazines are moisture sensitive. Magazines containing moisture-sensitive devices are placed in a moisture-barrier bag, then inside a box. The barrier bag also contains a metallized film that provides static shielding protection. The intermediate box is corrugated kraft material with a conductive carbon inner liner.

Figure 4. Bag/Magazine Packing Example

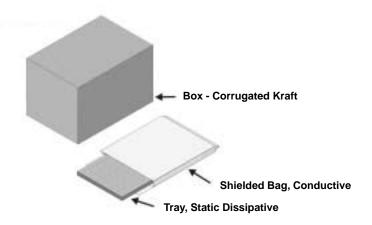

#### Tray

Individual devices are loaded into single trays. Loaded trays are then stacked to form standard multiples for packing. Typical multiples are five or ten loaded trays. An empty tray is placed on the topmost position of the stacked trays as a cover tray. The trays are then bound together and placed in a bag. The bag is sealed, and the assembly is placed in an intermediate container.

Protection from ESD is provided by ensuring that packing materials in proximity to the devices are not static generative and the entire intermediate container forms a shield sufficient to protect all the enclosed devices from external static voltages. In this configuration, the trays and bag inner surface are static dissipative. Surface resistivity for these materials is specified to be within the range of  $1 \times 10^5 \Omega$  per square to  $1 \times 10^{12} \Omega$  per square. The static shield is formed (for all moisture-sensitive devices) by a metallized sheet between the plastic layers. The metallized sheeting is conductive. The plastic surfaces of the bag (inner and outer) are static dissipative. Figure 5 illustrates the devices of the basic tray packing-material configuration.

Figure 5. Tray Packing-Material Example

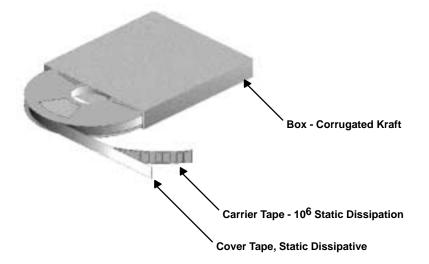

### Tape and Reel

One device is loaded into each cavity of the carrier tape. The loaded pockets are then sealed with a cover tape and the sealed assembly is wound onto a reel. The loaded reel is then placed into an intermediate container (see Figure 6). Tape-and-reel assemblies that contain moisture-sensitive devices are placed in a shielded bag prior to insertion into the intermediate container.

Figure 6. Tape-and-Reel Packaging Example

Protection from ESD is provided by ensuring that the packing materials in proximity to the devices are not static generative and the entire intermediate container forms a sufficient shield to protect all the enclosed devices from external static voltages. In this configuration, the carrier tape is  $1 \times 10^6 \Omega$  per square, and the reel and cover tape are static dissipative. The product is shipped with an extra-long innermost winding of empty static-dissipative carrier tape at the hub of the reel, (trailer) and an extra-long outermost winding of empty static-dissipative carrier tape, (leader) fully surrounding the inner and outer layer of devices, thus forming a shield to adequately protect the devices (see Figure 7).

TI internal tests have confirmed the shielding effects of the tape-and-reel configuration as described in previous paragraphs. The test procedure is described in the following paragraphs.

## Static Voltage Test on Loaded Tape-and-Reel Material

The devices were tested, then exposed to Phase II electrostatic stress. After testing, the units were returned to product engineering for postexposure electrical testing. All devices passed the postexposure testing.

Test elements and materials were:

- Test Plan Overview

- Phase I Prestress Electrical Test

- Phase II Stress Exposure

- Phase III Poststress Electrical Test

- Purpose

- Evaluate static-shielding properties

- Carrier Tape: C-PAK BC1010/1020

- Cover Tape: C-PAK type CP

- Equipment/Materials

- 6-in. × 6-in. aluminum plate (Pinion SA 1)

- High-voltage power supply (Spellman CZE1000R)

- DVM (Fluke 11)

- High-voltage probe (Fluke)

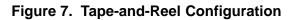

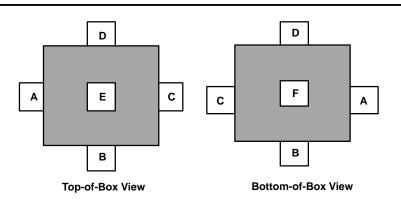

Phase II stress exposure tests, in which  $\pm 20$  kV was applied to a metallic plate placed at several locations on the box, are described in the following paragraphs (see Figure 8).

The charged plate was placed at location E (top of box) (see Figure 8). Then, the box was inverted and the plate placed at location F (see Figure 8). The charged plate was then placed vertical and lined up with the box edge (see A, B, C, and D, Figure 8). The box was then rotated so that each side (sides A-D) was exposed to the stress voltage (see Figure 9). At each exposure, the plate was biased to +20 kV for one minute. Then, the plate was biased to -20 kV for one minute. After exposure to both positive and negative static voltages, the next test point was exposed in the same manner.

Figure 8. Six Locations Used to Expose the Units to a  $\pm$ 20-kV Field

Figure 9. Charged-Plate Placement

Figure 9 shows the test setup used to expose devices in tape-and-reel packing to a 20-kV field. The metallic plate is 6-in.-square aluminum. The high-voltage power supply is not shown in configuration B.

Additionally, internal tests similar to those described previously have demonstrated that the packing method provides an electrostatic shield that is 95% efficient. The carrier tape has a surface resistivity between  $10^6 \Omega$  and  $10^7 \Omega$ . Tests have shown that with a 4-kV charge against the packing box (configurations A or B, Figure 9), less than 200 V is detected in the carrier-tape pocket.

#### **Test Requirements for Material Properties Confirmation**

Texas Instruments internal specifications require that tape-and-reel material ESD properties be verified. A summary of the requirements is included in the following paragraphs.

The surface resistivity of carrier tape-and-reel material is determined by measuring the resistance between two square electrodes spaced one square apart. Measured resistance (R) can be converted to surface resistivity (P) by using equation 1.

$P = K \times R$

where

K = 1.6

The antistatic property of the cover tape is determined by measuring the electrostatic voltage in the cover tape and the charge on the device contacting the cover tape.

Test results should be within these limits:

- The carrier tape (pocket areas) and reel materials (outer surface) used with any ESD-sensitive device shall have a surface resistivity of  $10^4 \Omega$  per square but < $10^{11} \Omega$  per square.

- A cover tape must measure <ABS (180) V in unrolling and peeling tests (see Figures 10 and 11).

Figure 11. Typical Unrolling Test

- A cover tape must generate:

- QM < 0.42 nC per square cm ( 2.7 nC per square inch ) of the footprint area on the devices (see Figure 12)

- QM < 0.64 nC on the test devices in a 1-minute simulated vibration test (see Figure 12)

#### Figure 12. Typical Cover-Tape Charge-Generation Test

- Typical measured values for TI tape-and-reel material

- Reel surface resistivity 1  $\times$  10<sup>7</sup>  $\Omega$  per square through 1  $\times$  10<sup>11</sup>  $\Omega$  per square (measured at TI)

- Resistance range can vary due to multiple suppliers.

- Carrier-tape surface resistivity (Courtesy of CPAK)

- Measure surface resistivity of carrier tape using the method based on AT&T procedure (see Table 1).

- Instrument: Hioki 3119 Digital Megaohm Meter Hi-tester

- Cover tape (see Table 2) (courtesy of Sumicarrier)

| TEOT         | CPAK CARRIER TAPE<br>SPECIFICATION: >10 <sup>4</sup> BU | SO20W - B3 MATERIAL<br>T < 10 <sup>11</sup> Ω PER SQUARE |  |

|--------------|---------------------------------------------------------|----------------------------------------------------------|--|

| TEST<br>ITEM | AIRCON ROOM (22°C/46% RH)                               | CHAMBER (25°C/9.8% RH)                                   |  |

|              | SURFACE RESISTIVITY<br>(Ω PER SQUARE)                   | SURFACE RESISTIVITY<br>( $\Omega$ PER SQUARE)            |  |

| 1            | 502,400                                                 | 1,416,000                                                |  |

| 2            | 568,000                                                 | 1,200,000                                                |  |

| 3            | 873,600                                                 | 1,392,000                                                |  |

| 4            | 777,600                                                 | 1,344,000                                                |  |

| 5            | 77,920                                                  | 124,800                                                  |  |

| Min          | 77,920                                                  | 124,800                                                  |  |

| Max 873,600  |                                                         | 1,416,000                                                |  |

| Avg 559,904  |                                                         | 1,095,360                                                |  |

|              |                                                         |                                                          |  |

| Avg          | $5.6 	imes 10^5 \ \Omega$ per square                    | $1.1 	imes 10^6 \Omega$ per square                       |  |

### Table 1. Measured Surface Resistivity of Carrier Tape

### Table 2. Static Properties

| STATIC PROPERTIES                     |         | METHOD         | CSL-Z7302            | UNIT     |

|---------------------------------------|---------|----------------|----------------------|----------|

| Surface resistivity                   | PET     | JIS K6911      | $5.0 \times 10^{10}$ | Ologuara |

|                                       | Sealant | ASTM D257      | 1.1×10 <sup>9</sup>  | Ω/square |

| Static decay time                     | PET     | MIL-B-81705C   | 0.03                 | <u> </u> |

|                                       | Sealant | (SPEC - < 2.0) | 0.02                 | S        |

| Triboelectric charge                  |         | SB Method 1    | 0.294                | nC       |

| Peel electrostatic charge             |         | SB Method 2    | 50                   | V        |

| Electrostatic charge during unrolling |         | Method 3       | 75                   | V        |

## Conclusions

Texas Instruments has an internal ESD handling specification (QSS 014-001) that is a mirror image of EIA-625, Requirements for Handling ESD Devices.

TI provides shielding protection against electrostatic fields on products we ship by using either a shielding bag, a carbon-coated box, or tape and reel inside a box, with one complete last turn of empty carrier tape on the reel. This provides shielding material completely surrounding all devices in the reel.

TI has shipped billions of units in this manner for more than ten years without any ESD problems related to packing methods.

ESD shielding is a relative term and no present industry ESD specification defines what shielding efficiency is required. The intent of EIA-625 referencing EIA-541 for shielding is to provide the test method for conducting a shielding test, rather than specify that the surface resistivity must be  $10^4 \Omega$  or less.

The effectiveness of shielding, rather than the measurement of the material characteristics, is important.

## Acknowledgments

- 1. CPAK, PTE, ESD Characteristics of Carrier Tape

- 2. Sumicarrier, PTE, ESD Characteristics of Cover Tape

- 3. Jim Hubbell, who supplied illustrations of TI standard packing configurations

### References

- 1. Oscar Trevino, ESD Test Plan for TI Devices (Phase II Testing)

- 2. Don Denton, ESD Position Paper, TI to Solectron, 4-9-1998.

- 3. JESD625-A, Requirements for Handling Electrostatic-Discharge-Sensitive (ESDS) Devices

- 4. EIA-383, Preparation for Delivery of Electrical and Electronic Components

- 5. EIA-541, Packaging Material Standards for ESD Sensitive Items

- 6. QSS 014-001, Handling Requirements for Electrostatic-Discharge (ESD) Sensitive Devices and Assemblies

## Glossary

ESD – Electrostatic discharge

Antistatic – The property of material that inhibits triboelectric charging.

Static-dissipative material – A material having a surface resistance between 1  $\times$  10  $^5$   $\Omega$  and 1  $\times$  10  $^{11}$   $\Omega$

Conductive material – A material that has a surface resistivity <  $1 \times 10^5 \Omega$  per square.

- Electrostatic-discharge susceptibility (sensitivity) or ESDS The lowest level of ESD that produces changes in device characteristics such that the device fails to meet its specified characteristics.

- Electrostatic shielding A barrier or enclosure that limits the penetration of an electrostatic field so that its effects do not reach the stored or contained devices and produce damage.

- Triboelectric charging The generation of electrostatic charges when two pieces of material in intimate contact are separated (where one, or both, is an insulator).

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third–party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Mailing Address:

Texas Instruments Post Office Box 655303 Dallas, Texas 75265

Copyright © 2002, Texas Instruments Incorporated