SGBS310A - SEPTEMBER 1996 - REVISED APRIL 1998

- Free-Running CLKA and CLKB Can Be Asynchronous or Coincident

- Two Independent 512 × 36 Clocked FIFOs Buffering Data in Opposite Directions

- Mailbox-Bypass Register for Each FIFO

- Programmable Almost-Full and Almost-Empty Flags

- Microprocessor Interface Control Logic

- IRA, ORA, AEA, and AFA Flags Synchronized by CLKA

- Released as DESC SMD (Standard Microcircuit Drawing) 5962-9562801QYA

- IRB, ORB, AEB, and AFB Flags Synchronized by CLKB

- Low-Power 0.8-μm Advanced CMOS Technology

- Supports Clock Frequencies up to 50 MHz

- Fast Access Times of 13 ns

- Packaged in 132-Pin Ceramic Quad Flat Package

## description

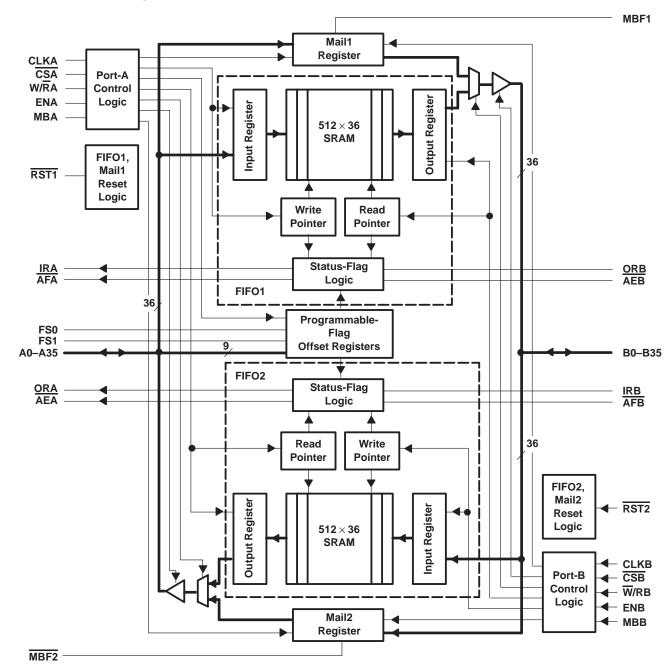

The SN54ACT3632 is a high-speed, low-power CMOS clocked bidirectional FIFO memory. It supports clock frequencies up to 50 MHz and has read access times as fast as 11 ns. Two independent  $512 \times 36$  dual-port SRAM FIFOs on the chip buffer data in opposite directions. Each FIFO has flags to indicate empty and full conditions and two programmable flags (almost full and almost empty) to indicate when a selected number of words is stored in memory. Communication between each port can bypass the FIFOs via two 36-bit mailbox registers. Each mailbox register has a flag to signal when new mail has been stored. Two or more devices can be used in parallel to create wider data paths.

The SN54ACT3632 is a clocked FIFO, which means each port employs a synchronous interface. All data transfers through a port are gated to the low-to-high transition of a port clock by enable signals. The clocks for each port are independent of one another and can be asynchronous or coincident. The enables for each port are arranged to provide a simple bidirectional interface between microprocessors and/or buses with synchronous control.

The input-ready (IRA, IRB) flag and almost-full (AFA, AFB) flag of a FIFO are two-stage synchronized to the port clock that writes data to its array. The output-ready (ORA, ORB) flag and almost-empty (AEA, AEB) flag of a FIFO are two-stage synchronized to the port clock that reads data from its array. Offset values for the almost-full and almost-empty flags of both FIFOs can be programmed from port A.

The SN54ACT3632 is characterized for operation over the full military temperature range of -55°C to 125°C.

For more information on this device family, see the following application reports:

- FIFO Mailbox-Bypass Registers: Using Bypass Registers to Initialize DMA Control (literature number SCAA007)

- Interfacing TI Clocked FIFOs With TI Floating-Point Digital Signal Processors (literature number SCAA005)

- Metastability Performance of Clocked FIFOs (literature number SCZA004)

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

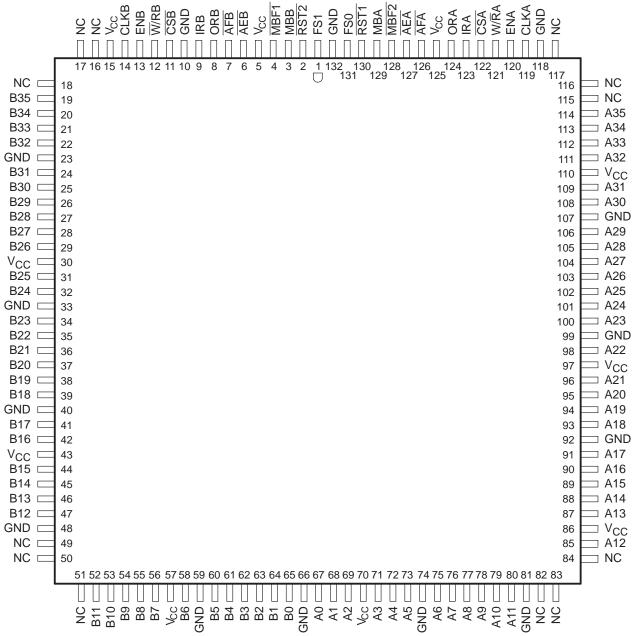

# HFP PACKAGE (TOP VIEW)

NC - No internal connection

## functional block diagram

# CLOCKED BIDIRECTIONAL FIRST-IN, FIRST-OUT MEMORY SGBS310A – SEPTEMBER 1996 – REVISED APRIL 1998

## **Terminal Functions**

| TERMINAL<br>NAME | I/O           | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A0-A35           | I/O           | Port-A data. The 36-bit bidirectional data port for side A.                                                                                                                                                                                                                                                                                                                                                                                                               |

| AEA              | O<br>(port A) | Port-A almost-empty flag. Programmable flag synchronized to CLKA. AEA is low when the number of words in FIFO2 is less than or equal to the value in the almost-empty A offset register, X2.                                                                                                                                                                                                                                                                              |

| ĀĒB              | O<br>(port B) | Port-B almost-empty flag. Programmable flag synchronized to CLKB. AEB is low when the number of words in FIFO1 is less than or equal to the value in the almost-empty B offset register, X1.                                                                                                                                                                                                                                                                              |

| ĀFĀ              | O<br>(port A) | Port-A almost-full flag. Programmable flag synchronized to CLKA. AFA is low when the number of empty locations in FIFO1 is less than or equal to the value in the almost-full A offset register, Y1.                                                                                                                                                                                                                                                                      |

| ĀFB              | O<br>(port B) | Port-B almost-full flag. Programmable flag synchronized to CLKB. AFB is low when the number of empty locations in FIFO2 is less than or equal to the value in the almost-full B offset register, Y2.                                                                                                                                                                                                                                                                      |

| B0-B35           | I/O           | Port-B data. The 36-bit bidirectional data port for side B.                                                                                                                                                                                                                                                                                                                                                                                                               |

| CLKA             | I             | Port-A clock. CLKA is a continuous clock that synchronizes all data transfers through port A and can be asynchronous or coincident to CLKB. IRA, ORA, AFA, and AEA are all synchronized to the low-to-high transition of CLKA.                                                                                                                                                                                                                                            |

| CLKB             | 1             | Port-B clock. CLKB is a continuous clock that <u>synchronizes</u> all data transfers through port B and can be asynchronous or coincident to CLKA. IRB, ORB, AFB, and AEB are synchronized to the low-to-high transition of CLKB.                                                                                                                                                                                                                                         |

| CSA              | 1             | Port-A chip select. $\overline{\text{CSA}}$ must be low to enable a low-to-high transition of CLKA to read or write data on port A. The A0–A35 outputs are in the high-impedance state when $\overline{\text{CSA}}$ is high.                                                                                                                                                                                                                                              |

| CSB              | I             | Port-B chip select. CSB must be low to enable a low-to-high transition of CLKB to read or write data on port B. The B0–B35 outputs are in the high-impedance state when CSB is high.                                                                                                                                                                                                                                                                                      |

| ENA              | I             | Port-A enable. ENA must be high to enable a low-to-high transition of CLKA to read or write data on port A.                                                                                                                                                                                                                                                                                                                                                               |

| ENB              | I             | Port-B enable. ENB must be high to enable a low-to-high transition of CLKB to read or write data on port B.                                                                                                                                                                                                                                                                                                                                                               |

| FS1, FS0         | I             | Flag-offset selects. The low-to-high transition of a FIFO reset input latches the values of FS0 and FS1. If either FS0 or FS1 is high when a reset input goes high, one of three preset values is selected as the offset for the FIFO almost-full and almost-empty flags. If both FIFOs are reset simultaneously and both FS0 and FS1 are low when RST1 and RST2 go high, the first four writes to FIFO1 program the almost-full and almost-empty offsets for both FIFOs. |

| IRA              | O<br>(port A) | Input-ready flag. IRA is synchronized to the low-to-high transition of CLKA. When IRA is low, FIFO1 is full and writes to its array are disabled. IRA is set low when FIFO1 is reset and is set high on the second low-to-high transition of CLKA after reset.                                                                                                                                                                                                            |

| IRB              | O<br>(port B) | Input-ready flag. IRB is synchronized to the low-to-high transition of CLKB. When IRB is low, FIFO2 is full and writes to its array are disabled. IRB is set low when FIFO2 is reset and is set high on the second low-to-high transition of CLKB after reset.                                                                                                                                                                                                            |

| МВА              | 1             | Port-A mailbox select. A high level on MBA chooses a mailbox register for a port-A read or write operation. When the A0–A35 outputs are active, a high level on MBA selects data from the mail2 register for output and a low level selects FIFO2 output-register data for output.                                                                                                                                                                                        |

| MBB              | 1             | Port-B mailbox select. A high level on MBB chooses a mailbox register for a port-B read or write operation. When the B0–B35 outputs are active, a high level on MBB selects data from the mail1 register for output and a low level selects FIFO1 output-register data for output.                                                                                                                                                                                        |

| MBF1             | 0             | Mail1 register flag. MBF1 is set low by the low-to-high transition of CLKA that writes data to the mail1 register. Writes to the mail1 register are inhibited while MBF1 is low. MBF1 is set high by a low-to-high transition of CLKB when a port-B read is selected and MBB is high. MBF1 is set high when FIFO1 is reset.                                                                                                                                               |

| MBF2             | 0             | Mail2 register flag. MBF2 is set low by the low-to-high transition of CLKB that writes data to the mail2 register. Writes to the mail2 register are inhibited while MBF2 is low. MBF2 is set high by a low-to-high transition of CLKA when a port-A read is selected and MBA is high. MBF2 also is set high when FIFO2 is reset.                                                                                                                                          |

| ORA              | O<br>(port A) | Output-ready flag. ORA is synchronized to the low-to-high transition of CLKA. When ORA is low, FIFO2 is empty and reads from its memory are disabled. Ready data is present on the output register of FIFO2 when ORA is high. ORA is forced low when FIFO2 is reset and goes high on the third low-to-high transition of CLKA after a word is loaded to empty memory.                                                                                                     |

SGBS310A - SEPTEMBER 1996 - REVISED APRIL 1998

## **Terminal Functions (Continued)**

| TERMINAL<br>NAME | I/O           | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                           |

|------------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ORB              | O<br>(port B) | Output-ready flag. ORB is synchronized to the low-to-high transition of CLKB. When ORB is low, FIFO1 is empty and reads from its memory are disabled. Ready data is present on the output register of FIFO1 when ORB is high. ORB is forced low when FIFO1 is reset and goes high on the third low-to-high transition of CLKB after a word is loaded to empty memory. |

| RST1             | I             | FIFO1 reset. To reset FIFO1, four low-to-high transitions of CLKA and four low-to-high transitions of CLKB must occur while RST1 is low. The low-to-high transition of RST1 latches the status of FS0 and FS1 for AFA and AEB offset selection. FIFO1 must be reset upon power up before data is written to its RAM.                                                  |

| RST2             | I             | FIFO2 reset. To reset FIFO2, four low-to-high transitions of CLKA and four low-to-high transitions of CLKB must occur while RST2 is low. The low-to-high transition of RST2 latches the status of FS0 and FS1 for AFB and AEA offset selection. FIFO2 must be reset upon power up before data is written to its RAM.                                                  |

| W/RA             | Ţ             | Port-A write/read select. A high on W/RA selects a write operation and a low selects a read operation on port A for a low-to-high transition of CLKA. The A0–A35 outputs are in the high-impedance state when W/RA is high.                                                                                                                                           |

| W/RB             | 1             | Port-B write/read select. A low on $\overline{W}$ /RB selects a write operation and a high selects a read operation on port B for a low-to-high transition of CLKB. The B0–B35 outputs are in the high-impedance state when $\overline{W}$ /RB is low.                                                                                                                |

#### detailed description

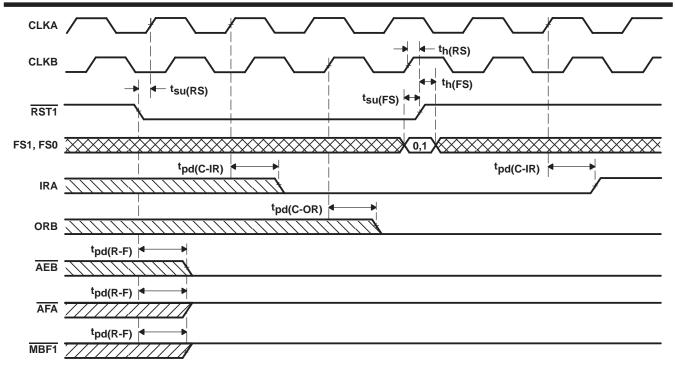

#### reset

The FIFO memories of the SN54ACT3632 are reset separately by taking their reset (RST1, RST2) inputs low for at least four port-A clock (CLKA) and four port-B clock (CLKB) low-to-high transitions. The reset inputs can switch asynchronously to the clocks. A FIFO reset initializes the internal read and write pointers and forces the input-ready flag (IRA, IRB) low, the output-ready flag (ORA, ORB) low, the almost-empty flag (AEA, AEB) low, and the almost-full flag (AFA, AFB) high. Resetting a FIFO also forces the mailbox flag (MBF1, MBF2) of the parallel mailbox register high. After a FIFO is reset, its input-ready flag is set high after two clock cycles to begin normal operation. A FIFO must be reset after power up before data is written to its memory.

A low-to-high transition on a FIFO reset ( $\overline{RST1}$ ,  $\overline{RST2}$ ) input latches the value of the flag-select (FS0, FS1) inputs for choosing the almost-full and almost-empty offset programming method.

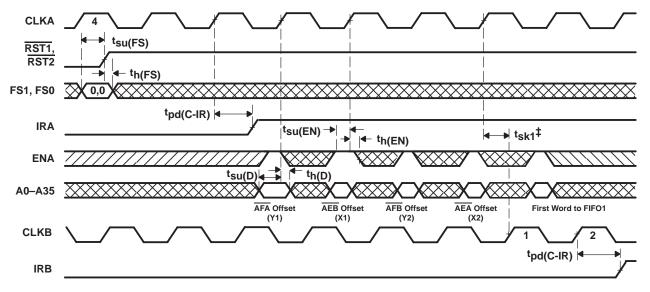

### almost-empty flag and almost-full flag offset programming

Four registers in the SN54ACT3632 are used to hold the offset values for the almost-empty and almost-full flags. The port-B almost-empty flag (AEB) offset register is labeled X1 and the port-A almost-empty flag (AEA) offset register is labeled X2. The port-A almost-full flag (AFA) offset register is labeled Y1 and the port-B almost-full flag (AFB) offset register is labeled Y2. The index of each register name corresponds to its FIFO number. The offset registers can be loaded with preset values during the reset of a FIFO or they can be programmed from port A (see Table 1).

**Table 1. Flag Programming**

| FS1 | FS0 | RST1 | RST2     | X1 AND Y1 REGISTERS†   | X2 AND Y2 REGISTERS‡   |

|-----|-----|------|----------|------------------------|------------------------|

| Н   | Н   | 1    | Х        | 64                     | X                      |

| Н   | Н   | Х    | <b>↑</b> | X 64                   |                        |

| Н   | L   | 1    | Х        | 16                     | Χ                      |

| Н   | L   | Х    | <b>↑</b> | X 16                   |                        |

| L   | Н   | 1    | Х        | 8                      | Χ                      |

| L   | Н   | Χ    | 1        | X                      | 8                      |

| L   | L   | 1    | 1        | Programmed from port A | Programmed from port A |

TX1 register holds the offset for AEB; Y1 register holds the offset for AFA.

<sup>‡</sup>X2 register holds the offset for AEA; Y2 register holds the offset for AFB.

SGBS310A - SEPTEMBER 1996 - REVISED APRIL 1998

### almost-empty flag and almost-full flag offset programming (continued)

To load the almost-empty flag and almost-full flag offset registers of a FIFO with one of the three preset values listed in Table 1, at least one of the flag-select inputs must be high during the low-to-high transition of its reset input. For example, to load the preset value of 64 into X1 and Y1, FS0 and FS1 must be high when FIFO1 reset (RST1) returns high. Flag-offset registers associated with FIFO2 are loaded with one of the preset values in the same way with FIFO2 reset (RST2). When using one of the preset values for the flag offsets, the FIFOs can be reset simultaneously or at different times.

To program the X1, X2, Y1, and Y2 registers from port A, both FIFOs should be reset simultaneously with FS0 and FS1 low during the low-to-high transition of the reset inputs. After this reset is complete, the first four writes to FIFO1 do not store data in RAM but load the offset registers in the order Y1, X1, Y2, X2. Each offset register uses port-A (A8-A0) inputs, with A8 as the most-significant bit. Each register value can be programmed from 1 to 508. After all the offset registers are programmed from port A, the port-B input-ready flag (IRB) is set high and both FIFOs begin normal operation.

### FIFO write/read operation

The state of the port-A data (A0-A35) outputs is controlled by the port-A chip select ( $\overline{CSA}$ ) and the port-A write/read select (W/RA). The A0–A35 outputs are in the high-impedance state when either  $\overline{CSA}$  or W/RA is high. The A0–A35 outputs are active when both  $\overline{CSA}$  and  $W/\overline{R}A$  are low.

Data is loaded into FIFO1 from the A0–A35 inputs on a low-to-high transition of CLKA when  $\overline{\text{CSA}}$  is low, W/ $\overline{\text{RA}}$ is high, ENA is high, MBA is low, and IRA is high. Data is read from FIFO2 to the A0-A35 outputs by a low-to-high transition of CLKA when  $\overline{CSA}$  is low, W/ $\overline{RA}$  is low, ENA is high, MBA is low, and ORA is high (see Table 2). FIFO reads and writes on port A are independent of any concurrent port-B operation.

| CSA | W/RA | ENA | MBA | CLKA | A0-A35 OUTPUTS                | PORT FUNCTION              |

|-----|------|-----|-----|------|-------------------------------|----------------------------|

| Н   | Х    | Х   | Х   | Х    | In high-impedance state       | None                       |

| L   | Н    | L   | Х   | Х    | In high-impedance state       | None                       |

| L   | Н    | Н   | L   | 1    | In high-impedance state       | FIFO1 write                |

| L   | Н    | Н   | Н   | 1    | In high-impedance state       | Mail1 write                |

| L   | L    | L   | L   | Х    | Active, FIFO2 output register | None                       |

| L   | L    | Н   | L   | 1    | Active, FIFO2 output register | FIFO2 read                 |

| L   | L    | L   | Н   | Х    | Active, mail2 register        | None                       |

| L   | L    | Н   | Н   | 1    | Active, mail2 register        | Mail2 read (set MBF2 high) |

Table 2. Port-A Enable Function Table

The port-B control signals are identical to those of port A with the exception that the port-B write/read select  $(\overline{W}/RB)$  is the inverse of the port-A write/read select  $(W/\overline{R}A)$ . The state of the port-B data (B0–B35) outputs is controlled by the port-B chip select  $(\overline{CSB})$  and the port-B write/read select  $(\overline{W}/RB)$ . The B0–B35 outputs are in the high-impedance state when either CSB is high or W/RB is low. The B0–B35 outputs are active when CSB is low and  $\overline{W}/RB$  is high.

Data is loaded into FIFO2 from the B0–B35 inputs on a low-to-high transition of CLKB when CSB is low, W/RB is low, ENB is high, MBB is low, and IRB is high. Data is read from FIFO1 to the B0-B35 outputs by a low-to-high transition of CLKB when  $\overline{\text{CSB}}$  is low,  $\overline{\text{W}}/\text{RB}$  is high, ENB is high, MBB is low, and ORB is high (see Table 3). FIFO reads and writes on port B are independent of any concurrent port-A operation.

SGBS310A – SEPTEMBER 1996 – REVISED APRIL 1998

### FIFO write/read operation (continued)

Table 3. Port-B Enable Function Table

| CSB | W/RB | ENB | MBB | CLKB | B0-B35 OUTPUTS                | PORT FUNCTION              |

|-----|------|-----|-----|------|-------------------------------|----------------------------|

| Н   | Х    | Х   | Х   | Х    | In high-impedance state       | None                       |

| L   | L    | L   | Х   | Х    | In high-impedance state       | None                       |

| L   | L    | Н   | L   | 1    | In high-impedance state       | FIFO2 write                |

| L   | L    | Н   | Н   | 1    | In high-impedance state       | Mail2 write                |

| L   | Н    | L   | L   | Х    | Active, FIFO1 output register | None                       |

| L   | Н    | Н   | L   | 1    | Active, FIFO1 output register | FIFO1 read                 |

| L   | Н    | L   | Н   | Х    | Active, mail1 register        | None                       |

| L   | Н    | Н   | Н   | 1    | Active, mail1 register        | Mail1 read (set MBF1 high) |

The setup- and hold-time constraints to the port clocks for the port-chip selects and write/read selects are only for enabling write and read operations and are not related to high-impedance control of the data outputs. If a port enable is low during a clock cycle, the port-chip select and write/read select may change states during the setup- and hold-time window of the cycle.

When a FIFO output-ready flag is low, the next data word is sent to the FIFO output register automatically by the low-to-high transition of the port clock that sets the output-ready flag high. When the output-ready flag is high, an available data word is clocked to the FIFO output register only when a FIFO read is selected by the port's chip select, write/read select, enable, and mailbox select.

## synchronized FIFO flags

Each FIFO is synchronized to its port clock through at least two flip-flop stages. This is done to improve flag-signal reliability by reducing the probability of metastable events when CLKA and CLKB operate asynchronously to one another. ORA, AEA, IRA, and AFA are synchronized to CLKA. ORB, AEB, IRB, and AFB are synchronized to CLKB. Tables 4 and 5 show the relationship of each port flag to FIFO1 and FIFO2.

**Table 4. FIFO1 Flag Operation**

| NUMBER OF WORDS<br>IN FIFO1†‡ | SYNCHR<br>TO C | -   | SYNCHRONIZED<br>TO CLKA |     |  |

|-------------------------------|----------------|-----|-------------------------|-----|--|

| IN FIFOT+                     | ORB            | AEB | AFA                     | IRA |  |

| 0                             | L              | L   | Н                       | Н   |  |

| 1 to X1                       | Н              | L   | Н                       | Н   |  |

| (X1 + 1) to [512 – (Y1 + 1)]  | Н              | Н   | Н                       | Н   |  |

| (512 – Y1) to 511             | Н              | Н   | L                       | Н   |  |

| 512                           | Н              | Н   | L                       | L   |  |

<sup>†</sup> X1 is the almost-empty offset for FIFO1 used by AEB. Y1 is the almost-full offset for FIFO1 used by AFA. Both X1 and Y1 are selected during a reset of FIFO1 or programmed from port A.

<sup>&</sup>lt;sup>‡</sup> When a word loaded to an empty FIFO is shifted to the output register, its previous FIFO memory location is free.

SGBS310A - SEPTEMBER 1996 - REVISED APRIL 1998

**Table 5. FIFO2 Flag Operation**

| NUMBER OF WORDS<br>IN FIFO2†‡ | SYNCHR<br>TO C | _   | SYNCHRONIZED<br>TO CLKB |     |  |

|-------------------------------|----------------|-----|-------------------------|-----|--|

| IN FIFO21+                    | ORA            | AEA | AFB                     | IRB |  |

| 0                             | L              | L   | Н                       | Н   |  |

| 1 to X2                       | Н              | L   | Н                       | Н   |  |

| (X2 + 1) to [512 – (Y2 + 1)]  | Н              | Н   | Н                       | Н   |  |

| (512 – Y2) to 511             | Н              | Н   | L                       | Н   |  |

| 512                           | Н              | Н   | L                       | L   |  |

<sup>†</sup> X2 is the almost-empty offset for FIFO2 used by AEA. Y2 is the almost-full offset for FIFO2 used by AFB. Both X2 and Y2 are selected during a reset of FIFO2 or programmed from port A.

#### output-ready flags (ORA, ORB)

The output-ready flag of a FIFO is synchronized to the port clock that reads data from its array. When the output-ready flag is high, new data is present in the FIFO output register. When the output-ready flag is low, the previous data word is present in the FIFO output register and attempted FIFO reads are ignored.

A FIFO read pointer is incremented each time a new word is clocked to its output register. The state machine that controls an output-ready flag monitors a write-pointer and read-pointer comparator that indicates when the FIFO SRAM status is empty, empty+1, or empty+2. From the time a word is written to a FIFO, it can be shifted to the FIFO output register in a minimum of three cycles of the output-ready flag synchronizing clock; therefore, an output-ready flag is low if a word in memory is the next data to be sent to the FIFO output register and three cycles of the port clock that reads data from the FIFO have not elapsed since the time the word was written. The output-ready flag of the FIFO remains low until the third low-to-high transition of the synchronizing clock occurs, simultaneously forcing the output-ready flag high and shifting the word to the FIFO output register.

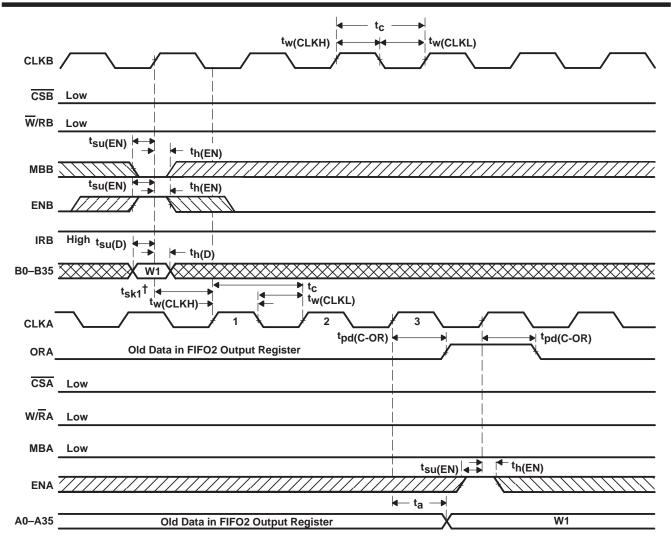

A low-to-high transition on an output-ready flag synchronizing clock begins the first synchronization cycle of a write if the clock transition occurs at time  $t_{sk1}$ , or greater, after the write. Otherwise, the subsequent clock cycle can be the first synchronization cycle (see Figures 7 and 8).

#### input-ready flags (IRA, IRB)

The input-ready flag of a FIFO is synchronized to the port clock that writes data to its array. When the input-ready flag is high, a memory location is free in the SRAM to receive new data. No memory locations are free when the input-ready flag is low and attempted writes to the FIFO are ignored.

Each time a word is written to a FIFO, its write pointer is incremented. The state machine that controls an input-ready flag monitors a write-pointer and read-pointer comparator that indicates when the FIFO SRAM status is full, full—1, or full—2. From the time a word is read from a FIFO, its previous memory location is ready to be written in a minimum of two cycles of the input-ready flag synchronizing clock; therefore, an input-ready flag is low if less than two cycles of the input-ready flag synchronizing clock have elapsed since the next memory write location has been read. The second low-to-high transition on the input-ready flag synchronizing clock after the read sets the input-ready flag high.

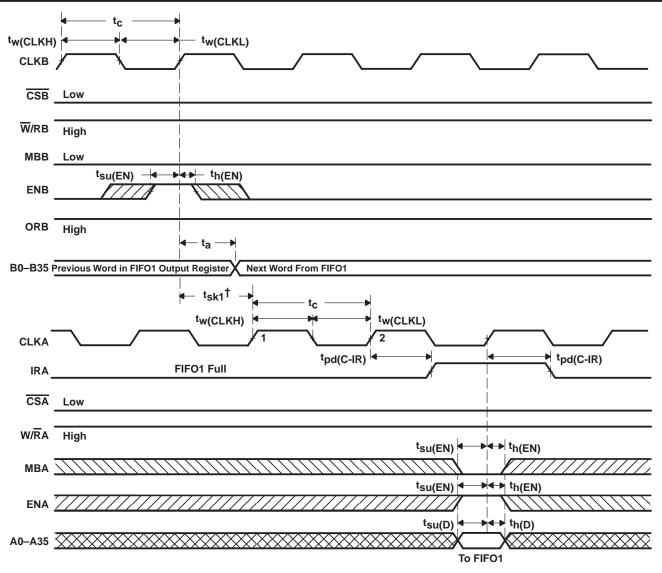

A low-to-high transition on an input-ready flag synchronizing clock begins the first synchronization cycle of a read if the clock transition occurs at time  $t_{sk1}$ , or greater, after the read. Otherwise, the subsequent clock cycle can be the first synchronization cycle (see Figures 9 and 10).

<sup>&</sup>lt;sup>‡</sup> When a word loaded to an empty FIFO is shifted to the output register, its previous FIFO memory location is free.

SGBS310A - SEPTEMBER 1996 - REVISED APRIL 1998

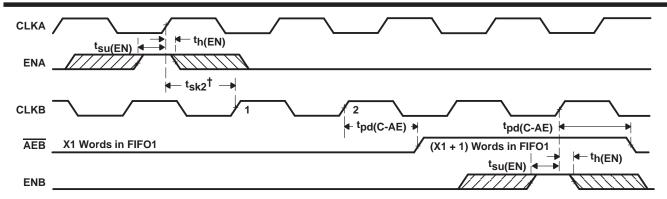

## almost-empty flags (AEA, AEB)

The almost-empty flag of a FIFO is synchronized to the port clock that reads data from its array. The state machine that controls an almost-empty flag monitors a write-pointer and read-pointer comparator that indicates when the FIFO SRAM status is almost empty, almost empty+1, or almost empty+2. The almost-empty state is defined by the contents of register X1 for  $\overline{AEB}$  and register X2 for  $\overline{AEA}$ . These registers are loaded with preset values during a FIFO reset or programmed from port A (see *almost-empty flag and almost-full flag offset programming*). An almost-empty flag is low when its FIFO contains X or fewer words and is high when its FIFO contains (X + 1) or more words. A data word present in the FIFO output register has been read from memory.

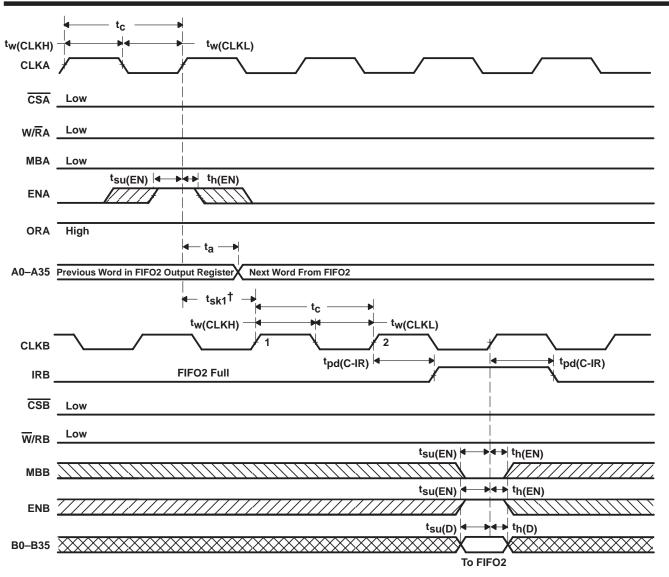

Two low-to-high transitions of the almost-empty flag synchronizing clock are required after a FIFO write for its almost-empty flag to reflect the new level of fill. Therefore, the almost-empty flag of a FIFO containing (X + 1) or more words remains low if two cycles of its synchronizing clock have not elapsed since the write that filled the memory to the (X + 1) level. An almost-empty flag is set high by the second low-to-high transition of its synchronizing clock after the FIFO write that fills memory to the (X + 1) level. A low-to-high transition of an almost-empty flag synchronizing clock begins the first synchronization cycle if it occurs at time  $t_{sk2}$ , or greater, after the write that fills the FIFO to (X + 1) words. Otherwise, the subsequent synchronizing clock cycle can be the first synchronization cycle (see Figures 11 and 12).

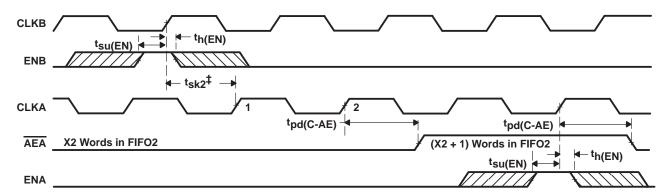

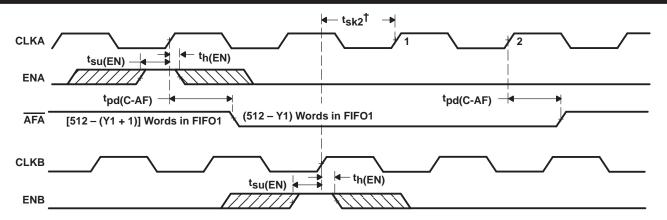

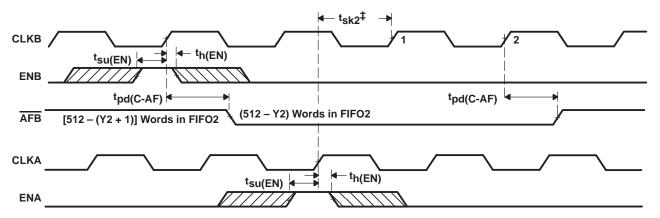

## almost-full flags (AFA, AFB)

The almost-full flag of a FIFO is synchronized to the port clock that writes data to its array. The state machine that controls an almost-full flag monitors a write-pointer and read-pointer comparator that indicates when the FIFO SRAM status is almost full, almost full-1, or almost full-2. The almost-full state is defined by the contents of register Y1 for  $\overline{AFA}$  and register Y2 for  $\overline{AFB}$ . These registers are loaded with preset values during a FIFO reset or programmed from port A (see almost-empty flag and almost-full flag offset programming). An almost-full flag is low when its FIFO contains (512 - Y) or more words and is high when its FIFO contains [512 - (Y + 1)] or less words. A data word present in the FIFO output register has been read from memory.

Two low-to-high transitions of the almost-full flag synchronizing clock are required after a FIFO read for its almost-full flag to reflect the new level of fill. Therefore, the almost-full flag of a FIFO containing [512 – (Y + 1)] or fewer words remains low if two cycles of its synchronizing clock have not elapsed since the read that reduced the number of words in memory to [512 – (Y + 1)]. An almost-full flag is set high by the second low-to-high transition of its synchronizing clock after the FIFO read that reduces the number of words in memory to [512 – (Y + 1)]. A low-to-high transition of an almost-full flag synchronizing clock begins the first synchronization cycle if it occurs at time  $t_{sk2}$ , or greater, after the read that reduces the number of words in memory to [512 – (Y + 1)]. Otherwise, the subsequent synchronizing clock cycle can be the first synchronization cycle (see Figures 13 and 14).

#### mailbox registers

Each FIFO has a 36-bit bypass register to pass command and control information between port A and port B without putting it in queue. The mailbox-select (MBA, MBB) inputs choose between a mail register and a FIFO for a port-data-transfer operation. A low-to-high transition on CLKA writes A0–A35 data to the mail1 register when a port-A write is selected by  $\overline{CSA}$ , W/ $\overline{R}A$ , and ENA and with MBA high. A low-to-high transition on CLKB writes B0–B35 data to the mail2 register when a port-B write is selected by  $\overline{CSB}$ ,  $\overline{W}/RB$ , and ENB and with MBB high. Writing data to a mail register sets its corresponding flag ( $\overline{MBF1}$  or  $\overline{MBF2}$ ) low. Attempted writes to a mail register are ignored while the mail flag is low.

When data outputs of a port are active, the data on the bus comes from the FIFO output register when the port mailbox select input is low and from the mail register when the port-mailbox select input is high. The mail1 register flag (MBF1) is set high by a low-to-high transition on CLKB when a port-B read is selected by  $\overline{CSB}$ ,  $\overline{W}/RB$ , and ENB and with MBB high. The mail2 register flag (MBF2) is set high by a low-to-high transition on CLKA when a port-A read is selected by  $\overline{CSA}$ ,  $\overline{W}/RA$ , and ENA and with MBA high. The data in a mail register remains intact after it is read and changes only when new data is written to the register.

Figure 1. FIFO1 Reset Loading X1 and Y1 With a Preset Value of Eight<sup>†</sup>

† FIFO2 is reset in the same manner to load X2 and Y2 with a preset value.

<sup>‡</sup> t<sub>Sk1</sub> is the minimum time between the rising CLKA edge and a rising CLKB edge for IRB to transition high in the next cycle. If the time between the rising edge of CLKA and rising edge of CLKB is less than t<sub>Sk1</sub>, IRB may transition high one cycle later than shown.

NOTE A: CSA = L, W/RA = H, MBA = L. It is not necessary to program offset register on consecutive clock cycles.

Figure 2. Programming the Almost-Full Flag and Almost-Empty Flag Offset Values After Reset

†Written to FIFO1

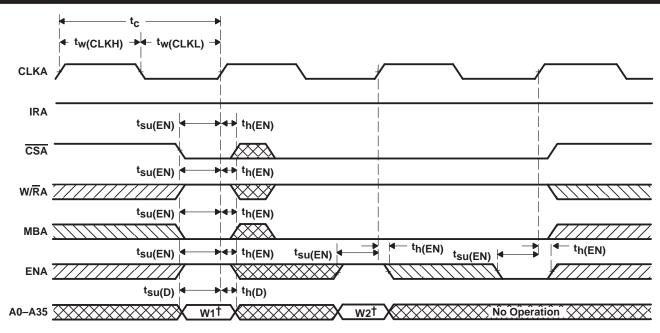

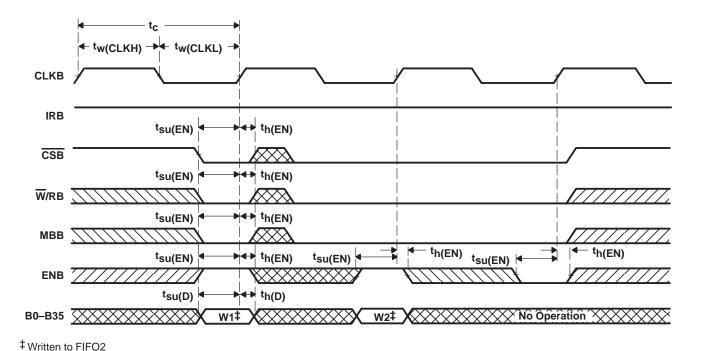

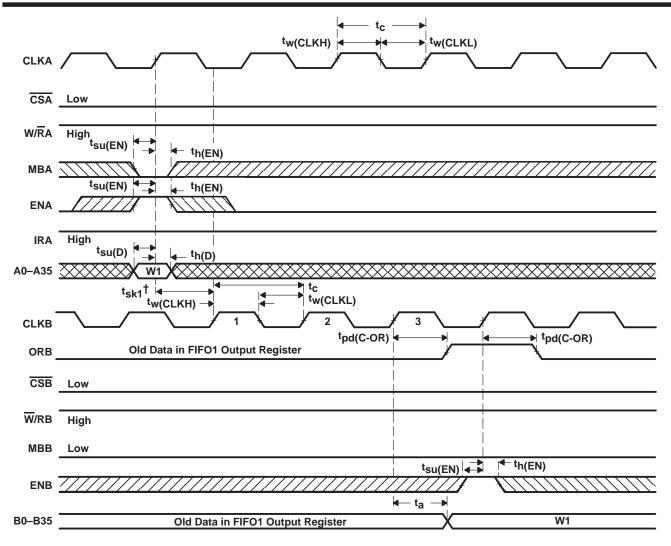

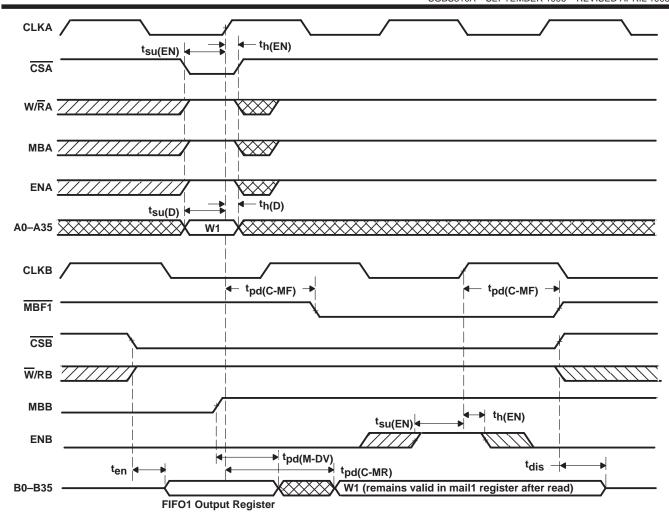

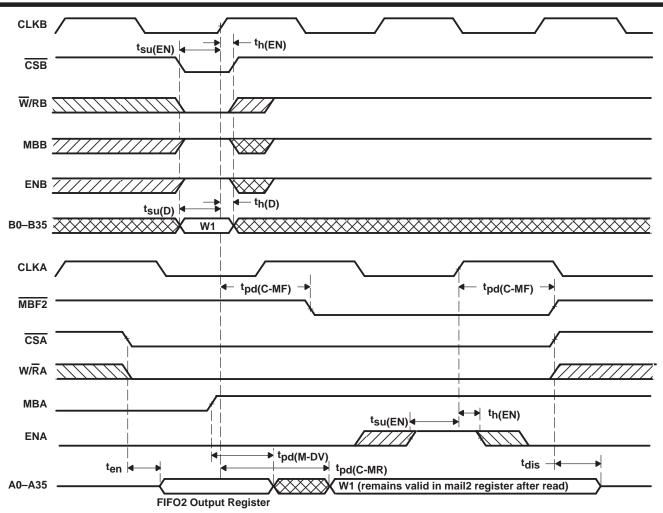

Figure 3. Port-A Write Cycle for FIFO1

Figure 4. Port-B Write Cycle for FIFO2

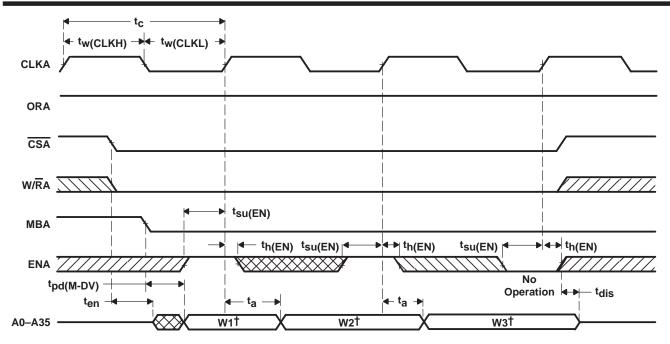

<sup>†</sup>Read from FIFO2

Figure 5. Port-A Read Cycle for FIFO2

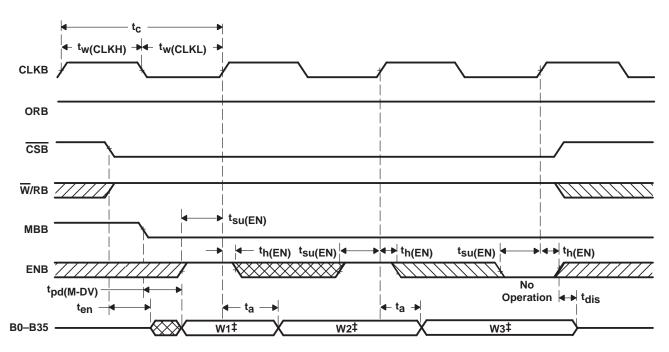

‡Read from FIFO1

Figure 6. Port-B Read Cycle for FIFO1

<sup>†</sup> t<sub>sk1</sub> is the minimum time between a rising CLKA edge and a rising CLKB edge for ORB to transition high and to clock the next word to the FIFO1 output register in three CLKB cycles. If the time between the rising CLKA edge and rising CLKB edge is less than t<sub>sk1</sub>, the transition of ORB high and load of the first word to the output register may occur one CLKB cycle later than shown.

Figure 7. ORB-Flag Timing and First Data-Word Fall Through When FIFO1 Is Empty

<sup>†</sup> t<sub>sk1</sub> is the minimum time between a rising CLKB edge and a rising CLKA edge for ORA to transition high and to clock the next word to the FIFO2 output register in three CLKA cycles. If the time between the rising CLKB edge and rising CLKA edge is less than t<sub>sk1</sub>, the transition of ORA high and load of the first word to the output register may occur one CLKA cycle later than shown.

Figure 8. ORA-Flag Timing and First Data-Word Fall Through When FIFO2 Is Empty

<sup>†</sup> t<sub>Sk1</sub> is the minimum time between a rising CLKB edge and a rising CLKA edge for IRA to transition high in the next CLKA cycle. If the time between the rising CLKB edge and rising CLKA edge is less than t<sub>sk1</sub>, IRA may transition high one CLKA cycle later than shown.

Figure 9. IRA-Flag Timing and First Available Write When FIFO1 Is Full

<sup>†</sup> t<sub>Sk1</sub> is the minimum time between a rising CLKA edge and a rising CLKB edge for IRB to transition high in the next CLKB cycle. If the time between the rising CLKA edge and rising CLKB edge is less than t<sub>sk1</sub>, IRB may transition high one CLKB cycle later than shown.

Figure 10. IRB-Flag Timing and First Available Write When FIFO2 Is Full

<sup>†</sup> t<sub>SK2</sub> is the minimum time between a rising CLKA edge and a rising CLKB edge for AEB to transition high in the next CLKB cycle. If the time between the rising CLKA edge and rising CLKB edge is less than t<sub>Sk2</sub>, AEB may transition high one CLKB cycle later than shown.

NOTE A: FIFO1 write (CSA = L, W/RA = H, MBA = L), FIFO1 read (CSB = L, W/RB = H, MBB = L). Data in the FIFO1 output register has been read from the FIFO.

Figure 11. AEB When FIFO1 Is Almost Empty

<sup>‡</sup>t<sub>SK2</sub> is the minimum time between a rising CLKB edge and a rising CLKA edge for AEA to transition high in the next CLKA cycle. If the time between the rising CLKB edge and rising CLKA edge is less than t<sub>Sk2</sub>, AEA may transition high one CLKA cycle later than shown.

NOTE A: FIFO2 write (CSB = L, W/RB = L, MBB = L), FIFO2 read (CSA = L, W/RA = L, MBA = L). Data in the FIFO2 output register has been read from the FIFO.

Figure 12. AEA When FIFO2 Is Almost Empty

<sup>†</sup>t<sub>sk2</sub> is the minimum time between a rising CLKA edge and a rising CLKB edge for AFA to transition high in the next CLKA cycle. If the time between the rising CLKA edge and rising CLKB edge is less than  $t_{Sk2}$ ,  $\overline{AFA}$  may transition high one CLKB cycle later than shown. NOTE A: FIFO1 write ( $\overline{CSA}$  = L, W/RA = H, MBA = L), FIFO1 read ( $\overline{CSB}$  = L, W/RB = H, MBB = L). Data in the FIFO1 output register has been read from the FIFO.

Figure 13. AFA When FIFO1 Is Almost Full

<sup>‡</sup>t<sub>SK2</sub> is the minimum time between a rising CLKB edge and a rising CLKA edge for AFB to transition high in the next CLKB cycle. If the time between the rising CLKB edge  $\underline{and}$  rising CLKA edge is less than  $\underline{t_{sk2}}$ ,  $\overline{AFB}$   $\underline{may}$  transition high one CLKA cycle later than shown. NOTE A: FIFO2 write (CSB = L, W/RB = L, MBB = L), FIFO2 read (CSA = L, W/RA = L, MBA = L). Data in the FIFO2 output register has been read from the FIFO.

Figure 14. AFB When FIFO2 Is Almost Full

# CLOCKED BIDIRECTIONAL FIRST-IN, FIRST-OUT MEMORY SGBS310A - SEPTEMBER 1996 - REVISED APRIL 1998

Figure 15. Mail1 Register and MBF1 Flag

Figure 16. Mail2 Register and MBF2 Flag

SGBS310A - SEPTEMBER 1996 - REVISED APRIL 1998

## absolute maximum ratings over operating free-air temperature range (unless otherwise noted)†

| Supply voltage range, V <sub>CC</sub>                          |                                  |

|----------------------------------------------------------------|----------------------------------|

| Input voltage range, V <sub>I</sub> (see Note 1)               | 0.5 V to V <sub>CC</sub> + 0.5 V |

| Output voltage range, VO (see Note 1)                          | 0.5 V to V <sub>CC</sub> + 0.5 V |

| Input clamp current, $I_{IK}$ ( $V_I < 0$ or $V_I > V_{CC}$ )  | ±20 mA                           |

| Output clamp current, $I_{OK}$ ( $V_O < 0$ or $V_O > V_{CC}$ ) | ±50 mA                           |

| Continuous output current, $I_O(V_O = 0 \text{ to } V_{CC})$   | ±50 mA                           |

| Continuous current through V <sub>CC</sub> or GND              | ±400 mA                          |

| Storage temperature range, T <sub>stq</sub>                    |                                  |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## recommended operating conditions

|     |                                | MIN | MAX | UNIT |

|-----|--------------------------------|-----|-----|------|

| VCC | Supply voltage                 | 4.5 | 5.5 | V    |

| VIH | High-level input voltage       | 2   |     | V    |

| VIL | Low-level input voltage        |     | 0.8 | V    |

| ІОН | High-level output current      |     | -4  | mA   |

| loL | Low-level output current       |     | 8   | mA   |

| TA  | Operating free-air temperature | -55 | 125 | °C   |

## electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

| PARAMETER       | TEST                                                                                | CONDITIONS                             |        | MIN | TYP‡ | MAX | UNIT |

|-----------------|-------------------------------------------------------------------------------------|----------------------------------------|--------|-----|------|-----|------|

| VOH             | $V_{CC} = 4.5 \text{ V},$                                                           | $I_{OH} = -4 \text{ mA}$               |        | 2.4 |      |     | V    |

| VOL             | $V_{CC} = 4.5 \text{ V},$                                                           | $I_{OL} = 8 \text{ mA}$                |        |     |      | 0.5 | V    |

| ΙĮ              | V <sub>CC</sub> = 5.5 V,                                                            | VI = VCC or 0                          |        |     |      | ±5  | μΑ   |

| I <sub>OZ</sub> | $V_{CC} = 5.5 V,$                                                                   | $V_O = V_{CC}$ or 0                    |        |     |      | ±5  | μΑ   |

| ICC             | V <sub>CC</sub> = 5.5 V,                                                            | $V_{I} = V_{CC} - 0.2 \text{ V or } 0$ |        |     |      | 400 | μΑ   |

|                 | V <sub>CC</sub> = 5.5 V, One input at 3.4 V, Other inputs at V <sub>CC</sub> or GND | CSA = V <sub>IH</sub>                  | A0-A35 |     | 0    |     |      |

|                 |                                                                                     | CSB = V <sub>IH</sub>                  | B0-B35 |     | 0    |     |      |

| Δlcc§           |                                                                                     | CSA = V <sub>IL</sub>                  | A0-A35 |     |      | 1   | mA   |

|                 |                                                                                     | CSB = V <sub>IL</sub>                  | B0-B35 |     |      | 1   |      |

|                 |                                                                                     | All other inputs                       |        |     |      | 1   |      |

| Ci              | V <sub>I</sub> = 0,                                                                 | f = 1 MHz                              |        |     | 4    |     | pF   |

| Co              | $V_0 = 0,$                                                                          | f = 1 MHz                              | ·      |     | 8    |     | pF   |

<sup>‡</sup> All typical values are at  $V_{CC} = 5 \text{ V}$ ,  $T_A = 25^{\circ}\text{C}$ .

NOTE 1: The input and output voltage ratings may be exceeded provided the input and output current ratings are observed.

<sup>§</sup> This is the supply current when each input is at one of the specified TTL voltage levels rather than 0 V or VCC.

SGBS310A - SEPTEMBER 1996 - REVISED APRIL 1998

## timing requirements over recommended ranges of supply voltage and operating free-air temperature (see Figures 1 through 17)

|                     |                                                                                        | MIN | MAX | UNIT |

|---------------------|----------------------------------------------------------------------------------------|-----|-----|------|

| fclock              | Clock frequency, CLKA or CLKB                                                          |     | 50  | MHz  |

| t <sub>C</sub>      | Clock cycle time, CLKA or CLKB                                                         | 20  |     | ns   |

| tw(CLKH)            | Pulse duration, CLKA and CLKB high                                                     | 8   |     | ns   |

| tw(CLKL)            | Pulse duration, CLKA and CLKB low                                                      | 8   |     | ns   |

| t <sub>su(D)</sub>  | Setup time, A0–A35 before CLKA↑ and B0–B35 before CLKB↑                                | 5   |     | ns   |

| tsu(EN)             | Setup time, CSA, W/RA, ENA, and MBA before CLKA↑; CSB, W/RB, ENB, and MBB before CLKB↑ | 5   |     | ns   |

| t <sub>su(RS)</sub> | Setup time, RST1 or RST2 low before CLKA↑ or CLKB↑†                                    | 6   |     | ns   |

| t <sub>su(FS)</sub> | Setup time, FS0 and FS1 before RST1 and RST2 high                                      | 8.5 |     | ns   |

| th(D)               | Hold time, A0–A35 after CLKA↑ and B0–B35 after CLKB↑                                   | 1   |     | ns   |

| th(EN)              | Hold time, CSA, W/RA, ENA, and MBA after CLKA↑; CSB, W/RB, ENB, and MBB after CLKB↑    | 1   |     | ns   |

| th(RS)              | Hold time, RST1 or RST2 low after CLKA↑ or CLKB↑†                                      | 4   |     | ns   |

| th(FS)              | Hold time, FS0 and FS1 after RST1 and RST2 high                                        | 3   |     | ns   |

| t <sub>sk1</sub> ‡  | Skew time between CLKA↑ and CLKB↑ for ORA, ORB, IRA, and IRB                           | 9   |     | ns   |

| t <sub>sk2</sub> ‡  | Skew time between CLKA↑ and CLKB↑ for AEA, AEB, AFA, and AFB                           | 16  |     | ns   |

<sup>†</sup> Requirement to count the clock edge as one of at least four needed to reset a FIFO

# switching characteristics over recommended ranges of supply voltage and operating free-air temperature, $C_L = 30$ pF (see Figures 1 through 17)

|                      | PARAMETER                                                                                                              | MIN | MAX  | UNIT |

|----------------------|------------------------------------------------------------------------------------------------------------------------|-----|------|------|

| f <sub>max</sub>     |                                                                                                                        | 50  |      | MHz  |

| ta                   | Access time, CLKA↑ to A0–A35 and CLKB↑ to B0–B35                                                                       | 3   | 15   | ns   |

| tpd(C-IR)            | Propagation delay time, CLKA↑ to IRA and CLKB↑ to IRB                                                                  | 2   | 10   | ns   |

| tpd(C-OR)            | Propagation delay time, CLKA↑ to ORA and CLKB↑ to ORB                                                                  | 1   | 10   | ns   |

| tpd(C-AE)            | Propagation delay time, CLKA↑ to AEA and CLKB↑ to AEB                                                                  | 1   | 10   | ns   |

| tpd(C-AF)            | Propagation delay time, CLKA↑ to AFA and CLKB↑ to AFB                                                                  | 1   | 10   | ns   |

| tpd(C-MF)            | Propagation delay time, CLKA↑ to MBF1 low or MBF2 high and CLKB↑ to MBF2 low or MBF1 high                              | 0   | 10   | ns   |

| tpd(C-MR)            | Propagation delay time, CLKA↑ to B0–B35§ and CLKB↑ to A0–A35¶                                                          | 3   | 18.7 | ns   |

| tpd(M-DV)            | Propagation delay time, MBA to A0–A35 valid and MBB to B0–B35 valid                                                    | 3   | 13   | ns   |

| <sup>t</sup> pd(R-F) | Propagation delay time, RST1 low to AEB low, AFA high, and MBF1 high, and RST2 low to AEA low, AFB high, and MBF2 high | 1   | 20   | ns   |

| t <sub>en</sub>      | Enable time, CSA and W/RA low to A0–A35 active and CSB low and W/RB high to B0–B35 active                              | 2   | 18   | ns   |

| <sup>t</sup> dis     | Disable time, CSA or W/RA high to A0–A35 at high impedance and CSB high or W/RB low to B0–B35 at high impedance        | 1   | 13   | ns   |

<sup>§</sup> Writing data to the mail1 register when the B0-B35 outputs are active and MBB is high

<sup>\$\</sup>frac{1}{2}\$ Skew time is not a timing constraint for proper device operation and is included only to illustrate the timing relationship between CLKA cycle and CLKB cycle.

<sup>¶</sup> Writing data to the mail2 register when the A0–A35 outputs are active and MBA is high

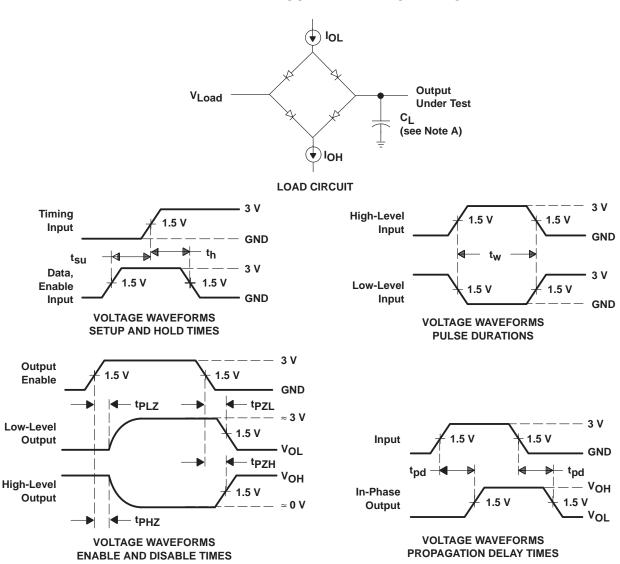

#### PARAMETER MEASUREMENT INFORMATION

NOTES: A. Includes probe and jig capacitance

- B. tpzL and tpzH are the same as ten.

- C. tpLZ and tpHZ are the same as t<sub>dis</sub>.

#### **CONDITIONS FOR LOAD CIRCUIT**

| PARAMETER        | I <sub>OL</sub><br>(mA) | IOH<br>(mA) | V <sub>Load</sub><br>(V) | C <sub>L</sub> †<br>(typical)<br>(pF) |  |

|------------------|-------------------------|-------------|--------------------------|---------------------------------------|--|

| <sup>t</sup> PZH | 8                       | 4           | 0                        | 20                                    |  |

| <sup>t</sup> PZL | 4                       | 8           | 3                        | 20                                    |  |

| <sup>t</sup> PHZ | 8                       | 6           | 1.5                      | 20                                    |  |

| <sup>t</sup> PLZ | 8                       | 6           | 1.5                      | 20                                    |  |

| tPD              | 4                       | 8           | 1.5                      | 20                                    |  |

<sup>†</sup> Includes probe and test-fixture capacitance

Figure 17. Load Circuit and Voltage Waveforms

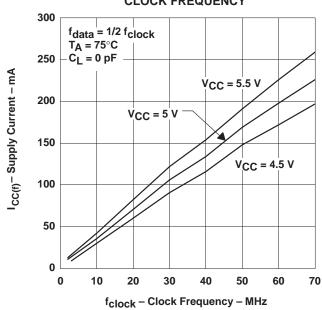

### TYPICAL CHARACTERISTICS

## **SUPPLY CURRENT CLOCK FREQUENCY**

Figure 18

www.ti.com 7-Oct-2025

#### PACKAGING INFORMATION

| Orderable part number | Status<br>(1) | Material type | Package   Pins  | Package qty   Carrier | <b>RoHS</b> (3) | Lead finish/<br>Ball material | MSL rating/<br>Peak reflow | Op temp (°C) | Part marking (6) |

|-----------------------|---------------|---------------|-----------------|-----------------------|-----------------|-------------------------------|----------------------------|--------------|------------------|

| SN54ACT3632HFP        | Active        | Production    | CFP (HFP)   132 | 1   TUBE              | No              | SNPB                          | N/A for Pkg Type           | -55 to 125   | SN54ACT3632HFP   |

| SN54ACT3632HFP.A      | Active        | Production    | CFP (HFP)   132 | 1   TUBE              | No              | SNPB                          | N/A for Pkg Type           | -55 to 125   | SN54ACT3632HFP   |

<sup>(1)</sup> Status: For more details on status, see our product life cycle.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

<sup>(2)</sup> Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

<sup>(4)</sup> Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> MSL rating/Peak reflow: The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

## **PACKAGE MATERIALS INFORMATION**

www.ti.com 10-Nov-2025

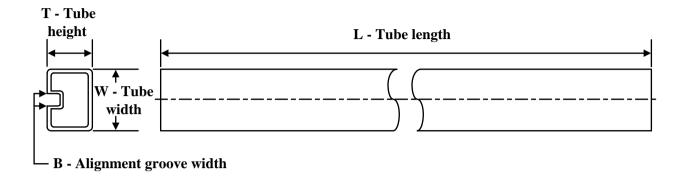

## **TUBE**

### \*All dimensions are nominal

| Device           | Package Name | Package Type | Pins | SPQ | L (mm) | W (mm) | T (µm) | B (mm) |

|------------------|--------------|--------------|------|-----|--------|--------|--------|--------|

| SN54ACT3632HFP   | HFP          | CFP          | 132  | 1   | 506.98 | 17.91  | 12570  | 5.46   |

| SN54ACT3632HFP.A | HFP          | CFP          | 132  | 1   | 506.98 | 17.91  | 12570  | 5.46   |

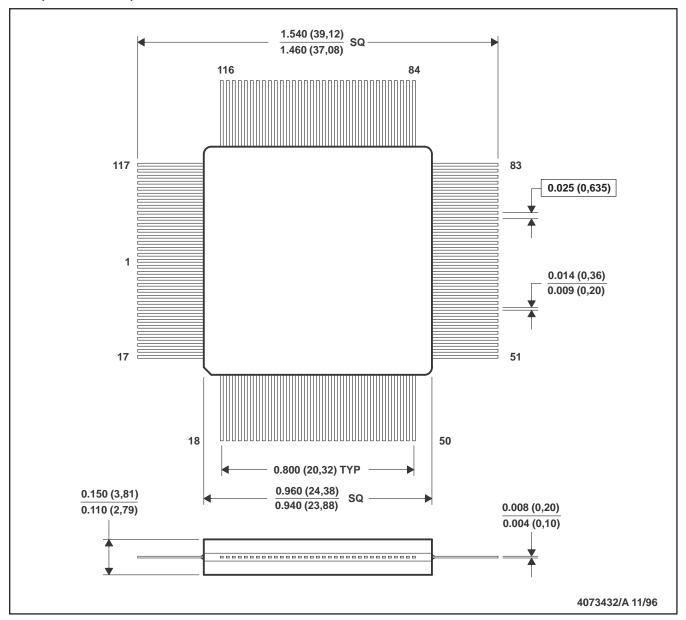

## HFP (S-GQFP-F132)

### **CERAMIC QUAD FLATPACK**

NOTES: A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- C. This package can be hermetically sealed with a ceramic lid using glass frit.

- $\label{eq:D.Body} \text{D. Body dimensions do not include glass overrun or protrusions.}$

### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you fully indemnify TI and its representatives against any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale, TI's General Quality Guidelines, or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products. Unless TI explicitly designates a product as custom or customer-specified, TI products are standard, catalog, general purpose devices.

TI objects to and rejects any additional or different terms you may propose.

Copyright © 2025, Texas Instruments Incorporated

Last updated 10/2025