SLOS531B-MAY 2007-REVISED OCTOBER 201

# 3-Channel RGBHV Video Buffer with I<sup>2</sup>C™ Control, 2:1 Input Mux, Monitor Pass-Through, and Selectable Input Bias Modes

Check for Samples: THS7347

#### **FEATURES**

- 3-Video Amplifiers for CVBS, S-Video, EDTV, HDTV Y'P'<sub>B</sub>P'<sub>R</sub>, G'B'R', and R'G'B' Video

- H/V Sync Paths with Adjustable Schmitt Trigger

- 2:1 Input Mux

- I<sup>2</sup>C Control of All Functions on Each Channel

- Unity-Gain Buffer Path for ADC Buffering:

- 500-MHz Bandwidth, 1200-V/µs Slew Rate

- Monitor Pass-Through Function:

- 500-MHz Bandwidth, 1300-V/µs Slew Rate

- 6-dB Gain with SAG Correction Capable

- High Output Impedance in Disable State

- Selectable Input Bias Modes:

- AC-Coupled with Sync-Tip Clamp

- AC-Coupled with Bias

- DC-Coupled with Offset Shift

- DC-Coupled

- +2.7-V to +5-V Single-Supply Operation

- Total Power Consumption: 265 mW at 3.3 V

- Disable Function Reduces Current to 0.1 µA

- · Rail-to-Rail Output:

- Output Swings Within 0.1 V of the Rails,

Allowing AC- or DC-Output Coupling

- · Lead-free, RoHS TQFP Package

#### **APPLICATIONS**

- Projectors

- Professional Video Systems

- LCD/ DLP<sup>®</sup>/LOCS Input Buffering

#### DESCRIPTION

Fabricated using the revolutionary complimentary silicon-germanium (SiGe) BiCom3 process, the THS7347 is a low-power, single-supply 2.7-V to 5-V 3-channel integrated video buffer with horizontal (H) and vertical (V) sync signal paths. It incorporates a 500-MHz bandwidth, 1200-V/µs unity-gain buffer ideal for driving analog-to-digital converters (ADCs) and video decoders. In parallel with the unity-gain buffer, a monitor pass-through path allows for passing the input signal on to other systems. This path has a 6-dB gain, 500-MHz bandwidth, 1300-V/µs slew rate, SAG correction capability, and high output impedance while disabled.

Each channel of the THS7347 is individually I<sup>2</sup>C-configurable for all functions, including controlling the 2:1 input mux. Its rail-to-rail output stage allows for both ac- and dc-coupling applications.

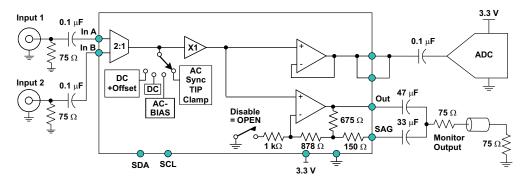

3.3 V Single-Supply Projector Input System with Monitor Pass-Through (One of Three R'G'B' Channels Shown)

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PowerPAD is a trademark of Texas Instruments. DLP is a registered trademark of Texas Instruments. I<sup>2</sup>C is a trademark of NXP Semiconductors, Inc. All other trademarks are the property of their respective owners.

#### **DESCRIPTION, CONTINUED**

As part of the THS7347 flexibility, the device input can be selected for ac- or dc-coupled inputs. The ac-coupled modes include a sync-tip clamp option for CVBS/Y'/G'B'R' with sync or a fixed bias for the C'/P'<sub>B</sub>/P'<sub>R</sub>/R'G'B' channels without sync. The dc input options include a dc input or a dc+Offset shift to allow for a full sync dynamic range at the output with 0-V input.

The THS7347 is available in a lead-free, RoHS-compliant TQFP package.

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

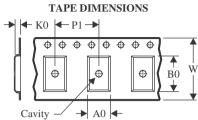

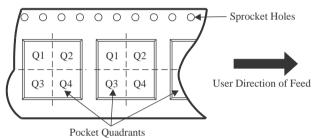

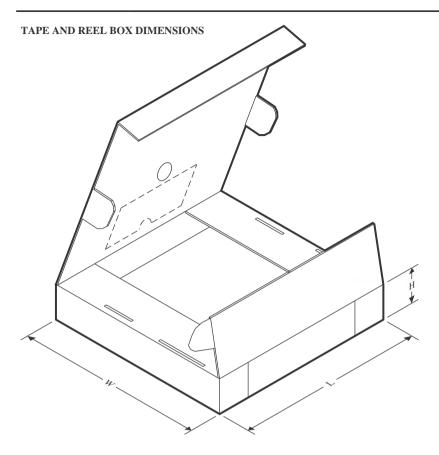

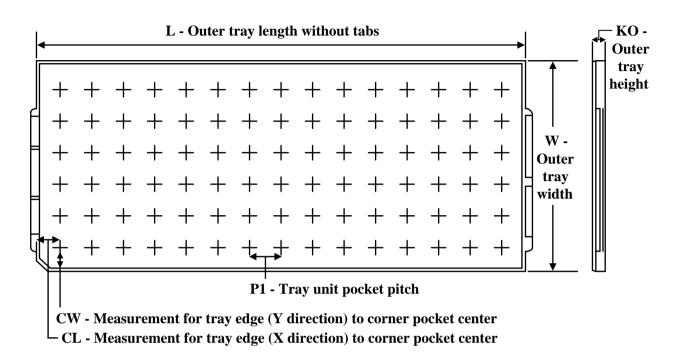

#### PACKAGING/ORDERING INFORMATION<sup>(1)</sup>

| PACKAGED DEVICES | PACKAGE TYPE           | TRANSPORT MEDIA, QUANTITY |

|------------------|------------------------|---------------------------|

| THS7347IPHP      | LITOED 40 Device DADIM | Tray, 250                 |

| THS7347IPHPR     | HTQFP-48 PowerPAD™     | Tape and Reel, 1000       |

For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI

web site at www.ti.com.

#### **ABSOLUTE MAXIMUM RATINGS**(1)

Over operating free-air temperature range (unless otherwise noted).

|                  |                      |                                                            | THS7347                                   | UNIT |  |

|------------------|----------------------|------------------------------------------------------------|-------------------------------------------|------|--|

| V <sub>SS</sub>  | Supply voltage, GND  | to V <sub>A</sub> or GND to V <sub>DD</sub>                | 5.5                                       | V    |  |

| VI               | Input voltage        |                                                            | –0.4 to V <sub>A</sub> or V <sub>DD</sub> | V    |  |

| lo               | Continuous output cu | rrent                                                      | ±80                                       | mA   |  |

|                  | Continuous power dis | ssipation                                                  | See Dissipation Rating Table              |      |  |

| T <sub>J</sub>   | Maximum junction ter | mperature, any condition <sup>(2)</sup>                    | +150                                      | °C   |  |

| TJ               | Maximum junction ter | mperature, continuous operation, long term reliability (3) | +125                                      | °C   |  |

| T <sub>stg</sub> | Storage temperature  | range                                                      | -65 to +150                               | °C   |  |

| -                | Lead temperature 1,6 | 6 mm (1/16 inch) from case for 10 seconds                  | 300                                       | °C   |  |

|                  |                      | НВМ                                                        | 1500                                      | V    |  |

|                  | ESD ratings          | CDM                                                        | 1500                                      | V    |  |

|                  |                      | MM                                                         | 100                                       | V    |  |

<sup>(1)</sup> Stresses above those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied Exposure to absolute maximum rated conditions for extended periods may degrade device reliability.

(2) The absolute maximum junction temperature under any condition is limited by the constraints of the silicon process.

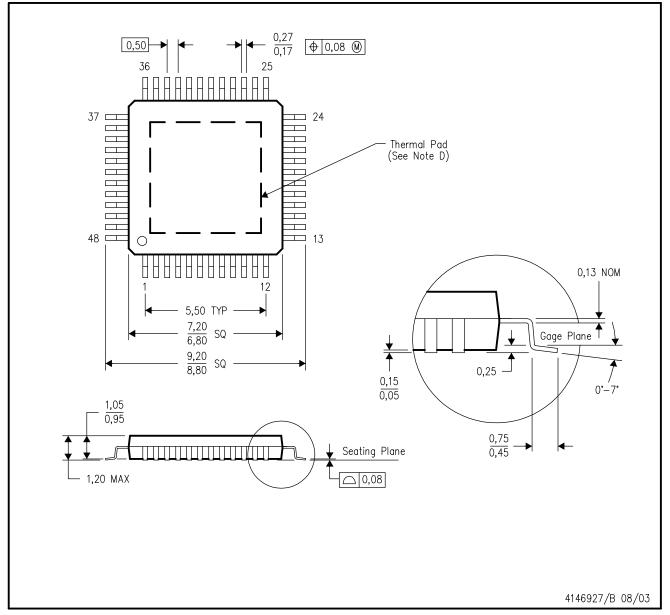

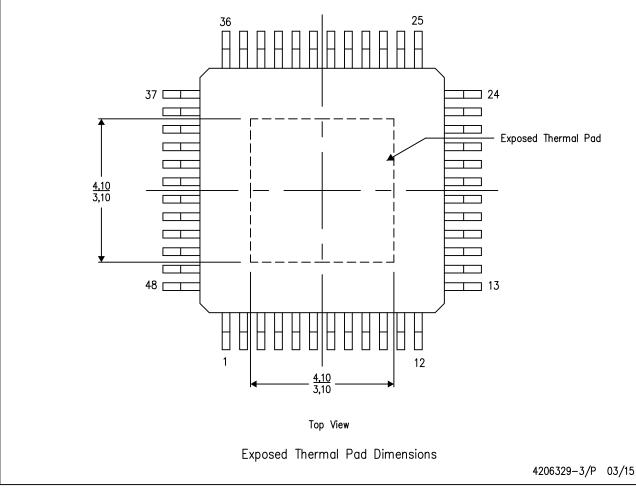

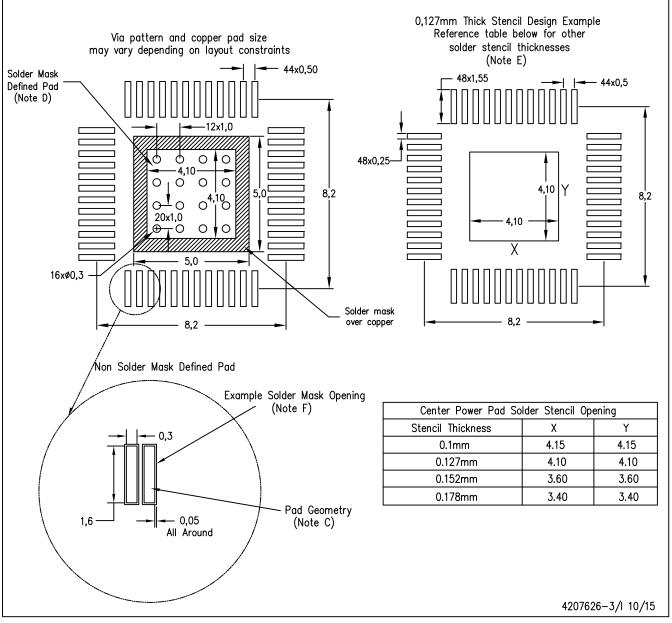

#### **DISSIPATION RATINGS**

|                              | θјς    |        |                        | RATING <sup>(1) (2)</sup><br>= +125°C) |  |  |

|------------------------------|--------|--------|------------------------|----------------------------------------|--|--|

| PACKAGE                      | (°Č/W) | (°C/W) | T <sub>A</sub> = +25°C | T <sub>A</sub> = +85°C                 |  |  |

| HTQFP-48 with PowerPAD (PHP) | 1.2    | 35     | 2.85 W                 | 1.14 W                                 |  |  |

<sup>(1)</sup> This data was taken with a PowerPAD standard 3-inch by 3-inch, 4-layer printed circuit board (PCB) with internal ground plane connections to the PowerPAD.

<sup>(3)</sup> The absolute maximum junction temperature for continuous operation is limited by the package constraints. Operation above this temperature may result in reduced reliability and/or lifetime of the device.

<sup>(2)</sup> Power rating is determined with a junction temperature of +125°C. This temperature is the point where distortion starts to substantially increase and long-term reliability starts to be reduced. Thermal management of the final PCB should strive to keep the junction temperature at or below +125°C for best performance and reliability.

www.ti.com

#### RECOMMENDED OPERATING CONDITIONS

|          |                                                                                     | MIN      | NOM N | ΛAΝ | UNIT |

|----------|-------------------------------------------------------------------------------------|----------|-------|-----|------|

| $V_{DD}$ | Digital supply voltage                                                              | 2.7      |       | 5   | V    |

| $V_A$    | Analog supply voltage. Must be equal to or greater than $V_{\mbox{\scriptsize DD}}$ | $V_{DD}$ |       | 5   | V    |

| $T_A$    | Ambient temperature                                                                 | -40      |       | +85 | °C   |

# ELECTRICAL CHARACTERISTICS, $V_A = V_{DD} = 3.3 \text{ V}$

$R_L$  = 150  $\Omega$  || 5 pF to GND for Monitor Output, 19 k $\Omega$  || 8 pF Load to GND for Buffer Output, SAG pin shorted to Monitor Output Pin, unless otherwise noted.

| PARAME<br>AC PERFORMANCE | TER            |                                                        |           |           | 000:            |                   |         |                 |

|--------------------------|----------------|--------------------------------------------------------|-----------|-----------|-----------------|-------------------|---------|-----------------|

|                          |                | TEST CONDITIONS                                        | +25°C     | +25°C     | 0°C to<br>+70°C | –40°C to<br>+85°C | UNIT    | MIN/MAX/<br>TYP |

|                          |                |                                                        |           |           |                 |                   |         |                 |

| Small-signal             | Buffer output  |                                                        | 500       |           |                 |                   | MHz     | Тур             |

| 1 1 1 1 1 1 ( 0 10)      | Monitor output | $V_O = 0.2 V_{PP}$                                     | 450       |           |                 |                   | MHz     | Тур             |

| . 15 ()                  | Buffer output  |                                                        | 425       |           |                 |                   | MHz     | Тур             |

| –1 dB flatness           | Monitor output | $V_0 = 0.2 V_{PP}$                                     | 375       |           |                 |                   | MHz     | Тур             |

| Large-signal             | Buffer output  | V <sub>O</sub> = 1 V <sub>PP</sub>                     | 475       |           |                 |                   | MHz     | Тур             |

| 1 1 1 M ( 0 ID)          | Monitor output | $V_O = 2 V_{PP}$                                       | 240       |           |                 |                   | MHz     | Тур             |

| 0                        | Buffer output  | V <sub>O</sub> = 1 V <sub>PP</sub>                     | 1050      |           |                 |                   | V/µs    | Тур             |

| Slew rate                | Monitor output | $V_O = 2 V_{PP}$                                       | 1050      |           |                 |                   | V/µs    | Тур             |

| Group delay at           | Buffer output  |                                                        | 1.2       |           |                 |                   | ns      | Тур             |

| 400 1:11-                | Monitor output |                                                        | 1.2       |           |                 |                   | ns      | Тур             |

| <b>5</b> ′′′             | Buffer output  | NETO (DA)                                              | 0.05/0.05 |           |                 |                   | %       | Тур             |

| Differential gain        | Monitor output | NTSC/PAL                                               | 0.1/0.1   |           |                 |                   | %       | Тур             |

|                          | Buffer output  |                                                        | 0.1/0.15  |           |                 |                   | degrees | Тур             |

| Differential phase       | Monitor output | NTSC/PAL                                               | 0.15/0.2  |           |                 |                   | degrees | Тур             |

| Total harmonic           | Buffer output  | V <sub>O</sub> = 1 V <sub>PP</sub>                     | -58       |           |                 |                   | dB      | Тур             |

| distantian £ 4 MIII      | Monitor output | $V_O = 2 V_{PP}$                                       | -57       |           |                 |                   | dB      | Тур             |

|                          | Buffer output  |                                                        | 63        |           |                 |                   | dB      | Тур             |

| Signal-to-noise ratio    | Monitor output | No weighting, up to 100 MHz                            | 65        |           |                 |                   | dB      | Тур             |

| Channel-to-channel       | Buffer output  | f = 100 MHz                                            | -40       |           |                 |                   | dB      | Тур             |

| onamic to chamic         | Monitor output |                                                        | -36       |           |                 |                   | dB      | Тур             |

|                          | Buffer output  | f = 100 MHz                                            | 64        |           |                 |                   | dB      | Тур             |

| MUX isolation            | Monitor output |                                                        | 66        |           |                 |                   | dB      | Тур             |

|                          | Buffer output  | f = 100 kHz; V <sub>O</sub> = 1 V <sub>PP</sub>        | 0         |           |                 |                   | dB      | Тур             |

| Gain                     | Monitor output | f = 100 kHz; V <sub>O</sub> = 2 V <sub>PP</sub>        | 6         | 5.8/6.25  | 5.75/6.3        | 5.75/6.35         | dB      | Min/Max         |

|                          | Buffer output  | 7 0 11                                                 | 6         |           |                 |                   | ns      | Тур             |

| Settling time            | Monitor output | $V_{IN} = 1 V_{PP}$ ; 0.5% settling                    | 6         |           |                 |                   | ns      | Тур             |

|                          | Buffer output  |                                                        | 0.3       |           |                 |                   | Ω       | Тур             |

| Output impedance         | Monitor output | f = 10 MHz                                             | 0.4       |           |                 |                   | Ω       | Тур             |

| DC PERFORMANCE           |                |                                                        |           |           |                 |                   |         | - 71-           |

|                          | Buffer output  |                                                        | 15        | ±80       | ±85             | ±85               | mV      | Max             |

| Output offset voltage    | Monitor output | Bias = dc                                              | 20        | ±120      | ±125            | ±125              | mV      | Max             |

|                          | Buffer output  |                                                        | 20        | 1120      | 1120            | 20                | μV/°C   | Тур             |

| Average offset           | Monitor output | Bias = dc                                              |           |           |                 | 20                | μV/°C   | Тур             |

|                          | mornior output | Bias = dc + shift, V <sub>IN</sub> = 0 V               | 255       | 175/355   | 165/365         | 160/370           | mV      | Min/Max         |

|                          | Buffer output  | Bias = ac                                              | 1.0       | 0.85/1.15 | 0.8/1.2         | 0.8/1.2           | V       | Min/Max         |

| Bias output voltage      |                | Bias = ac<br>Bias = dc + shift, $V_{IN} = 0 \text{ V}$ | 235       | 145/350   | 135/360         | 130/365           | mV      | Min/Max         |

|                          | Monitor output | Bias = ac  Bias = ac                                   | 1.7       | 1.55/1.85 | 1.5/1.9         | 1.5/1.9           | V       | Min/Max         |

| 0 " 1                    | Buffer output  | Dias = ac                                              | 290       | 200/405   | 1.5/1.9         | 190/415           | mV      | Min/Max         |

| - t                      | •              | Bias = ac STC, clamp voltage                           |           |           |                 |                   |         |                 |

| voltage                  | Monitor output | , , ,                                                  | 300       | 200/400   | 195/405         | 190/410           | mV      | Min/Max         |

# ELECTRICAL CHARACTERISTICS, $V_A = V_{DD} = 3.3 \text{ V}$ (continued)

$R_L$  = 150  $\Omega$  || 5 pF to GND for Monitor Output, 19 k $\Omega$  || 8 pF Load to GND for Buffer Output, SAG pin shorted to Monitor Output Pin, unless otherwise noted.

|                                          |                            |                                                      | TYP    |          | OVE             | R TEMPERA         | TURE  |                 |

|------------------------------------------|----------------------------|------------------------------------------------------|--------|----------|-----------------|-------------------|-------|-----------------|

| PARAI                                    | METER                      | TEST CONDITIONS                                      | +25°C  | +25°C    | 0°C to<br>+70°C | –40°C to<br>+85°C | UNIT  | MIN/MAX/<br>TYP |

| DC PERFORMANC                            | E, continued               |                                                      |        |          |                 |                   | •     |                 |

| Input bias current                       |                            | Bias = dc; (–) implies I <sub>B</sub> out of the pin | -1.3   | -3.0     | -3.5            | -3.5              | μA    | Max             |

| Average bias curren                      | t drift                    | Bias = dc                                            |        |          |                 | 10                | nA/°C | Тур             |

|                                          |                            | Bias = ac STC, low bias                              | 2.3    | 0.9/3.6  | 0.8/3.8         | 0.7/3.9           | μA    | Min/Max         |

| Sync tip clamp bias                      | current                    | Bias = ac STC, mid bias                              | 5.8    | 3.8/8.0  | 3.7/8.2         | 3.6/8.3           | μA    | Min/Max         |

|                                          |                            | Bias = ac STC, high bias                             | 8.1    | 5.7/10.8 | 5.6/11.0        | 5.5/11.1          | μA    | Min/Max         |

| INPUT CHARACTE                           | RISTICS                    |                                                      |        | 1        |                 |                   |       |                 |

| Input voltage range                      |                            | Bias = dc                                            | 0 to 2 |          |                 |                   | V     | Тур             |

|                                          |                            | Bias = ac bias mode                                  | 25     |          |                 |                   | kΩ    | Тур             |

| Input resistance                         |                            | Bias = dc, dc + shift, ac STC                        | 3      |          |                 |                   | ΜΩ    | Тур             |

| Input capacitance                        |                            |                                                      | 1.5    |          |                 |                   | pF    | Тур             |

| OUTPUT CHARAC                            | TERISTICS: MONIT           | TOR OUTPUT                                           |        |          |                 |                   |       | 7.              |

|                                          |                            | $R_L = 150 \Omega \text{ to } 1.65 \text{ V}$        | 3.15   | 2.9      | 2.8             | 2.8               | V     | Min             |

|                                          |                            | $R_1 = 150 \Omega$ to GND                            | 3.05   | 2.85     | 2.75            | 2.75              | V     | Min             |

| High output voltage                      | swing                      | R <sub>1</sub> = 75 Ω to 1.65 V                      | 3.05   |          |                 |                   | V     | Тур             |

|                                          |                            | $R_L = 75 \Omega$ to GND                             | 2.9    |          |                 |                   | V     | Тур             |

| Low output voltage swing                 |                            | R <sub>I</sub> = 150 Ω to 1.65 V                     | 0.15   | 0.25     | 0.28            | 0.29              | V     |                 |

|                                          |                            | $R_L = 150 \Omega$ to GND                            | 0.1    | 0.18     | 0.21            | 0.22              | V     |                 |

|                                          |                            | R <sub>1</sub> = 75 Ω to 1.65 V                      | 0.25   |          |                 | <del></del>       |       |                 |

|                                          |                            | $R_L = 75 \Omega \text{ to GND}$                     | 0.08   |          |                 |                   |       |                 |

|                                          | Sourcing                   | 1,2 19 12 10 6112                                    | 80     | 50       | 47              | 45                |       |                 |

| Output current                           | Sinking                    | $R_L$ = 10 Ω to 1.65 V                               | 75     | 50       | 47              | 45                | 71    |                 |

| OUTPUT CHARACT                           |                            | ER OUTPUT                                            |        | - 55     |                 |                   |       |                 |

| High output voltage                      |                            |                                                      |        |          |                 |                   |       | Ī               |

| (Limited by input rar                    |                            | Lood - 10 kO    9 pE to 1 65 V                       | 2      | 1.8      | 1.75            | 1.75              | V     | Min             |

| Low Output voltage (Limited by input rar | swing<br>age and G = 0 dB) | Load = 19 kΩ ∥ 8 pF to 1.65 V                        | 0.05   | 0.12     | 0.13            | 0.14              | V     | Max             |

| Output Current                           | Sourcing                   | $R_L = 10 \Omega$ to GND                             | 80     | 50       | 47              | 45                | mA    | Min             |

| Odiput Current                           | Sinking                    | $R_L = 10 \Omega$ to 1.65 V                          | 75     | 50       | 47              | 45                | mA    | Min             |

| POWER SUPPLY:                            | ANALOG                     |                                                      |        |          |                 |                   |       |                 |

| Maximum operating                        | voltage                    | $V_A$                                                | 3.3    | 5.5      | 5.5             | 5.5               | V     | Max             |

| Minimum operating                        | voltage                    | V <sub>A</sub>                                       | 3.3    | 2.7      | 2.7             | 2.7               | V     | Min             |

| Maximum quiescent                        | current                    | $V_A$ , dc + shift mode, $V_{IN}$ = 100 mV           | 80     | 100      | 103             | 105               | mA    | Max             |

| Minimum quiescent                        | current                    | $V_A$ , dc + shift mode, $V_{IN}$ = 100 mV           | 80     | 60       | 57              | 55                | mA    | Min             |

| Power supply rejecti                     | on (+PSRR)                 | Buffer output                                        | 50     |          |                 |                   | dB    | Тур             |

| POWER SUPPLY: I                          | DIGITAL                    |                                                      |        |          |                 |                   |       |                 |

| Maximum operating                        | voltage                    | $V_{DD}$                                             | 3.3    | 5.5      | 5.5             | 5.5               | V     | Max             |

| Minimum operating                        | voltage                    | V <sub>DD</sub>                                      | 3.3    | 2.7      | 2.7             | 2.7               | V     | Min             |

| Maximum quiescent current                |                            | $V_{DD}$ , $V_{IN} = 0 V$                            | 0.65   | 1.2      | 1.3             | 1.4               | mA    | Max             |

| Minimum quiescent                        | current                    | $V_{DD}$ , $V_{IN} = 0$ V                            | 0.65   | 0.35     | 0.3             | 0.25              | mA    | Min             |

| DISABLE CHARAC                           | TERISTICS: ALL C           | CHANNELS DISABLED                                    | *      | •        |                 |                   | •     | *               |

| Quiescent current                        |                            | All channels disabled                                | 0.1    |          |                 |                   | μA    | Тур             |

| Turn-on time delay (                     | t <sub>ON</sub> )          | Time for I <sub>S</sub> to reach 50% of final value  | 5      |          |                 |                   | μs    | Тур             |

| Turn-on time delay (                     | torr)                      | after I <sup>2</sup> C control is initiated          | 2      |          |                 |                   | μs    | Тур             |

# ELECTRICAL CHARACTERISTICS, $V_A = V_{DD} = 3.3 \text{ V}$ (continued)

$R_L$  = 150  $\Omega$  || 5 pF to GND for Monitor Output, 19 k $\Omega$  || 8 pF Load to GND for Buffer Output, SAG pin shorted to Monitor Output Pin, unless otherwise noted.

|                                                |                                                                              | TYP      | OVER TEMPERATURE |          |                   |      |                 |

|------------------------------------------------|------------------------------------------------------------------------------|----------|------------------|----------|-------------------|------|-----------------|

| PARAMETER                                      | TEST CONDITIONS                                                              | +25°C    | +25°C +25°C -    |          | –40°C to<br>+85°C | UNIT | MIN/MAX/<br>TYP |

| DIGITAL CHARACTERISTICS(1)                     |                                                                              |          | 1                |          |                   |      |                 |

| High level input voltage                       | V <sub>IH</sub>                                                              | 2.3      |                  |          |                   | V    | Тур             |

| Low level input voltage                        | V <sub>IL</sub>                                                              | 1.0      |                  |          |                   | V    | Тур             |

| H/V SYNC CHARACTERISTICS: R <sub>Lo</sub>      | $_{\rm ad}$ = 1 k $\Omega$ To GND <sup>(2)</sup>                             |          |                  |          |                   |      |                 |

| Schmitt trigger adjust pin voltage             | Reference for Schmitt trigger                                                | 1.47     | 1.35/1.6         | 1.3/1.65 | 1.27/1.68         | V    | Min/Max         |

| Schmitt trigger threshold range                | Allowable range for Schmitt trigger adjust                                   | 0.9 to 2 |                  |          |                   | V    | Тур             |

| Schmitt trigger VT+                            | Positive-going input voltage threshold relative to Schmitt trigger threshold |          |                  |          |                   | V    | Тур             |

| Schmitt trigger VT-                            | Negative-going input voltage threshold relative to Schmitt trigger threshold | -0.3     |                  |          |                   | V    | Тур             |

| Schmitt trigger threshold pin input resistance | Input resistance into Control pin                                            | 10       |                  |          |                   | kΩ   | Тур             |

| H/V Sync input impedance                       |                                                                              | 10       |                  |          |                   | МΩ   | Тур             |

| H/V Sync high output voltage                   | 1 kΩ to GND                                                                  | 3.15     | 3.05             | 3.0      | 3.0               | V    | Min             |

| H/V Sync low output voltage                    | 1 kΩ to GND                                                                  | 0.01     | 0.05             | 0.1      | 0.1               | V    | Max             |

| H/V Sync source current                        | 10 Ω to GND                                                                  | 50       | 35               | 30       | 30                | mA   | Min             |

| H/V Sync sink current                          | 10 Ω to 3.3 V                                                                | 35       | 25               | 23       | 21                | mA   | Min             |

| H/V Delay                                      | Delay from Input to output                                                   | 6.5      |                  |          |                   | ns   | Тур             |

| H/V to buffer output skew                      |                                                                              | 5        |                  |          |                   | ns   | Тур             |

<sup>(1)</sup> Standard CMOS logic.

(2) Schmitt trigger threshold is defined by (VT+ - VT-)/2.

# ELECTRICAL CHARACTERISTICS, $V_A = V_{DD} = 5 \text{ V}$

$R_L$  = 150 $\Omega$  || 5pF to GND for Monitor Output, 19k $\Omega$  || 8pF Load to GND for Buffer Output, SAG pin shorted to Monitor Output Pin, unless otherwise noted.

|                       |                |                                                      | TYP       | TYP OVER TEMPERA |                 |                   |         | ΓURE            |  |

|-----------------------|----------------|------------------------------------------------------|-----------|------------------|-----------------|-------------------|---------|-----------------|--|

| PARAM                 | ETER           | TEST CONDITIONS                                      | +25°C     | +25°C            | 0°C to<br>+70°C | –40°C to<br>+85°C | UNIT    | MIN/MAX/<br>TYP |  |

| AC PERFORMANCE        |                |                                                      |           |                  |                 |                   |         |                 |  |

| Small-signal          | Buffer output  |                                                      | 550       |                  |                 |                   | MHz     | Тур             |  |

| bandwidth (–3 dB)     | Monitor output | $V_O = 0.2 V_{PP}$                                   | 500       |                  |                 |                   | MHz     | Тур             |  |

|                       | Buffer output  |                                                      | 450       |                  |                 |                   | MHz     | Тур             |  |

| –1 dB flatness        | Monitor output | $V_O = 0.2 V_{PP}$                                   | 400       |                  |                 |                   | MHz     | Тур             |  |

| Large-signal          | Buffer output  | $V_O = 1 V_{PP}$                                     | 525       |                  |                 |                   | MHz     | Тур             |  |

| bandwidth (–3 dB)     | Monitor output | $V_O = 2 V_{PP}$                                     | 325       |                  |                 |                   | MHz     | Тур             |  |

|                       | Buffer output  | V <sub>O</sub> = 1 V <sub>PP</sub>                   | 1200      |                  |                 |                   | V/µs    | Тур             |  |

| Slew rate             | Monitor output | $V_O = 2 V_{PP}$                                     | 1350      |                  |                 |                   | V/µs    | Тур             |  |

| Group delay at        | Buffer output  |                                                      | 1.15      |                  |                 |                   | ns      | Тур             |  |

| 100 kHz               | Monitor output |                                                      | 1.15      |                  |                 |                   | ns      | Тур             |  |

|                       | Buffer output  |                                                      | 0.05/0.05 |                  |                 |                   | %       | Тур             |  |

| Differential gain     | Monitor output | NTSC/PAL                                             | 0.1/0.1   |                  |                 |                   | %       | Тур             |  |

|                       | Buffer output  |                                                      | 0.05/0.05 |                  |                 |                   | degrees | Тур             |  |

| Differential phase    | Monitor output | NTSC/PAL                                             | 0.05/0.05 |                  |                 |                   | degrees | Тур             |  |

| Total harmonic        | Buffer output  | $V_O = 1 V_{PP}$                                     | -71       |                  |                 |                   | dB      | Тур             |  |

| distortion f = 1 MHz  | Monitor output | $V_O = 2 V_{PP}$                                     | -67       |                  |                 |                   | dB      | Тур             |  |

|                       | Buffer output  |                                                      | 63        |                  |                 |                   | dB      | Тур             |  |

| Signal-to-noise ratio | Monitor output | No weighting, up to 100 MHz                          | 65        |                  |                 |                   | dB      | Тур             |  |

| Channel-to-channel    | Buffer output  |                                                      | -40       |                  |                 |                   | dB      | Тур             |  |

| crosstalk             | Monitor output | f = 100 MHz                                          | -36       |                  |                 |                   | dB      | Тур             |  |

| MUX Isolation         | Buffer output  |                                                      | 64        |                  |                 |                   | dB      | Тур             |  |

|                       | Monitor output | f = 100 MHz                                          | 66        |                  |                 |                   | dB      | Тур             |  |

| 0.1                   | Buffer output  | f = 100 kHz; V <sub>O</sub> = 1 V <sub>PP</sub>      | 0         |                  |                 |                   | dB      | Тур             |  |

| Gain                  | Monitor output | f = 100 kHz; V <sub>O</sub> = 2 V <sub>PP</sub>      | 6         | 5.8/6.25         | 5.75/6.3        | 5.75/6.35         | dB      | Min/Max         |  |

| 0                     | Buffer output  | V 4 V 2 TO 4 VIII                                    | 6         |                  |                 |                   | ns      | Тур             |  |

| Settling time         | Monitor output | $V_{IN} = 1 V_{PP}$ ; 0.5% settling                  | 6         |                  |                 |                   | ns      | Тур             |  |

| 0                     | Buffer output  | ( 40.11)                                             | 0.3       |                  |                 |                   | Ω       | Тур             |  |

| Output impedance      | Monitor output | f = 10 MHz                                           | 0.4       |                  |                 |                   | Ω       | Тур             |  |

| DC PERFORMANCE        |                |                                                      |           | •                |                 |                   | •       |                 |  |

| 0                     | Buffer output  | D: I                                                 | 15        | ±80              | ±85             | ±85               | mV      | Max             |  |

| Output offset voltage | Monitor output | Bias = dc                                            | 20        | ±120             | ±125            | ±125              | mV      | Max             |  |

| Average offset        | Buffer output  | D: I                                                 |           |                  |                 | 20                | μV/°C   | Тур             |  |

| voltage drift         | Monitor output | Bias = dc                                            |           |                  |                 | 20                | μV/°C   | Тур             |  |

|                       | 5 "            | Bias = dc + shift, V <sub>IN</sub> = 0 V             | 265       | 185/370          | 175/380         | 170/385           | mV      | Min/Max         |  |

| D'                    | Buffer output  | Bias = ac                                            | 1.5       | 1.3/1.65         | 1.25/1.7        | 1.25/1.7          | V       | Min/Max         |  |

| Bias output voltage   |                | Bias = dc + shift, V <sub>IN</sub> = 0 V             | 235       | 145/345          | 135/355         | 130/360           | mV      | Min/Max         |  |

|                       | Monitor output | Bias = ac                                            | 2.65      | 2.5/2.8          | 2.45/2.85       | 2.45/2.85         | V       | Min/Max         |  |

| Sync tip clamp        | Buffer output  | Biography #                                          | 295       | 205/410          | 200/415         | 195/420           | mV      | Min/Max         |  |

| voltage               | Monitor output | Bias = ac STC, clamp voltage                         | 300       | 200/400          | 195/405         | 190/410           | mV      | Min/Max         |  |

| Input bias current    | •              | Bias = dc; (–) implies I <sub>B</sub> out of the pin | -1.4      | -3.0             | -3.5            | -3.5              | μΑ      | Max             |  |

| Average bias current  | drift          | Bias = dc                                            |           |                  |                 | 10                | nA/°C   | Тур             |  |

|                       |                | Bias = ac STC, low bias                              | 2.4       | 0.9/3.9          | 0.8/4.0         | 0.7/4.1           | μA      | Min/Max         |  |

| Sync tip clamp bias c | urrent         | Bias = ac STC, mid bias                              | 6.2       | 3.9/8.4          | 3.8/8.6         | 3.7/8.7           | μA      | Min/Max         |  |

|                       |                | Bias = ac STC, high bias                             | 8.6       | 6/11.2           | 5.8/11.4        | 5.7/11.5          | μΑ      | Min/Max         |  |

# ELECTRICAL CHARACTERISTICS, $V_A = V_{DD} = 5 V$ (continued)

$R_L$  = 150 $\Omega$  || 5pF to GND for Monitor Output, 19k $\Omega$  || 8pF Load to GND for Buffer Output, SAG pin shorted to Monitor Output Pin, unless otherwise noted.

|                                                                 |                     |                                                     | TYP          |      | OVER TEMPERATURE |                   |        |                 |

|-----------------------------------------------------------------|---------------------|-----------------------------------------------------|--------------|------|------------------|-------------------|--------|-----------------|

| PARAI                                                           | METER               | TEST CONDITIONS                                     | +25°C        |      |                  | -40°C to<br>+85°C | UNIT   | MIN/MAX/<br>TYP |

| INPUT CHARACTE                                                  | RISTICS             |                                                     |              |      |                  |                   |        |                 |

| Input voltage range                                             |                     | Bias = dc                                           | 0 to 3.4     |      |                  |                   | V      | Тур             |

| Innut registeres                                                |                     | Bias = ac bias mode                                 | 25           |      |                  |                   | kΩ     | Тур             |

| Input resistance                                                |                     | Bias = dc, dc + shift, ac STC                       | 3            |      |                  |                   | МΩ     | Тур             |

| Input capacitance                                               |                     |                                                     | 1.5          |      |                  |                   | pF     | Тур             |

| OUTPUT CHARACT                                                  | TERISTICS: MONIT    | OR OUTPUT                                           |              |      |                  |                   |        |                 |

|                                                                 |                     | $R_L$ = 150 $\Omega$ to 2.5 $V$                     | 4.8          | 4.65 | 4.6              | 4.6               | V      | Min             |

| IP I A A A A A                                                  |                     | $R_L = 150 \Omega$ to GND                           | 4.7          | 4.55 | 4.5              | 4.5               | V      | Min             |

| High output voltage                                             | Swing               | $R_L$ = 75 $\Omega$ to 2.5 $V$                      | 4.7          |      |                  |                   | V      | Тур             |

|                                                                 |                     | $R_L = 75 \Omega$ to GND                            | 4.6          |      |                  |                   | V      | Тур             |

|                                                                 |                     | $R_L = 150 \Omega$ to 2.5 V                         | 0.2          | 0.25 | 0.28             | 0.30              | V      | Max             |

| Law autout valtage                                              | auda a              | $R_L$ = 150 $\Omega$ to GND                         | 0.1          | 0.19 | 0.23             | 0.24              | V      | Max             |

| Low output voltage sv                                           | swing               | $R_L = 75 \Omega$ to 2.5 V                          | 0.24         |      |                  |                   | V      | Тур             |

|                                                                 |                     | $R_L = 75 \Omega$ to GND                            | 0.085        |      |                  |                   | V      | Тур             |

| 0.44                                                            | Sourcing            | D 40.04-05.V                                        | 110          | 85   | 80               | 75                | mA     | Min             |

| Output current                                                  | Sinking             | $R_L = 10 \Omega \text{ to } 2.5 \text{ V}$         | 110          | 85   | 80               | 75                | mA Min | Min             |

| OUTPUT CHARACT                                                  | TERISTICS: BUFFE    | R OUTPUT                                            | <del>"</del> |      |                  |                   |        |                 |

| High output voltage swing (Limited by input range and G = 0 dB) |                     | Load = 19 kΩ ∥ 8 pF to 2.5 V                        | 3.4          | 3.1  | 3.0              | 3.0               | V      | Min             |

| Low output voltage swing (Limited by input range and G = 0 dB)  |                     | Load = 19 K12    0 pr to 2.5 v                      | 0.05         | 0.12 | 0.13             | 0.14              | V      | Max             |

| Output ourrent                                                  | Sourcing            | $R_L = 10 \Omega$ to GND                            | 110          | 85   | 80               | 75                | mA     | Min             |

| Output current                                                  | Sinking             | $R_L$ = 10 $\Omega$ to 2.5 V                        | 110          | 85   | 80               | 75                | mA     | Min             |

| POWER SUPPLY: A                                                 | ANALOG              |                                                     |              |      |                  |                   |        |                 |

| Maximum operating                                               | voltage             | V <sub>A</sub>                                      | 5.0          | 5.5  | 5.5              | 5.5               | V      | Max             |

| Minimum operating                                               | voltage             | V <sub>A</sub>                                      | 5.0          | 2.7  | 2.7              | 2.7               | V      | Min             |

| Maximum quiescent                                               | current             | $V_A$ , dc + shift mode, $V_{IN}$ = 100 mV          | 90           | 112  | 115              | 117               | mA     | Max             |

| Minimum quiescent                                               | current             | $V_A$ , dc + shift mode, $V_{IN}$ = 100 mV          | 90           | 68   | 65               | 63                | mA     | Min             |

| Power supply rejecti                                            | ion (+PSRR)         | Buffer Output                                       | 46           |      |                  |                   | dB     | Тур             |

| POWER SUPPLY: I                                                 | DIGITAL             |                                                     |              |      |                  |                   |        |                 |

| Maximum operating                                               | voltage             | $V_{DD}$                                            | 5.0          | 5.5  | 5.5              | 5.5               | V      | Max             |

| Minimum operating                                               | voltage             | V <sub>DD</sub>                                     | 5.0          | 2.7  | 2.7              | 2.7               | V      | Min             |

| Maximum quiescent                                               | current             | $V_{DD}$ , $V_{IN} = 0 V$                           | 1            | 2    | 3                | 3                 | mA     | Max             |

| Minimum quiescent                                               |                     | $V_{DD}$ , $V_{IN} = 0$ V                           | 1            | 0.5  | 0.4              | 0.4               | mA     | Min             |

| DIGITAL CHARACT                                                 | TERISTICS(1)        |                                                     |              |      |                  |                   |        |                 |

| High level input voltage                                        |                     | V <sub>IH</sub>                                     | 3.5          |      |                  |                   | V      | Тур             |

| Low level input volta                                           | ige                 | V <sub>IL</sub>                                     | 1.5          |      |                  |                   | V      | Тур             |

| DISABLE CHARAC                                                  | TERISTICS: ALL C    | HANNELS DISABLED                                    |              | -    | <del>.</del>     |                   | -      | -               |

| Quiescent current                                               |                     | All channels disabled                               | 1            |      |                  |                   | μA     | Тур             |

| Turn-on time delay (                                            | (t <sub>ON</sub> )  | Time for I <sub>S</sub> to reach 50% of final value | 5            |      |                  |                   | μs     | Тур             |

| Turn-on time delay (                                            | (t <sub>OFF</sub> ) | after I <sup>2</sup> C control is initiated         | 2            |      |                  |                   | μs     | Тур             |

<sup>(1)</sup> Standard CMOS logic.

# ELECTRICAL CHARACTERISTICS, $V_A = V_{DD} = 5 \text{ V}$ (continued)

$R_L$  = 150 $\Omega$  || 5pF to GND for Monitor Output, 19k $\Omega$  || 8pF Load to GND for Buffer Output, SAG pin shorted to Monitor Output Pin, unless otherwise noted.

|                                                |                                                                              | TYP      |           | OVER TEMPERATU |           |      |                 |

|------------------------------------------------|------------------------------------------------------------------------------|----------|-----------|----------------|-----------|------|-----------------|

| PARAMETER                                      | TEST CONDITIONS                                                              | +25°C    | +25°C     | 0°C to         |           | UNIT | MIN/MAX/<br>TYP |

| H/V SYNC CHARACTERISTICS: RLo                  | $_{\rm ad}$ = 1 k $\Omega$ To GND <sup>(2)</sup>                             |          |           |                |           |      |                 |

| Schmitt trigger adjust pin voltage             | Reference for Schmitt trigger                                                | 1.54     | 1.43/1.65 | 1.38/1.7       | 1.35/1.73 | V    | Min/Max         |

| Schmitt trigger threshold range                | Allowable range for Schmitt trigger adjust                                   | 0.9 to 2 |           |                |           | V    | Тур             |

| Schmitt trigger VT+                            | Positive-going input voltage threshold relative to Schmitt trigger threshold | 0.25     |           |                |           | V    | Тур             |

| Schmitt trigger VT-                            | Negative-going input voltage threshold relative to Schmitt trigger threshold | -0.3     |           |                |           | V    | Тур             |

| Schmitt trigger threshold pin input resistance | Input resistance into Control pin                                            | 10       |           |                |           | kΩ   | Тур             |

| H/V Sync input impedance                       |                                                                              | 10       |           |                |           | МΩ   | Тур             |

| H/V Sync high output voltage                   | 1 kΩ to GND                                                                  | 4.8      | 4.7       | 4.6            | 4.6       | V    | Min             |

| H/V Sync low output voltage                    | 1 kΩ to GND                                                                  | 0.01     | 0.05      | 0.1            | 0.1       | V    | Max             |

| H/V Sync source current                        | 10 Ω to GND                                                                  | 90       | 60        | 55             | 55        | mA   | Min             |

| H/V Sync sink current                          | 10 Ω to 5 V                                                                  | 50       | 30        | 27             | 25        | mA   | Min             |

| H/V Delay                                      | Delay from input to output                                                   | 6.5      |           |                |           | ns   | Тур             |

| H/V to buffer output skew                      |                                                                              | 5        |           |                |           | ns   | Тур             |

<sup>(2)</sup> Schmitt trigger threshold is defined by (VT+ - VT-)/2.

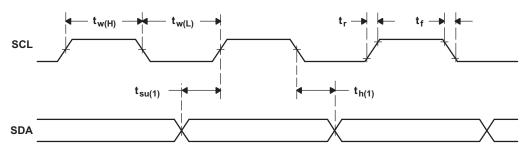

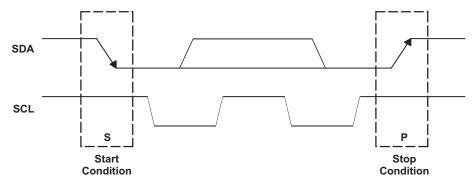

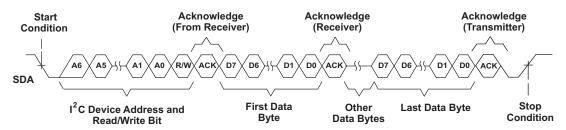

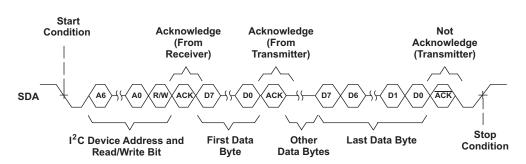

### TIMING REQUIREMENTS FOR I<sup>2</sup>C INTERFACE<sup>(1)(2)</sup>

At  $V_{DD} = 2.7 \text{ V to 5 V}$ .

|                    |                                                 | STANDARD | MODE | FAST N |     |      |

|--------------------|-------------------------------------------------|----------|------|--------|-----|------|

|                    | PARAMETER                                       | MIN      | MAX  | MIN    | MAX | UNIT |

| f <sub>SCL</sub>   | Clock frequency, SCL                            | 0        | 100  | 0      | 400 | kHz  |

| t <sub>w(H)</sub>  | Pulse duration, SCL high                        | 4        |      | 0.6    |     | μs   |

| t <sub>w(L)</sub>  | Pulse duration, SCL low                         | 4.7      |      | 1.3    |     | μs   |

| t <sub>r</sub>     | Rise time, SCL and SDA                          |          | 1000 |        | 300 | ns   |

| t <sub>f</sub>     | Fall time, SCL and SDA                          |          | 300  |        | 300 | ns   |

| t <sub>su(1)</sub> | Setup time, SDA to SCL                          | 250      |      | 100    |     | ns   |

| t <sub>h(1)</sub>  | Hold time, SCL to SDA                           | 0        |      | 0      |     | ns   |

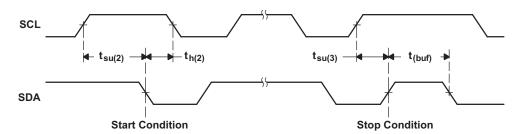

| t <sub>(buf)</sub> | Bus free time between stop and start conditions | 4.7      |      | 1.3    |     | μs   |

| t <sub>su(2)</sub> | Setup time, SCL to start condition              | 4.7      |      | 0.6    |     | μs   |

| t <sub>h(2)</sub>  | Hold time, start condition to SCL               | 4        |      | 0.6    |     | μs   |

| t <sub>su(3)</sub> | Setup time, SCL to stop condition               | 4        |      | 0.6    |     | μs   |

| C <sub>b</sub>     | Capacitive load for each bus line               |          | 400  |        | 400 | pF   |

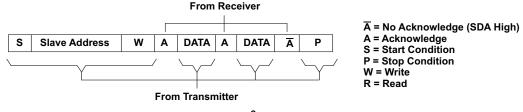

- The THS7347  $I^2C$  address = 01011(A1)(A0)( $R\overline{NV}$ ). See the *Applications Information* section for more information. The THS7347 was designed to comply with version 2.1 of the  $I^2C$  specification.

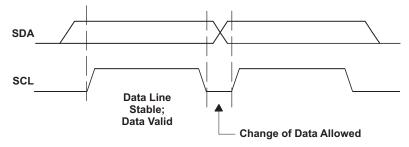

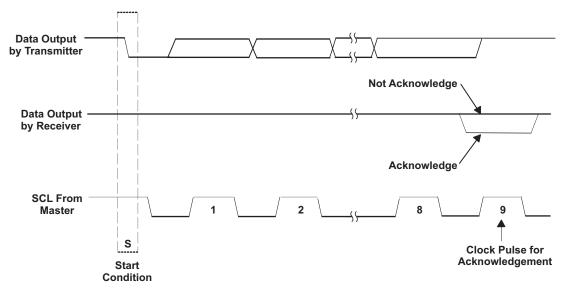

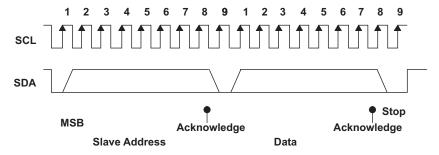

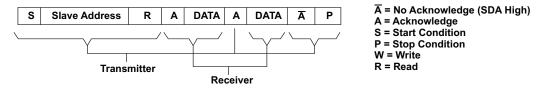

Figure 1. SCL and SDA Timing

Figure 2. Start and Stop Conditions

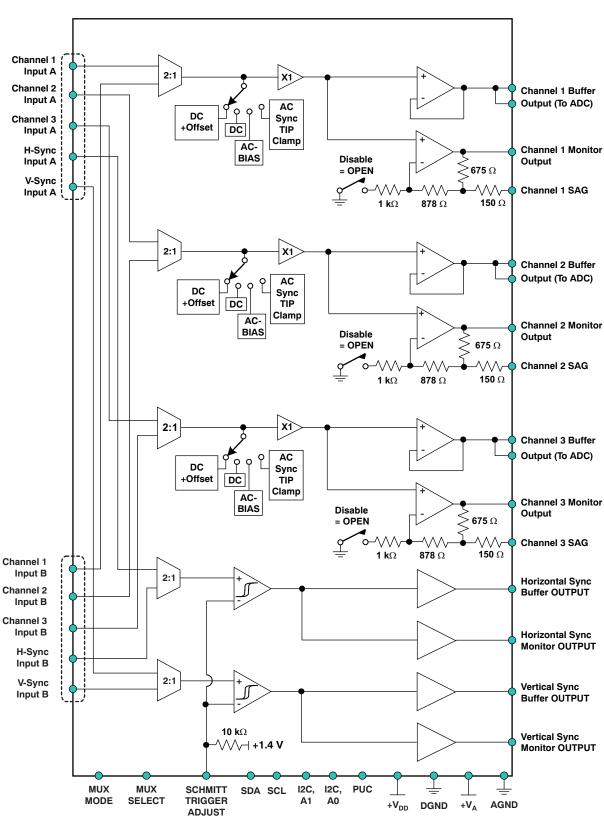

#### **FUNCTIONAL BLOCK DIAGRAM**

NOTE: The I<sup>2</sup>C address of the THS7347 is 01011(A1)(A0)( $R/\overline{W}$ ).

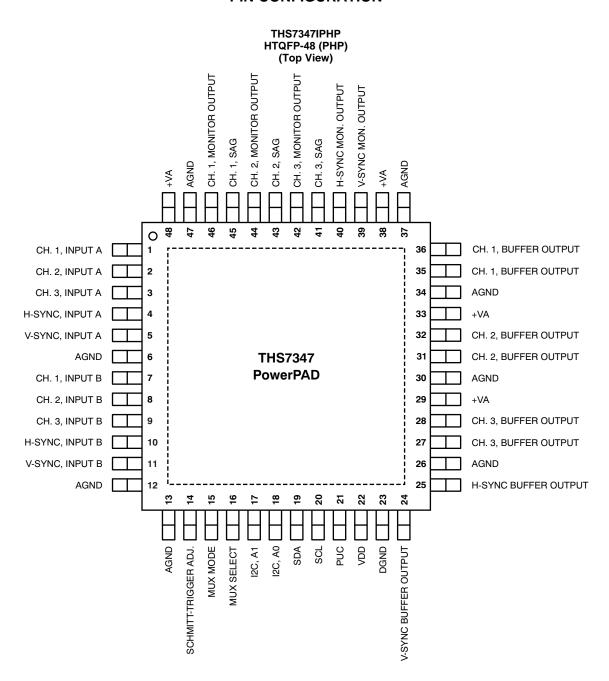

#### **PIN CONFIGURATION**

#### **TERMINAL FUNCTIONS**

|                 | TERMINAL FOROTIONS |     |                                |  |  |  |  |  |  |

|-----------------|--------------------|-----|--------------------------------|--|--|--|--|--|--|

| TERMINA         | TERMINAL           |     | DESCRIPTION                    |  |  |  |  |  |  |

| NAME            | NO.                | 1/0 | DESCRIPTION                    |  |  |  |  |  |  |

| CH. 1, INPUT A  | 1                  | I   | Video Input Channel 1, Input A |  |  |  |  |  |  |

| CH. 2, INPUT A  | 2                  | 1   | Video Input Channel 2, Input A |  |  |  |  |  |  |

| CH. 3, INPUT A  | 3                  | ı   | Video Input Channel 3, Input A |  |  |  |  |  |  |

| H-SYNC, INPUT A | 4                  | I   | Horizontal Sync, Input A       |  |  |  |  |  |  |

| V-SYNC, INPUT A | 5                  | I   | Vertical Sync, Input A         |  |  |  |  |  |  |

| CH. 1, INPUT B  | 7                  | ı   | Video Input Channel 1, Input B |  |  |  |  |  |  |

| CH. 2, INPUT B  | 8                  | ı   | Video Input Channel 2, Input B |  |  |  |  |  |  |

| CH. 3, INPUT B  | 9                  | I   | Video Input Channel 3, Input B |  |  |  |  |  |  |

# **TERMINAL FUNCTIONS (continued)**

| TERMINAL                 |                                  |     | TERMINAL FONCTIONS (Continued)                                                                                                                                                                                                                        |  |  |  |  |  |  |

|--------------------------|----------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| NAME                     | NO.                              | I/O | DESCRIPTION                                                                                                                                                                                                                                           |  |  |  |  |  |  |

| H-SYNC, INPUT B          | 10                               |     | Horizontal Sync, Input B                                                                                                                                                                                                                              |  |  |  |  |  |  |

| V-SYNC, INPUT B          | 11                               | 1   | Vertical Sync, Input B                                                                                                                                                                                                                                |  |  |  |  |  |  |

| I <sup>2</sup> C, A1     | 17                               | I   | I <sup>2</sup> C Slave Address Control Bit A1. Connect to V <sub>DD</sub> for a logic 1 preset value or GND for a logic 0 preset value.                                                                                                               |  |  |  |  |  |  |

| I <sup>2</sup> C, A0     | 18                               | I   | I <sup>2</sup> C Slave Address Control Bit A0. Connect to V <sub>DD</sub> for a logic 1 preset value or GND for a logic 0 preset value.                                                                                                               |  |  |  |  |  |  |

| SDA                      | 19                               | I/O | Serial data line of the $I^2C$ bus. Pull-up resistor should have a minimum value = 2 k $\Omega$ and a maximum value = 19 k $\Omega$ . Pull up to $V_{DD}$ .                                                                                           |  |  |  |  |  |  |

| SCL                      | 20                               | I   | $I^2C$ bus clock line. Pull-up resistor should have a minimum value = 2 kΩ and a maximum value = 19 -kΩ. Pull up to $V_{DD}$ .                                                                                                                        |  |  |  |  |  |  |

| PUC                      | 21                               | I   | Power-Up Condition. Connect to GND for all channels disabled upon power-up. Connect to V <sub>DD</sub> (logic high) to set buffer outputs to OFF and monitor outputs ON with ac-bias configuration on Channels 1 to 3 and both H-Sync/V-Sync enabled. |  |  |  |  |  |  |

| MUX MODE                 | 15                               | I   | Sets the MUX configuration control. Connect to logic low for MUX Select (pin 16) control of the MUX. Connect to logic high for I <sup>2</sup> C control of the MUX.                                                                                   |  |  |  |  |  |  |

| MUX SELECT               | 16                               | I   | Controls the MUX selection when MUX MODE (pin 15) is set to logic low. Connect to logic low for MUX selector set to Input A. Connect to logic high for MUX selector set to Input B.                                                                   |  |  |  |  |  |  |

| CH. 1, BUFFER OUTPUT     | 35, 36                           | 0   | Output Channel 1 from either CH. 1, INPUT A or CH. 1, INPUT B. Connect to ADC/Scalar/Decoder. Both pins should be connected together on the PCB.                                                                                                      |  |  |  |  |  |  |

| CH. 2, BUFFER OUTPUT     | 31, 32                           | 0   | Output Channel 2 from either CH. 2, INPUT A or CH. 2, INPUT B. Connect to ADC/Scalar/Decoder. Both pins should be connected together on the PCB.                                                                                                      |  |  |  |  |  |  |

| CH. 3, BUFFER OUTPUT     | 27, 28                           | 0   | Output Channel 3 from either CH. 3, INPUT A or CH. 3, INPUT B. Connect to ADC/Scalar/Decoder. Both pins should be connected together on the PCB.                                                                                                      |  |  |  |  |  |  |

| H-SYNC BUFFER<br>OUTPUT  | 25                               | 0   | Horizontal Sync Buffer Output. Connect to ADC/Scalar H-sync input.                                                                                                                                                                                    |  |  |  |  |  |  |

| V-SYNC BUFFER<br>OUTPUT  | 24                               | 0   | Vertical Sync Buffer Output. Connect to ADC/Scalar V-sync input.                                                                                                                                                                                      |  |  |  |  |  |  |

| CH. 1, SAG               | 45                               | 0   | Video Monitor Pass-Through Output Channel 1 SAG Correction pin. If SAG is not used, connect Directly to CH. 1, OUTPUT pin 46.                                                                                                                         |  |  |  |  |  |  |

| CH. 1, MONITOR<br>OUTPUT | 46                               | 0   | Video Monitor Pass-Through Output Channel 1 from either CH. 1, INPUT A or CH. 1, INPUT B.                                                                                                                                                             |  |  |  |  |  |  |

| CH. 2, SAG               | 43                               | 0   | Video Monitor Pass-Through Output Channel 2 SAG Correction pin. If SAG is not used, connect Directly to CH. 2, OUTPUT pin 44.                                                                                                                         |  |  |  |  |  |  |

| CH. 2, MONITOR<br>OUTPUT | 44                               | 0   | Video Monitor Pass-Through Output Channel 2 from either CH. 2, INPUT A or CH. 2, INPUT B.                                                                                                                                                             |  |  |  |  |  |  |

| CH. 3, SAG               | 41                               | 0   | Video Monitor Pass-Through Output Channel 3 SAG Correction pin. If SAG is not used, connect Directly to CH. 3, OUTPUT pin 42.                                                                                                                         |  |  |  |  |  |  |

| CH. 3, MONITOR<br>OUTPUT | 42                               | 0   | Video Monitor Pass-Through Output Channel 3 from either CH. 3, INPUT A or CH. 3, INPUT B.                                                                                                                                                             |  |  |  |  |  |  |

| H-SYNC MONITOR<br>OUTPUT | 40                               | 0   | Horizontal Sync Monitor Pass-Through Output.                                                                                                                                                                                                          |  |  |  |  |  |  |

| V-SYNC MONITOR<br>OUTPUT | 39                               | 0   | Vertical Sync Monitor Pass-Through Output.                                                                                                                                                                                                            |  |  |  |  |  |  |

| AGND                     | 6, 12, 13, 26,<br>30, 34, 37, 47 | I   | Ground Reference pin for analog signals. Internally, these pins connect to DGND, although it is recommended to have the AGND and DGND connected to the proper signals for best results.                                                               |  |  |  |  |  |  |

| +V <sub>A</sub>          | 29, 33, 38, 48                   | I   | Analog Positive Power Supply Input pins. Connect to 2.7 V to 5 V. Must be equal to or greater than VDD.                                                                                                                                               |  |  |  |  |  |  |

| $V_{DD}$                 | 22                               | I   | Digital Positive Supply pin for I <sup>2</sup> C circuitry and H-Sync/V-Sync outputs. Connect to 2.7 V to 5 V.                                                                                                                                        |  |  |  |  |  |  |

| DGND                     | 23                               | I   | Digital GND pin for HV circuitry and I <sup>2</sup> C circuitry.                                                                                                                                                                                      |  |  |  |  |  |  |

| Schmitt Trigger Adjust   | 14                               | I   | Defaults to 1.45 V (TTL compatible). Connect to external voltage reference to adjust H-Sync/V-Sync input thresholds from 0.9 V to 2 V range.                                                                                                          |  |  |  |  |  |  |

#### **APPLICATIONS INFORMATION**

The THS7347 is targeted for RGB+HV video buffer applications. Although it can be used for numerous other applications, the needs and requirements of the video signal were the most important design parameters of the THS7347. Built on the revolutionary complementary silicon-germanium (SiGe) BiCom3 process, the THS7347 incorporates many features not typically found in integrated video parts while consuming very low power. Each channel configuration is completely independent of the other channels. This architecture allows for any configuration for each channel to be dictated by the end user, rather than the part dictating what the configuration must be—resulting in a highly flexible system.

#### The THS7347 has the following features:

- I<sup>2</sup>C interface for easy interfacing to the system.

- Single-supply 2.7-V to 5-V operation with low quiescent current of 80 mA at 3.3 V.

- 2:1 input mux.

- Input configuration accepts dc, dc + shift, ac bias, or ac sync-tip clamp selection.

- 500-MHz unity-gain buffer amplifier to drive ADC/Scalar/Decoder.

- Monitor Pass-Through path has an internal fixed gain of 2 V/V (+6 dB) amplifier that can drive two video lines per channel with dc coupling, traditional ac coupling, or SAG-corrected ac coupling.

- While disabled, the Monitor Pass-Through path has a very high output impedance (> 500 kΩ || 8 pF)

- Power-Up Control (PUC) allows the THS7347 to be fully disabled or have the Monitor Pass-Through function (with ac-bias mode on all channels) enabled upon initial device power-up.

- Mux is controlled by either I<sup>2</sup>C or a general-purpose input/output (GPIO) pin, based on the MUX Mode pin logic.

- H-Sync and V-Sync paths have an externally-adjustable Schmitt trigger threshold

- Disable mode reduces quiescent current to as low as 0.1-µA.

#### **OPERATING VOLTAGE**

The THS7347 is designed to operate from 2.7 V to 5 V over a -40°C to +85°C temperature range. The impact on performance over the entire temperature range is negligible because of the implementation of thin film resistors and high-quality, low temperature coefficient capacitors.

A 0.1- $\mu$ F to 0.01- $\mu$ F capacitor should be placed as close as possible to the power-supply pins. Failure to do so may result in the THS7347 outputs ringing or oscillating. Additionally, a large capacitor, such as 100  $\mu$ F, should be placed on the power-supply line to minimize issues with 50-Hz/60-Hz line frequencies.

#### **INPUT VOLTAGE**

The THS7347 input range allows for an input signal range from ground to approximately ( $V_S+-1.6$  V). However, because of the internal fixed gain of 2 V/V (+6 dB), the output is generally the limiting factor for the allowable linear input range. For example, with a 5-V supply, the linear input range is from GND to 3.4 V. As a result of the gain, the linear output range limits the allowable linear input range from GND to 2.5 V at most.

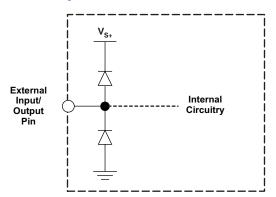

#### INPUT OVERVOLTAGE PROTECTION

The THS7347 is built using a very high-speed complementary bipolar and CMOS process. The internal junction breakdown voltages are relatively low for these very small geometry devices. These breakdowns are reflected in the Absolute Maximum Ratings table. All input and output device pins are protected with internal ESD protection diodes to the power supplies, as shown in Figure 3.

Figure 3. Internal ESD Protection

These diodes provide moderate protection to input overdrive voltages above and below the supplies. The protection diodes can typically support 30 mA of continuous current when overdriven.

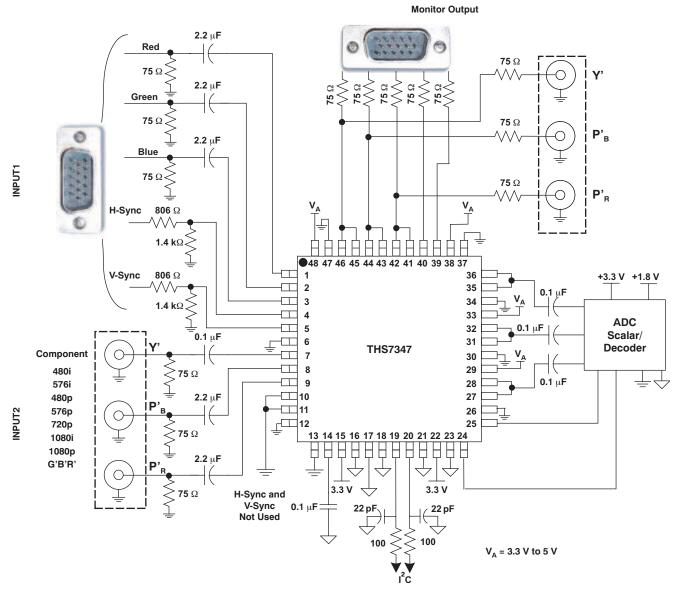

#### TYPICAL CONFIGURATION

A typical application circuit usng the THS7347 as an ac-coupled input video buffer is shown in Figure 4. It shows the THS7347 driving a video ADC (such as the TVP7000) with 0-dB gain and also driving an output line with 6-dB gain. The Horizontal and Vertical Sync signals are also driven to the ADC and the Monitor Output separately. Although the computer resolution R'G'B'HV signals are shown, these channels can easily be the high-definition video (HD), enhanced-definition (ED), or standard-definition (SD) Y'P'<sub>B</sub>P'<sub>R</sub> (sometimes labeled Y'U'V' or incorrectly labeled Y'C'<sub>B</sub>C'<sub>R</sub>) channels. These channels could also be S-Video Y'/C' channels and the composite video baseband signal (CVBS). Note that the R'G'B' channels could be professional/broadcast G'B'R' signals or other R'G'B' variations based on the placement of the sync signals that are commonly called R'G'sB' (sync on Green) or R'sG'sB's (sync on all signals).

The second set of inputs (B-Channels) shown are connected to another set of inputs. Again, these inputs can be either HD, ED, SD, or R'G'B'/G'B'R' video signals. The THS7347 flexibility allows for virtually any input signal to be driven into the THS7347 regardless of the other set of inputs. Simple control of the I<sup>2</sup>C configures the THS7347 for any conceivable combination. For example, the THS7347 can be configured to have Channel 1 Input connected to input A while Channel 2 and Channel 3 are connected to input B. See the multiple application notes sections explaining the I<sup>2</sup>C interface later in this document for details on configuring these options.

Note that the Y' term is used for the luma channels throughout this document, rather than the more common luminance (Y) term. The reason for this usage is to account for the true definition of luminance as stipulated by the CIE (International Commission on Illumination). Video departs from true luminance because a nonlinear term, gamma, is added to the true RGB signals to form R'G'B' signals. These R'G'B' signals are then utilized to mathematically create luma (Y'). Therefore, true luminance (Y) is not maintained, and thus the difference in terminology arises.

This rationale is also utilized for the chroma (C') term. Chroma is derived from the nonlinear R'G'B' terms and therefore it is also nonlinear. True chominance (C) is derived from linear RGB, and thus the difference between chroma (C') and chrominance (C) exists. The color difference signals ( $P'_B/P'_R/U'/V'$ ) are also referenced this way to denote the nonlinear (gamma-corrected) signals.

R'G'B' (commonly labeled RGB) is also called G'B'R' (again commonly labeled as GBR) in professional video systems. The SMPTE component standard stipulates that the luma information is placed on the first channel, the blue color difference is placed on the second channel, and the red color difference signal is placed on the third channel. This approach is consistent with the Y'P'<sub>B</sub>P'<sub>R</sub> nomenclature. Because the luma channel (Y') carries the sync information and the green channel (G') also carries the sync information, it makes logical sense that G' be

placed first in the system. Since the blue color difference channel  $(P'_B)$  is next and the red color difference channel  $(P'_R)$  is last, then it also makes logical sense to place the B' signal on the second channel and the R' signal on the third channel, respectively. Thus, hardware compatibility is better achieved when using G'B'R' rather than R'G'B'. Note that for many G'B'R' systems, sync is embedded on all three channels; this configuration may not always be the case for all systems.

- (1) Inputs and/or outputs can be ac- or dc-coupled if desired.

- (2) H-Sync and V-Sync input resistance as shown above =  $2.2 \text{ k}\Omega$ , but may be changed to any desired resistance.

- (3) If the Monitor or Buffer PCB trace is > 25 mm, it is recommended to place at least a  $10-\Omega$  resistor in series with each signal to reduce PCB parasitic issues

Figure 4. Typical R'G'B'HV and Y'P'BP'R AC-Coupled Inputs and DC-Coupled Output Configuration

#### I<sup>2</sup>C INTERFACE NOTES