www.ti.com

# Stand-Alone Multi-Cell Lithium-Ion/Polymer Precision Protectors

Check for Samples: bq77908

# **FEATURES**

- 4-, 5-, 6-, 7-, or 8 Series Cell Protection

- Individual Cell-Voltage Monitoring

- Low-Side NMOS FET Drive for Charge and Discharge Control

- Compatible With 1-mΩ Current-Sense Resistor

- Supply-Voltage Range From 5.6 V to 40 V

- Integrated 3.3-V Micro-Power LDO Regulator

- Low Supply Current

- Normal Mode: 50 µA, Typical

- Shutdown Mode, LDO OFF: 5 μA, Typical

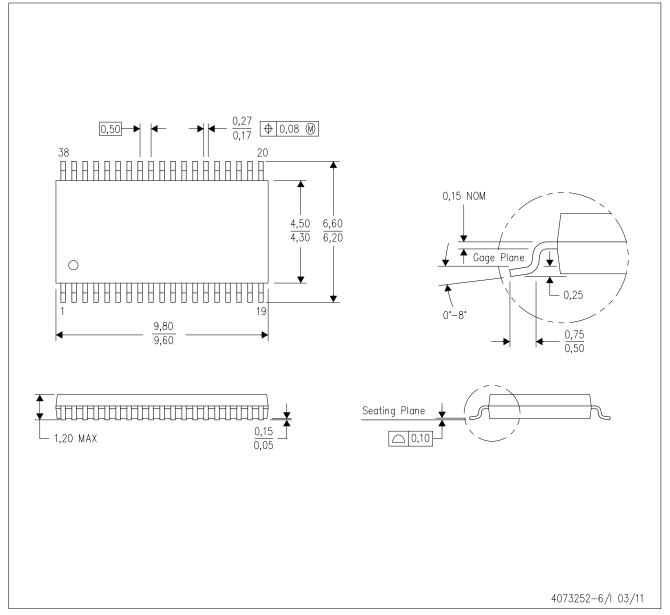

- 38-Pin TSSOP Package

- Internal 50-mA Automatic Cell Balancing

#### **APPLICATIONS**

- Cordless Power Tools

- · Cordless Lawn Equipment

- Electric Bikes

- UPS

- Medical Equipment

- Light Electric Vehicles (LEV)

# **DESCRIPTION**

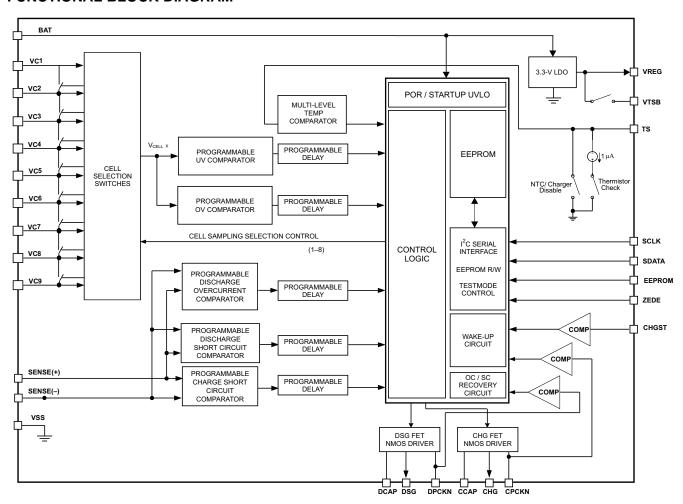

The bq77908 precision protector is a complete stand-alone, self-contained battery-protection and cell-balancing device intended for Li-ion/polymer battery packs.

The bq77908 monitors 4 to 8 series individual cell voltages and provides fast-acting outputs which may be used to drive N-channel MOSFETs to interrupt the power path. Activation delays and recovery methods for each safety condition are fully programmable in non-volatile memory.

Automatic cell balancing is provided using internal 50-mA cell circuits. A robust balancing algorithm ensures optimum performance by maintaining all cell voltages in balance. Balancing may be configured to operate at all times, only during charge, or can be disabled completely.

Additional advanced safety features of the bq77908 include the ability to control split power-path MOSFETs, an open-cell sense-line detection mechanism, and the ability to detect an open or shorted external temperature sensor.

# **Programmable Protection Functions**

- Wide range of programmable detection thresholds and delay times

- Configurable for multiple cell types and application requirements:

- Cell overvoltage

- Cell undervoltage

- Pack discharge overcurrent

- Pack discharge short circuit

- Pack charge short-circuit current

- Variable gain (×1 or ×5) current-sense circuit

- Compatible with a wide range of current-sense resistors (1 mΩ to 5 mΩ typical) sized for application requirements

#### **Fixed Hardware Protection Functions**

- Preset overtemperature protections

- Open-cell detection

- Open and shorted thermistor detection

- Brownout protection quickly shuts off FETs under low-battery conditions to avoid FET overheating

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

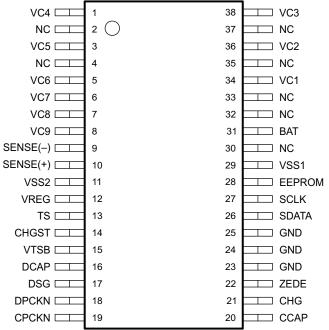

# **PIN DETAILS**

# PIN FUNCTIONS (38-Pin Package)

|          | PIN                         |                                                                                                                                                                                                               |

|----------|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME     | NO.                         | DESCRIPTION                                                                                                                                                                                                   |

| BAT      | 31                          | Power supply voltage, tied to highest cell(+)                                                                                                                                                                 |

| CCAP     | 20                          | Energy storage capacitor for charge FET drive                                                                                                                                                                 |

| CHG      | 21                          | Charge FET (n-channel) gate drive                                                                                                                                                                             |

| CHGST    | 14                          | Charger-status input, used to detect charger connection/wakeup                                                                                                                                                |

| CPCKN    | 19                          | Pack – charger negative terminal (charger return)                                                                                                                                                             |

| DCAP     | 16                          | Energy storage capacitor for discharge FET drive                                                                                                                                                              |

| DPCKN    | 18                          | Pack – discharge negative terminal (load return)                                                                                                                                                              |

| DSG      | 17                          | Discharge FET (n-channel) gate drive                                                                                                                                                                          |

| EEPROM   | 28                          | EEPROM programming voltage input. Connect to VSS for normal operation.                                                                                                                                        |

| GND      | 23, 24, 25                  | Logic ground (not for power return or analog reference). Tie to VSS.                                                                                                                                          |

| NC       | 2, 4, 30, 32,<br>33, 35, 37 | No connect (DO NOT CONNECT) externally. Failure to leave NC pins open can cause faulty operation.                                                                                                             |

| SCLK     | 27                          | Serial-communication clock input used for EEPROM programming                                                                                                                                                  |

| SDATA    | 26                          | Serial-communication data input/output used for EEPROM programming (open-drain)                                                                                                                               |

| SENSE(+) | 10                          | Current-sense input                                                                                                                                                                                           |

| SENSE(-) | 9                           | Current-sense input                                                                                                                                                                                           |

| TS       | 13                          | Temperature sensing input                                                                                                                                                                                     |

| VC1      | 34                          | Sense-voltage input terminal for most-positive cell                                                                                                                                                           |

| VC2      | 36                          | Sense-voltage input terminal for second-most-positive cell                                                                                                                                                    |

| VC3      | 38                          | Sense-voltage input terminal for third-most-positive cell                                                                                                                                                     |

| VC4      | 1                           | Sense-voltage input terminal for fourth-most-positive cell                                                                                                                                                    |

| VC5      | 3                           | Sense-voltage input terminal for fifth-most-positive cell                                                                                                                                                     |

| VC6      | 5                           | Sense-voltage input terminal for sixth-most-positive cell                                                                                                                                                     |

| VC7      | 6                           | Sense-voltage input terminal for seventh-most-positive cell                                                                                                                                                   |

| VC8      | 7                           | Sense-voltage input terminal for eighthmost-positive (most-negative) cell                                                                                                                                     |

| VC9      | 8                           | Most-negative cell(-) terminal (BAT-)                                                                                                                                                                         |

| VREG     | 12                          | Integrated 3.3-V regulator output                                                                                                                                                                             |

| VSS1     | 29                          | Analog ground (substrate reference)                                                                                                                                                                           |

| VSS2     | 11                          | Analog ground (substrate reference)                                                                                                                                                                           |

| VTSB     | 15                          | Thermistor bias supply (sourced from VREG)                                                                                                                                                                    |

| ZEDE     | 22                          | Zero Delay test mode pin. Enables serial communications interface and minimizes protection delay times when connected to logic high. Connect to VSS for normal operation. A strong connection is recommended. |

# PIN DIAGRAM - bq77908 - 38-Pin SSOP DBT PACKAGE

# DBT PACKAGE (TOP VIEW)

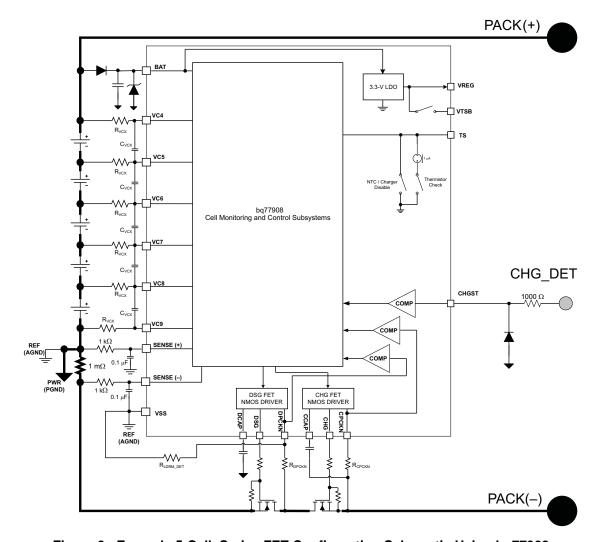

#### **FUNCTIONAL BLOCK DIAGRAM**

## **ORDERING INFORMATION**

| PART NUMBER | PACKAGE TYPE | PACKAGING       |  |

|-------------|--------------|-----------------|--|

| bq77908DBT  | TSSOP        | 50-piece tube   |  |

| bq77908DBTR | TSSOP        | 2000-piece reel |  |

#### **ELECTRICAL SPECIFICATIONS**

# ABSOLUTE MAXIMUM RATINGS(1)

over operating free-air temperature range (unless otherwise noted)

|                                             |                                                       | VALUE / UNIT                                               |

|---------------------------------------------|-------------------------------------------------------|------------------------------------------------------------|

| DC supply-voltage range, V <sub>MAX</sub>   | BAT                                                   | -0.3 to (5 × N) V, N = number of cells implemented in pack |

|                                             | DPCKN                                                 | −0.3 V to 50 V                                             |

|                                             | CPCKN                                                 | (BAT – 50) V to (BAT + 0.9) V                              |

|                                             | Cell-to-cell differential, VCx to VC(x+1), x = 1 to 8 | –0.3 V to 9 V                                              |

|                                             | SENSE(+)                                              | –3 V to 3 V                                                |

| lament violta an incident                   | SENSE(-)                                              | −0.3 V to 50 V                                             |

| nput voltage range, V <sub>IN</sub>         | SCLK, SDATA, ZEDE (2)                                 | –0.3 V to 7 V                                              |

|                                             | TS, CHGST <sup>(3)(4)</sup>                           | −0.3 V to BAT V                                            |

|                                             | EEPROM                                                | −0.3 V to 15 V                                             |

|                                             | Cell input VCx, x = 1-8                               | (9 – x) × 5 V                                              |

|                                             | Cell input VC9                                        | –3 V to 3 V                                                |

|                                             | CHG referenced to CPCKN                               | – 0.3 V to 15 V                                            |

| Output voltage range, V <sub>O</sub>        | DSG referenced to VSS                                 | −0.3 V to 15 V                                             |

|                                             | VTSB                                                  | –0.3 V to 5 V                                              |

| Current for cell balancing, I <sub>CB</sub> |                                                       | 70 mA                                                      |

| Regulator current, I <sub>REG</sub> 45      |                                                       | 45 mA                                                      |

| Storage temperature range, T <sub>stg</sub> |                                                       | −65°C to 150°C                                             |

- (1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only. Functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

- (2) All signal / logic pins which may be connected to the pack external terminals are internally clamped to a maximum voltage of 5 V. If the external source driving these signals exceeds the clamp threshold, series resistance from the pin to the pack terminal is required to avoid overstress on the clamping circuit.

- (3) CHGST and TS pins are tolerant of applied overvoltage as noted to allow for charger single-fault tolerance. Normal operating range is typically 3.3 V or less at this pin; thus, high voltage seen here may correspond to a fault condition.

- (4) Although no damage results when CHGST = VSS 0.3 V, for proper operation at power up, CHGST must be ≥ VSS 0.25 V.

#### THERMAL INFORMATION

|                  |                                                                    | bq77908 |      |

|------------------|--------------------------------------------------------------------|---------|------|

|                  | THERMAL METRIC <sup>(1)</sup>                                      | DBT     | UNIT |

|                  |                                                                    | 38 PINS |      |

| $\theta_{JA}$    | Junction-to-ambient thermal resistance, non-LDO <sup>(2)</sup>     | 71.7    | °C/W |

| $\theta_{JA2}$   | Junction-to-ambient thermal resistance, LDO (2) (3)                | 115.8   | °C/W |

| $\theta_{JCtop}$ | Junction-to-case (top) thermal resistance <sup>(4)</sup>           | 18.5    | °C/W |

| $\theta_{JB}$    | Junction-to-board thermal resistance <sup>(5)</sup>                | 33.9    | °C/W |

| $\Psi_{JT}$      | Junction-to-top characterization parameter, non-LDO <sup>(6)</sup> | 1       | °C/W |

| <b>Ψ</b> ЈТ2     | Junction-to-top characterization parameter, LDO <sup>(6)</sup> (3) | 38.9    | °C/W |

- (1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

- (2) The junction-to-ambient thermal resistance under natural convection is obtained in a simulation on a JEDEC-standard, high-K board, as specified in JESD51-7, in an environment described in JESD51-2a.

- (3) These metrics should be used only for calculating junction temperature due to power dissipation resulting from the I<sub>OUT</sub> load on VREG. Junction temperature calculations for all other sources of power dissipation should use the standard values θ<sub>JA</sub> and ψ<sub>JT</sub>.

- (4) The junction-to-case (top) thermal resistance is obtained by simulating a cold plate test on the package top. No specific JEDEC-standard test exists, but a close description can be found in the ANSI SEMI standard G30-88.

- (5) The junction-to-board thermal resistance is obtained by simulating in an environment with a ring cold plate fixture to control the PCB temperature, as described in JESD51-8.

- (6) The junction-to-top characterization parameter,  $\psi_{JT}$ , estimates the junction temperature of a device in a real system and is extracted from the simulation data for obtaining  $\theta_{JA}$ , using a procedure described in JESD51-2a (sections 6 and 7).

Copyright © 2011, Texas Instruments Incorporated

# THERMAL INFORMATION (continued)

|                  |                                                             | bq77908 |      |

|------------------|-------------------------------------------------------------|---------|------|

|                  | THERMAL METRIC <sup>(1)</sup>                               | DBT     | UNIT |

|                  |                                                             | 38 PINS |      |

| ΨЈВ              | Junction-to-board characterization parameter <sup>(7)</sup> | 33.2    | °C/W |

| $\theta_{JCbot}$ | Junction-to-case (bottom) thermal resistance (8)            | N/A     | °C/W |

<sup>(7)</sup> The junction-to-board characterization parameter,  $\psi_{JB}$ , estimates the junction temperature of a device in a real system and is extracted from the simulation data for obtaining  $\theta_{JA}$ , using a procedure described in JESD51-2a (sections 6 and 7).

# RECOMMENDED OPERATING CONDITIONS

over operating free-air temperature range (unless otherwise noted)

|                                            |                                                                 |                                                              | MIN                    | TYP | MAX                  | UNIT  |

|--------------------------------------------|-----------------------------------------------------------------|--------------------------------------------------------------|------------------------|-----|----------------------|-------|

| Supply voltage                             |                                                                 | BAT <sup>(1)</sup>                                           | 5.6 <sup>(2)</sup>     |     | 35 <sup>(3)</sup>    | V     |

|                                            |                                                                 | Cell differential, VCx to VC(x + 1), (x = 1 to 8)            | 1.4                    |     | 4.375                | V     |

| $V_{I}$                                    | Input voltage range                                             | Cell input VCx, $x = 1 - 8$                                  |                        |     | (9 – x) ×<br>4.375 V |       |

|                                            |                                                                 | Cell input VC9                                               | -1                     |     | 1                    |       |

| $V_{IH}$                                   | Logic-level input, high                                         | SCLK, SDATA, EEPROM, ZEDE                                    | 0.8 × V <sub>REG</sub> |     |                      | V     |

| $V_{IL}$                                   | Logic-level input, low                                          | SCLK, SDATA, EEFROM, ZEDE                                    |                        |     | $0.2 \times V_{REG}$ | V     |

| VSENSE(+)                                  | Voltage applied at SENSE(±)                                     |                                                              | VSS - 1                |     | VSS + 1              | V     |

| VSENSE(-)                                  | pins                                                            |                                                              | -0.2                   |     | BAT                  | V     |

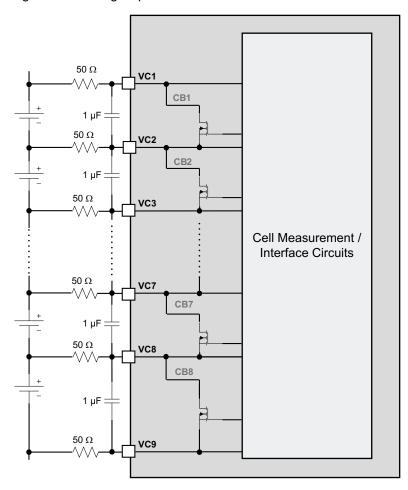

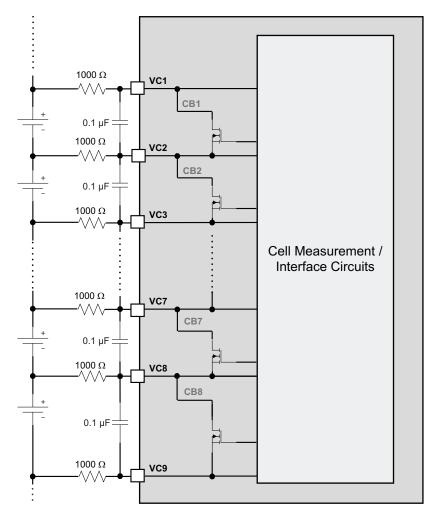

| R <sub>VCX</sub>                           | Recommended VCx nominal input resistance                        |                                                              | 50                     | 100 | 1000                 | Ω     |

| I <sub>REG</sub>                           | Regulator current                                               |                                                              |                        |     | 10                   | mA    |

| $I_{CB}$                                   | Cell balancing current                                          |                                                              |                        |     | 50                   | mA    |

| C <sub>VCX</sub>                           | Recommended VCx nominal input filter capacitance                |                                                              |                        |     | 1                    | μF    |

| R <sub>CPCKN</sub> ,<br>R <sub>DPCKN</sub> | Recommended isolation-pin input resistance                      |                                                              |                        | 100 |                      | Ω     |

| R <sub>LDRM_DET</sub>                      | Pulldown for load-removal detection                             |                                                              |                        | 50  |                      | kΩ    |

| C <sub>VREG</sub>                          | External 3.3-V REG capacitor                                    |                                                              | 1                      |     |                      | μF    |

|                                            | EEPROM number of writes                                         |                                                              |                        |     | 3                    | times |

| T <sub>OPR</sub>                           | Operating temperature                                           | Meeting all specification limits                             | -25                    |     | 85                   | °C    |

| T <sub>FUNC</sub>                          | Functional temperature                                          | Operational but may be out of spec limits, no damage to part | -40                    |     | 100                  | °C    |

| C <sub>CCAP</sub> ,<br>C <sub>DCAP</sub>   | External capacitance on CCAP and DCAP pins (4)                  |                                                              | 0.1                    | 1   |                      | μF    |

| R <sub>P</sub>                             | Serial communication interface pullup resistance <sup>(5)</sup> | SCLK, SDATA                                                  |                        | 2.2 |                      | kΩ    |

<sup>1)</sup> The voltage rate of change at the BAT pin should be limited to a maximum of 1 V per µs in order to prevent unwanted device shutdown.

Submit Documentation Feedback

Copyright © 2011, Texas Instruments Incorporated

<sup>(8)</sup> The junction-to-case (bottom) thermal resistance is obtained by simulating a cold plate test on the exposed (power) pad. No specific JEDEC standard test exists, but a close description can be found in the ANSI SEMI standard G30-88.

<sup>(2)</sup> Minimum voltage assumes 4-cell connection at 1.4 V/cell.

<sup>(3)</sup> Maximum voltage assumes 8-cell connection at 4.375 V/cell.

<sup>(4)</sup> C<sub>CCAP</sub> and C<sub>DCAP</sub> act as charge reservoirs for the CHG and DSG pins when driving large protection FETs. Minimum value is required for stability, independent of the CHG and DSG loading.

<sup>(5)</sup> Pullups for configuration of device during pack manufacturing. SCLK and SDATA should be pulled high or low in application.

#### **ELECTRICAL CHARACTERISTICS**

Vcell(n) = 1.4 to 4.375 for all cells,  $T_A = -25$ °C to 85°C, BAT = 5.6 to 35 V; Typical values stated where  $T_A = 25$ °C and BAT = 28.8 V (unless otherwise noted)

| PARAMETER                              |                                                                        | TEST CONDITIONS                                                        |                                                | MIN                   | TYP | MAX  | UNIT |

|----------------------------------------|------------------------------------------------------------------------|------------------------------------------------------------------------|------------------------------------------------|-----------------------|-----|------|------|

| SUPPLY CURRENT                         |                                                                        | -                                                                      |                                                |                       |     |      |      |

| I <sub>CC</sub>                        | Normal-mode average supply<br>current                                  | CHG, DSG = on (no dc los<br>I <sub>REG</sub> = 0 mA, BAT = 28.8 \      |                                                |                       | 50  | 75   | μΑ   |

| I <sub>SHUTDOWN 2</sub> <sup>(1)</sup> | Shutdown mode, LDO off                                                 | Vcell < Vuv, VREG = off (I                                             | EEPROM set), CPCKN = 0.3 V                     |                       | 5   | 17   |      |

| SHUTDOWN_2`'                           | Shuldown mode, LDO on                                                  | Vcell < Vuv, VREG = off (I                                             | EEPROM set), CPCKN = 0.5 V                     |                       | 20  | 60   | μA   |

| INTERNAL POWER C                       | ONTROL (STARTUP, SHUTDOWN, GATE I                                      | ORIVE UNDERVOLTAGE)                                                    |                                                |                       |     |      |      |

| V <sub>STARTUP</sub>                   | Minimum voltage for initial power up <sup>(2)</sup>                    | Measured at BAT pin                                                    |                                                |                       |     | 7    | V    |

| V <sub>POR</sub> <sup>(3)</sup>        | LDO POR voltage – voltage on LDO that initiates a POR                  | I <sub>LDO</sub> = 2 mA                                                |                                                | 2.7                   |     | 3.2  | V    |

| $V_{GATE\_UV}$                         | FET gate shutdown threshold (voltage falling)                          | Measured at CCAP / DCA                                                 | P pins                                         | 4.5                   | 4.9 | 5.3  | V    |

| $V_{\text{GATE\_UV\_H}}$               | FET gate shutdown hysteresis voltage                                   | Measured at CCAP / DCA                                                 | P pins                                         | 0.45                  |     | 0.7  | V    |

| FET DRIVE(4)                           |                                                                        |                                                                        |                                                |                       |     |      |      |

|                                        | Gate drive voltage at DSG and CHG pins for FET ON (enabled) conditions | BAT voltage = 35 V (gate-drive circuit in regulation mode), no dc load |                                                | 11                    | 12  | 14   | V    |

| $V_{(FETON)}$                          |                                                                        | BAT voltage = 10 V (gate-drive circuit in dropout mode), no dc load    |                                                | 9                     |     |      |      |

|                                        | Continuono                                                             | BAT voltage = 6.4 V (gate-drive circuit in dropout mode), no dc load   |                                                | >V <sub>GATE_UV</sub> |     |      |      |

|                                        | Gate drive voltage at DSG and                                          | $V_{O(FETOFFDSG)} = V_{(DSG)} - V_{GND}$                               |                                                |                       |     | 0.2  |      |

| $V_{(FETOFF)}$                         | CHG pins for FET OFF<br>(disabled) conditions                          | $V_{O(FETOFFCHG)} = V_{(VHG)} - V_{pack-}$                             |                                                |                       | 0.2 | V    |      |

|                                        |                                                                        |                                                                        | V <sub>DSG</sub> : 10% to 90%                  |                       | 90  | 140  | )    |

|                                        | Rise time, measured at IC pin $C_L = 50 \text{ nF}$ ,                  | $C_L = 50 \text{ nF, BAT} = 35 \text{ V}$                              | V <sub>CHG</sub> : 10% to 90%                  |                       | 90  | 140  |      |

| t <sub>r</sub>                         | (CHG or DSG)                                                           | C <sub>1</sub> = 50 nF, BAT = 6.4 V                                    | V <sub>DSG</sub> : 10% to 90%                  |                       | 90  | 140  | μs   |

|                                        |                                                                        | C <sub>L</sub> = 50 NF, BAT = 6.4 V                                    | V <sub>CHG</sub> : 10% to 90%                  |                       | 90  | 140  |      |

|                                        |                                                                        | C <sub>1</sub> = 50 nF, BAT = 35 V                                     | V <sub>DSG</sub> : 90% to 10%                  |                       | 10  | 20   |      |

| +                                      | Fall time, measured at IC pin                                          | C <sub>L</sub> = 50 HF, BAT = 55 V                                     | V <sub>CHG</sub> : 90% to 10%                  |                       | 20  | 40   | ue   |

| t <sub>f</sub>                         | (CHG or DSG)                                                           | C <sub>1</sub> = 50 nF, BAT = 6.4 V                                    | V <sub>DSG</sub> : 90% to 10%                  |                       | 50  | 100  | μs   |

|                                        |                                                                        | OL - 30 HF, DAT = 0.4 V                                                | V <sub>CHG</sub> : 90% to 10%                  |                       | 50  | 100  |      |

| VREG, INTEGRATED                       | 3.3-V LDO                                                              |                                                                        |                                                |                       |     |      |      |

|                                        | Output-voltage regulation under                                        | I <sub>OUT</sub> = 10 mA (maximum d                                    | c load) <sup>(5)</sup>                         | 3.1                   | 3.3 | 3.55 | V    |

| $V_{REG}$                              | all line, load, temperature conditions                                 | I <sub>OUT</sub> = 0.2 mA                                              |                                                | 3.1                   | 3.3 | 3.55 | V    |

| I <sub>sc</sub>                        | Short-circuit current limit                                            | VREG = 0 V, forced extern                                              | nal short (thermally protected) <sup>(6)</sup> | 20                    |     | 45   | mA   |

- (1) For predictable shutdown current, the voltage at CPCKN with respect to VSS must be controlled. In the parallel FET case, CPCKN is clamped through the body diode of the charge FET. In the series FET case, external circuitry is required to keep CPCKN from floating. Contact TI for recommended application circuits.

- (2) At this voltage, the LDO has sufficient voltage to maintain regulation. The POR then enables the charger-detect logic. Logic is held in reset until inserted into charger and LDO has reached V<sub>POR</sub>. The part still operates below 7 V to the spec limit of 5.6 V.

- (3) V<sub>POR</sub> and V<sub>REG</sub> are derived from the same internal reference, so that the MAX value of VPOR and the MIN value of VREG do not occur at the same time.

- (4) FET drive is disabled if voltage at CCAP or DCAP pins < V<sub>GATE\_UV</sub>. Turnoff due to gate-drive undervoltage condition meets the same timing requirements as logic-initiated gate turnoff.

- (5) ELECTRICAL CHARACTERISTICS assume that I<sub>OUT</sub> = 0 so that the internal junction temperature (T<sub>J</sub>) is effectively equal to the ambient temperature (T<sub>A</sub>). For larger non-zero values of I<sub>OUT</sub>, T<sub>J</sub> can be significantly higher than T<sub>A</sub>. In these cases, T<sub>J</sub> should be substituted for T<sub>A</sub> in the test and operating conditions. T<sub>J</sub> can be calculated from the device power dissipation as described under THERMAL CHARACTERISTICS. The device power dissipation due to I<sub>OUT</sub> is (VBAT VREG) × I<sub>OUT</sub>.

- (6) Regulator shuts down prior to current-limit maximum specification if junction temperature exceeds safe range.

# **ELECTRICAL CHARACTERISTICS (continued)**

Vcell(n) = 1.4 to 4.375 for all cells,  $T_A = -25$ °C to 85°C, BAT = 5.6 to 35 V; Typical values stated where  $T_A = 25$ °C and BAT = 28.8 V (unless otherwise noted)

|                                        | PARAMETER                                                                                  | TEST                                                                         | CONDITIONS                                         | MIN   | TYP   | MAX | UNIT  |

|----------------------------------------|--------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|----------------------------------------------------|-------|-------|-----|-------|

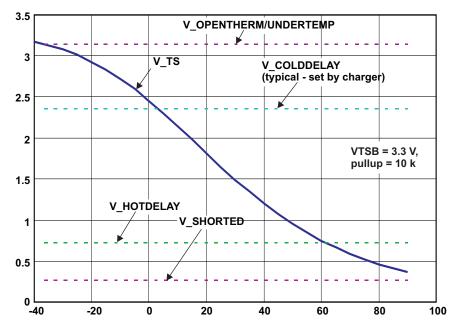

| TS TEMPERATURE SENS                    | SING                                                                                       |                                                                              |                                                    |       | -     |     | -     |

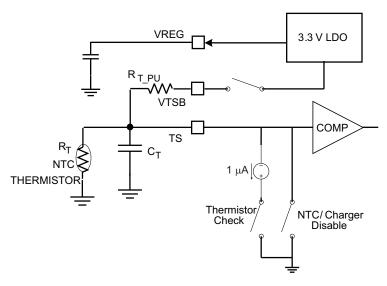

|                                        | VTSB pin pullup resistance                                                                 | I <sub>OUT</sub> = -1 mA at VTSB pin                                         | $r_{DS(on)} = (V_{REG} - V_{VTSB}) / 1 \text{ mA}$ |       | 50    | 150 |       |

| r <sub>DS(on)</sub>                    | TS pin fault-signal pulldown resistance                                                    | OV_TS_CTRL = 1, Vcell :                                                      | > Vov                                              |       | 50    | 150 | Ω     |

| I <sub>TS_PD</sub>                     | TS pin thermistor check pulldown current                                                   | TS = 3.3 V (externally driv                                                  | ven)                                               | 1     | 2     | 4   | μΑ    |

| t <sub>THERM_CHECK</sub>               | Thermistor fault sampling interval                                                         |                                                                              |                                                    |       | 4     |     | s     |

| V <sub>EXT_BIAS_DET</sub>              | Thermistor external-bias supply-detection threshold                                        | Internal VTSB supply off                                                     |                                                    | 13    | 15    | 17  | %VREG |

| $V_{HOT}$                              | Overtemperature-detection threshold (ratiometric to VTSB)                                  | Internal VTSB supply on, no external bias                                    |                                                    | 17    |       | 21  | %VREG |

| V <sub>TH_SHORT</sub>                  | Thermistor short-detection trip threshold (ratiometric to VTSB)                            | Internal VTSB supply on,                                                     | no external bias                                   | 1     |       | 10  | %VREG |

| V <sub>TH_HYST</sub>                   | TS comparator hysteresis                                                                   | Hysteresis for short, open comparators                                       | , and overtemperature                              | 3     |       | 8   | %VREG |

| V <sub>TH_OPEN</sub>                   | Thermistor open detection (ratiometric to VTSB)                                            | Internal VTSB supply on,                                                     | no external bias                                   | 90    |       | 98  | %VREG |

| CELL BALANCE                           |                                                                                            |                                                                              |                                                    | -     | *     | •   |       |

|                                        |                                                                                            |                                                                              | $V_{CELL} = CBV_{MAX} = 3.9$                       | -50%  | 10    | 50% |       |

| R <sub>BAL</sub>                       | Cell-balance internal resistance <sup>(7)</sup>                                            | r <sub>DS(on)</sub> for internal FET<br>switch, T <sub>A</sub> = 0°C to 50°C | V <sub>CELL</sub> = CBV <sub>MAX</sub> = 3.2       | -50%  | 20    | 50% | Ω     |

|                                        | resistance                                                                                 | SWILCH, TA = 0 0 to 50 0                                                     | V <sub>CELL</sub> = CBV <sub>MAX</sub> = 2.5       | -50%  | 30    | 50% |       |

| t <sub>CELL_BAL_CHECK</sub>            | Cell balancing update interval                                                             |                                                                              |                                                    |       | 7.5   |     | min   |

| OPEN CELL CONNECTIO                    | ON                                                                                         | I .                                                                          | 1                                                  |       |       |     |       |

| I <sub>LOAD_OPEN_CELL</sub> (8)        | Cell loading during open-cell detect                                                       |                                                                              |                                                    | 75    |       | 450 | μA    |

| topen_cell_check                       | Open-cell fault-sampling interval<br>(N = total number of cells in<br>pack)                |                                                                              |                                                    |       | 4 × N |     | s     |

| R <sub>OPEN_CELL</sub>                 | Minimum impedance from cell terminal to VCx input that is interpreted as an open condition |                                                                              |                                                    |       |       | 100 | kΩ    |

| BATTERY-PROTECTION-                    | -THRESHOLD TOLERANCES <sup>(9)</sup>                                                       |                                                                              |                                                    |       |       |     |       |

|                                        | OV detection threshold accuracy                                                            | T <sub>A</sub> = 0°C to 50°C                                                 |                                                    | -25   |       | 25  |       |

|                                        | for V <sub>OV</sub> = 4.2 V <sup>(10)</sup>                                                | T <sub>A</sub> = -25°C to 85°C                                               |                                                    | -50   |       | 50  | .,    |

| $\Delta V_{OV}$                        | OV detection threshold accuracy                                                            | T <sub>A</sub> = 0°C to 50°C                                                 |                                                    | -50 5 |       | 50  | mV    |

|                                        | for $V_{OV} = 3.2 \text{ V}^{(10)}$                                                        | $T_A = -25$ °C to 85°C                                                       |                                                    | -75   |       | 75  |       |

| $\Delta V_{UV}$                        | UV detection threshold accuracy                                                            | T <sub>A</sub> = -25°C to 85°C                                               |                                                    | -100  |       | 100 | mV    |

| ΔV <sub>SCD</sub><br>ΔV <sub>OCD</sub> | OCC/SCD detection threshold accuracy                                                       | T <sub>A</sub> = -25°C to 85°C                                               |                                                    | -20%  |       | 20% |       |

|                                        | SCC detection threshold                                                                    | V <sub>SCC</sub> from 10 mV to 15 m <sup>3</sup>                             | V                                                  | -3    |       | 3   | mV    |

| $\Delta V_{SCC}$                       | accuracy                                                                                   | V <sub>SCC</sub> > 15 mV                                                     |                                                    | -20%  |       | 20% |       |

| BATTERY PROTECTION                     | DELAY-TIME TOLERANCES(9)                                                                   |                                                                              |                                                    | II.   |       | l   |       |

| $\Delta t_{OV}$                        | OV detection delay time accuracy                                                           |                                                                              |                                                    | -15%  |       | 15% |       |

| $\Delta t_{UV}$                        | UV detection delay time accuracy                                                           | Default EEPROM setting                                                       |                                                    | -15%  |       | 15% |       |

| $\Delta t_{SCD}$                       | OCD/SCD detection delay time accuracy                                                      | 4 May                                                                        |                                                    | -15%  |       | 15% |       |

| $\Delta t_{SCC}$                       | SCD detection delay time accuracy                                                          | t <sub>SCD</sub> Max                                                         |                                                    | -15%  |       | 15% |       |

|                                        |                                                                                            | +                                                                            |                                                    |       |       |     |       |

- (7) Balance current is not internally limited. External series resistance must be used to ensure balance current is below 50 mA maximum to limit IC internal power dissipation.

- (8) This current is sufficient to detect an open-cell condition down to 100 kΩ across the cell from circuitry outside of the bq77908. The average current from this loading is less than 1 μA for a 8-cell configuration.

- Application Note: When using this part with other devices that connect to the battery cells, care must be taken to avoid excessive parallel capacitances on the cell input pins.

- (9) Nominal values are set by EEPROM programming; see EEPROM table for possible values.

- (10) Standard production parts are calibrated at 4.2 V. An additional OV threshold accuracy shift of 25 mV per volt of OV set point is possible. Contact TI for calibration options at set point voltages other than 4.2 V.

# **ELECTRICAL CHARACTERISTICS (continued)**

Vcell(n) = 1.4 to 4.375 for all cells,  $T_A = -25^{\circ}\text{C}$  to 85°C, BAT = 5.6 to 35 V; Typical values stated where  $T_A = 25^{\circ}\text{C}$  and BAT = 28.8 V (unless otherwise noted)

| PARAMETER              |                                                                                                                                                                   | TEST CONDITIONS    | MIN  | TYP  | MAX  | UNIT  |

|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|------|------|------|-------|

| CHARGER DETECTI        | ION <sup>(11)</sup>                                                                                                                                               |                    |      |      | "    |       |

| V <sub>CHG_DET1</sub>  | Voltage at CHGST pin,<br>referenced to VSS, to determine<br>charger present (charger<br>insertion detected when voltage<br>at CHGST pin > V <sub>CHG,DET1</sub> ) | 5.6 V < BAT < 35 V | 0.3  | 0.5  | 0.7  | V     |

| LOAD REMOVAL DE        | ETECTION                                                                                                                                                          |                    |      |      |      |       |

| V <sub>OPEN_LOAD</sub> | Voltage at DPCKN, referenced to VSS, with DSG FET disabled to detect load removal (load removal detected when voltage at DPCKN < V <sub>OPEN,LOAD</sub> )         | 5.6 V < BAT < 35 V | 1.5  | 2    | 2.5  | V     |

| R <sub>DSG_GND</sub>   | Internal resistance between DPCKN and VSS                                                                                                                         | 5.6 V < BAT < 35 V | 1000 | 1500 | 3000 | kΩ    |

| EEPROM LIFETIME        |                                                                                                                                                                   |                    |      |      | 1    |       |

| T <sub>DR</sub>        | Data retention                                                                                                                                                    | 5.6 V < BAT < 35 V | 10   |      |      | years |

<sup>(11)</sup> Alternate charger detection options are available using the CPCKN pin. Contact TI for additional configuration versions.

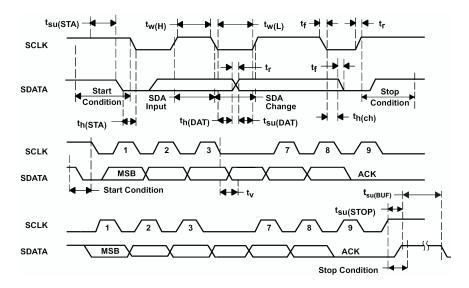

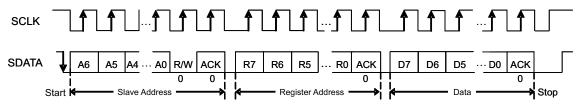

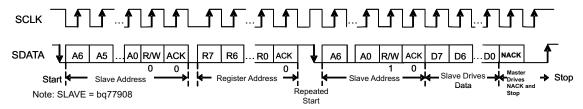

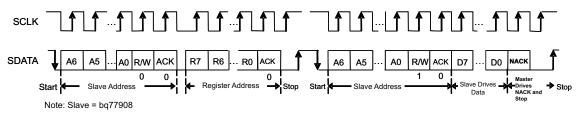

# **SERIAL COMMUNICATION INTERFACE (for Configuration Only)**

BAT = 5.6 V to 35 V,  $T_A = -25^{\circ}C$  to  $85^{\circ}C$

|                       | PARAMETER                                                            | MIN | MAX  | UNIT |

|-----------------------|----------------------------------------------------------------------|-----|------|------|

| t <sub>r</sub>        | SCLK, SDATA rise time                                                |     | 1000 | ns   |

| t <sub>f</sub>        | SCLK, SDATA fall time                                                |     | 300  | ns   |

| t <sub>w(H)</sub>     | SCLK pulse duration, high                                            | 8   |      | μs   |

| t <sub>w(L)</sub>     | SCLK pulse duration, low                                             | 10  |      | μs   |

| t <sub>su(STA)</sub>  | Setup time for START condition                                       | 9.4 |      | μs   |

| t <sub>h(STA)</sub>   | START condition hold time after which first clock pulse is generated | 8   |      | μs   |

| t <sub>su(DAT)</sub>  | Data setup time                                                      | 250 |      | ns   |

| t <sub>h(DAT)</sub>   | Data hold time                                                       | 0   |      | μs   |

| t <sub>su(STOP)</sub> | Setup time for STOP condition                                        | 8   |      | μs   |

| t <sub>su(BUF)</sub>  | Time the bus must be free before new transmission can start          | 9.4 |      | μs   |

| t <sub>V</sub>        | Clock low to data out valid                                          |     | 900  | ns   |

| t <sub>h(CH)</sub>    | Data out hold time after clock low                                   | 0   |      | ns   |

| f <sub>SCL</sub>      | Clock frequency                                                      | 0   | 50   | kHz  |

#### **GENERAL OPERATIONAL OVERVIEW**

## **POWER MODES**

The bq77908 has the following power modes: active and shutdown (LDO disabled). The following table outlines the operational functions in the different power modes.

| POWER MODE                 | MODE DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                 |

|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Active                     | The IC is operating with internal LDO enabled and battery monitoring functions available and operating. The active power mode includes <i>normal</i> operation, i.e., all cell voltages, load current, and temperature are within range, and DSG and CHG FETs are enabled. The active power mode also includes any fault detection / protection states which do not require the IC to drop to a low-power state. |

| Shutdown – LDO<br>disabled | Under certain fault conditions (see Table 2), the bq77908 enters the lowest possible power state to minimize current drain on the battery pack. The LDO output is turned off. All functions of the IC are inactive until a <i>charger recovery</i> condition is detected.                                                                                                                                        |

## **NORMAL OPERATION MODE**

When no cell voltage, pack current, temperature, open cell, or thermistor faults are present, the CHG and DSG FETs are turned ON, allowing normal operation of the system.

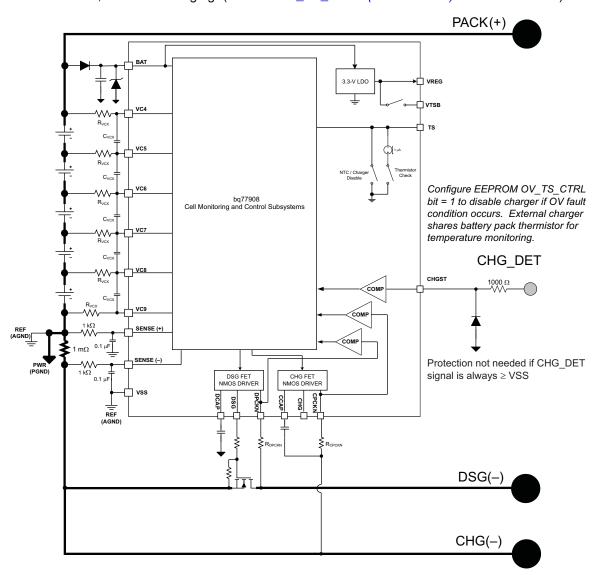

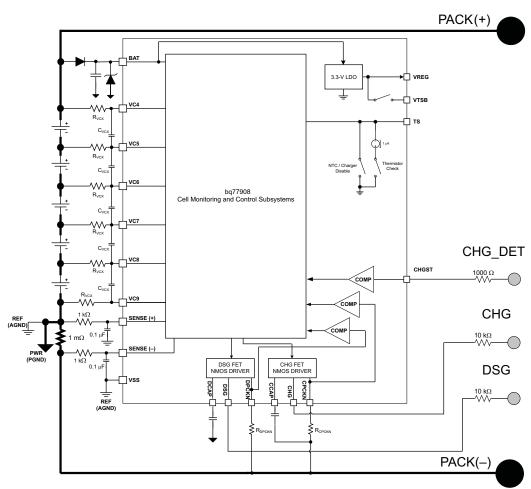

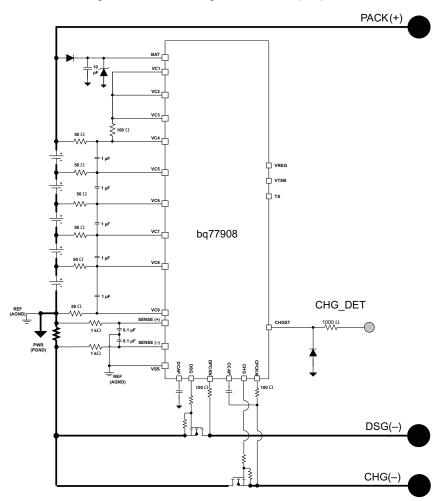

The architecture of the bq77908 allows the customer to implement different arrangements of power FET components within the battery pack. Some examples of different power FET arrangements are shown in the *Application Information* section.

#### PROGRAMMABLE PROTECTION FUNCTIONS

The bq77908 provides the following types of protection functions:

- Cell overvoltage

- Cell undervoltage

- · Discharge overcurrent

- Discharge-current short circuit

- · Charge-current short circuit

All of the voltage/current and time-delay thresholds can be adjusted for a specific application by programming the EEPROM settings of the IC. The ranges available are shown in Table 1.

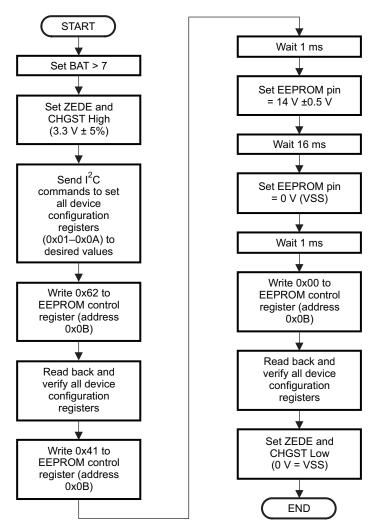

## **CAUTION**

Only a maximum of three EEPROM write cycles per byte should performed to ensure long-term data retention stability. (For circuit development purposes, the EEPROM may be rewritten many times.)

Table 1. Detection Voltage, Detection Delay Time Summary

| PARA                    | AMETER                                        | RANGE<br>(EEPROM Selected) | MIN    | MAX     | STEP            |

|-------------------------|-----------------------------------------------|----------------------------|--------|---------|-----------------|

| Overvoltage             | Cell voltage                                  |                            | 2.8 V  | 4.375 V | 25 mV           |

|                         | Delay                                         |                            | 0.5 s  | 2.25 s  | 0.25 s          |

|                         | Hysteresis                                    |                            | 0 mV   | 300 mV  | 25 mV or 50 mV  |

| Undervoltage            | Cell voltage                                  |                            | 1.4 V  | 2.9 V   | 100 mV          |

|                         | Delay                                         |                            | 500 ms | 32 s    | Binary spacing  |

|                         | Hysteresis                                    |                            | 400 mV | 1600 mV | 400 mV          |

| Discharge overcurrent   | SENSE(-) pin voltage with respect to SENSE(+) | Low                        | 25 mV  | 100 mV  | 5 mV            |

|                         |                                               | High                       | 125 mV | 500 mV  | 25 mV           |

|                         | Delay                                         |                            | 20 ms  | 300 ms  | 20 ms           |

|                         |                                               |                            | 400 ms | 2000 ms | 100 ms          |

| Discharge short circuit | SENSE(-) pin voltage with                     | Low                        | 40 mV  | 190 mV  | 10 mV           |

|                         | respect to SENSE(+)                           | High                       | 200 mV | 950 mV  | 50 mV           |

|                         | Delay                                         | Fast                       | 60 µs  | 960 µs  | 60 µs           |

|                         |                                               | Slow                       | 50 ms  | 1500 ms | 50 ms or 100 ms |

| Charge short circuit    | SENSE(-) pin voltage with                     | Low                        | –10 mV | −85 mV  | 5 mV            |

|                         | respect to SENSE(+)                           | High                       | –50 mV | –425 mV | 25 mV           |

|                         | Delay                                         |                            | 60 µs  | 960 µs  | 60 µs           |

# **Cell Overvoltage Detection and Recovery**

The CHG FET is turned off if any one of the cell voltages remains higher than  $V_{OV}$  for a period greater than  $t_{OV}$ . As a result, the cells are protected from an overcharge condition. After an overvoltage event occurs, the all cells must relax to less than  $(V_{OV} - V_{HYST})$  to allow recovery.

The V<sub>OV</sub>, t<sub>OV</sub>, and V<sub>HYST</sub> values can be set via the EEPROM bits OVT, OVD, and OVH.

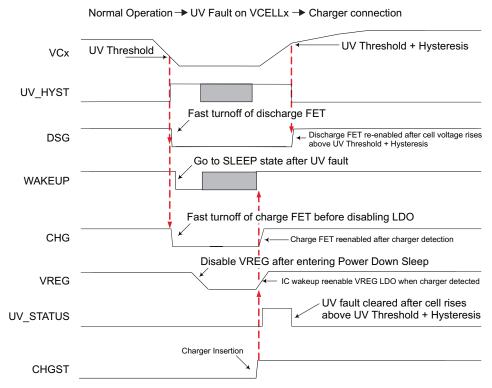

# **Cell Undervoltage Detection and Recovery**

When any one of the cell voltages falls below  $V_{UV}$ , for a period of  $t_{UV}$ , the bq77908 enters the undervoltage protection state. The DSG FET is turned off, and depending on configuration, the device could enter the SHUTDOWN mode. Both  $V_{UV}$  and  $t_{UV}$  can be configured via EEPROM bits UVT and UVD.

The recovery (fault release) is controlled by the EEPROM configuration bit UV REC.

Copyright © 2011, Texas Instruments Incorporated

If UV\_REC = 0, the DSG FET is re-enabled when **all** the cell voltages increase back above the  $V_{UV}$  threshold level plus the hysteresis value; there is no time-delay part of the recovery. In this case, when UV\_REC = 0 and under high load currents, the Vcell voltages could recover to >UV + hyst very quickly, re-enabling the FETs and allowing the high load current to persist. Care should be taken when using this UV\_REC = 0 mode, as the power MOSFETs could oscillate rapidly.

#### **CAUTION**

Care should be taken to properly set overcurrent and cell undervoltage trip thresholds, because it is possible that a fully charged pack with a continuous high discharge load can oscillate in and out of the undervoltage condition. This may result in overheating of the cells or protection MOSFETs due to the potentially high-duty-cycle operation.

If  $UV_REC = 1$ , the DSG FET is re-enabled when **all** the cell voltages increase back above the  $V_{UV}$  threshold level plus the hysteresis value **AND** the load is removed.

Current is interrupted by opening the FETs, and at this point the cell voltages may quickly recover above the UV + hyst levels if the battery pack is not completely depleted. However, the external load may remain attached. When the external load is removed, the IC detects load removal and reconnects the DSG FET.

If UV\_REC\_DLY = 1 and any cell remains below the VUV threshold level plus the hysteresis for longer than 8 seconds, the device enters SHUTDOWN mode. If UV\_REC\_DLY = 0, the device does **not** enter the SHUTDOWN mode from the cell undervoltage fault condition.

The LDO is turned off during the SHUTDOWN mode. Insertion into a charger is required to recover from the SHUTDOWN mode.

Charger detection methods are discussed in later sections, such as Application Information.

#### Overcurrent in Discharge (OCD) Detection

The OCD detection feature senses an overload current by measuring the voltage across the sense resistor. When an overload condition is detected, both of the power FETS are disabled to prevent damage to the cells and FET components. Criteria for fault recovery depend on the state of the SOR (EEPROM bit). Overcurrent trip level  $(V_{\text{OCD}})$  and blanking time delay  $(t_{\text{OCD}})$  are programmable via EEPROM bits OCDT and OCDD to match individual application requirements.

#### Short Circuit in Discharge (SCD) Detection

The SCD detection function senses severe discharge current by measuring the voltage across the sense resistor. When a short circuit is detected, both of the power FETs are disabled to prevent damage to the cells and FET components. Criteria for fault recovery depend on the state of the of the SOR (EEPROM bit). Short-circuit trip level ( $V_{SCD}$ ) and blanking time delay ( $t_{SCD}$ ) are programmable via EEPROM bits SCDT and SCDD to match individual application requirements.

#### Load Removal Detection/OCD and SCD Fault Recovery

The part includes an internal high-impedance connection between the DPCKN and VSS pins of approximately 1.5  $M\Omega$ . An external load (for example power tool motor winding), if still connected to the pack terminals, would present a very low impedance relative to the high internal pulldown resistance.

#### **NOTE**

If the external load presents additional capacitance, then an external pulldown may be required between the DPCKN and VSS pins. This extra pulldown does not increase battery load current when the external load is removed.

If the DSG power FET is disabled after an overload or short-circuit event, the voltage at the DPCKN is

approximately equivalent to the BAT voltage potential while an external load (e.g., power tool motor) is present at the pack terminals. When the external load is removed, the high-value internal resistance pulls down the DPCKN potential to the internal VSS level. An internal comparator monitors the DPCKN terminal voltage during the protection state. When the DPCKN voltage falls to  $< V_{OPEN\_LOAD}$  (approximately 2 V), the load removal is detected. Fault recovery from an OCD or SCD event depends on the state of the SOR EEPROM bit.

If SOR = 0, the FETs are re-enabled only after the external load removal is detected.

If SOR = 1, the FETs are re-enabled after the load is removed and a charger insertion is detected.

#### (Details of charger presence detection methods are discussed in later sections.)

#### Short Circuit in Charge (SCC) Detection

The SCC detection function senses severe charge current by measuring the voltage across the sense resistor. In this case, the voltage is negative (opposite polarity of OCD and SCD detection). When a short circuit is detected, both of the power FETS are disabled to prevent damage to the cells and FET components. Short-circuit trip level ( $V_{SCD}$ ) and blanking time delay ( $t_{SCD}$ ) are programmable via EEPROM bits SCCT and SCCD to match individual application requirements.

#### NOTE

The current sensing element must be located along a common charge and discharge path in order to protect against both charge and discharge current faults. This is particularly important to note for parallel FET configurations or configurations that combine the FET with the sense element.

# **Short Circuit in Charge Recovery**

An SCC fault is cleared after charger removal is detected. (See later sections for details of charger insertion and removal detection methods).

#### FIXED HARDWARE FAULT-PROTECTION FUNCTIONS

The bq77908 provides a number of fixed protection settings for hardware faults as listed:

- · Open cell connection

- Pack voltage Brownout condition power FET protection

- Charger-enable temperature range

- Open thermistor connection

- · Shorted thermistor connection

- Overtemperature protection

#### **Open Cell Connection**

A mechanical or assembly fault in the pack can cause a high-impedance or broken connection between the IC cell sense pins and the actual cells. During operation, the bq77908 periodically checks the validity of the individual cell voltage reading by applying a micropower pulsed load across each cell. If the connection between the pin and the cell is opened, the apparent cell voltage will collapse and a fault (permanent failure) condition is detected. The open cell detection reading is taken at a time interval of topen\_cell\_check, as specified in the parametric tables. Recommended external filter-capacitor maximum value is also listed in the *Recommended Operating Conditions*. Because an open-cell fault may be considered as a permanent failure, the fault detection logic must detect two consecutive open-cell conditions prior to activating the protection condition for an open-cell fault. Due to the nature of open-cell fault conditions, other *apparent* faults may be observed during an open-cell condition.

Summary of open-cell detection-logic operation:

For an N-cell battery pack, the bq77908 always protects (by opening the FETs) in some manner within the 2

× N × t<sub>OPEN\_CELL\_CHECK</sub> time frame (sampling interval is t<sub>OPEN\_CELL\_CHECK</sub>, and two successive open cell faults

are required to avoid nuisance tripping).

Copyright © 2011, Texas Instruments Incorporated

- Because an open cell connection results in a floating VCx input, a UV or an OV fault may be detected before

the open-cell fault due to their shorter fault filter times. Furthermore, the OV or UV condition may not be

stable and the fault may recover during the open-cell check interval (i.e., the FETs may toggle). In all cases

the open-cell fault is detected within the open-cell fault filter time and the FETs are shut off until the recovery

conditions are satisfied.

- The LDO shuts down following the detection of an open-cell fault, provided that a charger is not detected.

When the pack is awakened following this, the open-cell fault is initially cleared (FETs closed) and must be

re-evaluated over the filter time before the fault is again registered. Charger detection inhibits LDO shutdown;

however, once the charger is disconnected, the LDO then shuts down, provided that the recovery conditions

have not yet been satisfied.

#### **Additional Fault Protection Functions**

The brownout protection functionality is discussed in the *IC Internal Power Control* section of this document. Thermistor fault detection, charger/thermistor interface and control are discussed in the *Application Information* section.

#### IC INTERNAL POWER CONTROL

#### Power-On Reset/UVLO

On initial application of power to the BAT pin, the IC internal power supply rail begins to ramp up. The IC contains an internal undervoltage lockout (UVLO)/power-on reset (POR) circuit that prevents operation until the BAT voltage is sufficient to ensure predictable start-up and operation. All power for the IC internal circuitry is derived from the BAT pin. The UVLO/POR start-up threshold is specified in the parametric table as V<sub>STARTUP</sub>. Once the BAT voltage has exceeded this level, the internal LDO regulator and control circuitry are enabled and continue to operate even if BAT falls below VSTARTUP. If the BAT pin falls below the operational range given under *Recommended Operating Conditions*, the device powers down.

On initial power up, the state of the output MOSFET drive pins (CHG and DSG) is indeterminate until the voltage on BAT reaches the  $V_{STARTUP}$  threshold. No load should be applied during this period.

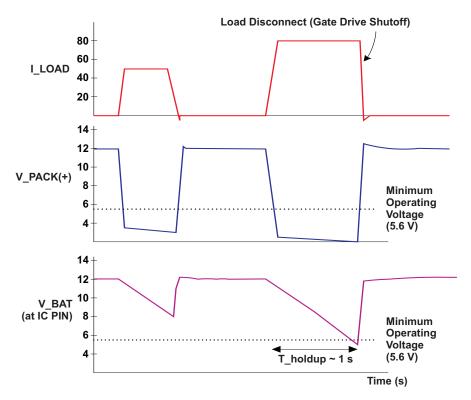

#### **BAT Holdup/Brownout Protection Functionality**

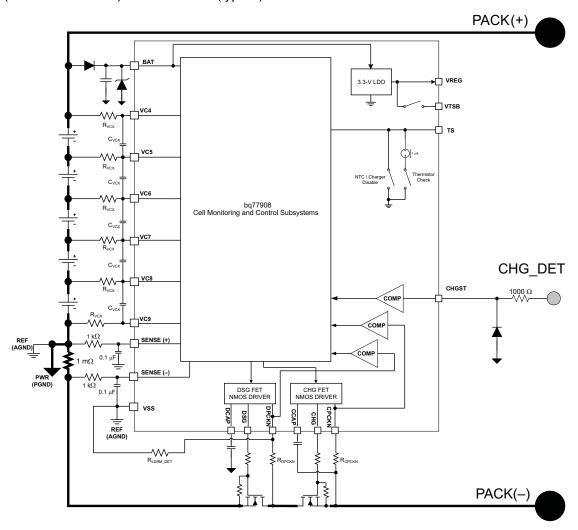

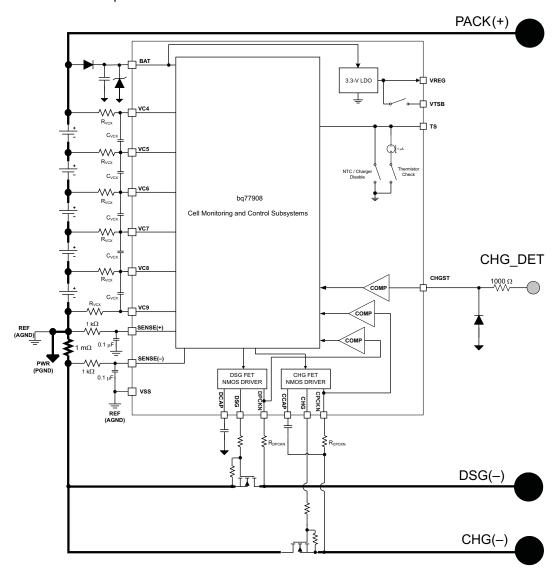

The BAT pin is used to power the IC internal circuitry, and should be supplied through a diode and held up with a capacitor (1) placed near the IC as shown in the application diagrams (see Figure 2 CELL BALANCING FUNCTION). The external diode prevents discharge of the IC power rail during external transients on the PACK(+) node.

This allows the bq77908 to maintain proper control of the pack and system during brownout conditions.

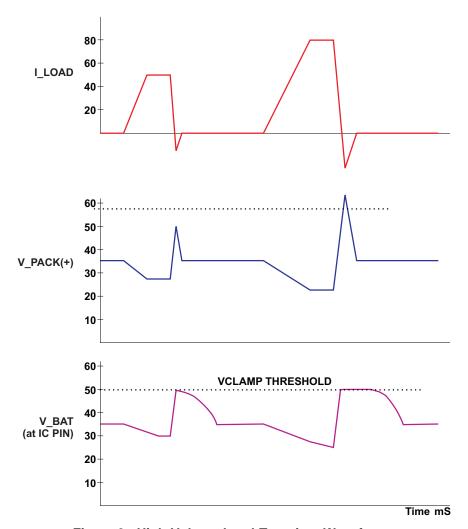

Brownout is defined as a situation during which the stack voltage collapses to a voltage below the minimum operating voltage of the IC (~5.6 V) for a short duration (~1 s). A typical application case is shown below. Additional examples are provided in the *Application Information* section later in this document.

If there are short-duration sags in the PACK(+) voltage (typically due to high load transients), the operating current for the IC is momentarily provided by the external capacitor. Assuming that there is no external load on the VREG (LDO output) pin, the IC draws approximately 50-µA average current from the capacitor. The holdup time before the IC goes into shutdown mode depends on the initial pack voltage. For a normal *low battery* initial condition using a 4-cell stack, the cells may be in the range of 3 V/cell or 12 V total for the pack voltage. If a load transient occurs at this point, and the pack voltage sags down to below the IC POR threshold, the voltage at the BAT pin is held above 5 V for slightly greater than one second using a 10-µF capacitor.

Waveforms typical of a load transient during low pack voltage conditions are shown as follows. In the first load transient, the PACK(+) rail momentarily collapses but the load is disconnected before the holdup time limit is exceeded. In the second load transient, the load is left on for a duration exceeding the holdup capability, so when the IC operating voltage reaches the gate-drive undervoltage limit, the external power FETs are disabled to disconnect the load.

(1) The capacitor should be sized according to the application requirements. A typical value would be 10 µF.

Figure 1. Load Transient Examples

## **BAT Voltage Peak Detection/Transient Suppression**

The use of an external diode and holdup capacitor allows the IC to provide controlled operation during brownout conditions. However, when the battery pack is at a high level, a different issue must be considered.

During normal operation of power equipment, load transients may induce high-voltage pulses on the PACK(+) rail that exceed the steady-state dc voltage output of the battery pack. In some cases, these transient voltages can exceed the battery rail by several volts. The voltage at the BAT pin may be *held up* to these higher voltages for a longer duration because the diode prevents the capacitor from discharging back into the cell stack after the transient pulses decay. When the dc level of the battery pack voltage is near 35 Vdc, high-current load disconnection may cause transients that would exceed the absolute maximum ratings of the device.

The BAT pin incorporates an internal Zener clamp that dissipates any transient voltage at the BAT pin that exceeds 50 V. This internal clamp has very limited energy absorption ability. Therefore, additional external circuitry is required for transient suppression, depending on the application environment. A Zener or equivalent rated at  $<5 \Omega$  and >3 W is recommended.

#### **BAT Voltage Rate of Change**

In addition to providing the holdup function, the filter components at the BAT pin serve to limit the maximum voltage rate of change. The voltage rate of change at the BAT pin should be limited to a maximum of 1 V per µs in order to prevent unwanted device shutdown.

Figure 2. Example 5-Cell, Series FET Configuration Schematic Using bq77908

Waveforms illustrative of load transients during high pack voltage conditions are shown here.

Figure 3. High-Voltage Load-Transient Waveforms

#### **FET Gate Drive Control**

As noted in the previous section, the BAT voltage at the IC pin is held up slightly longer than the external PACK(+) voltage using the external diode/capacitor to feed the BAT rail. Thus, if the BAT pin voltage at the IC sags, the external voltage sag will have exceeded the holdup time, and the IC is no longer able to operate for an extended period of time. At this point, the DSG and CHG gate drive outputs are actively driven low. The FET driver stages use two additional external capacitors (connected at the CCAP and DCAP pins) to maintain a local power reservoir dedicated to the gate drive circuitry, as the system (BAT) voltage may be collapsing during the time that the FETs are being turned off. The FETs are turned off when the voltage at the CCAP and/or DCAP pins falls below  $V_{GATE\_UV}$ .

By turning off the FETs quickly, the system avoids the condition of insufficient gate drive due to low battery voltage. (If the FET gate drive is not high enough, the power components may not be in their linear operating region, and could overheat due to resistive losses at high load currents).

In the case of a system undervoltage condition, both FETs are disabled within 500  $\mu$ s maximum; in all cases the FET fall time is less than fall time specified in the *Electrical Characteristics* section (FET Drive). During initial power up, once the UVLO threshold has been reached and the IC powers up fully, the rise time of the FET gate drive signal is also < 200  $\mu$ s. This assumes a nominal gate capacitance of 50 nF as specified in the *Electrical Characteristics* tables.

#### **NOTE**

Selection of power FETs should consider the resistive losses that may occur during the undefined voltage range during power up from a complete collapse of battery voltage and holdup capacitance.

#### **INITIAL POWER UP**

#### **Cell Connection**

The IC design allows connection of the cells in any order. For EEPROM programming, only the VSS and BAT terminals must be connected to allow the device to communicate using the serial communication interface.

For normal pack assembly, the recommended connection procedure is to start with the VSS connection, followed by the (+) terminal of the lowest (most negative) cell, and continuing up the stack to the top (most positive) cell. The BAT voltage shown in Start-Up Timing assumes this connection sequence is used.

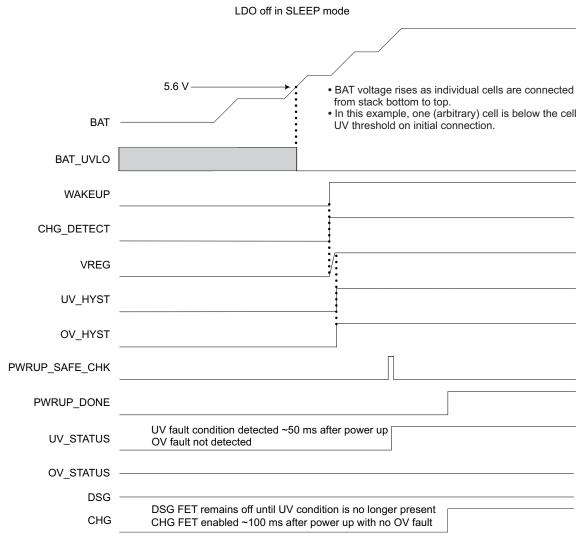

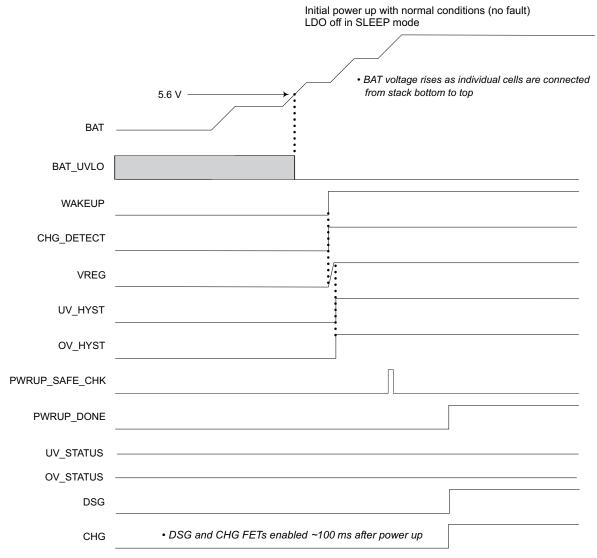

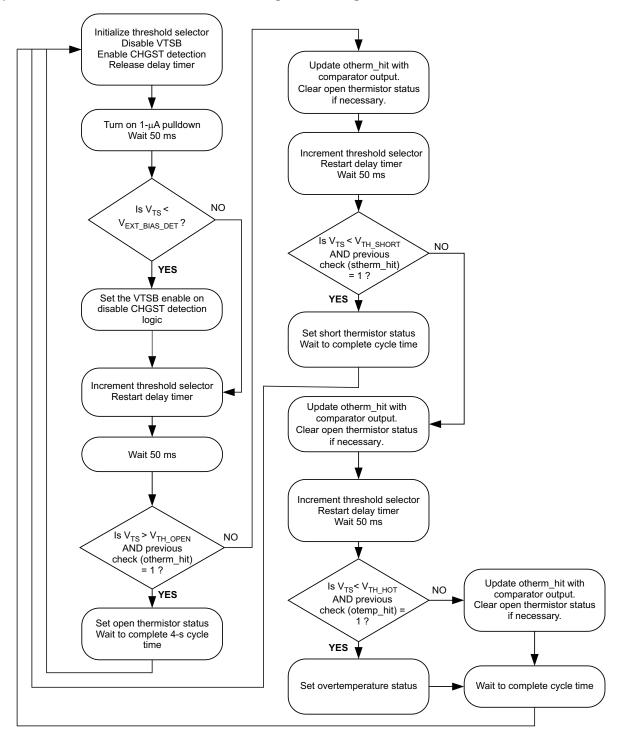

#### Power-Up Sequence and Continuous Fault-Detection Logic

The bq77908 goes through a fixed set of safety checks on each power-up sequence. The same checks are performed on each recovery cycle from the SHUTDOWN state (after a charger is detected).

For each power up, the following tests are made. If any of the conditions indicate a fault, the IC goes into the appropriate protection state. External connections may be required for fault recovery (such as load removal or insertion into charger). The device goes through a power-up sequence in < 100 ms, assuming no faults exist.

After the release of the internal digital reset, the logic begins a power-up safety check. Two internal signals, designated PWRUP\_SAFE\_CHK and PWRUP\_DONE, control the sequence.

When PWRUP\_DONE is low, the following conditions are forced:

- 1. CHG and DSG external pins / gate drive signals are low.

- 2. UV\_HYST = HI (internal logic signal use hysteresis level above UV threshold to clear fault)

- OV\_HYST = HI (internal logic signal use hysteresis level below OV threshold to clear fault)

After 50 ms of time has elapsed, a pulse of PWRUP\_SAFE\_CHK performs a check of each of the following circuits (with all time delays disabled):

- 1. UV comparator

- 2. OV comparator

- OCD comparator

- 4. SCD comparator

If a fault condition was found for any of the circuits, an internal fault status bit is set. For another 50 ms, the circuit has a chance to recover if the sample was corrupted. At the end of 100 ms, the PWRUP\_DONE signal is released. If no faults exist, the CHG, DSG, UV\_HYST, and OV\_HYST return to their normal-mode state.

Several of the protection circuits were not included in the power-up sequence (SCC, OT, TS, TO, OC). These faults are checked after the power-up sequence is completed. **Note:** This check is only performed on a power up from LDO-off or a digital reset occurring (i.e., POR state).

## **Start-Up Timing**

The following timing diagrams refer to signals at the device pins as well as to the following INTERNAL logic signals.

- BAT UVLO = HI when the BAT pin is below the POR threshold (undervoltage lockout).

- WAKEUP = HI whenever a charger is attached.

- UV\_STATUS = HI when n UV condition has been detected.

- OV\_STATUS = HI when an OV condition has been detected.

Submit Documentation Feedback

Copyright © 2011, Texas Instruments Incorporated

Figure 4. Initial Power Up With Single-Cell UV Fault

Copyright © 2011, Texas Instruments Incorporated

Figure 5. Initial Power Up With Normal Conditions (No Fault)

#### Table 2. Fault Detection, Action, and Recovery Condition Summary

|                               |                                                                   |                                         | Action Taken          |     |                                               |                 | T                                                                                                                   |