**TPS65200**

SLVSA48A - APRIL 2010-REVISED SEPTEMBER 2015

# TPS65200 Li+ Battery Charger With WLED Driver and Current Shunt Monitor

## **Features**

- Battery Switching Charger, WLED Driver, and Current Shunt Monitor in a Single Package

- **Battery Charger**

- Charges Faster Than Linear Chargers

- High-Accuracy Voltage and Current Regulation

- Input Current Regulation Accuracy: ±5% (100 mA, 500 mA)

- Charge Voltage Regulation Accuracy: ±0.5% (25°C) ±1% (0 - 125°C)

- Charge Current Regulation Accuracy: ±5%

- Bad Adaptor Detection and Rejection

- Safety Limit Register for Maximum Charge Voltage and Current Limiting

- High-Efficiency Mini-USB/AC Battery Charger for Single-Cell Li-Ion and Li-Polymer Battery **Packs**

- Built-In Input Current Sensing and Limiting

- Integrated Power FETs for Up to 1.25-A Charge Rate

- Programmable Charge Parameters through I<sup>2</sup>C Interface (Up to 400 Kbps):

- Input Current

- Fast-Charge/Termination Current

- Charge Voltage (3.5 V 4.44 V)

- Safety Timer

- Termination Enable

- Synchronous Fixed-Frequency PWM Controller Operating at 3 MHz With 0% to 99.5% Duty Cycle

- Safety Timer With Reset Control

- Reverse Leakage Protection Prevents Battery Drainage

- Thermal Regulation and Protection

- Input/Output Overvoltage Protection

- **Automatic Charging**

- **Boost Mode Operation for USB OTG**

- Input Voltage Range (VSYS): 2.5 V to

- Output Voltage for VBUS: 5 V

- **WLED Driver**

- 35-V Open LED Protection for Up to 8 LEDs

- 200-mV Reference Voltage With ±2% Accuracy

- Built-In Soft Start for WLED Boost

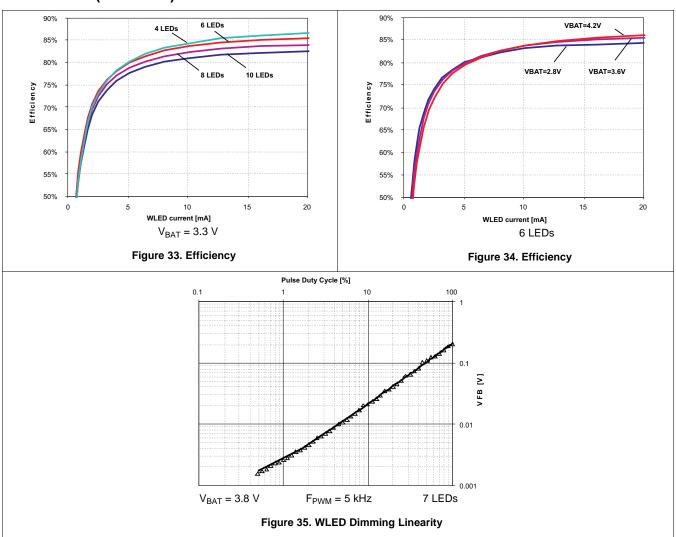

- Up to 90% Efficiency

- **Current Shunt Monitor**

- Fixed Gain of 25 V/V

- Input Referred Offset Voltage Less Than ±40 µV Typical Enables Use of Shunt Resistors as Low as 20 mΩ

- **Buffered Reference Voltage**

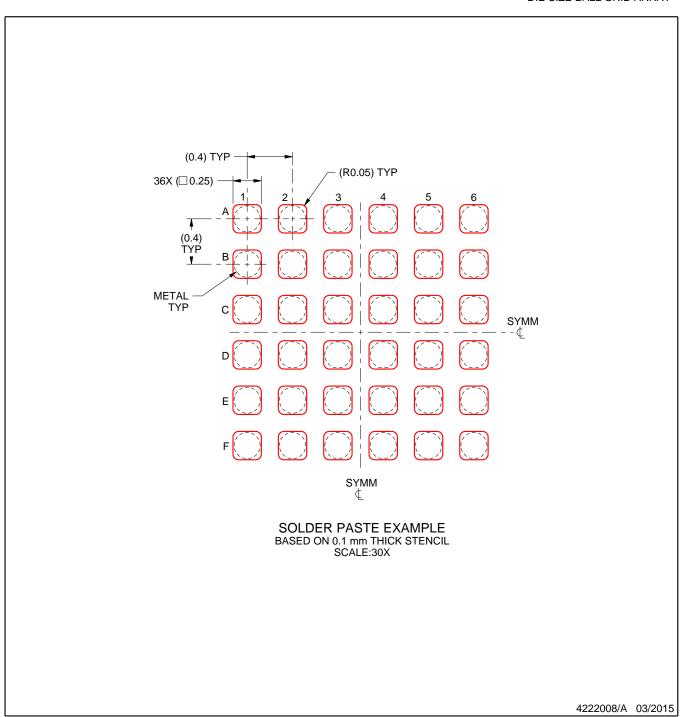

- Package

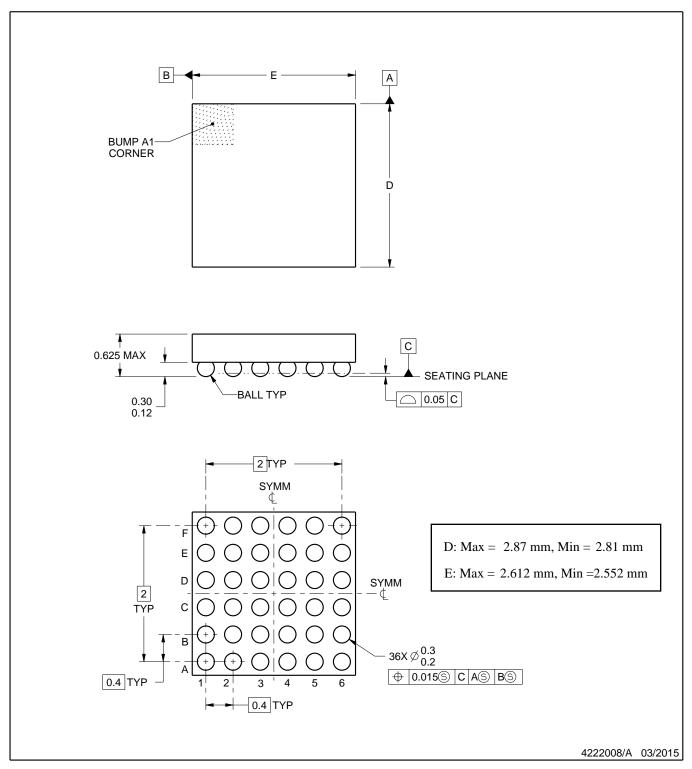

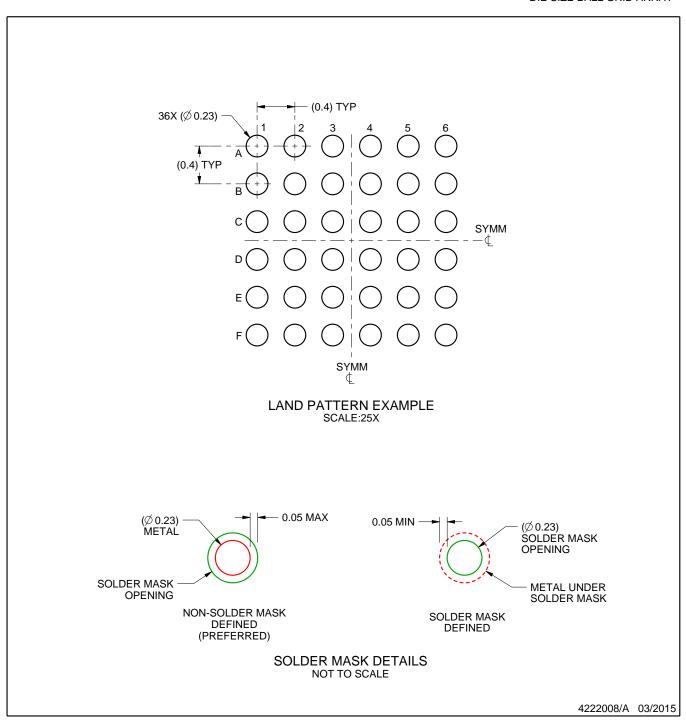

- 36-Ball, 0.4-mm Pitch DSBGA Package

## **Applications**

- Mobile Phones and Smart Phones

- MP3 Players

- Portable Navigation Devices

- Handheld Devices

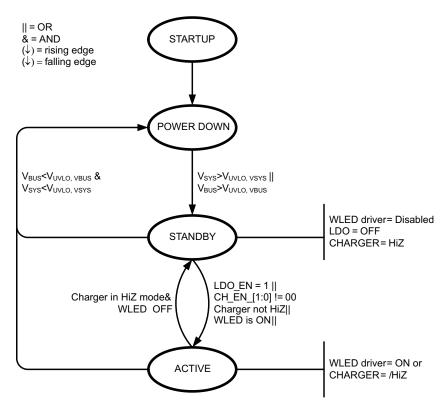

## 3 Description

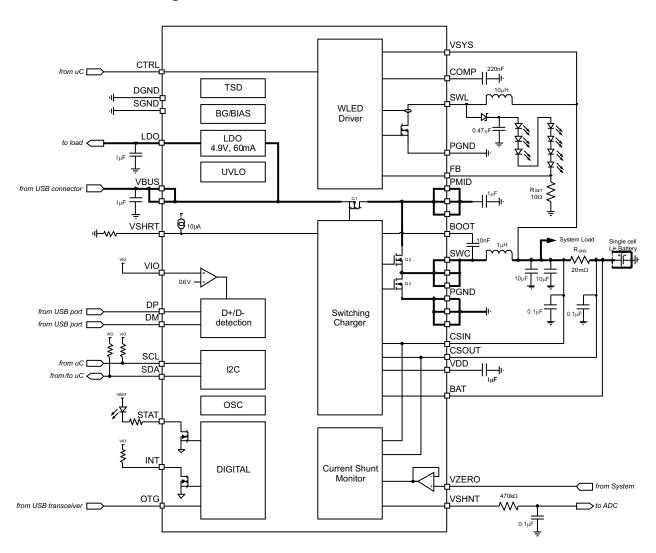

The TPS65200 device integrates a high-efficiency, USB-friendly switched-mode charger with OTG support for single-cell Li-ion and Li-polymer batteries, D+D- detection, a 50-mA fixed-voltage LDO, a highefficiency WLED boost converter, and high-accuracy current-shunt monitor into a single chip.

The TPS65200 comes in a tiny, 2.8-mm x 2.6-mm, 36-pin, 0.4-mm pitch die size ball grid array (DSBGA).

#### Device Information(1)

| PART NUMBER | PACKAGE    | BODY SIZE (NOM)   |  |

|-------------|------------|-------------------|--|

| TPS65200    | DSBGA (36) | 2.60 mm x 2.90 mm |  |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

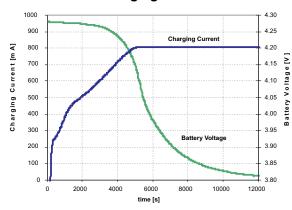

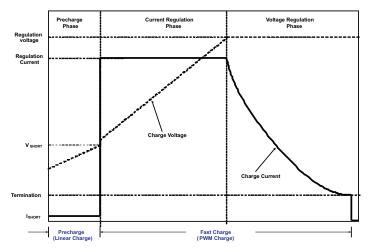

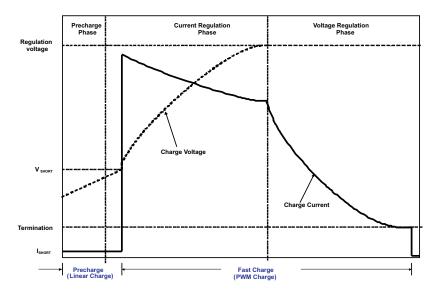

#### **Charging Curve**

## **Table of Contents**

| 1 | Features 1                           | 7.4 Device Functional Modes24                         |

|---|--------------------------------------|-------------------------------------------------------|

| 2 | Applications 1                       | 7.5 Programming35                                     |

| 3 | Description 1                        | 7.6 Register Maps36                                   |

| 4 | Revision History2                    | 8 Application and Implementation 50                   |

| 5 | Pin Configuration and Functions      | 8.1 Application Information 50                        |

| 6 | Specifications4                      | 8.2 Typical Application 50                            |

| U | 6.1 Absolute Maximum Ratings         | 9 Power Supply Recommendations 53                     |

|   | 6.2 ESD Ratings                      | 10 Layout 53                                          |

|   | 6.3 Recommended Operating Conditions | 10.1 Layout Guidelines 53                             |

|   | 6.4 Thermal Information              | 10.2 Layout Example54                                 |

|   | 6.5 Electrical Characteristics       | 11 Device and Documentation Support 55                |

|   | 6.6 Data Transmission Timing         | 11.1 Device Support55                                 |

|   | 6.7 Typical Characteristics          | 11.2 Community Resources55                            |

| 7 | Detailed Description 18              | 11.3 Trademarks 55                                    |

| • | 7.1 Overview                         | 11.4 Electrostatic Discharge Caution55                |

|   | 7.2 Functional Block Diagram         | 11.5 Glossary55                                       |

|   | 7.3 Feature Description              | 12 Mechanical, Packaging, and Orderable Information55 |

## 4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

## Changes from Original (April 2010) to Revision A

**Page**

Product Folder Links: TPS65200

Copyright © 2010-2015, Texas Instruments Incorporated

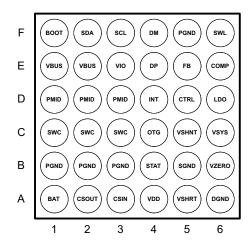

# 5 Pin Configuration and Functions

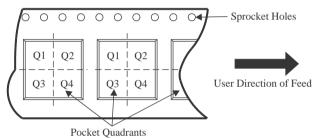

YFF Package 36-Pin DSBGA Bottom View, Top View

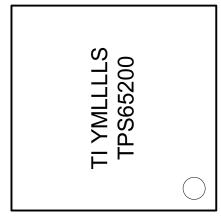

TI = TI LETTERS

YM = YEAR / MONTH DATE CODE

LLLL = LOT TRACE CODE

S = ASSEMBLY SITE CODE

O = Pin A1 (Filled Solid)

## **Pin Functions**

|     | PIN   |     |                                                                                                                                                                                                                                                                                                                                                   |

|-----|-------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO. | NAME  | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                       |

| A1  | BAT   | 0   | Output of the linear charger and battery voltage sense. Connect the battery from this pin to ground.                                                                                                                                                                                                                                              |

| A2  | CSOUT | ı   | Charge current-sense input. Battery current is sensed through the voltage drop across an external sense resistor. A 0.1-µF ceramic capacitor to PGND is required.                                                                                                                                                                                 |

| А3  | CSIN  | ı   | Charge current-sense input. Battery current is sensed through the voltage drop across an external sense resistor. A 0.1-µF ceramic capacitor to PGND is required.                                                                                                                                                                                 |

| A4  | VDD   | 0   | Internal supply for battery charger. Connect a 1-mF ceramic capacitor from this output to PGND. External load on VDD is not recommended.                                                                                                                                                                                                          |

| A5  | VSHRT | I   | The voltage on this pin defines the battery voltage for transitioning from linear charge (pre-charge) to fast charge. A 10-µA current source is internally connected to this pin. Connect a resistor from this pin to ground to setup VSHORT reference. If the pin is left floating or tied to VDD an internal VSHORT reference of 2.1 V is used. |

| A6  | DGND  |     | Digital ground                                                                                                                                                                                                                                                                                                                                    |

| B1  |       |     |                                                                                                                                                                                                                                                                                                                                                   |

| B2  | PGND  |     | Power ground                                                                                                                                                                                                                                                                                                                                      |

| ВЗ  |       |     |                                                                                                                                                                                                                                                                                                                                                   |

| B4  | STAT  | 0   | Charge status pin. Pulled low when charge in progress. Open drain for other conditions. This pin can also be controlled through I <sup>2</sup> C register. STAT can be used to drive a LED or communicate with a host processor.                                                                                                                  |

| B5  | SGND  |     | Signal ground                                                                                                                                                                                                                                                                                                                                     |

| B6  | VZERO | I   | This pin sets the zero-current output voltage level of the current shunt monitor.                                                                                                                                                                                                                                                                 |

| C1  |       |     |                                                                                                                                                                                                                                                                                                                                                   |

| C2  | SWC   | 0   | Internal switch to inductor connection (charger)                                                                                                                                                                                                                                                                                                  |

| C3  |       |     |                                                                                                                                                                                                                                                                                                                                                   |

| C4  | OTG   | I   | Boost control pin. Boost mode is turned on whenever this pin is active. Polarity is user defined through I <sup>2</sup> C register. The pin is disabled by default and can be enabled through I <sup>2</sup> C register bit.                                                                                                                      |

| C5  | VSHNT | 0   | Output of current shunt monitor. For positive currents (into battery) VSHNT > VZERO. For negative currents (out of the battery) VSHNT < VZERO.                                                                                                                                                                                                    |

| C6  | VSYS  | I   | Input supply for WLED driver and current shunt monitor                                                                                                                                                                                                                                                                                            |

| D1  |       |     |                                                                                                                                                                                                                                                                                                                                                   |

| D2  | PMID  | 0   | Connection point between reverse blocking MOSFET and high-side switching MOSFET. Bypass it with a minimum of 1-µF capacitor from PMID to PGND. No other circuits are recommended to connect at PMID pin.                                                                                                                                          |

| D3  |       |     | pin.                                                                                                                                                                                                                                                                                                                                              |

| D4  | INT   | 0   | Interrupt pin (open-drain). This pin is pulled low to signal to the main processor that a fault has occurred.                                                                                                                                                                                                                                     |

## Pin Functions (continued)

|     | PIN      | 1/0 | DESCRIPTION                                                                                                                                                                             |

|-----|----------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO. | NAME     | 1/0 | DESCRIPTION                                                                                                                                                                             |

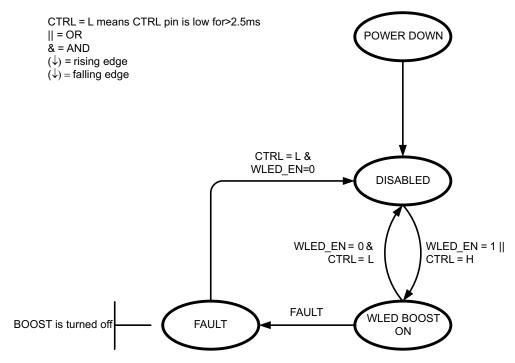

| D5  | CTRL     | I   | Control pin of the LED boost regulator. It is a multi-functional pin which can be used for enable control and PWM dimming.                                                              |

| D6  | LDO      | 0   | LDO output. LDO is regulated to 4.9 V and drives 60-mA of current. Bypass LDO to GND with at least a 1-µF ceramic capacitor. LDO is enabled when VBUS is above the VBUS UVLO threshold. |

| E1  | VELIC    | 1/0 | Charger input voltage. Bypass it with a 1-µF ceramic capacitor from VBUS to PGND. It also provides power to                                                                             |

| E2  | VBUS I/O |     | the load in boost mode.                                                                                                                                                                 |

| E3  | VIO      | I   | I/O reference voltage. A VIO level above 0.6 V disables automatic D+/D- detection.                                                                                                      |

| E4  | DP       | I   | USB port D+ input connection                                                                                                                                                            |

| E5  | FB       | I   | Feedback pin for current. Connect the sense resistor from FB to GND.                                                                                                                    |

| E6  | COMP     | 0   | Output of the transconductance error amplifier. Connect an external capacitor to this pin to compensate the regulator.                                                                  |

| F1  | воот     | 0   | Boot-strapped capacitor for the high-side MOSFET gate driver. Connect a 10-nF ceramic capacitor (voltage rating above 10 V) from BOOST pin to SWC pin.                                  |

| F2  | SDA      | I/O | I <sup>2</sup> C interface data                                                                                                                                                         |

| F3  | SCL      | I   | I <sup>2</sup> C interface clock                                                                                                                                                        |

| F4  | DM       | I   | USB port D- input connection                                                                                                                                                            |

| F5  | PGND     |     | Power ground                                                                                                                                                                            |

| F6  | SWL      | I   | This is the switching node of the LED driver. Connect the inductor from the supply to the SWL pin. This pin is also used to sense the output voltage for open LED protection.           |

# 6 Specifications

## 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)(2)

|                                                   |                                                                                                         | MIN  | MAX | UNIT |

|---------------------------------------------------|---------------------------------------------------------------------------------------------------------|------|-----|------|

| Supply voltage (with respect to PGN               | ID) VBUS                                                                                                | -2   | 20  | V    |

|                                                   | SDA, SCL, DM, DP, SWL, VZERO, VSHRT, CSIN, CSOUT, CSOT, LDO, INT, OTG, VSYS, VSHNT, VDD, VIO, BAT, CTRL | -0.3 | 7   |      |

| Input/Output voltage (with respect to             | PMID, STAT                                                                                              | -0.3 | 20  |      |

| PGND)                                             | VDD                                                                                                     |      | 6.5 | V    |

| ·                                                 | SWC, BOOT                                                                                               | -0.7 | 20  |      |

|                                                   | FB,COMP                                                                                                 | -0.3 | 3   |      |

|                                                   | SWL                                                                                                     | -0.3 | 44  |      |

| Voltage difference between CSIN as                | nd CSOUT inputs (VCSIN -VCSOUT)                                                                         |      | ± 7 | V    |

| Output current (average)                          | SWC                                                                                                     |      | 1.5 | Α    |

| Output current (continuous)                       | LDO                                                                                                     |      | 100 | mA   |

| T <sub>A</sub> Operating ambient temperature      |                                                                                                         | -40  | 85  | °C   |

| T <sub>J</sub> Max operating junction temperature |                                                                                                         |      | 150 | °C   |

| T <sub>C</sub> Max operating case temperature     |                                                                                                         |      | 150 | °C   |

| T <sub>stg</sub> Storage temperature              |                                                                                                         | -65  | 150 | °C   |

<sup>(1)</sup> Stresses beyond those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under *Recommended Operating Conditions* is not implied. Exposure to absolute—maximum—rated conditions for extended periods may affect device reliability.

<sup>(2)</sup> All voltage values are with respect to network ground terminal.

## 6.2 ESD Ratings

|                    |                           |                                                                               | VALUE | UNIT |

|--------------------|---------------------------|-------------------------------------------------------------------------------|-------|------|

| V <sub>(ESD)</sub> | Flootroototic discharge   | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins <sup>(1)</sup>   | ±2000 | V    |

|                    | Electrostatic discharge C | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins (2) | ±500  | V    |

JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process. JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

## 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|      |                | MIN  | NOM MAX | UNIT |

|------|----------------|------|---------|------|

| VBUS | Supply voltage | 4    | 6       | V    |

| SWL  | Output voltage | VBAT | 39      | V    |

## 6.4 Thermal Information

|                       |                                              | TPS65200    |      |

|-----------------------|----------------------------------------------|-------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | YFF (DSBGA) | UNIT |

|                       |                                              | 36 PINS     |      |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance       | 54.5        | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 0.2         | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 8.5         | °C/W |

| Ψлт                   | Junction-to-top characterization parameter   | 0.9         | °C/W |

| ΨЈВ                   | Junction-to-board characterization parameter | 8.5         | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | N/A         | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

## 6.5 Electrical Characteristics

VBAT = 3.6 V  $\pm$ 5%, T<sub>J</sub> = 27°C (unless otherwise noted)

|                                                                                   | PARAMETER                                                                                        | TEST (                                        | CONDITIONS                                                                 | MIN   | TYP   | MAX      | UNIT |

|-----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|-----------------------------------------------|----------------------------------------------------------------------------|-------|-------|----------|------|

| INPUT CUR                                                                         | RENTS                                                                                            |                                               |                                                                            |       |       | *        |      |

|                                                                                   |                                                                                                  |                                               | Charger Hi-Z mode<br>WLED disabled<br>Shunt monitor<br>disabled            |       | 2     | 10       |      |

| I <sub>DISCHARGE</sub>                                                            | Battery discharge current in high<br>Impedance mode (CSIN,<br>CSOUT,SWC, SWL, BAT, VSYS<br>pins) | 0°C < TJ < 85°C,<br>V <sub>BAT</sub> = 4.2 V  | Charger Hi-Z mode<br>WLED enabled, no<br>load<br>Shunt monitor<br>disabled |       |       | 1800     | μΑ   |

|                                                                                   |                                                                                                  |                                               | Charger HiZ mode<br>WLED disabled Shunt<br>monitor enabled                 |       |       | 60       |      |

|                                                                                   |                                                                                                  | V <sub>BUS</sub> > V <sub>BUS(min)</sub>      | Charger PWM ON                                                             |       | 10000 |          |      |

| I <sub>DISCHARGE</sub> I <sub>VBUS</sub> I <sub>VBUS_LEAK</sub> VOLTAGE RE  VOREG | VBUS supply current                                                                              |                                               | Charger PWM OFF                                                            |       |       | 5000     | μA   |

|                                                                                   |                                                                                                  | 0°C < T <sub>J</sub> < 85°C, HZ_MODE = 1      |                                                                            | 15    |       |          |      |

| I <sub>VBUS_LEAK</sub>                                                            | Leakage current from battery to VBUS pin                                                         | 0°C < T <sub>J</sub> < 85°C, \                | / <sub>BAT</sub> = 4.2 V HiZ mode                                          |       |       | 5        | μΑ   |

| VOLTAGE I                                                                         | REGULATION                                                                                       |                                               |                                                                            |       |       | <u> </u> |      |

| I <sub>DISCHARGE</sub> I <sub>VBUS</sub> I <sub>VBUS</sub> LEAK VOLTAGE R         | Output charge voltage                                                                            | Operating in voltage regulation, programmable |                                                                            | 3.5   |       | 4.44     | V    |

|                                                                                   | Voltage up sulption on a superior                                                                | T <sub>A</sub> = 25°C                         |                                                                            | -0.5% |       | 0.5%     |      |

|                                                                                   | Voltage regulation accuracy                                                                      | Full temperature range                        |                                                                            | -1%   |       | 1%       |      |

VBAT = 3.6 V  $\pm$ 5%, T<sub>J</sub> = 27°C (unless otherwise noted)

|                        | PARAMETER                                                                                                                | TEST CONDITIONS                                                                                                                                                                  | MIN                                                                                                                                                                            | TYP | MAX                                                            | UNIT |

|------------------------|--------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|----------------------------------------------------------------|------|

| CURRENT F              | REGULATION -FAST CHARGE                                                                                                  |                                                                                                                                                                                  |                                                                                                                                                                                |     |                                                                |      |

|                        | Output charge ourrent                                                                                                    | $\label{eq:VSHRT} \begin{split} &V_{SHRT} \leq V_{CSOUT} < V_{OREG} \\ &V_{BUS} > 5 \text{ V, } R_{SNS} = 20 \text{ m}\Omega, \\ &LOW\_CHG = 0, \text{Programmable} \end{split}$ | 550                                                                                                                                                                            |     | 1250                                                           | mΛ   |

| I <sub>OCHARGE</sub>   | Output charge current                                                                                                    | $\begin{split} &V_{LOWV} \leq V_{CSOUT} < V_{OREG}, \\ &V_{BUS} > 5 \text{ V, } R_{SNS} = 20 \text{ m}\Omega, \\ &LOW\_CHG = 1 \end{split}$                                      | UT < VOREG SNS = 20 mΩ, 0, Programmable UT < VOREG, SNS = 20 mΩ, 150 200 150 200 1 250 NS, SNS = 20 mΩ, 1 150 200 1 200 NS, SNS = 20 mΩ, 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 | mA  |                                                                |      |

| CHARGE TE              | ERMINATION DETECTION                                                                                                     |                                                                                                                                                                                  |                                                                                                                                                                                |     |                                                                |      |

| I <sub>TERM</sub>      | Termination charge current                                                                                               | $V_{CSOUT} > V_{OREG-VRCH}, V_{BUS} > 5 V,$<br>$R_{SNS} = 20 \text{ m}\Omega, \text{ Programmable}$                                                                              | 50                                                                                                                                                                             |     | 400                                                            | mA   |

|                        | Deglitch time for charge termination                                                                                     | Both rising and falling, 2-mV overdrive,<br>$t_{RISE}$ , $t_{FALL}$ = 100 ns                                                                                                     |                                                                                                                                                                                | 30  |                                                                | ms   |

| CHARGE C               | URRENT ACCURACY                                                                                                          |                                                                                                                                                                                  |                                                                                                                                                                                |     |                                                                |      |

| V <sub>OS, CHRGR</sub> | Offset voltage, sense voltage amplifier Charge current accuracy = V <sub>OS</sub> /(I <sub>SET</sub> xR <sub>SNS</sub> ) | $T_A = 0$ °C to 85°C                                                                                                                                                             | -1                                                                                                                                                                             |     | 1                                                              | mV   |

| BAD ADAP               | TOR DETECTION                                                                                                            |                                                                                                                                                                                  | •                                                                                                                                                                              |     |                                                                |      |

|                        | Input voltage lower limit                                                                                                | Bad adaptor detection, V <sub>BUS</sub> falling                                                                                                                                  | 3.6                                                                                                                                                                            | 3.8 | 4                                                              | V    |

| $V_{IN(MIN)}$          | Deglitch time for $V_{\text{BUS}}$ rising above $V_{\text{IN(MIN)}}$                                                     | Rising voltage, 2-mV over drive, $t_{RISE} = 100 \text{ ns}$                                                                                                                     |                                                                                                                                                                                | 30  |                                                                | ms   |

|                        | Hysteresis for V <sub>IN(MIN)</sub>                                                                                      | V <sub>BUS</sub> rising                                                                                                                                                          | 100                                                                                                                                                                            |     | 200                                                            | mV   |

| I <sub>ADET</sub>      | Current source to GND                                                                                                    | During bad adaptor detection                                                                                                                                                     | 20                                                                                                                                                                             | 30  | 40                                                             | mA   |

| T <sub>INT</sub>       | Detection interval                                                                                                       | Input power source detection                                                                                                                                                     |                                                                                                                                                                                | 2   |                                                                | S    |

| INPUT BASI             | ED DYNAMIC POWER MANAGEMEN                                                                                               | IT                                                                                                                                                                               |                                                                                                                                                                                |     |                                                                |      |

| $V_{IN\_LOW}$          | The threshold when input based DPM loop kicks in                                                                         | Charge mode, programmable                                                                                                                                                        | 4.2                                                                                                                                                                            |     | 4.76                                                           | V    |

| VIN_LOW                | DPM loop kick-in threshold tolerance                                                                                     |                                                                                                                                                                                  | -2%                                                                                                                                                                            |     | 2%                                                             |      |

| INPUT CUR              | RENT LIMITING                                                                                                            |                                                                                                                                                                                  | •                                                                                                                                                                              |     |                                                                |      |

|                        |                                                                                                                          | I <sub>IN_LIMIT</sub> = 100 mA                                                                                                                                                   | 88                                                                                                                                                                             | 93  | 98                                                             |      |

| I <sub>IN_LIMIT</sub>  | Input current limiting threshold                                                                                         | I <sub>IN_LIMIT</sub> = 500 mA                                                                                                                                                   | 450                                                                                                                                                                            | 475 | 500                                                            | mA   |

|                        |                                                                                                                          | I <sub>IN_LIMIT</sub> = 975 mA                                                                                                                                                   | 875                                                                                                                                                                            | 925 | 1<br>200<br>40<br>4.76<br>2%<br>98<br>500<br>975<br>6.5<br>6.5 |      |

| VDD REGUL              | LATOR                                                                                                                    |                                                                                                                                                                                  |                                                                                                                                                                                |     |                                                                |      |

| .,                     | Internal bias regulator voltage                                                                                          | $V_{BUS} > V_{IN(min)}$ or $V_{SYS} > V_{BATMIN}$ ,<br>$I_{VDD} = 1$ mA, $C_{VDD} = 1$ $\mu F$                                                                                   | 2                                                                                                                                                                              |     | 6.5                                                            | V    |

| $V_{DD}$               | VDD output short current limit                                                                                           |                                                                                                                                                                                  |                                                                                                                                                                                | 30  | 200 400 400 4,76 2% 98 500 975 6.5 6.5 160 0.4 1               | mA   |

|                        | Voltage from BST pin to SWC pin                                                                                          | During charge or boost operation                                                                                                                                                 |                                                                                                                                                                                |     | 6.5                                                            | V    |

| BATTERY R              | RECHARGE THRESHOLD                                                                                                       |                                                                                                                                                                                  |                                                                                                                                                                                |     |                                                                |      |

|                        | Recharge threshold voltage                                                                                               | Below V <sub>OREG</sub>                                                                                                                                                          | 100                                                                                                                                                                            | 130 | 160                                                            | mV   |

| V <sub>RCH</sub>       | Deglitch time                                                                                                            | V <sub>CSOUT</sub> decreasing below threshold, t <sub>FALL</sub> = 100 ns, 10-mV overdrive                                                                                       |                                                                                                                                                                                | 130 |                                                                | ms   |

| STAT OUTP              | PUT                                                                                                                      |                                                                                                                                                                                  |                                                                                                                                                                                |     |                                                                |      |

| Vo. (07: =)            | Low-level output saturation voltage                                                                                      | I <sub>O</sub> = 10 mA, sink current                                                                                                                                             |                                                                                                                                                                                |     | 0.4                                                            | V    |

| V <sub>OL(STAT)</sub>  | High-level leakage current                                                                                               | Voltage on STAT pin is 5 V                                                                                                                                                       |                                                                                                                                                                                |     | 1                                                              | μΑ   |

| REVERSE P              | PROTECTION COMPARATOR                                                                                                    |                                                                                                                                                                                  |                                                                                                                                                                                |     |                                                                |      |

| $V_{REV}$              | Reverse protection threshold, $V_{\text{BUS-VCSOUT}}$                                                                    | 2.3 V ≤ V <sub>CSOUT</sub> ≤ V <sub>OREG</sub> , V <sub>BUS</sub> falling                                                                                                        | 0                                                                                                                                                                              | 40  | 100                                                            | mV   |

|                        | Reverse protection exit hysteresis                                                                                       | 2.3 V ≤ V <sub>CSOUT</sub> ≤ V <sub>OREG</sub>                                                                                                                                   | 140                                                                                                                                                                            | 200 | 260                                                            | mV   |

| V <sub>REV-EXIT</sub>  | Deglitch time for $V_{BUS}$ rising above $V_{REV} + V_{REV\_EXIT}$                                                       | Rising voltage                                                                                                                                                                   |                                                                                                                                                                                | 30  |                                                                | ms   |

|                        | · · · · · · · · · · · · · · · · · · ·                                                                                    |                                                                                                                                                                                  |                                                                                                                                                                                |     |                                                                |      |

VBAT = 3.6 V  $\pm$ 5%, T<sub>J</sub> = 27°C (unless otherwise noted)

|                                                                                                | PARAMETER                                                                | TEST CONDITIONS                                                                           | MIN  | TYP   | MAX                    | UNIT |

|------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|------|-------|------------------------|------|

| VBUS UVLC                                                                                      | )                                                                        |                                                                                           |      |       |                        |      |

| V <sub>UVLO</sub>                                                                              | IC active threshold voltage                                              | V <sub>BUS</sub> rising                                                                   | 3.05 | 3.3   | 3.55                   | V    |

| V <sub>UVLO_HYS</sub>                                                                          | IC active hysteresis                                                     | V <sub>BUS</sub> falling from above V <sub>UVLO</sub>                                     | 120  | 150   |                        | mV   |

| PWM                                                                                            | •                                                                        | 0 000                                                                                     |      |       |                        |      |

| f <sub>PWM</sub>                                                                               | PWM frequency, charger                                                   |                                                                                           |      | 3     |                        | MHz  |

|                                                                                                | Internal top reverse blocking MOSFET on-resistance                       | I <sub>IN_LIMIT</sub> = 500 mA,<br>Measured from VBUS to PMID                             |      | 180   |                        |      |

| R <sub>DSON</sub>                                                                              | Internal top N-channel Switching MOSFET on-resistance                    | Measured from PMID to SWC                                                                 |      | 120   |                        | mΩ   |

|                                                                                                | Internal bottom N-channel MOSFET on-resistance                           | Measured from SW to PGND                                                                  |      | 150   |                        |      |

| D <sub>MAX</sub>                                                                               | Maximum duty cycle                                                       |                                                                                           |      | 99.5% |                        |      |

| D <sub>MIN</sub>                                                                               | Minimum duty cycle                                                       |                                                                                           | 0%   |       |                        |      |

|                                                                                                | Synchronous mode to nonsynchronous mode transition current threshold (1) | Low-side MOSFET cycle-by-cycle current sensing                                            |      | 100   |                        | mA   |

| BOOST MO                                                                                       | DE OPERATION FOR VBUS (OPA_N                                             | IODE=1, HZ_MODE=0)                                                                        |      |       |                        |      |

| V <sub>BUS_B</sub>                                                                             | Boost output voltage (to pin VBUS)                                       | 2.5 V < V <sub>BUS</sub> < 4.5 V; Including line and load regulation over full temp range | 4.75 | 5     | 5.25                   | V    |

| I <sub>BO</sub>                                                                                | Maximum output current for boost                                         | $V_{BUS\_B} = 5 \text{ V}, 2.5 \text{ V} < V_{BUS} < 4.5 \text{ V}$                       | 200  |       |                        | mA   |

| I <sub>BLIMIT</sub>                                                                            | Cycle by cycle current limit for boost                                   | V <sub>BUS_B</sub> = 5 V, 2.5 V < V <sub>SYS</sub> < 4.5 V                                |      | 1     |                        | Α    |

| V <sub>BUSOVP</sub>                                                                            | Overvoltage protection threshold for boost (VBUS pin)                    | Threshold over V <sub>BUS</sub> to turn off converter during boost                        | 5.8  | 6     | 6.2                    | V    |

|                                                                                                | VBUSOVP hysteresis                                                       | V <sub>BUS</sub> falling from above V <sub>BUSOVP</sub>                                   |      | 200   |                        | mV   |

| V                                                                                              | Maximum battery voltage for boost                                        | V <sub>SYS</sub> rising edge during boost                                                 | 4.75 | 4.9   | 9 5.05                 | V    |

| VBATMAX                                                                                        | VBATMAX hysteresis                                                       | V <sub>SYS</sub> falling from above V <sub>BATMAX</sub>                                   |      | 200   |                        | mV   |

| VDATAIN                                                                                        | Minimum battery voltage for boost                                        | During boosting                                                                           |      | 2.5   |                        | V    |

| * DATIVIIN                                                                                     | (VSYS pin)                                                               | Before boost starts                                                                       |      | 2.9   | 9 5.05<br>0 5          | •    |

|                                                                                                | Boost output resistance at high<br>impedance mode (From VBUS to<br>PGND) | HZ_MODE = 1                                                                               | 500  |       |                        | kΩ   |

| CHARGER I                                                                                      | PROTECTION                                                               |                                                                                           |      |       | •                      |      |

| V <sub>OVP-IN USB</sub>                                                                        | Input V <sub>BUSOVP</sub> threshold voltage                              | Threshold over V <sub>BUS</sub> to turn off converter during charge                       | 6.3  | 6.5   | 6.7                    | V    |

| *** "***                                                                                       | V <sub>OVP_IN_USB</sub> hysteresis                                       | V <sub>BUS</sub> falling from above V <sub>OVP_IN</sub>                                   |      | 140   |                        | mV   |

| V                                                                                              | Battery OVP threshold voltage                                            | $V_{CSOUT}$ threshold over $V_{OREG}$ to turn off charger during charge (% $V_{OREG}$ )   | 110% | 117%  | 121%                   |      |

| VOVP                                                                                           | V <sub>OVP</sub> hysteresis                                              | Lower limit for $V_{CSOUT}$ falling from > $V_{OVP}$ (% $V_{OREG}$ )                      |      | 11%   |                        |      |

| I <sub>LIMIT</sub>                                                                             | Cycle-by-cycle current limit for charge                                  | Charge mode operation                                                                     | 1.8  | 2.4   | 3                      | Α    |

|                                                                                                |                                                                          | V <sub>CSOUT</sub> rising, VSHRT connected to VDD                                         | 2    | 2.1   | 2.2                    | V    |

|                                                                                                | Trickle to fast charge threshold                                         | Resistor connected from VSHRT to GND                                                      | 1.8  |       | V <sub>BUS</sub> – 0.7 | V    |

| V <sub>SHORT</sub>                                                                             | Internal current source connected to V <sub>SHRT</sub> pin               |                                                                                           | 9.4  | 10    | 10.6                   | μΑ   |

| DMIN  BOOST MOI  BUS_B  BO  BLIMIT  BUSOVP  BATMAX  BATMIN  CHARGER F  OVP-IN_USB  VOVP  LIMIT | V <sub>SHORT</sub> hysteresis                                            | V <sub>CSOUT</sub> falling from above VSHORT                                              |      | 100   |                        | mV   |

|                                                                                                | Enable threshold for internal V <sub>SHORT</sub> reference               | percentage of VDD                                                                         |      | 90%   |                        |      |

<sup>(1)</sup> Bottom N-channel MOSFET always turns on for approximately 60 ns and then turns off if current is too low.

VBAT = 3.6 V  $\pm$ 5%, T<sub>J</sub> = 27°C (unless otherwise noted)

|                         | PARAMETER                                               | TEST CONDITIONS                                                                 | MIN  | TYP | MAX | UNIT |

|-------------------------|---------------------------------------------------------|---------------------------------------------------------------------------------|------|-----|-----|------|

| I <sub>SHORT</sub>      | Trickle charge charging current                         | V <sub>CSOUT</sub> ≤ V <sub>SHORT</sub>                                         | 20   | 30  | 40  | mA   |

| T <sub>CF</sub>         | Thermal regulation threshold                            | Charge current begins to taper down                                             |      | 120 |     | °C   |

| T <sub>32S</sub>        | Time constant for the 32-second timer                   | 32 second mode                                                                  |      | 32  |     | s    |

| WLED VOL                | TAGE AND CURRENT CONTROL                                |                                                                                 |      |     |     |      |

| V <sub>REF</sub>        | Voltage feedback regulation voltage                     |                                                                                 | 198  | 203 | 208 | mV   |

|                         | Voltage feedback regulation voltage                     | V <sub>FB</sub> [4:0] = 01110 (V <sub>FB</sub> = 25%)                           | 47   | 50  | 53  | \/   |

| $V_{REF\_PWM}$          | under brightness control                                | V <sub>FB</sub> [4:0] = 01110 (V <sub>FB</sub> = 10%)                           | 17   | 20  | 23  | mV   |

| f <sub>CTRL</sub>       | PWM dimming frequency                                   |                                                                                 | 1    |     | 100 | kHz  |

| t <sub>CNTRL, MIN</sub> | Minimum on-time for PWM dimming pulse                   |                                                                                 | 2.2  |     |     | μs   |

| I <sub>FB</sub>         | Voltage feedback input bias current                     | V <sub>FB</sub> = 200 mV                                                        |      |     | 1   | μΑ   |

| f <sub>PWM</sub>        | PWM frequency, WLED boost                               |                                                                                 |      | 600 |     | kHz  |

| D <sub>max</sub>        | Maximum duty cycle                                      | V <sub>FB</sub> = 100 mV                                                        | 90%  | 93% |     |      |

| t <sub>min_on</sub>     | Minimum 0N pulse width                                  |                                                                                 |      | 40  |     | ns   |

| L                       | Inductor                                                |                                                                                 | 10   |     | 22  | μH   |

| C <sub>OUT</sub>        | Output capacitor                                        |                                                                                 | 0.47 |     | 10  | μF   |

|                         | VER SWIITCH                                             |                                                                                 |      |     | •   |      |

| R <sub>DS(on)</sub>     | N-channel MOSFET on-resistance                          | V <sub>SYS</sub> = 3.6 V                                                        |      | 300 | 600 | mΩ   |

| I <sub>LN_NFET</sub>    | N-channel leakage current                               | V <sub>SWL</sub> = 30 V, T <sub>A</sub> = 25°C                                  |      |     | 1   | μΑ   |

| WLED PRO                | TECTION                                                 |                                                                                 |      |     |     |      |

|                         | Under Voltage Lock Out (VSYS pin)                       | V <sub>SYS</sub> falling                                                        |      | 2.2 | 2.5 | V    |

| $V_{UVLO}$              | UVLO hysteresis                                         |                                                                                 |      | 70  |     | mV   |

| V <sub>OVP</sub>        | Overvoltage Protection threshold                        |                                                                                 | 35   | 37  | 39  | V    |

| I <sub>LIM</sub>        | N-Channel MOSFET current limit                          | D = D <sub>max</sub>                                                            | 560  | 700 | 840 | mA   |

| I <sub>LIM_Start</sub>  | Startup current limit                                   | D = D <sub>max</sub>                                                            |      | 400 |     | mA   |

| t <sub>HALF_LIM</sub>   | Time step for half current limit                        |                                                                                 |      | 5   |     | ms   |

| t <sub>REF</sub>        | V <sub>REF</sub> filter time constant                   |                                                                                 |      | 180 |     | μs   |

| t <sub>step</sub>       | V <sub>REF</sub> ramp up time                           |                                                                                 |      | 213 |     | μs   |

|                         | SHUNT MONITOR                                           |                                                                                 |      |     | *   |      |

| V <sub>CM</sub>         | Common-mode input range                                 | V <sub>CSIN</sub> = V <sub>CSOUT</sub>                                          | -0.3 |     | 7   | V    |

| CMR                     | Common-mode rejection                                   | V <sub>CSIN</sub> = 2.7 V to 5 V, V <sub>CSIN</sub> - V <sub>CSOUT</sub> = 0 mV | 100  |     |     | dB   |

|                         | 0"                                                      | T <sub>A</sub> = 0°C to 60°C                                                    | -75  |     | 75  | .,   |

| $V_{OS, CSM}$           | Offset-voltage, referred to input                       | T <sub>A</sub> = -20°C to 85°C                                                  | -85  |     | 85  | μV   |

| 0                       | Gain                                                    |                                                                                 |      | 25  |     | V/V  |

| G                       | Gain error                                              |                                                                                 | -1%  |     | 1%  |      |

| V <sub>SHNT</sub>       | Swing to positive power supply rail (V <sub>SYS</sub> ) | V <sub>SYS</sub> - V <sub>SHNT</sub>                                            | 100  |     |     | mV   |

| OFFICE                  | Swing to GND                                            | V <sub>SHNT</sub> - V <sub>GND</sub>                                            | 100  |     |     |      |

| GBW                     | Bandwidth                                               | C <sub>LOAD</sub> = 10 pF                                                       |      | 9   |     | kHz  |

| I <sub>VZERO</sub>      | VZERO bias current                                      | T <sub>A</sub> = -20°C to 85°C                                                  |      |     | 10  | nA   |

| $V_{\sf ZERO}$          | Swing to positive power supply rail (V <sub>SYS</sub> ) | V <sub>SYS</sub> – V <sub>ZERO</sub>                                            | 1.5  |     |     | V    |

| ZLINO                   | Swing to GND                                            | V <sub>ZERO</sub> - V <sub>GND</sub>                                            | 0.7  |     |     | -    |

|                         | Undervoltage lockout (VSYS pin)                         | V <sub>SYS</sub> falling                                                        |      | 2.2 | 2.5 | V    |

| $V_{UVLO}$              | UVLO hysteresis                                         |                                                                                 |      | 70  |     | mV   |

VBAT = 3.6 V  $\pm$ 5%, T<sub>J</sub> = 27°C (unless otherwise noted)

|                      | PARAMETER                          | TEST CONDITIONS                                | MIN  | TYP | MAX  | UNIT |  |

|----------------------|------------------------------------|------------------------------------------------|------|-----|------|------|--|

| LDO                  |                                    |                                                | '    |     |      |      |  |

| $V_{LDO}$            | LDO Output Voltage                 | VIN = 5.5V                                     | 4.8  | 4.9 | 5    | V    |  |

|                      | PSRR                               | f = 100 Hz, CLDO = 1.0 μF                      |      | 60  |      | dB   |  |

| I <sub>LDO</sub>     | Maximum LDO Output Current         |                                                | 60   |     |      | mA   |  |

| $V_{DO}$             | Dropout Voltage                    | VIN = 4.5 V, ILDO = 50 mA                      |      | 100 | 250  | mV   |  |

| D+/D- DETI           | ECTION                             |                                                | 1    |     | ,    |      |  |

|                      | D+ voltage source                  |                                                | 0.5  | 0.6 | 0.7  | V    |  |

| $V_{DP\_SCR}$        | D+ voltage source output current   |                                                | 250  |     |      | μΑ   |  |

| I <sub>DM_SINK</sub> | D- current sink                    |                                                | 50   | 100 | 150  | μΑ   |  |

| 0                    | Input capacitance                  | DM pin, switch open                            |      | 4.5 | 5    | pF   |  |

| C <sub>I</sub>       |                                    | DP pin, switch open                            |      | 4.5 | 5    |      |  |

|                      | Input leakage                      | DM pin, switch open                            | -1   |     | 1    | μΑ   |  |

| I <sub>I</sub>       |                                    | DP pin, switch open                            | -1   |     | 1    |      |  |

| $V_{DP\_LOW}$        | DP low comparator threshold        |                                                | 0.8  |     |      | V    |  |

| V <sub>DM_HIGH</sub> | DM high comparator threshold       |                                                | 0.8  |     |      | V    |  |

| $V_{DM\_LOW}$        | DM low comparator threshold        |                                                |      |     | 475  | mV   |  |

|                      | ELS AND TIMING CHARTERISTICS       | (SCL, SDA, CTRL, INT)                          | 1    |     | •    |      |  |

|                      | Output low threshold level         | I <sub>O</sub> = 3 mA, sink current (SDA, INT) |      |     | 0.4  |      |  |

| $V_{OL}$             | Input low threshold level          |                                                |      |     | 0.4  | V    |  |

|                      | Input high threshold level         |                                                | 1.2  |     |      |      |  |

| I <sub>(bias)</sub>  | Input bias current (SCL, SDA, INT) | V <sub>IO</sub> = 1.8 V                        |      |     | 1    | μΑ   |  |

| f <sub>SCL</sub>     | SCL clock frequency                |                                                |      |     | 400  | kHz  |  |

| R <sub>CTRL</sub>    | CTRL pulldown resistor             |                                                | 400  | 800 | 1600 | kΩ   |  |

| t <sub>OFF</sub>     | CTRL pulse width to shutdown       | CTRL high to low                               | 2.5  |     |      | ms   |  |

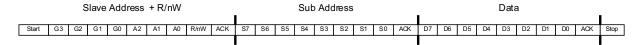

|                      | 7-bit slave address 1101 010       |                                                |      |     |      |      |  |

| OSCILLAT             | OR                                 |                                                | 1    |     | •    |      |  |

| fosc                 | Oscillator frequency               |                                                |      | 3   |      | MHz  |  |

|                      | Frequency accuracy                 | $T_A = -40$ °C to 85°C                         | -10% |     | 10%  |      |  |

| THERMAL              | SHUTDOWN                           |                                                |      |     |      |      |  |

| T <sub>SHTDWN</sub>  | Thermal trip point                 |                                                |      | 165 |      | 20   |  |

|                      | Thermal hysteresis                 |                                                |      | 10  |      | °C   |  |

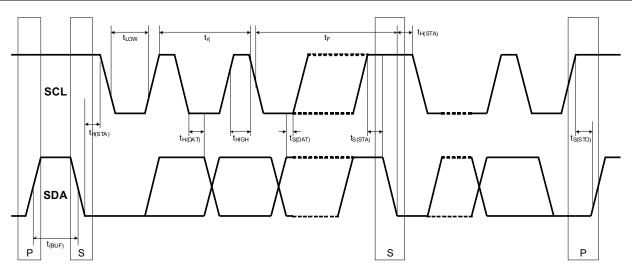

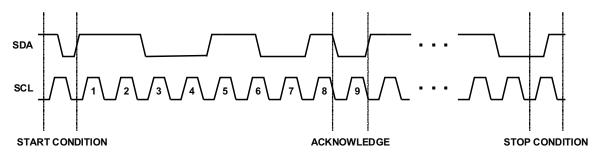

# 6.6 Data Transmission Timing

$V_{BAT} = 3.6 \pm 5\%$ ,  $T_A = 25$  °C,  $C_L = 100$  pF (unless otherwise noted)

|                     |                                                |               | MIN | NOM MAX | UNIT |

|---------------------|------------------------------------------------|---------------|-----|---------|------|

| f <sub>(SCL)</sub>  | Serial clock frequency                         | Standard mode |     | 100     | KHz  |

|                     |                                                | Fast mode     |     | 400     |      |

| t <sub>(BUF)</sub>  | Bus free time between stop and start condition | SCL = 100 kHz | 4.7 |         | μs   |

|                     |                                                | SCL = 400 kHz | 1.3 |         |      |

| t <sub>(SP)</sub>   | Tolerable spike width on bus                   | SCL = 100 kHz |     | 50      | ns   |

|                     |                                                | SCL = 400 kHz |     |         |      |

|                     | SCL low time                                   | SCL = 100 kHz | 4.7 |         | μs   |

| $t_{LOW}$           |                                                | SCL = 400 kHz | 1.3 |         |      |

|                     | 0011111                                        | SCL = 100 kHz | 4   |         | μs   |

| t <sub>HIGH</sub>   | SCL high time                                  | SCL = 400 kHz | 0.6 |         |      |

| t <sub>S(DAT)</sub> | SDA → SCL setup time                           | SCL = 100 kHz | 250 |         | ns   |

|                     |                                                | SCL = 400 kHz | 100 |         |      |

| t <sub>S(STA)</sub> | Start condition setup time                     | SCL = 100 kHz | 4.7 |         | μs   |

|                     |                                                | SCL = 400 kHz | 0.6 |         |      |

| t <sub>S(STO)</sub> | Stop condition setup time                      | SCL = 100 kHz | 4   |         | μs   |

|                     |                                                | SCL = 400 kHz | 0.6 |         |      |

| t <sub>H(DAT)</sub> | SDA → SCL hold time                            | SCL = 100 kHz | 0   | 3.45    | μs   |

|                     |                                                | SCL = 400 kHz | 0   | 0.9     |      |

| t <sub>H(STA)</sub> | Start condition hold time                      | SCL = 100 kHz | 4   |         | μs   |

|                     |                                                | SCL = 400 kHz | 0.6 |         |      |

|                     | Rise time of SCL Signal                        | SCL = 100 kHz |     | 1000    | ns   |

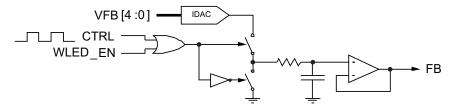

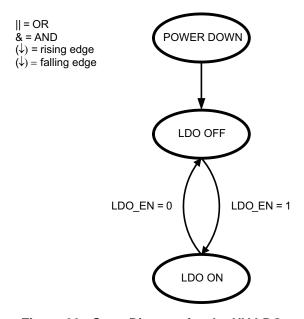

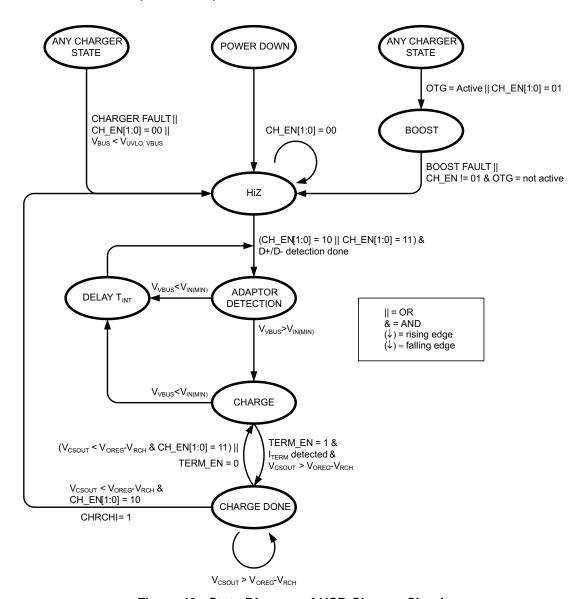

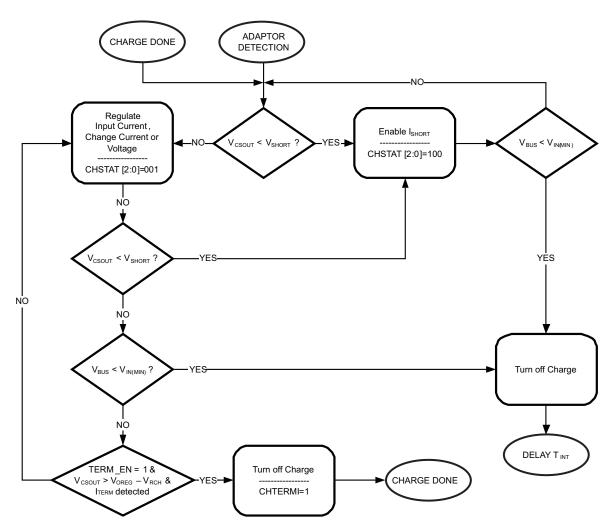

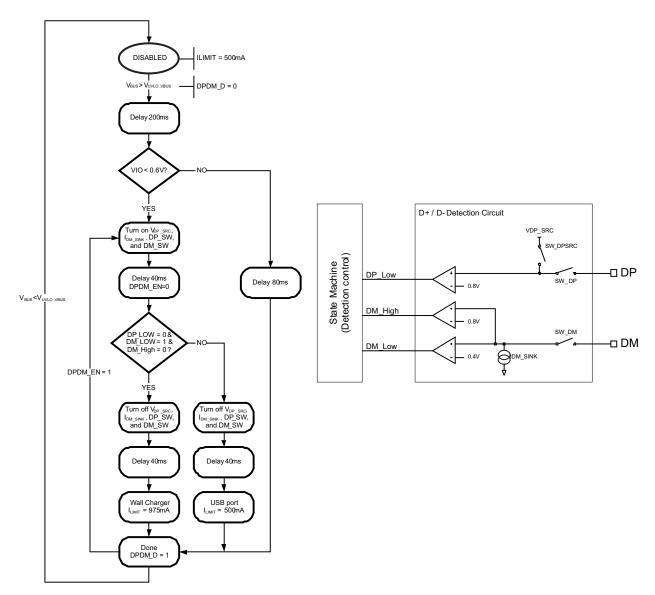

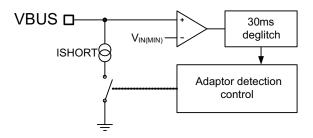

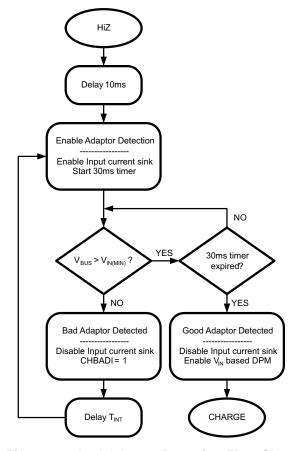

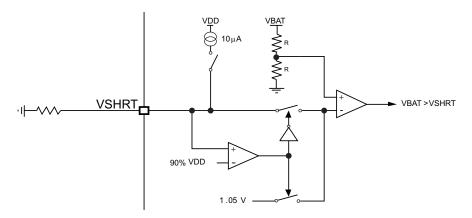

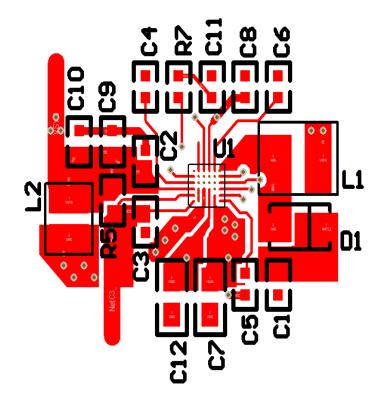

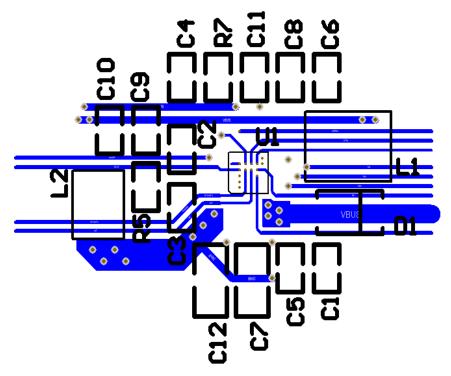

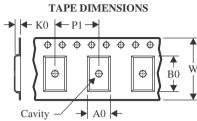

| $t_{r(SCL)}$        |                                                | SCL = 400 kHz |     | 300     |      |