# LM4940 Boomer® Audio Power Amplifier Series 6W Stereo Audio Power Amplifier

Check for Samples: LM4940

# **FEATURES**

- Click and Pop Circuitry Eliminates Noise During Turn-On and Turn-Off Transitions

- Low Current, Active-Low Shutdown Mode

- Low Quiescent Current

- Stereo 6W Output, R<sub>L</sub> = 4Ω

- Short Circuit Protection

- Unity-Gain Stable

- External Gain Configuration Capability

### **APPLICATIONS**

- Flat Panel Monitors

- Flat Panel TVs

- Computer Sound Cards

#### **KEY SPECIFICATIONS**

- Quiscent Power Supply Current: 40mA (max) (SE)

- P<sub>OUT</sub> V<sub>DD</sub> = 14.4V, R<sub>L</sub> = 4Ω, 10% THD+N: 6 W (typ)

- Shutdown Current: 40µA (typ)

# **DESCRIPTION**

The LM4940 is a dual audio power amplifier primarily designed for demanding applications in flat panel monitors and TVs. It is capable of delivering 6 watts per channel to a  $4\Omega$  load with less than 10% THD+N while operating on a 14.4V<sub>DC</sub> power supply.

Boomer<sup>™</sup> audio power amplifiers were designed specifically to provide high quality output power with a minimal amount of external components. The LM4940 does not require bootstrap capacitors or snubber circuits. Therefore, it is ideally suited for display applications requiring high power and minimal size.

The LM4940 features a low-power consumption active-low shutdown mode. Additionally, the LM4940 features an internal thermal shutdown protection mechanism along with short circuit protection.

The LM4940 contains advanced pop and click circuitry that eliminates noises which would otherwise occur during turn-on and turn-off transitions.

The LM4940 is a unity-gain stable and can be configured by external gain-setting resistors.

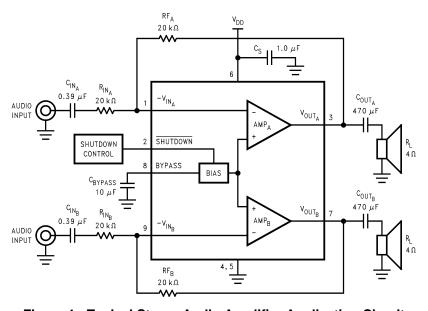

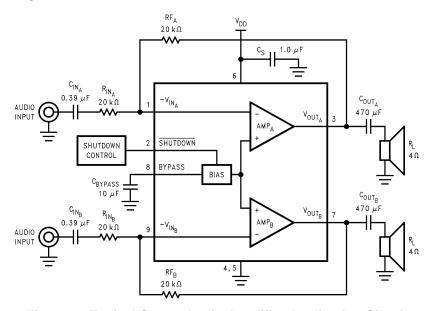

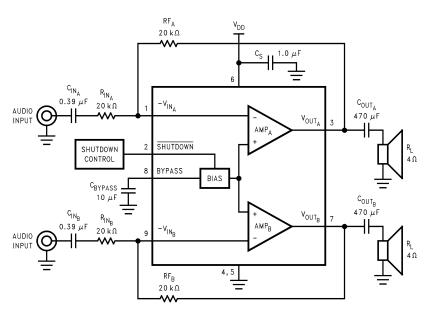

#### TYPICAL APPLICATION

Figure 1. Typical Stereo Audio Amplifier Application Circuit

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

Boomer is a trademark of Texas Instruments, Inc.

All other trademarks are the property of their respective owners.

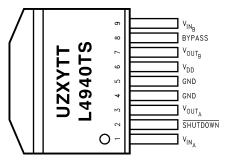

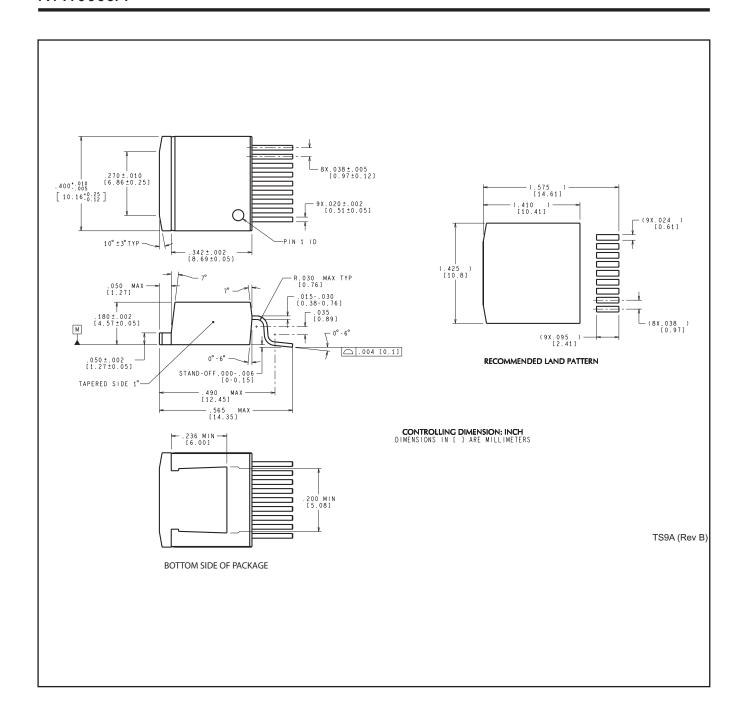

### **CONNECTION DIAGRAM**

U = Wafer Fab Code, Z = Assembly Plant Code, XY = Date Code, TT = Die Traceability

Plastic Package, DDPAK Top View See Package Number KTW

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

# ABSOLUTE MAXIMUM RATINGS(1)(2)(3)

| Supply Voltage (pin 6, referenced to GND | pins 4 and 5)                        | 18.0V                           |  |  |  |

|------------------------------------------|--------------------------------------|---------------------------------|--|--|--|

| Storage Temperature                      | −65°C to +150°C                      |                                 |  |  |  |

| Input Voltage                            | Pins 3 and 7                         | -0.3V to V <sub>DD</sub> + 0.3V |  |  |  |

|                                          | Pins 1, 2, 8, and 9                  | -0.3V to 9.5V                   |  |  |  |

| Power Dissipation (4)                    |                                      | Internally limited              |  |  |  |

| ESD Susceptibility <sup>(5)</sup>        |                                      | 2000V                           |  |  |  |

| ESD Susceptibility <sup>(6)</sup>        |                                      | 200V                            |  |  |  |

| Junction Temperature                     |                                      | 150°C                           |  |  |  |

| Thermal Resistance                       | θ <sub>JC</sub> (KTW)                | 4°C/W                           |  |  |  |

|                                          | $\theta_{JA}$ (KTW) $^{(4)}$         | 20°C/W                          |  |  |  |

|                                          | $\theta_{JC}$ (NEC)                  | 4°C/W                           |  |  |  |

|                                          | θ <sub>JA</sub> (NEC) <sup>(4)</sup> | 20°C/W                          |  |  |  |

- (1) All voltages are measured with respect to the GND pin, unless otherwise specified.

- (2) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is functional, but do not ensure specific performance limits. Electrical Characteristics state DC and AC electrical specifications under particular test conditions which ensure performance limits. This assumes that the device is within the Operating Ratings. Specifications are not ensured for parameters where no limit is given, however, the typical value is a good indication of device performance.

- (3) If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office/ Distributors for availability and specifications.

- (4) The maximum power dissipation must be derated at elevated temperatures and is dictated by T<sub>JMAX</sub>, θ<sub>JA</sub>, and the ambient temperature, T<sub>A</sub>. The maximum allowable power dissipation is P<sub>DMAX</sub> = (T<sub>JMAX</sub> T<sub>A</sub>) / θ<sub>JA</sub> or the given in Absolute Maximum Ratings, whichever is lower. For the LM4940 typical application (shown in Figure 1) with V<sub>DD</sub> = 12V, R<sub>L</sub> = 4Ω stereo operation the total power dissipation is 3.65W. θ<sub>JA</sub> = 20°C/W for both DDPAK and TO–220 packages mounted to 16in² heatsink surface area.

- (5) Human body model, 100pF discharged through a  $1.5k\Omega$  resistor.

- (6) Machine Model, 220pF-240pF discharged through all pins.

#### **OPERATING RATINGS**

| Temperature Range $(T_{MIN} \le T_A \le T_{MAX})$ | -40°C ≤ T <sub>A</sub> ≤ 85°C |

|---------------------------------------------------|-------------------------------|

| Supply Voltage                                    | 10V ≤ V <sub>DD</sub> ≤ 16V   |

Product Folder Links: LM4940

# ELECTRICAL CHARACTERISTICS $V_{DD} = 12V^{(1)(2)}$

The following specifications apply for  $V_{DD}$  = 12V,  $A_V$  = 10,  $R_L$  = 4 $\Omega$ , f = 1kHz unless otherwise specified. Limits apply for  $T_A$  = 25°C.

|                    |                                   | 0 100                                                             | LM4                    | LM4940                    |                    |  |  |

|--------------------|-----------------------------------|-------------------------------------------------------------------|------------------------|---------------------------|--------------------|--|--|

| Symbol             | Parameter                         | Conditions                                                        | Typical <sup>(3)</sup> | Limit <sup>(4)(5)</sup>   | Units<br>(Limits)  |  |  |

| I <sub>DD</sub>    | Quiescent Power Supply Current    | V <sub>IN</sub> = 0V, I <sub>O</sub> = 0A, No Load                | 16                     | 40                        | mA (max)           |  |  |

| I <sub>SD</sub>    | Shutdown Current                  | V <sub>SHUTDOWN</sub> = GND <sup>(6)</sup>                        | 40                     | 100                       | μA (max)           |  |  |

| V <sub>SDIH</sub>  | Shutdown Voltage Input High       |                                                                   |                        | 2.0<br>V <sub>DD</sub> /2 | V (min)<br>V (max) |  |  |

| V <sub>SDIL</sub>  | Shutdown Voltage Input Low        |                                                                   |                        | 0.4                       | V (max)            |  |  |

|                    |                                   | Single Channel                                                    |                        |                           |                    |  |  |

| <b>D</b>           | 0                                 | THD+N = 1%                                                        | 3.1                    | 2.8                       | )A/ ('-)           |  |  |

| Po                 | Output Power                      | THD+N = 10%                                                       | 4.2                    |                           | W (min)            |  |  |

|                    |                                   | V <sub>DD</sub> = 14.4V, THD+N = 10%                              | 6.0                    |                           | 1                  |  |  |

| THD+N              | Total Harmomic Distortion + Noise | $P_{O} = 1W_{RMS}, A_{V} = 10, f = 1kHz$                          | 0.15                   |                           | %                  |  |  |

| $\epsilon_{ m OS}$ | Output Noise                      | A-Weighted Filter, V <sub>IN</sub> = 0V,<br>Input Referred        | 10                     |                           | μV                 |  |  |

| X <sub>TALK</sub>  | Channel Separation                | P <sub>O</sub> = 1W                                               | 70                     |                           | dB                 |  |  |

| PSRR               | Power Supply Rejection Ratio      | $V_{RIPPLE} = 200 \text{mV}_{p-p}$<br>$f_{RIPPLE} = 1 \text{kHz}$ | 56                     |                           | dB                 |  |  |

- (1) All voltages are measured with respect to the GND pin, unless otherwise specified.

- Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is functional, but do not ensure specific performance limits. Electrical Characteristics state DC and AC electrical specifications under particular test conditions which ensure performance limits. This assumes that the device is within the Operating Ratings. Specifications are not ensured for parameters where no limit is given, however, the typical value is a good indication of device performance.

- Typicals are measured at 25°C and represent the parametric norm.

- Limits are specified to AOQL (Average Outgoing Quality Level).

- (5)

- Datasheet min/max specification limits are specified by design, test, or statistical analysis.

Shutdown current is measured in a normal room environment. The Shutdown pin should be driven as close as possible to GND for minimum shutdown current.

# TYPICAL APPLICATION

Figure 2. Typical Stereo Audio Amplifier Application Circuit

# **EXTERNAL COMPONENTS DESCRIPTION**

Refer to Figure 1.

| Con | nponents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Functional Description                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 1.  | This is the inverting input resistance that, along with $R_F$ , sets the closed-loop gain. Input resistance $R_{IN}$ capacitance $C_{IN}$ form a high pass filter. The filter's cutoff frequency is $R_{IN}$ frequency is $R_{IN}$ cutoff frequency is |                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| 2.  | C <sub>IN</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | This is the input coupling capacitor. It blocks DC voltage at the amplifier's inverting input. $C_{IN}$ and $R_{IN}$ create a highpass filter. The filter's cutoff frequency is $f_C = 1/(2\pi R_{IN}C_{IN})$ . Refer to the SELECTING EXTERNAL COMPONENTS section for an explanation of determining $C_{IN}$ 's value.                                     |  |  |  |  |  |

| 3.  | R <sub>F</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | This is the feedback resistance that, along with R <sub>i</sub> , sets closed-loop gain.                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| 4.  | Cs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | The supply bypass capacitor. Refer to the POWER SUPPLY BYPASSING section for information about properly placing, and selecting the value of, this capacitor.                                                                                                                                                                                                |  |  |  |  |  |

| 5.  | C <sub>BYPASS</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | This capacitor filters the half-supply voltage present on the BYPASS pin. Refer to the SELECTING EXTERNAL COMPONENTS for information about properly placing, and selecting the value of, this capacitor.                                                                                                                                                    |  |  |  |  |  |

| 6.  | C <sub>OUT</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | This is the output coupling capacitor. It blocks the nominal $V_{DD}/2$ voltage present at the output and prevents it from reaching the load. $C_{OUT}$ and $R_L$ form a high pass filter whose cutoff frequency is $f_C = 1/(2\pi R_L C_{OUT})$ . Refer to the SELECTING EXTERNAL COMPONENTS section for an explanation of determining $C_{OUT}$ 's value. |  |  |  |  |  |

Product Folder Links: LM4940

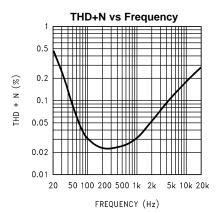

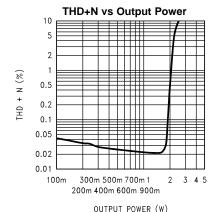

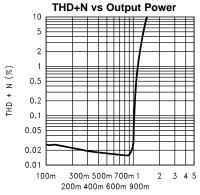

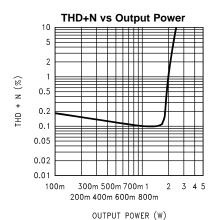

#### TYPICAL PERFORMANCE CHARACTERISTICS

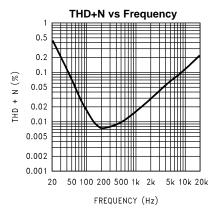

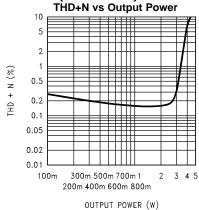

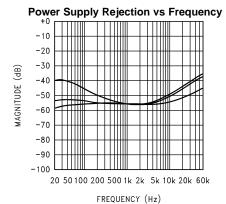

$V_{DD}$  = 12V,  $R_L$  = 4 $\Omega$ , SE operation, both channels driven and loaded (average shown)  $P_{OUT}$  = 1W,  $A_V$  = 1

Figure 3.

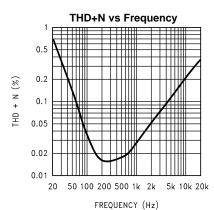

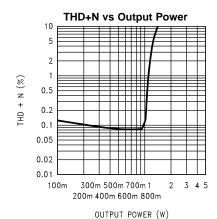

$V_{DD}$  = 12V,  $R_L$  = 8 $\Omega$ , SE operation, both channels driven and loaded (average shown),  $P_{OUT}$  = 1W,  $A_V$  = 1

Figure 5.

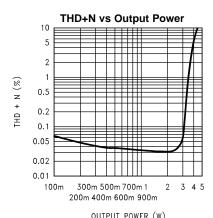

$V_{DD}$  = 12V,  $R_L$  = 4 $\Omega$ , SE operation,  $A_V$  = 1 single channel driven/single channel measured,  $f_{IN}$  = 1kHz

Figure 7.

$V_{DD}$  = 12V,  $R_L$  = 4 $\Omega$ , SE operation, both channels driven and loaded (average shown),  $P_{OUT}$  = 2.5W,  $A_V$  = 1

Figure 4.

$V_{DD}=14.4V,\ R_L=4\Omega,\ SE\ operation,\ A_V=1$  single channel driven/single channel measured,  $f_{IN}=1kHz$

Figure 6.

$V_{DD}$  = 12V,  $R_L$  = 8 $\Omega$ , SE operation,  $A_V$  = 1 single channel driven/single channel measured,  $f_{IN}$  = 1kHz

Figure 8.

# TYPICAL PERFORMANCE CHARACTERISTICS (continued)

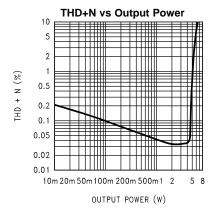

$V_{DD}$  = 12V,  $R_L$  = 16 $\Omega$ , SE operation,  $A_V$  = 1 single channel driven/single channel measured,  $f_{IN}$  = 1kHz

Figure 9.

OUTPUT POWER (W)

$V_{DD}=12V,~R_L=8\Omega,~SE~operation,~A_V=10 \\$  single channel driven/single channel measured,  $f_{IN}=1kHz$

Figure 11.

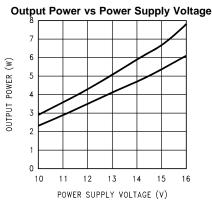

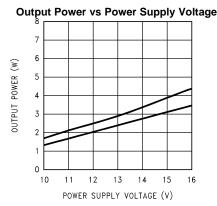

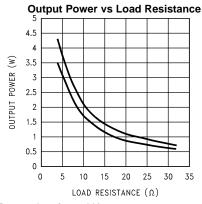

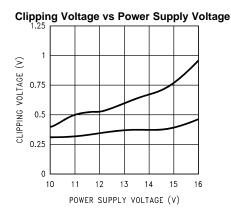

$R_L=4\Omega,$  SE operation,  $f_{IN}=1kHz,$  both channels driven and loaded (average shown), at (from top to bottom at 12V): THD+N = 10%, THD+N = 1%

Figure 13.

$V_{DD}$  = 12V,  $R_L$  = 4 $\Omega$ , SE operation,  $A_V$  = 10 single channel driven/single channel measured,  $f_{IN}$  = 1kHz

Figure 10.

$V_{DD}$  = 12V,  $R_L$  = 16 $\Omega$ , SE operation,  $A_V$  = 10 single channel driven/single channel measured,  $f_{IN}$  = 1kHz

Figure 12.

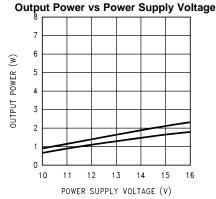

$R_L=8\Omega,$  SE operation,  $f_{IN}=1kHz,$  both channels driven and loaded (average shown), at (from top to bottom at 12V): THD+N = 10%, THD+N = 1%

Figure 14.

# TYPICAL PERFORMANCE CHARACTERISTICS (continued)

$R_L=16\Omega,$  SE operation,  $f_{\text{IN}}=1\text{kHz},$  both channels driven and loaded (average shown), at (from top to bottom at 12V): THD+N = 10%, THD+N = 1%

Figure 15.

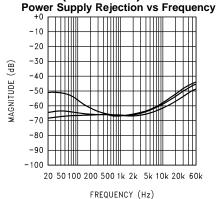

$$\begin{split} &V_{DD}=12V,\,R_L=8\Omega,\,SE\,\,\text{operation},\,V_{RIPPLE}=200\text{mV}_{p\text{-}p},\\ &A_V=10,\,\text{at}\,\,(\text{from top to bottom at 60Hz});\\ &C_{BYPASS}=1\mu\text{F},\,C_{BYPASS}=4.7\mu\text{F},\,C_{BYPASS}=10\mu\text{F}\\ &\textbf{Figure 17}. \end{split}$$

$V_{DD}$  = 12V, SE operation,  $f_{IN}$  = 1kHz, both channels driven and loaded, at (from top to bottom at 15 $\Omega$ ): THD+N = 10%, THD+N = 1%

Figure 19.

$$\begin{split} &V_{DD}=12V,\ R_L=8\Omega,\ \text{SE operation},\\ &V_{R|PPLE}=200\text{mV}_{p\text{-}p},\ \text{at (from top to bottom at 60Hz):}\\ &C_{BYPASS}=1\mu\text{F},\ C_{BYPASS}=4.7\mu\text{F},\ C_{BYPASS}=10\mu\text{F} \end{split}$$

Figure 16.

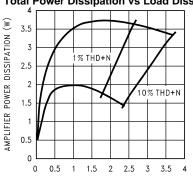

AMPLIFIER LOAD DISSIPATION PER CHANNEL (W)

$$\begin{split} &V_{DD}=12V,\,\text{SE operation,}\,\,f_{IN}=1\text{kHz,}\\ &\text{at (from top to bottom at 1W):}\\ &R_L=4\Omega,\,R_L=8\Omega \end{split}$$

Figure 18.

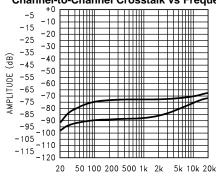

# Channel-to-Channel Crosstalk vs Frequency

$$\begin{split} &V_{DD}=12V,~R_L=4\Omega,~P_{OUT}=1W,~SE~operation,\\ &at~(from~top~to~bottom~at~1kHz):~V_{INB}~driven,\\ &V_{OUTA}~measured;~V_{INA}~driven,~V_{OUTB}~measured \end{split}$$

Figure 20.

FREQUENCY (Hz)

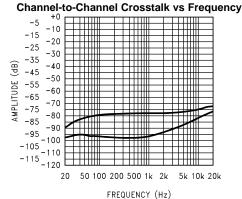

# TYPICAL PERFORMANCE CHARACTERISTICS (continued)

$$\begin{split} &V_{DD} = 12 V, \, R_L = 8 \Omega, \, P_{OUT} = 1 W, \, SE \, \, operation, \\ &at \, (from \, top \, to \, bottom \, at \, 1kHz): \, V_{INB} \, \, driven, \\ &V_{OUTA} \, measured; \, V_{INA} \, \, driven, \, \, V_{OUTB} \, measured \\ & \textbf{Figure 21.} \end{split}$$

$R_L = 4\Omega$ , SE operation  $V_{IN} = 0V$ ,  $R_{SOURCE} = 50\Omega$

Figure 22.

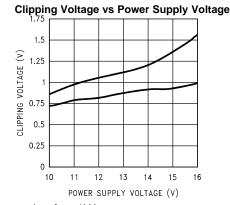

$R_L=4\Omega$ , SE operation,  $f_{\text{IN}}=1\text{kHz}$  both channels driven and loaded, at (from top to bottom at 13V): negative signal swing, positive signal swing Figure 23.

$R_L = 8\Omega$ , SE operation,  $f_{\text{IN}} = 1 \text{kHz}$  both channels driven and loaded, at (from top to bottom at 13V): negative signal swing, positive signal swing Figure 24.

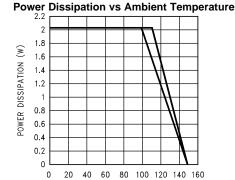

$V_{DD} = 12V$ ,  $R_L = 8\Omega$  (SE),  $f_{IN} = 1kHz$ , (from top to bottom at 120°C):  $16in^2$  copper plane heatsink area,  $8in^2$  copper plane heatsink area

Figure 25.

AMBIENT TEMPERATURE (°C)

Product Folder Links: LM4940

#### APPLICATION INFORMATION

Figure 26. Typical LM4940 Stereo Amplifier Application Circuit

#### HIGH VOLTAGE BOOMER WITH INCREASED OUTPUT POWER

Unlike previous 5V Boomer amplifiers, the LM4940 is designed to operate over a power supply voltages range of 10V to 15V. Operating on a 12V power supply, the LM4940 will deliver 3.1W per channel into  $4\Omega$  loads with no more than 1% THD+N.

#### POWER DISSIPATION

Power dissipation is a major concern when designing a successful single-ended amplifier. Equation 1 states the maximum power dissipation point for a single-ended amplifier operating at a given supply voltage and driving a specified output load.

$$P_{DMAX-SF} = (V_{DD})^2 I (2\pi^2 R_1): Single Ended$$

(1)

The LM4940's dissipation is twice the value given by Equation 1 when driving two SE loads. For a 12V supply and two  $8\Omega$  SE loads, the LM4940's dissipation is 1.82W.

The maximum power dissipation point (twice the value given by Equation 1 must not exceed the power dissipation given by Equation 2:

$$P_{DMAX}' = (T_{JMAX} - T_A) / \theta_{JA}$$

(2)

The LM4940's  $T_{JMAX} = 150^{\circ}\text{C}$ . In the KTW package, the LM4940's  $\theta_{JA}$  is 20°C/W when the metal tab is soldered to a copper plane of at least  $16\text{in}^2$ . This plane can be split between the top and bottom layers of a two-sided PCB. Connect the two layers together under the tab with a 5x5 array of vias. For the NEC package, use an external heatsink with a thermal impedance that is less than 20°C/W. At any given ambient temperature  $T_A$ , use Equation 3 to find the maximum internal power dissipation supported by the IC packaging. Rearranging Equation 3 and substituting  $P_{DMAX}$  for  $P_{DMAX}$  results in Equation 4. This equation gives the maximum ambient temperature that still allows maximum stereo power dissipation without violating the LM4940's maximum junction temperature.

$$T_{A} = T_{JMAX} - P_{DMAX-SE}\theta_{JA}$$

(3)

For a typical application with a 12V power supply and two  $4\Omega$  SE loads, the maximum ambient temperature that allows maximum stereo power dissipation without exceeding the maximum junction temperature is approximately 113°C for the KTW package.

$$T_{\text{JMAX}} = P_{\text{DMAX-SE}}\theta_{\text{JA}} + T_{\text{A}} \tag{4}$$

Equation 4 gives the maximum junction temperature T<sub>JMAX</sub>. If the result violates the LM4940's 150°C, reduce the maximum junction temperature by reducing the power supply voltage or increasing the load resistance. Further allowance should be made for increased ambient temperatures.

The above examples assume that a device is operating around the maximum power dissipation point. Since internal power dissipation is a function of output power, higher ambient temperatures are allowed as output power or duty cycle decreases.

If the result of Equation 3 is greater than that of Equation 4, then decrease the supply voltage, increase the load impedance, or reduce the ambient temperature. Further, ensure that speakers rated at a nominal  $4\Omega$  do not fall below  $3\Omega$ . If these measures are insufficient, a heat sink can be added to reduce  $\theta_{JA}$ . The heat sink can be created using additional copper area around the package, with connections to the ground pins, supply pin and amplifier output pins. Refer to the TYPICAL PERFORMANCE CHARACTERISTICS curves for power dissipation information at lower output power levels.

#### **POWER SUPPLY VOLTAGE LIMITS**

Continuous proper operation is ensured by never exceeding the voltage applied to any pin, with respect to ground, as listed in the Absolute Maximum Ratings section.

### **POWER SUPPLY BYPASSING**

As with any power amplifier, proper supply bypassing is critical for low noise performance and high power supply rejection. Applications that employ a voltage regulator typically use a 10µF in parallel with a 0.1µF filter capacitors to stabilize the regulator's output, reduce noise on the supply line, and improve the supply's transient response. However, their presence does not eliminate the need for a local 1.0µF tantalum bypass capacitance connected between the LM4940's supply pins and ground. Do not substitute a ceramic capacitor for the tantalum. Doing so may cause oscillation. Keep the length of leads and traces that connect capacitors between the LM4940's power supply pin and ground as short as possible. Connecting a 10µF capacitor, CBYPASS, between the BYPASS pin and ground improves the internal bias voltage's stability and improves the amplifier's PSRR. The PSRR improvements increase as the bypass pin capacitor value increases. Too large, however, increases turn-on time and can compromise the amplifier's click and pop performance. The selection of bypass capacitor values, especially CBYPASS, depends on desired PSRR requirements, click and pop performance (as explained in the section, SELECTING EXTERNAL COMPONENTS), system cost, and size constraints.

### **MICRO-POWER SHUTDOWN**

The LM4940 features an active-low shutdown mode that disables the amplifier's bias circuitry, reducing the supply current to  $40\mu A$  (typ). Connect SHUTDOWN to a voltage between 2V to  $V_{DD}/2$  for normal operation. Connect SHUTDOWN to GND to disable the device. A voltage that is greater than GND can increase shutdown current.

Product Folder Links: LM4940

#### **SELECTING EXTERNAL COMPONENTS**

#### Input Capacitor Value Selection

Two quantities determine the value of the input coupling capacitor: the lowest audio frequency that requires amplification and desired output transient suppression.

As shown in Figure 26, the input resistor ( $R_{IN}$ ) and the input capacitor ( $C_{IN}$ ) produce a high pass filter cutoff frequency that is found using Equation 5.

$$f_{\rm C} = 1/2\pi R_{\rm i} C_{\rm i} \tag{5}$$

As an example when using a speaker with a low frequency limit of 50Hz,  $C_i$ , using Equation 5 is 0.159 $\mu$ F. The 0.39 $\mu$ F  $C_{INA}$  shown in Figure 26 allows the LM4940 to drive high efficiency, full range speaker whose response extends below 30Hz.

### **Output Coupling Capacitor Value Selection**

The capacitors  $C_{OUTA}$  and  $C_{OUTB}$  that block the  $V_{DD}/2$  output DC bias voltage and couple the output AC signal to the amplifier loads also determine low frequency response. These capacitors, combined with their respective loads create a highpass filter cutoff frequency. The frequency is also given by Equation 5.

Using the same conditions as above, with a  $4\Omega$  speaker,  $C_{OUT}$  is  $820\mu F$  (nearest common valve).

### **Bypass Capacitor Value**

Besides minimizing the input capacitor size, careful consideration should be paid to value of  $C_{\text{BYPASS}}$ , the capacitor connected to the BYPASS pin. Since  $C_{\text{BYPASS}}$  determines how fast the LM4940 settles to quiescent operation, its value is critical when minimizing turn-on pops. The slower the LM4940's outputs ramp to their quiescent DC voltage (nominally  $V_{\text{DD}}/2$ ), the smaller the turn-on pop. Choosing  $C_{\text{BYPASS}}$  equal to  $10\mu\text{F}$  along with a small value of  $C_{\text{IN}}$  (in the range of  $0.1\mu\text{F}$  to  $0.39\mu\text{F}$ ), produces a click-less and pop-less shutdown function. As discussed above, choosing  $C_{\text{IN}}$  no larger than necessary for the desired bandwidth helps minimize clicks and pops.

## **OPTIMIZING CLICK AND POP REDUCTION PERFORMANCE**

The LM4940 contains circuitry that eliminates turn-on and shutdown transients ("clicks and pops"). For this discussion, turn-on refers to either applying the power supply voltage or when the micro-power shutdown mode is deactivated.

As the  $V_{DD}/2$  voltage present at the BYPASS pin ramps to its final value, the LM4940's internal amplifiers are configured as unity gain buffers and are disconnected from the AMP<sub>A</sub> and AMP<sub>B</sub> pins. An internal current source charges the capacitor connected between the BYPASS pin and GND in a controlled manner. Ideally, the input and outputs track the voltage applied to the BYPASS pin. The gain of the internal amplifiers remains unity until the voltage applied to the BYPASS pin.

The gain of the internal amplifiers remains unity until the voltage on the bypass pin reaches  $V_{DD}/2$ . As soon as the voltage on the bypass pin is stable, the device becomes fully operational and the amplifier outputs are reconnected to their respective output pins. Although the BYPASS pin current cannot be modified, changing the size of  $C_{\text{BYPASS}}$  alters the device's turn-on time. Here are some typical turn-on times for various values of  $C_{\text{BYPASS}}$ :

| C <sub>B</sub> (µF) | T <sub>ON</sub> (ms) |

|---------------------|----------------------|

| 1.0                 | 120                  |

| 2.2                 | 120                  |

| 4.7                 | 200                  |

| 10                  | 440                  |

Product Folder Links: LM4940

Copyright © 2003-2013, Texas Instruments Incorporated

In order eliminate "clicks and pops", all capacitors must be discharged before turn-on. Rapidly switching V<sub>DD</sub> may not allow the capacitors to fully discharge, which may cause "clicks and pops".

There is a relationship between the value of  $C_{IN}$  and  $C_{BYPASS}$  that ensures minimum output transient when power is applied or the shutdown mode is deactivated. Best performance is achieved by setting the time constant created by  $C_{IN}$  and  $R_i$  +  $R_f$  to a value less than the turn-on time for a given value of  $C_{BYPASS}$  as shown in the table above.

#### **AUDIO POWER AMPLIFIER DESIGN**

### Audio Amplifier Design: Driving 3W into a 4Ω load

The following are the desired operational parameters:

| Power Output    | 3W <sub>RMS</sub>         |

|-----------------|---------------------------|

| Load Impedance  | 4Ω                        |

| Input Level     | 0.3V <sub>RMS</sub> (max) |

| Input Impedance | 20kΩ                      |

| Bandwidth       | 100Hz-20kHz ± 0.25dB      |

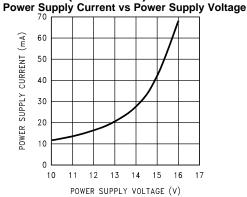

The design begins by specifying the minimum supply voltage necessary to obtain the specified output power. One way to find the minimum supply voltage is to use the Output Power vs Power Supply Voltage curve in the TYPICAL PERFORMANCE CHARACTERISTICS section. Another way, using Equation 6, is to calculate the peak output voltage necessary to achieve the desired output power for a given load impedance. To account for the amplifier's dropout voltage, two additional voltages, based on the Clipping Dropout Voltage vs Power Supply Voltage in the TYPICAL PERFORMANCE CHARACTERISTICS curves, must be added to the result obtained by Equation 6. The result is Equation 7.

$$V_{\text{opeak}} = \sqrt{(2R_{\text{L}}P_{\text{O}})} \tag{6}$$

$$V_{DD} = V_{OLITPEAK} + V_{ODTOP} + V_{ODROT}$$

(7)

The Figure 13 graph for an  $8\Omega$  load indicates a minimum supply voltage of 11.8V. The commonly used 12V supply voltage easily meets this. The additional voltage creates the benefit of headroom, allowing the LM4940 to produce an output power of 3W without clipping or other audible distortion. The choice of supply voltage must also not create a situation that violates of maximum power dissipation as explained above in the POWER DISSIPATION section. After satisfying the LM4940's power dissipation requirements, the minimum differential gain needed to achieve 3W dissipation in a  $4\Omega$  BTL load is found using Equation 8.

$$A_{V} \ge \sqrt{(P_{O}R_{L})}/(V_{IN}) = V_{orms}/V_{inrms}$$

(8)

Thus, a minimum gain of 11.6 allows the LM4940's to reach full output swing and maintain low noise and THD+N performance. For this example, let  $A_V = 12$ . The amplifier's overall BTL gain is set using the input (RIN<sub>A</sub>) and feedback (R) resistors of the first amplifier in the series BTL configuration. Additionally,  $A_{V-BTL}$  is twice the gain set by the first amplifier's  $R_{IN}$  and  $R_f$ . With the desired input impedance set at  $20k\Omega$ , the feedback resistor is found using Equation 9.

$$R_{I}/R_{IN} = A_{V} \tag{9}$$

Product Folder Links: LM4940

The value of  $R_f$  is 240k $\Omega$ . The nominal output power is 3W.

The last step in this design example is setting the amplifier's -3dB frequency bandwidth. To achieve the desired ±0.25dB pass band magnitude variation limit, the low frequency response must extend to at least one-fifth the lower bandwidth limit and the high frequency response must extend to at least five times the upper bandwidth limit. The gain variation for both response limits is 0.17dB, well within the ±0.25dB-desired limit. The results are an

$$f_L = 100Hz / 5 = 20Hz$$

(10)

and

$$f_1 = 20kHz \times 5 = 100kHz$$

(11)

As mentioned in the SELECTING EXTERNAL COMPONENTS section,  $R_{INA}$  and  $C_{INA}$ , as well as  $C_{OUT}$  and  $R_{L}$ , create a highpass filter that sets the amplifier's lower bandpass frequency limit. Find the coupling capacitor's value using Equation 14.

$$C_{IN} = 1/2\pi R_{IN} f_L$$

(12)

The result is

$$1 / (2\pi x 20k\Omega x 20Hz) = 0.398\mu F = C_{IN}$$

(13)

and

$$1/(2\pi \times 4\Omega \times 20Hz) = 1989\mu F = C_{out}$$

(14)

Use a 0.39μF capacitor for C<sub>IN</sub> and a 2000μF capacitor for C<sub>OUT</sub>, the closest standard values.

The product of the desired high frequency cutoff (100kHz in this example) and the differential gain  $A_V$ , determines the upper passband response limit. With  $A_V = 12$  and  $f_H = 100kHz$ , the closed-loop gain bandwidth product (GBWP) is 1.2mHz. This is less than the LM4940's 3.5MHz GBWP. With this margin, the amplifier can be used in designs that require more differential gain while avoiding performance restricting bandwidth limitations.

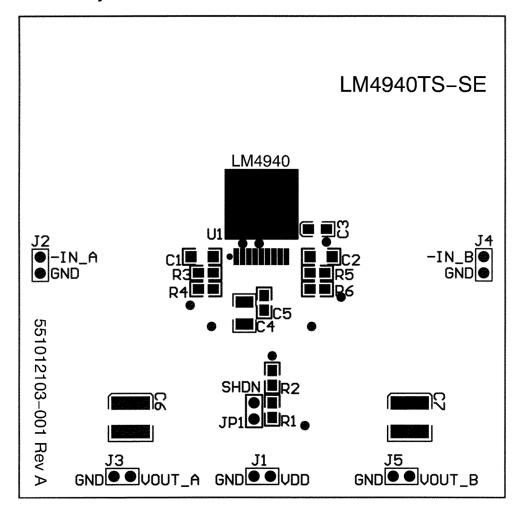

# RECOMMENDED PRINTED CIRCUIT BOARD LAYOUT

Figure 27 through Figure 29 show the recommended two-layer PC board layout that is optimized for the DDPAK-packaged LM4940 and associated external components. This circuit board is designed for use with an external 12V supply and  $4\Omega$  (min) speakers.

This circuit board is easy to use. Apply 12V and ground to the board's  $V_{DD}$  and GND pads, respectively. Connect a speaker between the board's  $OUT_A$  and  $OUT_B$  outputs and their respective GND terminals.

# **Demonstration Board Layout**

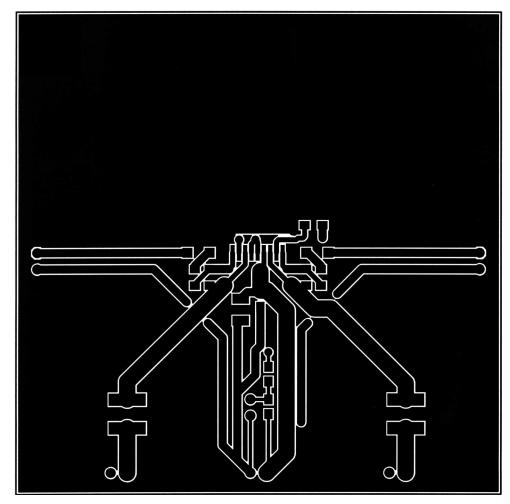

Figure 27. Recommended KTW PCB Layout: Top Silkscreen

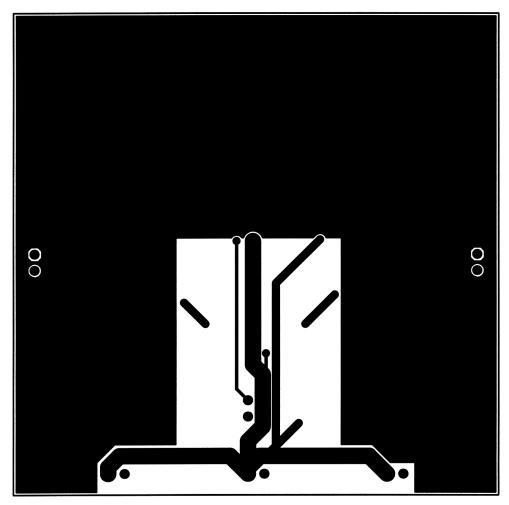

Figure 28. Recommended KTW PCB Layout: Top Layer

Figure 29. Recommended KTW PCB Layout: Bottom Layer

# SNAS219C - OCTOBER 2003-REVISED MAY 2013

# **REVISION HISTORY**

| Changes from Revision B (May 2013) to Revision C |                                                    |   |   |  |  |

|--------------------------------------------------|----------------------------------------------------|---|---|--|--|

| •                                                | Changed layout of National Data Sheet to TI format | 1 | 7 |  |  |

# PACKAGE OPTION ADDENDUM

10-Dec-2020

#### PACKAGING INFORMATION

www.ti.com

| Orderable Device | Status | Package Type     | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan               | Lead finish/<br>Ball material | MSL Peak Temp       | Op Temp (°C) | Device Marking (4/5) | Samples |

|------------------|--------|------------------|--------------------|------|----------------|------------------------|-------------------------------|---------------------|--------------|----------------------|---------|

| LM4940TS/NOPB    | ACTIVE | DDPAK/<br>TO-263 | KTW                | 9    | 45             | RoHS-Exempt & Green    | SN                            | Level-3-245C-168 HR | -40 to 85    | L4940TS              | Samples |

| LM4940TSX/NOPB   | ACTIVE | DDPAK/<br>TO-263 | KTW                | 9    | 500            | RoHS-Exempt<br>& Green | SN                            | Level-3-245C-168 HR | -40 to 85    | L4940TS              | Samples |

(1) The marketing status values are defined as follows:

**ACTIVE:** Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead finish/Ball material Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

10-Dec-2020

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 11-May-2024

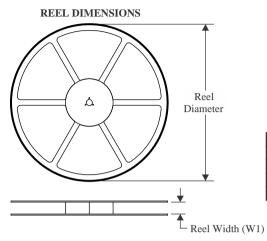

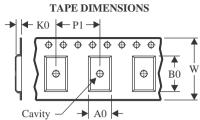

# TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

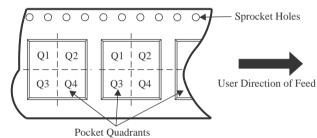

## QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device         | Package<br>Type  | Package<br>Drawing | l . | SPQ | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|----------------|------------------|--------------------|-----|-----|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| LM4940TSX/NOPB | DDPAK/<br>TO-263 | KTW                | 9   | 500 | 330.0                    | 24.4                     | 10.75      | 14.85      | 5.0        | 16.0       | 24.0      | Q2               |

www.ti.com 11-May-2024

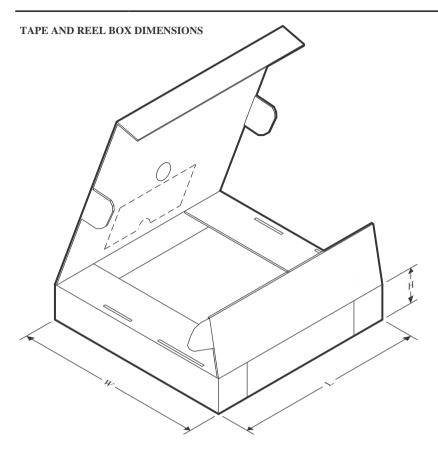

# \*All dimensions are nominal

| Ì | Device         | Device Package Type |     | Pins | SPQ | Length (mm) | Width (mm) | Height (mm) |  |

|---|----------------|---------------------|-----|------|-----|-------------|------------|-------------|--|

| ı | LM4940TSX/NOPB | DDPAK/TO-263        | KTW | 9    | 500 | 356.0       | 356.0      | 45.0        |  |

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 11-May-2024

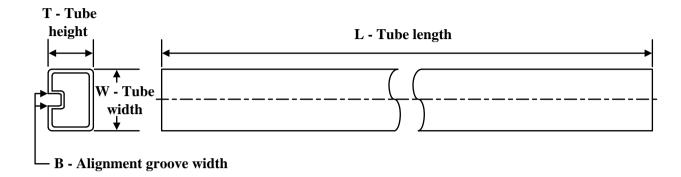

# **TUBE**

## \*All dimensions are nominal

| Device        | Package Name | Package Type | Pins | SPQ | L (mm) | W (mm) | T (µm) | B (mm) |

|---------------|--------------|--------------|------|-----|--------|--------|--------|--------|

| LM4940TS/NOPB | KTW          | TO-263       | 9    | 45  | 502    | 25     | 8204.2 | 9.19   |

# IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2024, Texas Instruments Incorporated