SNLS156E-SEPTEMBER 2003-REVISED APRIL 2013

# DS92LV18 18-Bit Bus LVDS Serializer/Deserializer - 15-66 MHz

Check for Samples: DS92LV18

## **FEATURES**

- 15-66 MHz 18:1/1:18 Serializer/Deserializer (2.376 Gbps Full Duplex Throughput)

- Independent Transmitter and Receiver **Operation with Separate Clock, Enable, and** Power Down Pins

- Hot Plug Protection (Power Up High Impedance) and Synchronization (Receiver Locks to Random Data)

- Wide ±5% Reference Clock Frequency **Tolerance for Easy System Design Using Locally-Generated Clocks**

- Line and Local Loopback Modes

- **Robust BLVDS Serial Transmission Across** • **Backplanes and Cables for Low EMI**

- No External Coding Required

- Internal PLL, No External PLL Components Required

- Single +3.3V Power Supply

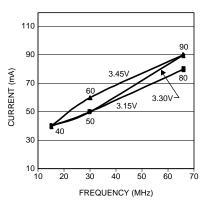

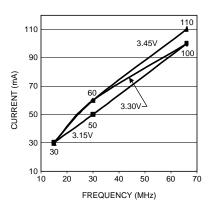

- Low Power: 90mA (typ) Transmitter, 100mA • (typ) at 66 MHz with PRBS-15 Pattern

- ±100 mV Receiver Input Threshold

- Loss of Lock Detection and Reporting Pin

- Industrial -40 to +85°C Temperature Range

- >2.0kV HBM ESD

- Compact, Standard 80-Pin LQFP Package

## DESCRIPTION

The DS92LV18 Serializer/Deserializer (SERDES) pair transparently translates a 18-bit parallel bus into a BLVDS serial stream with embedded clock information. This single serial stream simplifies transferring a 18-bit, or less, bus over PCB traces and cables by eliminating the skew problems between parallel data and clock paths. It saves system cost by narrowing data paths that in turn reduce PCB layers, cable width, and connector size and pins.

This SERDES pair includes built-in system and device test capability. The line loopback feature enables the user to check the integrity of the serial data transmission paths of the transmitter and receiver while deserializing the serial data to parallel data at the receiver outputs. The local loopback feature enables the user to check the integrity of the transceiver from the local parallel-bus side.

The DS92LV18 incorporates modified BLVDS signaling on the high-speed I/O. BLVDS provides a low power and low noise environment for reliably transferring data over a serial transmission path. The equal and opposite currents through the differential data path control EMI by coupling the resulting fringing fields together.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. All trademarks are the property of their respective owners.

SNLS156E - SEPTEMBER 2003-REVISED APRIL 2013

www.ti.com

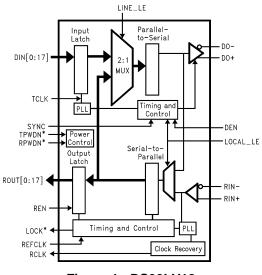

### **Block Diagram**

Figure 1. DS92LV18

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

### Absolute Maximum Ratings (1)(2)

| Supply Voltage (V <sub>CC</sub> )                            | -0.3V to +4V  |                                  |

|--------------------------------------------------------------|---------------|----------------------------------|

| LVCMOS/LVTTL Input Voltage                                   |               | -0.3V to (V <sub>CC</sub> +0.3V) |

| LVCMOS/LVTTL Output Voltage                                  |               | -0.3V to (V <sub>CC</sub> +0.3V) |

| Bus LVDS Receiver Input Voltage                              |               | -0.3V to +3.9V                   |

| Bus LVDS Driver Output Voltage                               |               | -0.3V to +3.9V                   |

| Bus LVDS Output Short Circuit Duration                       | 10ms          |                                  |

| Junction Temperature                                         | +150°C        |                                  |

| Storage Temperature                                          |               | −65°C to +150°C                  |

| Lead Temperature (Soldering, 4 seconds)                      |               | +260°C                           |

| Maximum Package Power Dissipation Capacity Package Derating: | 80L LQFP      | 23.2 mW/°C above +25°C           |

|                                                              | $\theta_{JA}$ | 43°C/W                           |

|                                                              | $\theta_{JC}$ | 11.1°C/W                         |

| ESD Rating (HBM)                                             |               | >2.0kV                           |

(1) "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be ensured. They are not meant to imply that the devices should be operated at these limits. The table of "Electrical Characteristics" specifies conditions of device operation.

(2) If Military/Aerospace specified devices are required, please contact the TI Sales Office/Distributors for availability and specifications.

#### **Recommended Operating Conditions**

|                                                  | Min  | Nom | Мах  | Units |

|--------------------------------------------------|------|-----|------|-------|

| Supply Voltage (V <sub>CC</sub> )                | 3.15 | 3.3 | 3.45 | V     |

| Operating Free Air Temperature (T <sub>A</sub> ) | -40  | +25 | +85  | °C    |

| Clock Rate                                       | 15   |     | 66   | MHz   |

| Supply Noise                                     |      |     | 100  | mV    |

|                                                  |      |     |      | (p-p) |

#### **Electrical Characteristics**

Over recommended operating supply and temperature ranges unless otherwise specified.

| Symbol                  | Parameter                                       | Conditions                                                                    | Pin/Freq.                                                    | Min  | Typ <sup>(1)</sup> | Max             | Units |

|-------------------------|-------------------------------------------------|-------------------------------------------------------------------------------|--------------------------------------------------------------|------|--------------------|-----------------|-------|

| LVCMOS/L                | VTTL DC Specifications                          |                                                                               |                                                              |      |                    |                 |       |

| V <sub>IH</sub>         | High Level Input Voltage                        |                                                                               | DEN, TCLK, TPWDN,                                            | 2.0  |                    | V <sub>CC</sub> | V     |

| VIL                     | Low Level Input Voltage                         |                                                                               | DIN,                                                         | GND  |                    | 0.8             | V     |

| V <sub>CL</sub>         | Input Clamp Voltage                             | I <sub>CL</sub> = −18 mA                                                      | SYNC, RCLK_R/F,<br>REN, REFCLK,                              |      | -0.7               | -1.5            | V     |

| I <sub>IN</sub>         | Input Current                                   | V <sub>IN</sub> = 0V or 3.6V                                                  | RPWDN                                                        | -10  | ±2                 | +10             | μA    |

| V <sub>OH</sub>         | High Level Output Voltage                       | I <sub>OH</sub> = −9 mA                                                       |                                                              | 2.3  | 3.0                | V <sub>CC</sub> | V     |

| V <sub>OL</sub>         | Low Level Output Voltage                        | I <sub>OL</sub> = 9 mA                                                        | R <sub>OUT</sub> , RCLK, LOCK                                | GND  | 0.33               | 0.5             | V     |

| I <sub>OS</sub>         | Output Short Circuit Current                    | VOUT = 0V                                                                     |                                                              | -15  | -48                | -85             | mA    |

| I <sub>OZ</sub>         | TRI-STATE Output Current                        | PWRDN or REN =0.8V, VOUT = 0V orVCC                                           | R <sub>OUT</sub> , RCLK                                      | -10  | ±0.4               | +10             | μA    |

| Bus LVDS                | DC specifications                               |                                                                               |                                                              |      |                    |                 | I     |

| VTH <sup>(2)</sup>      | Differential Threshold High<br>Voltage          |                                                                               |                                                              |      |                    | +100            | mV    |

| VTL <sup>(2)</sup>      | Differential Threshold Low<br>Voltage           | VCM = +1.1V                                                                   | RI+, RI-                                                     | -100 |                    |                 | mV    |

| L.                      | Input Current                                   | V <sub>IN</sub> = +2.4V, V <sub>CC</sub> = 3.6V or 0V                         | KI <del>I</del> , KI-                                        | -10  | ±5                 | +10             | μA    |

| I <sub>IN</sub>         | input Current                                   | $V_{IN} = 0V, V_{CC} = 3.6V \text{ or}$                                       |                                                              | -10  | ±5                 | +10             | μA    |

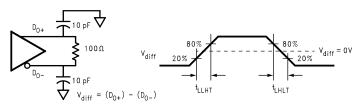

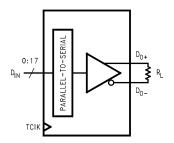

| $V_{OD}^{(2)}$          | Output Differential Voltage<br>(DO+) - (DO-)    | Figure 19, <sup>(3)</sup> ,<br>$R_L = 100\Omega$                              |                                                              | 350  | 500                | 550             | mV    |

| $\Delta V_{OD}{}^{(2)}$ | Output Differential Voltage<br>Unbalance        |                                                                               |                                                              |      | 2                  | 15              | mV    |

| V <sub>OS</sub>         | Offset Voltage                                  |                                                                               |                                                              | 1.05 | 1.2                | 1.25            | V     |

| $\Delta V_{OS}$         | Offset Voltage Unbalance                        |                                                                               |                                                              |      | 2.7                | 15              | mV    |

| I <sub>OS</sub>         | Output Short Circuit Current                    | DO = 0V, Din = H,<br>TPWDN and DEN = 2.4V                                     | DO+, DO-                                                     | -35  | -50                | -70             | mA    |

| I <sub>OZ</sub>         | TRI-STATE Output Current                        | TPWDN or DEN =<br>0.8V, DO = 0V OR<br>VDD                                     |                                                              | -10  | ± 1                | 10              | μA    |

| I <sub>OX</sub>         | Power-Off Output Current                        | VDD = 0V, DO = 0V or<br>3.6V                                                  | -                                                            | -10  | ± 1                | 10              | μA    |

| SER/DES S               | SUPPLY CURRENT (DVDD, PVDD                      | and AVDD pins)                                                                | •                                                            |      | *                  |                 |       |

|                         | Total Supply Current (includes                  | $\begin{array}{l} C_L = 15 p F, \\ R_L = 100 \ \Omega \end{array}$            | f = 66 MHz, PRBS-15<br>pattern                               |      | 190                |                 | mA    |

| I <sub>CCT</sub>        | Total Supply Current (includes<br>load current) | $\begin{array}{c} C_{L} = 15 \text{ pF}, \\ R_{L} = 100 \ \Omega \end{array}$ | f = 66 MHz, Worst case<br>pattern (Checker-board<br>pattern) |      | 220                | 320             | mA    |

| I <sub>CCX</sub>        | Supply Current Powerdown                        | <u>PWRDN</u> = 0.8V, REN<br>= 0.8V                                            |                                                              |      | 1.5                | 3.0             | mA    |

(1) Typical values are given for  $V_{CC} = 3.3V$  and  $T_A = +25^{\circ}C$ . (2) Current into device pins is defined as positive. Current out of device pins is defined as negative. Voltages are referenced to ground except VOD, ΔVOD, VTH and VTL which are differential voltages.

The VOD specification is a measurement of the difference between the single-ended VOH and VOL output voltages across a100 ohm (3) load. Applying the formula OUT+ - OUT- to the differential outputs will result in a waveform with peak to peak amplitude equal to twice the datasheet indicated VOD.

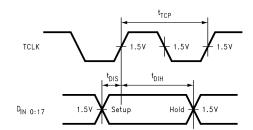

# Serializer Timing Requirements for TCLK

Over recommended operating supply and temperature ranges unless otherwise specified.

| Symbol            | Parameter                  | Conditions         | Min  | Тур  | Max  | Units       |

|-------------------|----------------------------|--------------------|------|------|------|-------------|

| t <sub>TCP</sub>  | Transmit Clock Period      |                    | 15.2 | Т    | 66.7 | ns          |

| t <sub>TCIH</sub> | Transmit Clock High Time   |                    | 0.4T | 0.5T | 0.6T | ns          |

| t <sub>TCIL</sub> | Transmit Clock Low Time    |                    | 0.4T | 0.5T | 0.6T | ns          |

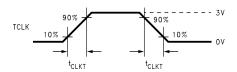

| t <sub>CLKT</sub> | TCLK Input Transition Time |                    |      | 3    | 6    | ns          |

| t <sub>JIT</sub>  | TCLK Input Jitter          | See <sup>(1)</sup> |      |      | 80   | ps<br>(RMS) |

(1) Specified by Design (SBD) using statistical analysis.

# **Serializer Switching Characteristics**

Over recommended operating supply and temperature ranges unless otherwise specified.

| Symbol            | Parameter                               | Conditions                                       | Min                    | Тур                    | Max                    | Units       |

|-------------------|-----------------------------------------|--------------------------------------------------|------------------------|------------------------|------------------------|-------------|

| t <sub>LLHT</sub> | Bus LVDS Low-to-High<br>Transition Time | Figure 4, <sup>(1)</sup>                         |                        | 0.2                    | 0.4                    | ns          |

| t <sub>LHLT</sub> | Bus LVDS High-to-Low<br>Transition Time | $R_L = 100\Omega$ ,<br>$C_L=10pF$ to GND         |                        | 0.2                    | 0.4                    | ns          |

| t <sub>DIS</sub>  | DIN (0-17) Setup to TCLK                | Figure 7, <sup>(1)</sup>                         | 2.4                    |                        |                        | ns          |

| t <sub>DIH</sub>  | DIN (0-17) Hold from TCLK               | $R_L = 100\Omega,$<br>$C_L=10pF$ to GND          | 0                      |                        |                        | ns          |

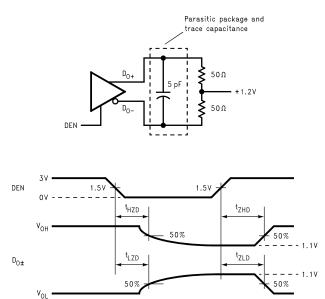

| t <sub>HZD</sub>  | DO ± HIGH to<br>TRI-STATE Delay         |                                                  |                        | 2.3                    | 10                     | ns          |

| t <sub>LZD</sub>  | DO ± LOW to TRI-STATE<br>Delay          | Figure $8^{(2)}$ R <sub>L</sub> = 100 $\Omega$ , |                        | 1.9                    | 10                     | ns          |

| t <sub>ZHD</sub>  | DO ± TRI-STATE to HIGH<br>Delay         | C <sub>L</sub> =10pF to GND                      |                        | 1.0                    | 10                     | ns          |

| t <sub>ZLD</sub>  | DO ± TRI-STATE to LOW<br>Delay          |                                                  |                        | 1.0                    | 10                     | ns          |

| t <sub>SPW</sub>  | SYNC Pulse Width                        | Figure 10, $R_L = 100\Omega$                     | 5*t <sub>TCP</sub>     |                        | 6*t <sub>TCP</sub>     | ns          |

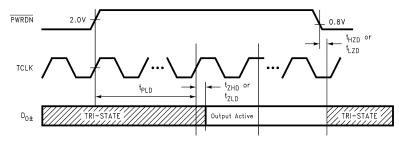

| t <sub>PLD</sub>  | Serializer PLL Lock Time                | Figure 9, $R_L = 100\Omega$                      | 510*t <sub>TCP</sub>   |                        | 1024*t <sub>TCP</sub>  | ns          |

| t <sub>SD</sub>   | Serializer Delay                        | Figure 11, $R_L = 100\Omega$                     | t <sub>TCP</sub> + 1.0 | t <sub>TCP</sub> + 2.0 | t <sub>TCP</sub> + 4.0 | ns          |

| t <sub>RJIT</sub> | Random Jitter                           | Room Temp., 3.3V,<br>66 MHz                      |                        | 4.5                    |                        | ps<br>(RMS) |

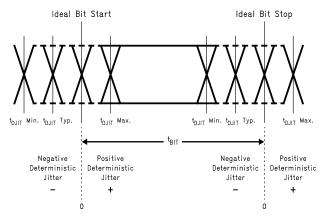

|                   | Deterministic Jitter                    | 15 MHz                                           | -430                   |                        | 190                    | ps          |

| t <sub>DJIT</sub> | Figure 17, <sup>(1)</sup>               | 66 MHz                                           | -40                    |                        | 70                     | ps          |

(1) Specified by Design (SBD) using statistical analysis.

(2) Due to TRI-STATE of the Serializer, the Deserializer will lose PLL lock and have to resynchronize before data transfer.

# **Deserializer Timing Requirements for REFCLK**

Over recommended operating supply and temperature ranges unless otherwise specified.

| Symbol                               | Parameter                     | Conditions | Min  | Тур | Max  | Units |

|--------------------------------------|-------------------------------|------------|------|-----|------|-------|

| t <sub>RFCP</sub>                    | REFCLK Period                 |            | 15.2 | Т   | 66.7 | ns    |

| t <sub>RFDC</sub>                    | REFCLK Duty Cycle             |            | 40   | 50  | 60   | %     |

| t <sub>RFCP</sub> / t <sub>TCP</sub> | Ratio of REFCLK to TCLK       |            | 0.95 |     | 1.05 |       |

| t <sub>RFTT</sub>                    | <b>REFCLK Transition Time</b> |            |      |     | 6    | ns    |

### **Deserializer Switching Characteristics**

Over recommended operating supply and temperature ranges unless otherwise specified.

| Symbol                           | Parameter                                     | Conditions           | Pin/Freq.                             | Min                         | Тур                         | Max                         | Units |

|----------------------------------|-----------------------------------------------|----------------------|---------------------------------------|-----------------------------|-----------------------------|-----------------------------|-------|

| t <sub>RCP</sub>                 | Receiver out Clock<br>Period                  | $t_{RCP} = t_{TCP}$  | RCLK                                  | 15.2                        |                             | 66.7                        | ns    |

| t <sub>RDC</sub>                 | RCLK Duty Cycle                               |                      | RCLK                                  | 45                          | 50                          | 55                          | %     |

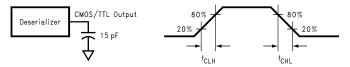

| t <sub>CLH</sub>                 | CMOS/TTL Low-to-<br>High Transition Time      | CL = 15 pF           | RO <u>UT(0</u> -17),<br>LOCK,<br>RCLK |                             | 2.2                         | 4                           | ns    |

| t <sub>CHL</sub>                 | CMOS/TTL High-to-<br>Low Transition Time      | Figure 5             |                                       |                             | 2.2                         | 4                           | ns    |

| t <sub>ROS</sub>                 | ROUT (0-9) Setup<br>Data to RCLK              | Figure 12            |                                       | 0.35*t <sub>RCP</sub>       | 0.5*t <sub>RCP</sub>        |                             | ns    |

| t <sub>ROH</sub>                 | ROUT (0-9) Hold<br>Data to RCLK               | Figure 13            |                                       | −0.35*t <sub>RCP</sub>      | −0.5*t <sub>RCP</sub>       |                             | ns    |

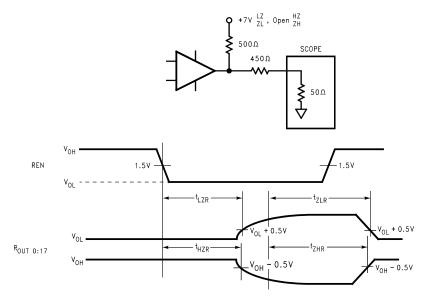

| t <sub>HZR</sub>                 | HIGH to TRI-STATE<br>Delay                    |                      |                                       |                             | 2.2                         | 10                          | ns    |

| t <sub>LZR</sub>                 | LOW to TRI-STATE<br>Delay                     | Einen 14             | ROUT(0-17),                           |                             | 2.2                         | 10                          | ns    |

| t <sub>ZHR</sub>                 | TRI-STATE to HIGH<br>Delay                    | Figure 14            | LOCK                                  |                             | 2.3                         | 10                          | ns    |

| t <sub>ZLR</sub>                 | TRI-STATE to LOW<br>Delay                     |                      |                                       |                             | 2.9                         | 10                          | ns    |

| t <sub>DD</sub>                  | Deserializer Delay                            |                      | RCLK                                  | 1.75*t <sub>RCP</sub> + 2.1 | 1.75*t <sub>RCP</sub> + 4.0 | 1.75*t <sub>RCP</sub> + 6.1 | ns    |

|                                  | Deserializer PLL                              |                      | 15MHz                                 |                             | 3.7                         | 10                          | μs    |

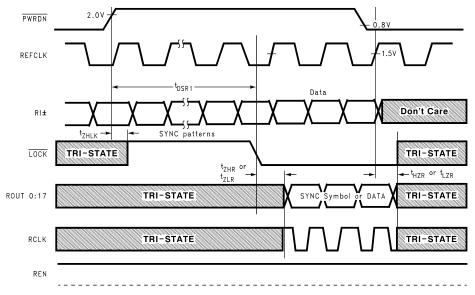

| t <sub>DSR1</sub> <sup>(1)</sup> | Lock Time from<br>Powerdown (with<br>SYNCPAT) | Figure 15,<br>(2)(3) | 66 MHz                                |                             | 1.9                         | 4                           | μs    |

| (1)                              | Deserializer PLL                              | Figure 16,           | 15MHz                                 |                             | 1.5                         | 5                           | μs    |

| t <sub>DSR2</sub> <sup>(1)</sup> | Lock time from<br>SYNCPAT                     | (2)(3)               | 66 MHz                                |                             | 0.9                         | 2                           | μs    |

|                                  | Ideal Deserializer                            | Figure 18<br>(4)(3)  | 15 MHz                                |                             |                             | 1490                        | ps    |

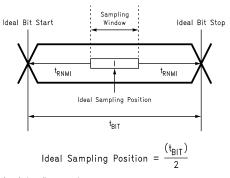

| t <sub>RNMI-R</sub>              | Noise Margin Right                            | -(4)(3)              | 66 MHz                                |                             |                             | 180                         | ps    |

| t                                | Ideal Deserializer                            | Figure 18<br>(4)(3)  | 15 MHz                                |                             |                             | 1460                        | ps    |

| t <sub>RNMI-L</sub>              | Noise Margin Left                             | (4)(3)               | 66 MHz                                |                             |                             | 330                         | ps    |

| t <sub>JI</sub>                  | Total Interconnect                            | See <sup>(5)</sup>   | 15 MHz                                |                             |                             | 1060                        | ps    |

| IJ                               | Jitter Budget                                 | See V                | 66 MHz                                |                             |                             | 160                         | ps    |

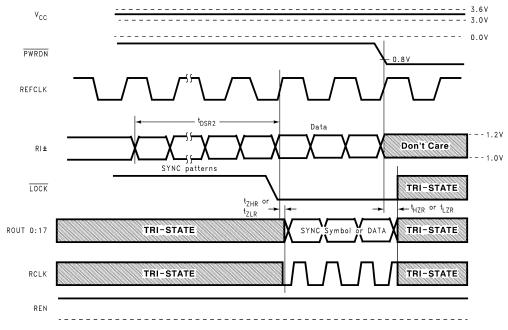

t<sub>DSR1</sub> is the time required by the deserializer to obtain lock when exiting powerdown mode. t<sub>DSR1</sub> is specified with synchronization (1) patterns (SYNCPATs) present at the LVDS inputs (RI+ and RI-) before exiting powerdown mode. t<sub>DSR2</sub> is the time required to obtain lock for the powered-up and enabled deserializer when the LVDS input (RI+ and RI-) conditions change from not receiving data to receiving synchronization patterns. Both t<sub>DSR1</sub> and t<sub>DSR2</sub> are specified with the REFCLK running and stable. A sync pattern is a fixed pattern with 9-bits of data high followed by 9-bits of data low. The SYNC pattern is automatically generated by

(2) the transmitter when the SYNC pin is pulled high.

Specified by Design (SBD) using statistical analysis. (3)

(4) tRNMI is a measure of how much phase noise (jitter) the deserializer can tolerate in the incoming data stream before bit errors occur. It is a measurement in reference with the ideal bit position, please see AN-1217 (SNLA053) for detail. Total Interconnect Jitter Budget (t<sub>JI</sub>) specifies the allowable jitter added by the interconnect assuming both transmitter and receiver are

(5) DS92LV18 circuits. t<sub>JI</sub> is GBD using statistical analysis.

SNLS156E - SEPTEMBER 2003-REVISED APRIL 2013

www.ti.com

### **AC Timing Diagrams and Test Circuits**

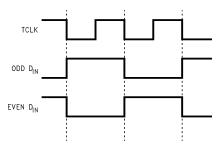

Figure 2. "Worst Case" Serializer ICC Test Pattern

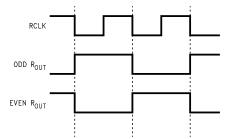

Figure 3. "Worst Case" Deserializer ICC Test Pattern

Figure 4. Serializer Bus LVDS Distributed Output Load and Transition Times

Figure 5. Deserializer CMOS/TTL Distributed Output Load and Transition Times

Figure 6. Serializer Input Clock Transition Time

Figure 8. Serializer TRI-STATE Test Circuit and Timing

Figure 9. Serializer PLL Lock Time, and PWRDN TRI-STATE Delays

SNLS156E - SEPTEMBER 2003 - REVISED APRIL 2013

www.ti.com

Figure 13. Deserializer Setup and Hold Times

SNLS156E-SEPTEMBER 2003-REVISED APRIL 2013

Figure 14. Deserializer TRI-STATE Test Circuit and Timing

Figure 15. Deserializer PLL Lock Times and PWRDN TRI-STATE Delays

# DS92LV18

#### SNLS156E-SEPTEMBER 2003-REVISED APRIL 2013

**NSTRUMENTS**

ÈXAS

Figure 16. Deserializer PLL Lock Time from SYNCPAT

$t_{RNMI-L}$  is the noise margin on the left of the figure above.  $t_{RNMI-R}$  is the noise margin on the right of the above figure.

#### Figure 18. Deserializer Noise Margin (t<sub>RNMI</sub>) and Sampling window

Figure 19. V<sub>OD</sub> Diagram

Figure 20. Typical ICC vs. Frequency with PRBS-15 Pattern (Transmitter Only)

Figure 21. Typical ICC vs. Frequency with PRBS-15 Pattern (Receiver Only)

SNLS156E - SEPTEMBER 2003-REVISED APRIL 2013

www.ti.com

## FUNCTIONAL DESCRIPTION

The DS92LV18 combines a serializer and deserializer onto a single chip. The serializer accepts an 18-bit LVCMOS or LVTTL data bus and transforms it into a BLVDS serial data stream with embedded clock information. The deserializer then recovers the clock and data to deliver the resulting 18-bit wide words to the output.

The device has a separate transmit block and receive block that can operate independently of each other. Each has a power down control to enable efficient operation in various applications. For example, the transceiver can operate as a standby in a redundant data path but still conserve power. The part can be configured as a Serializer, Deserializer, or as a Full Duplex SER/DES.

The DS92LV18 serializer and deserializer blocks each have three operating states. They are the Initialization, Data Transfer, and Resynchronization states. In addition, there are two passive states: Powerdown and TRI-STATE.

The following sections describe each operation mode and passive state.

#### Initialization

Before the DS92LV18 sends or receives data, it must initialize the links to and from another DS92LV18. Initialization refers to synchronizing the Serializer's and Deserializer's PLL's to local clocks. The local clocks must be the same frequency or within a specified range if from different sources. After the Serializers synchronize to the local clocks, the Deserializers synchronize to the Serializers as the second and final initialization step.

Step 1: When  $V_{CC}$  is applied to both Serializer and/or Deserializer, the respective outputs are held in TRI-STATE and internal circuitry is disabled by on-chip power-on circuitry. When  $V_{CC}$  reaches  $V_{CC}$  OK (2.2V) the PLL in each device begins locking to a local clock. For the Serializer, the local clock is the transmit clock, TCLK. For the Deserializer, the local clock is applied to the REFCLK pin. A local on-board oscillator or other source provides the specified clock input to the TCLK and REFCLK pin.

The Serializer outputs are held in TRI-STATE while the PLL locks to the TCLK. After locking to TCLK, the Serializer block is now ready to send data or synchronization patterns. If the SYNC pin is high, then the Serializer block generates and sends the synchronization patterns (sync-pattern).

The Deserializer output will remain in TRI-STATE while its PLL locks to the REFCLK. Also, the Deserializer LOCK output will remain high until its PLL locks to incoming data or a sync-pattern on the RIN pins.

Step 2: The Deserializer PLL must synchronize to the Serializer to complete the initialization. The Serializer that is generating the stream to the Deserializer must send random (non-repetitive) data patterns or sync-patterns during this step of the Initialization State. The Deserializer will lock onto sync-patterns within a specified amount of time. The lock to random data depends on the data patterns and therefore, the lock time is unspecified.

In order to lock to the incoming LVDS data stream, the Deserializer identifies the rising clock edge in a syncpattern and locks to it. If the Deserializer is locking to a random data stream from the Serializer, then it performs a series of operations to identify the rising clock edge and locks to it. Because this locking procedure depends on the data pattern, it is not possible to specify how long it will take. At the point when the Deserializer's PLL locks to the embedded clock, the LOCK pin goes low and valid data appears on the output. Note that the LOCK signal is synchronous to valid data appearing on the outputs.

The user's application determines whether SYNC or lock-to-random-data mode is the preferred method for synchronization. If sync-patterns are preferred, the associated Deserializer's LOCK pin is a convenient way to provide control of the Serializer's SYNC pin.

#### Data Transfer

After initialization, the DS92LV18 Serializer is able to transfer data to the Deserializer. The serial data stream includes a start bit and stop bit appended by the serializer, which frames the eighteen data bits. The start bit is always high and the stop bit is always low. The start and stop bits also function as clock bits embedded in the serial stream.

The Serializer block accepts data from the DIN0-DIN17 parallel inputs. The TCLK signal latches the incoming data on the rising edge. If the SYNC input is high for 6 TCLK cycles, the DS92LV18 does not latch data from DIN0-DIN17.

The Serializer transmits the data and clock bits (18+2 bits) at 20 times the TCLK frequency. For example, if TCLK is 60 MHz, the serial rate is 60 X 20= 1200 Mbps. Since only 18 bits are from input data, the serial 'payload' rate is 18 times the TCLK frequency. For instance, if TCLK = 60 MHz, the payload data rate is 60 X 18 = 1080 Mbps. TCLK is provided by the data source and must be in the range of 15 MHz to 66 MHz.

When the Deserializer channel synchronizes to the input from a Serializer, it drives its LOCK pin low and synchronously delivers valid data on the output. The Deserializer locks to the embedded clock, uses it to generate multiple internal data strobes, and then drives the recovered clock to the RCLK pin. The recovered clock (RCLK output pin) is synchronous to the data on the ROUT[0:17] pins. While LOCK is low, data on ROUT[0:17] is valid. Otherwise, ROUT[0:17] is invalid.

ROUT[0:17], LOCK, and RCLK signals will drive a minimum of three CMOS input gates (15pF total load) at a 66 MHz clock rate. This drive capacity allows bussing outputs of multiple Deserializers to multiple destination ASIC inputs. REN controls TRI-STATE for ROUTn and the RCLK pin on the Deserializer.

The Deserializer input pins are high impedance during receiver powerdown (RPWDN low) and power-off (VCC = 0V).

#### Resynchronization

If the Deserializer loses lock, it will automatically try to resynchronize. For example, if the embedded clock edge is not detected two times in succession, the PLL loses lock and the LOCK pin is driven high. The Deserializer then enters the operating mode where it tries to lock to a random data stream. It looks for the embedded clock edge, identifies it and then proceeds through the synchronization process.

The logic state of the LOCK signal indicates whether the data on ROUT is valid; when it is low, the data is valid. The system must monitor the LOCK pin to determine whether data on the ROUT is valid. Because there is a short delay in the LOCK signal's response to the PLL losing synchronization to the incoming data stream, the system must determine the validity of data for the cycles before the LOCK signal goes high.

The user can choose to resynchronize to the random data stream or to force fast synchronization by pulsing the Serializer's SYNC pin. Lock times depend on serial data stream characteristics. The primary constraint on the "random" lock time is the initial phase relation between the incoming data and the REFCLK when the Deserializer powers up. An advantage of using the SYNC pattern to force synchronization is the ability for the user to predict the delay before the PLL regains lock. This scheme is left up to the user discretion. One recommendation is to provide a feedback loop using the LOCK pin itself to control the sync request of the Serializer, which is the SYNC pin.

If a specific pattern is repetitive, the Deserializer's PLL will not lock in order to prevent the Deserializer from locking to the data pattern rather than the clock. We refer to such pattern as a repetitive multi-transition, RMT. This occurs when more than one Low-High transition takes places in a clock cycle over multiple cycles. This occurs when any bit, except DIN 17, is held at a low state and the adjacent bit is held high, creating a 0-1 transition. The internal circuitry accomplishes this by detecting more than one potential position for clocking bits. Upon detection, the circuitry will prevent the LOCK output from becoming active until the RMT pattern changes. Once the RMT pattern changes and the internal circuitry recognizes the clock bits in the serial data stream, the PLL of the Deserializer will lock, which will drive the LOCK output to low and the output data ROUTn will become valid.

#### Powerdown

The Powerdown state is a low <u>power sleep mode that</u> the Serializer and Deserializer will occupy while waiting for initialization. You can also use TPWDN and RPWDN to reduce power when there are no pending data transfers. The Deserializer enters powerdown mode when RPWDN is driven low. In powerdown mode, the PLL stops and the outputs enter TRI-STATE, which reduces supply current to the µA range.

To bring the Deserializer block out of the Powerdown state, the system drives **RPWDN** high. When the Deserializer exits Powerdown, it automatically enters the Initialization state. The system must then allow time for Initialization before data transfer can begin.

The TPWDN pin driven low forces the Serializer block into low power consumption, where the supply current is in the µA range. The Serializer PLL stops and the output goes into a TRI-STATE condition.

SNLS156E - SEPTEMBER 2003 - REVISED APRIL 2013

www.ti.com

To bring the Serializer block out of the powerdown state, the system drives TPWDN high. When the Serializer exits Powerdown, its PLL must lock to TCLK before it is ready for the Initialization state. The system must then allow time for Initialization before data transfer can begin.

## TRI-STATE

When the system drives the REN pin low, the Deserializer's outputs enter TRI-STATE. This will TRI-STATE the receiver output pins (ROUT[0:17]) and RCLK. When the system drives REN high, the Deserializer will return to the previous state as long as all other control pins remain static (RPWDN).

When the system drives the DEN pin low, the Serializer's LVDS outputs enter TRI-STATE. When the system drives the DEN signal high, the Serializer output will return to the previous state as long as all other control and data input pins remain in the same condition before DEN was driven low.

### Loopback Test Operation

The DS92LV18 includes two Loopback modes for testing the device functionality and the transmission line continuity. Asserting the Line Loopback control signal connects the serial data input ( $RIN_{\pm}$ ) to the serial data output ( $DO_{\pm}$ ) and to the parallel data output (ROUT[0:17]). The serial data goes through deserializer and serializer blocks.

Asserting the Local Loopback control signal connects the parallel data input (DIN[0:17]) back to the parallel data output (ROUT[0:17]). The connection route includes all the functional blocks of the SER/DES Pair. The serial data output (DO±) is automatically disabled during the Local Loopback operating mode.

Please note that when switching between normal, line, or loopback modes, the deserializer will need to relock. In order for the serializer and deserializer to resync, the TCLK and REFCLK frequencies must be within ±5% of each other.

#### **Application Information**

#### USING THE DS92LV18

The DS92LV18 combines a Serializer and Deserializer onto a single chip that sends 18 bits of parallel TTL data over a serial Bus LVDS link up to 1.32 Gbps. Serialization of the input data is accomplished using an on-board PLL at the Serializer which embeds two clock bits with the data. The Deserializer uses a separate reference clock (REFCLK) and an on-board PLL to extract the clock information from the incoming data stream and deserialize the data. The Deserializer monitors the incoming clock information to determine lock status and will indicate loss of lock by asserting the LOCK output high.

#### POWER CONSIDERATIONS

An all CMOS design of the Serializer and Deserializer makes them inherently low power devices. Additionally, the constant current source nature of the LVDS outputs minimize the slope of the speed vs.  $I_{CC}$  curve of CMOS designs.

#### POWERING UP THE DESERIALIZER

The REFCLK input can be running before the Deserializer is powered up and it must be running in order for the Deserializer to lock to incoming data. The Deserializer outputs will remain in TRI-STATE until the Deserializer detects data transmission at its inputs and locks to the incoming serial data stream.

#### NOISE MARGIN

The Deserializer noise margin is the amount of input jitter (phase noise) that the Deserializer can tolerate and still reliably recover data. Various environmental and systematic factors include:

Serializer: TCLK jitter, V<sub>CC</sub> noise (noise bandwidth and out-of-band noise)

Media: ISI,  $V_{CM}$  noise

Deserializer: V<sub>CC</sub> noise

For a graphical representation of noise margin, please see Figure 18.

#### **RECOVERING FROM LOCK LOSS**

SNLS156E - SEPTEMBER 2003-REVISED APRIL 2013

In the case where the Serializer loses lock during data transmission, up to 5 cycles of data that were previously received could be invalid. This is due to a delay in the lock detection circuit. The lock detect circuit requires that invalid clock information be received 2 times in a row to indicate loss of lock. <u>Since clock</u> information has been lost, it is possible that data was also lost during these cycles. If the Deserializer LOCK pin goes low, data from at least the previous 5 cycles should be resent upon regaining lock.

Lock can be regained at the Deserializer by causing the Serializer to resend SYNC patterns as described above or by random data locking which can take more time depending upon the data patterns being received.

#### INPUT FAILSAFE

In the event that the Deserializer is disconnected from the Serializer, or the Deserializer loses lock, the failsafe circuitry is designed to reject a certain amount of noise from being interpreted as data or clock. The Deserializer outputs (ROUT [0:17] and RCLK) will be asserted HIGH.

#### HOT INSERTION

All of TI's LVDS devices are hot pluggable if you follow a few rules. When inserting, ensure the Ground pin(s) makes contact first, then the VCC pin(s), then the I/O pin(s). When removing, the I/O pins should be unplugged first, then VCC, then Ground.

#### PCB LAYOUT AND POWER SYSTEM CONSIDERATIONS

Circuit board layout and stack-up for the BLVDS devices should be designed to provide low-noise power feed to the device. Good layout practice will also separate high-frequency or high-level inputs and outputs to minimize unwanted stray noise pickup, feedback and interference. Power system performance may be greatly improved by using thin dielectrics (2 to 4 mils) for power / ground sandwiches. This arrangement provides plane capacitance for the PCB power system with low-inductance parasitics, which has proven especially effective at high frequencies above approximately 50MHz, and makes the value and placement of external bypass capacitors less critical. External bypass capacitors should include both RF ceramic and tantalum electrolytic types. RF capacitors may use values in the range of 0.01 uF to 0.1 uF. Tantalum capacitors may be in the 2.2 uF to 10 uF range. Voltage rating of the tantalum capacitors should be at least 5X the power supply voltage being used.

It is a recommended practice to use two vias at each power pin as well as at all RF bypass capacitor terminals. Dual vias reduce the interconnect inductance by up to half, thereby reducing interconnect inductance and extending the effective frequency range of the bypass components. Locate RF capacitors as close as possible to the supply pins, and use wide low impedance traces (not 50 Ohm traces). Surface mount capacitors are recommended due to their smaller parasitics. When using multiple capacitors per supply pin, locate the smaller value closer to the pin. A large bulk capacitor is recommend at the point of power entry. This is typically in the 50uF to 100uF range and will smooth low frequency switching noise. It is recommended to connect power and ground pins directly to the power and ground planes with bypass capacitors connected to the plane with via on both ends of the capacitor. Connecting power or ground pins to an external bypass capacitor will increase the inductance of the path.

A small body size X7R chip capacitor, such as 0603, is recommended for external bypass. Its small body size reduces the parasitic inductance of the capacitor. The user must pay attention to the resonance frequency of these external bypass capacitors, usually in the range of 20-30 MHz range. To provide effective bypassing, multiple capacitors are often used to achieve low impedance between the supply rails over the frequency of interest. At high frequency, it is also a common practice to use two vias from power and ground pins to the planes, reducing the impedance at high frequency.

Some devices provide separate power and ground pins for different portions of the circuit. This is done to isolate switching noise effects between different sections of the circuit. Separate planes on the PCB are typically not required. Pin Description tables typically provide guidance on which circuit blocks are connected to which power pin pairs. In some cases, an external filter many be used to provide clean power to sensitive circuits such as PLLs.

Use at least a four layer board with a power and ground plane. Locate CMOS (TTL) signals away from the LVDS lines to prevent coupling from the CMOS lines to the LVDS lines. Closely-coupled differential lines of 100 Ohms are typically recommended for LVDS interconnect. The closely-coupled lines help to ensure that coupled noise will appear as common-mode and thus is rejected by the receivers. The tightly coupled lines will also radiate less.

Copyright © 2003–2013, Texas Instruments Incorporated

SNLS156E – SEPTEMBER 2003 – REVISED APRIL 2013

www.ti.com

Termination of the LVDS interconnect is required. For point-to-point applications, termination should be located at the load end. Nominal value is 100 Ohms to match the line's differential impedance. Place the resistor as close to the receiver inputs as possible to minimize the resulting stub between the termination resistor and receiver.

Additional general guidance can be found in the LVDS Owner's Manual - available in PDF format from the TI web site at: www.ti.com/lvds.

Specific guidance for this device is provided next.

#### DS92LV18 BLVDS SER/DES PAIR

General device specific guidance is given below. Exact guidance can not be given as it is dictated by other board level /system level criteria. This includes the density of the board, power rails, power supply, and other integrated circuit power supply needs.

#### DVDD = DIGITAL SECTION POWER SUPPLY

These pins supply the digital portion of the device as well as the receiver output buffers. The Deserializer's DVDD requires more bypass to power the outputs under synchronous switching conditions. The Serializer's DVDD is less critical. The receiver's DVDD pins power 4 outputs from each DVDD pin. An estimate of local capacitance required indicates a minimum of 22nF is required. This is calculated by taking 4 times the maximum short current (4 X 70 = 280mA), multiplying by the rise time of the part (4ns), and dividing by the maximum allowed droop in VDD (assume 50mV) yields 22.4nF. Rounding up to a standard value, 0.1uF is selected for each DVDD pin.

#### **PVDD = PLL SECTION POWER SUPPLY**

The PVDD pin supplies the PLL circuit. Note that the DS92LV18 has two separate PLL and supply pins. The PLL(s) require clean power for the minimization of Jitter. A supply noise frequency in the 300 kHz to 1 MHz range can cause increased output jitter. Certain power supplies may have switching frequencies or high harmonic content in this range. If this is the case, filtering of this noise spectrum may be required. A notch filter response is best to provide a stable VDD, suppression of the noise band, and good high-frequency response (clock fundamental). This may be accomplished with a pie filter (CRC or CLC). If employed, a separate pie filter is recommended for each PLL to minimize drop in potential due to the series resistance. The pie filter should be located close to the PVDD power pin. Separate power planes for the PVDD pins is typically not required.

#### AVDD = LVDS SECTION POWER SUPPLY

The AVDD pins power the LVDS portion of the circuit. The DS92LV18 has four AVDD pins. Due to the nature of the design, current draw is not excessive on these pins. A 0.1uF capacitor is sufficient for these pins. If space is available, a 0.01uF capacitor may be used in parallel with the 0.1uF capacitor for additional high frequency filtering.

#### GROUNDS

The AGND pin should be connected to the signal common in the cable for the return path of any common-mode current. Most of the LVDS current will be odd-mode and return within the interconnect pair. A small amount of current may be even-mode due to coupled noise and driver imbalances. This current should return via a low impedance known path.

A solid ground plane is recommended for both DVDD, PVDD or AVDD. Using a split plane may cause ground loops or a difference in ground potential at various ground pins of the device.

#### SNLS156E-SEPTEMBER 2003-REVISED APRIL 2013

|                |              |                          | Fruth Table    | es                             |        |                                     |

|----------------|--------------|--------------------------|----------------|--------------------------------|--------|-------------------------------------|

|                |              | Trai                     | nsmitter Truth | Table                          |        |                                     |

| TPWDN (Pin 42) | DEN (Pin     | 19)                      | TX PLL         | . Status (Internal)            | LVDS ( | Outputs (Pins 13 and 14)            |

| L              | Х            |                          |                | Х                              |        | Hi Z                                |

| Н              | L            |                          |                | Х                              |        | Hi Z                                |

| Н              | Н            | Н                        |                | Not Locked                     |        | Hi Z                                |

| Н              | Н            |                          |                | Locked Serialized              |        | Data with Embedded Clock            |

|                | · · ·        | Re                       | ceiver Truth T | able                           | •      |                                     |

| RPWDN (Pin 01) | REN (Pin 02) | RX PLL Status (Internal) |                | ROUTn & RCL<br>(See Pin Diagra |        | LOCK (Pin 63)                       |

| L              | Х            |                          | Х              | Hi Z                           |        | Hi Z                                |

| Н              | L            | x                        |                | Hi Z                           |        | L = PLL Locked;<br>H = PLL Unlocked |

| Н              | Н            | Not                      | Locked         | н                              |        | Н                                   |

| Н              | Н            | Lo                       | ocked          | Data & CLK Act                 | ive    | L                                   |

...

. .

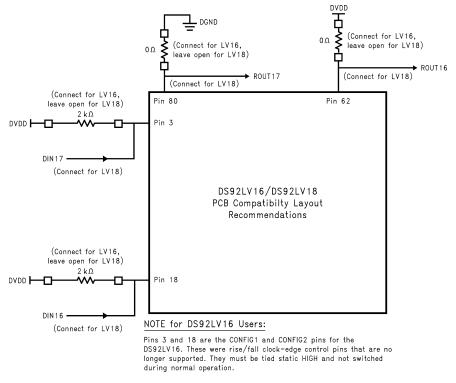

#### Footprint Changes between the DS92LV16 and the DS92LV18

| DS92LV16 vs. DS92LV18 Footprint Changes |          |          |  |  |  |  |

|-----------------------------------------|----------|----------|--|--|--|--|

| Pin Number                              | DS92LV16 | DS92LV18 |  |  |  |  |

| 3                                       | CONFIG1  | DIN17    |  |  |  |  |

| 18                                      | CONFIG2  | DIN16    |  |  |  |  |

| 62                                      | DVDD     | ROUT16   |  |  |  |  |

| 80                                      | DGND     | ROUT17   |  |  |  |  |

#### PCB Compatibility Between the DS92LV16 and DS92LV18

SNLS156E-SEPTEMBER 2003-REVISED APRIL 2013

www.ti.com

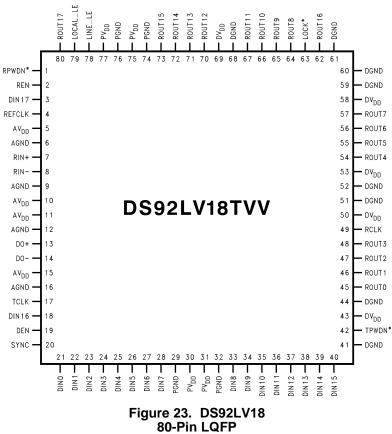

### Pin Diagram

Top View

DS92LV18

www.ti.com

#### SNLS156E - SEPTEMBER 2003-REVISED APRIL 2013

| Table 1. | <b>PIN DESCRIPTIONS</b> |  |

|----------|-------------------------|--|

|          |                         |  |

| Pin #                                                                        | Pin Name    | I/O     | Description                                                                                                                                                                        |

|------------------------------------------------------------------------------|-------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                                                                            | RPWDN       | CMOS, I | RPWDN = Low will put the Receiver in low power, stand-by, mode.<br>Note: The Receiver PLL will lose lock. <sup>(1)</sup>                                                           |

| 2                                                                            | REN         | CMOS, I | REN = Low will disable the Receiver outputs. Receiver PLL remains locked. (See LOCK pin description) <sup>(1)</sup>                                                                |

| 4                                                                            | REFCLK      | CMOS, I | Frequency reference clock input for the receiver.                                                                                                                                  |

| 5, 10, 11, 15                                                                | AVDD        |         | Analog Voltage Supply                                                                                                                                                              |

| 6,9,12,16                                                                    | AGND        |         | Analog Ground                                                                                                                                                                      |

| 7                                                                            | RIN+        | LVDS, I | Receiver LVDS True Input                                                                                                                                                           |

| 8                                                                            | RIN-        | LVDS, I | Receiver LVDS Inverting Input                                                                                                                                                      |

| 13                                                                           | DO+         | LVDS, O | Transmitter LVDS True Output                                                                                                                                                       |

| 14                                                                           | DO-         | LVDS, O | Transmitter LVDS Inverting Output                                                                                                                                                  |

| 17                                                                           | TCLK        | CMOS, I | Transmitter reference clock. Used to strobe data at the DIN Inputs and to drive the transmitter PLL. See TCLK Timing Requirements.                                                 |

| 19                                                                           | DEN         | CMOS, I | DEN = Low will disable the Transmitter outputs. The transmitter PLL will remain locked. <sup>(1)</sup>                                                                             |

| 20                                                                           | SYNC        | CMOS, I | SYNC = High will cause the transmitter to ignore the data inputs and send SYNC patterns to provide a locking reference to receiver(s). See Functional Description. <sup>(1)</sup>  |

| 3, 18,21, 22, 23, 24, 25,<br>26, 27, 28, 33, 34, 35, 36,<br>37, 38, 39, 40   | DIN (0:17)  | CMOS, I | Transmitter data inputs. <sup>(1)</sup>                                                                                                                                            |

| 29,32                                                                        | PGND        |         | PLL Ground.                                                                                                                                                                        |

| 30,31                                                                        | PVDD        |         | PLL Voltage supply.                                                                                                                                                                |

| 41, 44, 51, 52, 59, 60, 61,<br>68                                            | DGND        |         | Digital Ground.                                                                                                                                                                    |

| 42                                                                           | TPWDN       | CMOS, I | $\overline{\text{TPWDN}}$ = Low will put the Transmitter in low power, stand-by mode.<br>Note: The transmitter PLL will lose lock. <sup>(1)</sup>                                  |

| 43, 50, 53, 58, 69                                                           | DVDD        |         | Digital Voltage Supplies.                                                                                                                                                          |

| 45, 46, 47, 48, 54, 55, 56,<br>57, 62, 64, 65, 66, 67, 70,<br>71, 72, 73, 80 | ROUT (0:17) | CMOS, O | Receiver Outputs.                                                                                                                                                                  |

| 49                                                                           | RCLK        | CMOS, O | Recovered Clock. Parallel data rate clock recovered from embedded clock. Used to strobe ROUT (0:17). LVCMOS Level output.                                                          |

| 63                                                                           | LOCK        | CMOS, O | $\overline{\text{LOCK}}$ indicates the status of the receiver PLL. $\overline{\text{LOCK}}$ = H - receiver PLL is unlocked, $\overline{\text{LOCK}}$ = L - receiver PLL is locked. |

| 74,76                                                                        | PGND        |         | PLL Grounds.                                                                                                                                                                       |

| 75,77                                                                        | PVDD        |         | PLL Voltage Supplies.                                                                                                                                                              |

| 78                                                                           | LINE_LE     | CMOS, I | LINE_LE = High enables the receiver loopback mode. Data received at the RIN $\pm$ inputs is fed back through the DO $\pm$ outputs. <sup>(1)</sup>                                  |

| 79                                                                           | LOCAL_LE    | CMOS, I | LOCAL_LE = High enables the transmitter loopback mode. Data received at the DIN inputs is fed back through the ROUT outputs. <sup>(1)</sup>                                        |

(1) Input defaults to "low" state when left open due to an internal on-chip pull-down circuit.

SNLS156E - SEPTEMBER 2003-REVISED APRIL 2013

# **REVISION HISTORY**

| Cł | hanges from Revision D (April 2013) to Revision E  | Page |

|----|----------------------------------------------------|------|

| •  | Changed layout of National Data Sheet to TI format | . 19 |

www.ti.com

10-Dec-2020

## PACKAGING INFORMATION

| Orderable Device  | Status<br>(1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan<br>(2) | Lead finish/<br>Ball material | MSL Peak Temp<br>(3) | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|-------------------|---------------|--------------|--------------------|------|----------------|-----------------|-------------------------------|----------------------|--------------|-------------------------|---------|

| DS92LV18TVV/NOPB  | ACTIVE        | LQFP         | PN                 | 80   | 119            | RoHS & Green    | SN                            | Level-3-260C-168 HR  | -40 to 85    | DS92LV18TVV<br>>B       | Samples |

| DS92LV18TVVX/NOPB | ACTIVE        | LQFP         | PN                 | 80   | 1000           | RoHS & Green    | SN                            | Level-3-260C-168 HR  | -40 to 85    | DS92LV18TVV<br>>B       | Samples |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

**PREVIEW:** Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

**RoHS Exempt:** TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <= 1000ppm threshold. Antimony trioxide based flame retardants must also meet the <= 1000ppm threshold requirement.

<sup>(3)</sup> MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

(5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

<sup>(6)</sup> Lead finish/Ball material - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

# PACKAGE OPTION ADDENDUM

10-Dec-2020

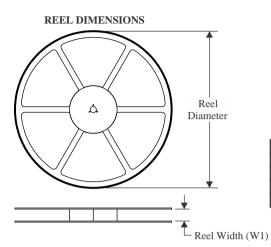

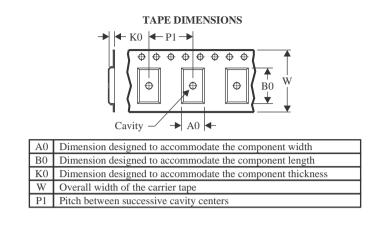

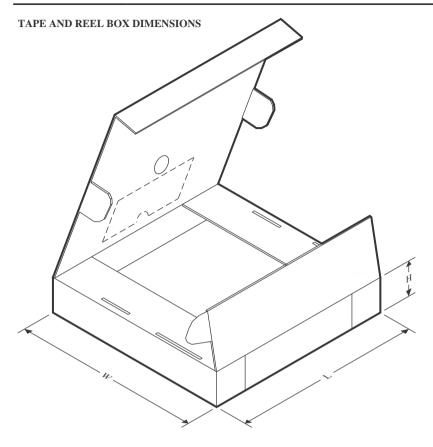

## TAPE AND REEL INFORMATION

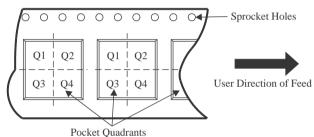

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| *All dimensions are nominal |                 |                    |    |      |                          |                          |       |            |            |            |           |                  |

|-----------------------------|-----------------|--------------------|----|------|--------------------------|--------------------------|-------|------------|------------|------------|-----------|------------------|

| Device                      | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | ` '   | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

| DS92LV18TVVX/NOPB           | LQFP            | PN                 | 80 | 1000 | 330.0                    | 24.4                     | 14.65 | 14.65      | 2.3        | 24.0       | 24.0      | Q2               |

# PACKAGE MATERIALS INFORMATION

6-Feb-2024

\*All dimensions are nominal

| Device            | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|-------------------|--------------|-----------------|------|------|-------------|------------|-------------|

| DS92LV18TVVX/NOPB | LQFP         | PN              | 80   | 1000 | 367.0       | 367.0      | 45.0        |

## TEXAS INSTRUMENTS

www.ti.com

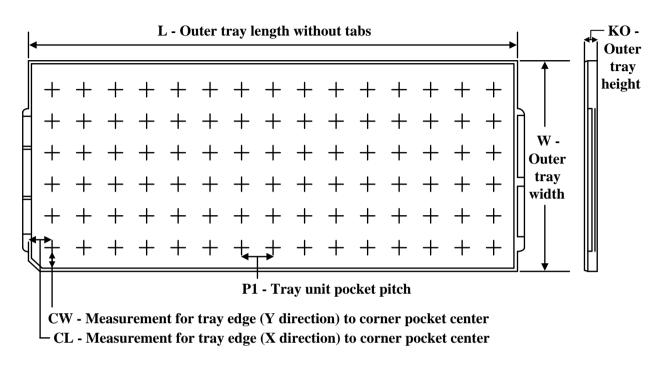

### TRAY

6-Feb-2024

Chamfer on Tray corner indicates Pin 1 orientation of packed units.

\*All dimensions are nominal

| Device           | Package<br>Name | Package<br>Type | Pins | SPQ | Unit array<br>matrix | Max<br>temperature<br>(°C) | L (mm) | W<br>(mm) | K0<br>(µm) | P1<br>(mm) | CL<br>(mm) | CW<br>(mm) |

|------------------|-----------------|-----------------|------|-----|----------------------|----------------------------|--------|-----------|------------|------------|------------|------------|

| DS92LV18TVV/NOPB | PN              | LQFP            | 80   | 119 | 7 X 17               | 150                        | 322.6  | 135.9     | 7620       | 17.9       | 14.3       | 13.95      |

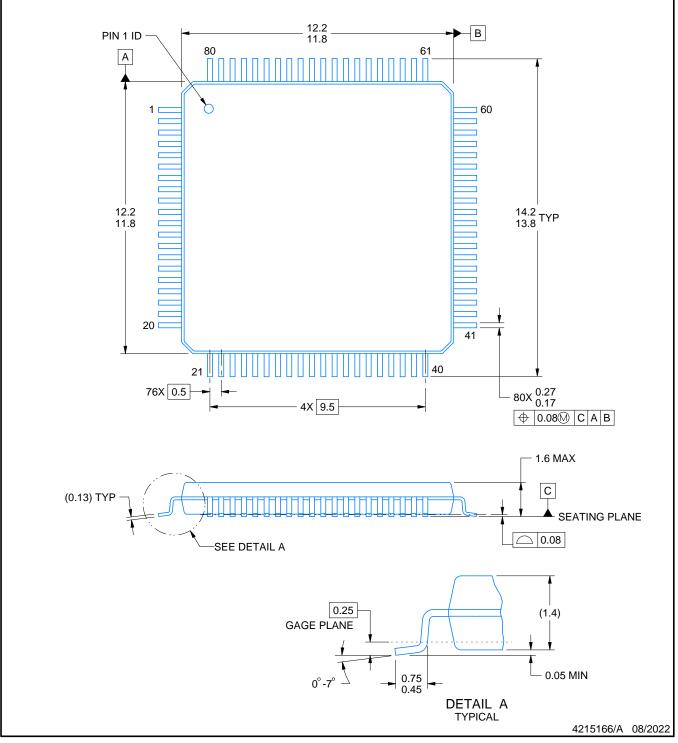

# **PN0080A**

# **PACKAGE OUTLINE**

# LQFP - 1.6 mm max height

PLASTIC QUAD FLATPACK

NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing All lifear differsions are in minimeters, vary amore per ASME Y14.5M.

This drawing is subject to change without notice.

Reference JEDEC registration MS-026.

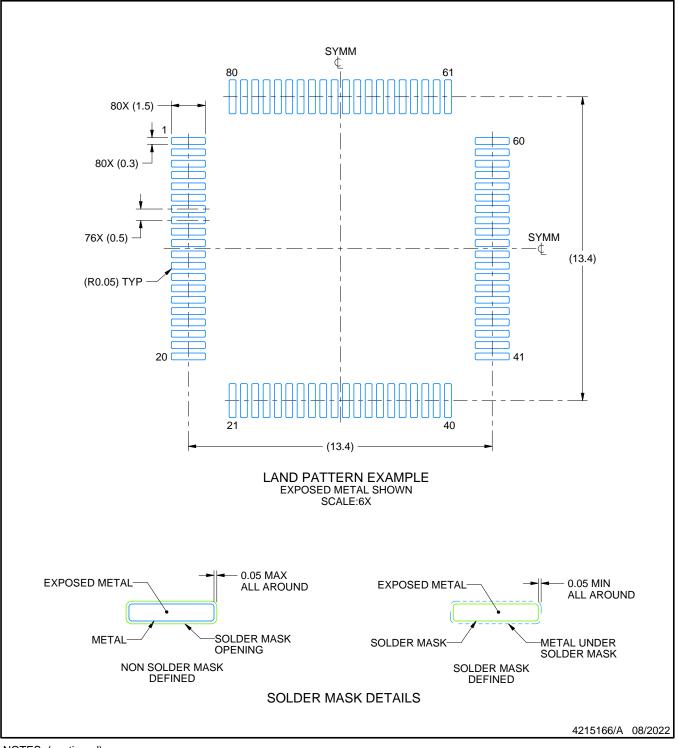

# **PN0080A**

# **EXAMPLE BOARD LAYOUT**

# LQFP - 1.6 mm max height

PLASTIC QUAD FLATPACK

NOTES: (continued)

4. Publication IPC-7351 may have alternate designs.

Solder mask tolerances between and around signal pads can vary based on board fabrication site.

For more information, see Texas Instruments literature number SLMA004 (www.ti.com/lit/slma004).

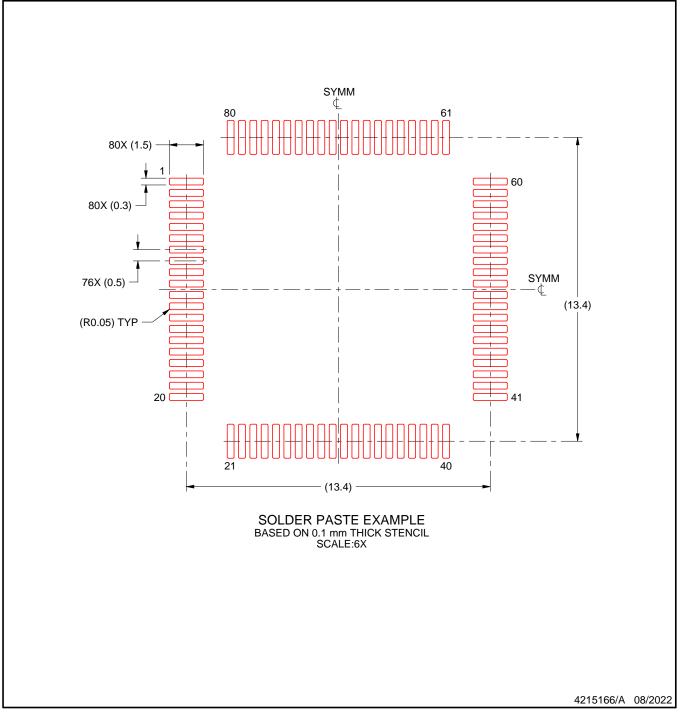

# PN0080A

# **EXAMPLE STENCIL DESIGN**

# LQFP - 1.6 mm max height

PLASTIC QUAD FLATPACK

NOTES: (continued)

7. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

8. Board assembly site may have different recommendations for stencil design.

## IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2024, Texas Instruments Incorporated