LMV831, LMV832, LMV834

www.ti.com

SNOSAZ6B-AUGUST 2008-REVISED MARCH 2013

## LMV831 Single/ LMV832 Dual/ LMV834 Quad 3.3 MHz Low Power CMOS, EMI Hardened Operational Amplifiers

Check for Samples: LMV831, LMV832, LMV834

## FEATURES

- Unless Otherwise Noted, Typical Values at  $T_A{=}25^{\circ}\text{C},\,V^{+}=3.3\text{V}$

- Supply Voltage 2.7V to 5.5V

- Supply Current (per Channel) 240 µA

- Input Offset Voltage 1 mV Max

- Input Bias Current 0.1 pA

- GBW 3.3 MHz

- EMIRR at 1.8 GHz 120 dB

- Input Noise Voltage at 1 kHz 12 nV/\/Hz

- Slew Rate 2 V/µs

- Output Voltage Swing Rail-to-Rail

- Output Current Drive 30 mA

- Operating Ambient Temperature Range –40°C to 125°C

## APPLICATIONS

- Photodiode Preamp

- Piezoelectric Sensors

- Portable/Battery-Powered Electronic Equipment

- Filters/Buffers

- PDAs/Phone Accessories

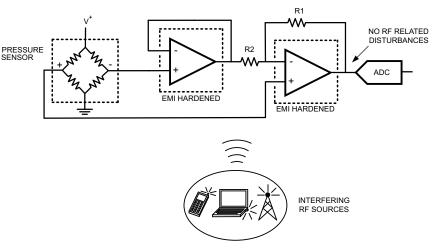

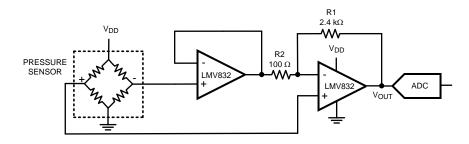

### **Typical Application**

## DESCRIPTION

TI's LMV831, LMV832, and LMV834 are CMOS input, low power op amp IC's, providing a low input bias current, a wide temperature range of -40°C to 125°C and exceptional performance making them robust general purpose parts. Additionally, the LMV831/LMV832/LMV834 are EMI hardened to minimize any interference so they are ideal for EMI sensitive applications.

The unity gain stable LMV831/LMV832/LMV834 feature 3.3 MHz of bandwidth while consuming only 0.24 mA of current per channel. These parts also maintain stability for capacitive loads as large as 200 pF. The LMV831/LMV832/LMV834 provide superior performance and economy in terms of power and space usage.

This family of parts has a maximum input offset voltage of 1 mV, a rail-to-rail output stage and an input common-mode voltage range that includes ground. Over an operating range from 2.7V to 5.5V the LMV831/LMV832/LMV834 provide a PSRR of 93 dB, and a CMRR of 91 dB. The LMV831 is offered in the space saving 5-Pin SC70 package, the LMV832 in the 8-Pin VSSOP and the LMV834 is offered in the 14-Pin TSSOP package.

Figure 1. EMI Hardened Sensor Application

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. All trademarks are the property of their respective owners.

www.ti.com

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

### Absolute Maximum Ratings<sup>(1)(2)</sup>

|                                      | Human Body Model                | 2 kV                                          |

|--------------------------------------|---------------------------------|-----------------------------------------------|

| ESD Tolerance <sup>(3)</sup>         | Charge-Device Model             | 1 kV                                          |

|                                      | Machine Model                   | 200V                                          |

| V <sub>IN</sub> Differential         | ± Supply Voltage                |                                               |

| Supply Voltage ( $V_S = V^+ - V^-$ ) | 6V                              |                                               |

| Voltage at Input/Output Pins         |                                 | V <sup>+</sup> +0.4V,<br>V <sup>−</sup> −0.4V |

| Storage Temperature Range            |                                 | −65°C to 150°C                                |

| Junction Temperature <sup>(4)</sup>  |                                 | 150°C                                         |

| Soldering Information                | Infrared or Convection (20 sec) | 260°C                                         |

(1) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is intended to be functional, but specific performance is not ensured. For ensured specifications and the test conditions, see the Electrical Characteristics Tables.

(2) If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office/ Distributors for availability and specifications.

(3) Human Body Model, applicable std. MIL-STD-883, Method 3015.7. Machine Model, applicable std. JESD22-A115-A (ESD MM std. of JEDEC) Field-Induced Charge-Device Model, applicable std. JESD22-C101-C (ESD FICDM std. of JEDEC).

(4) The maximum power dissipation is a function of  $T_{J(MAX)}$ ,  $\theta_{JA}$ , and  $T_A$ . The maximum allowable power dissipation at any ambient temperature is  $P_D = (T_{J(MAX)} - T_A)/\theta_{JA}$ . All numbers apply for packages soldered directly onto a PC board.

## **Operating Ratings**<sup>(1)</sup>

| Temperature Range <sup>(2)</sup>                   | -40°C to 125°C |         |

|----------------------------------------------------|----------------|---------|

| Supply Voltage ( $V_S = V^+ - V^-$ )               | 2.7V to 5.5V   |         |

|                                                    | 5-Pin SC70     | 302°C/W |

| Package Thermal Resistance ( $\theta_{JA}^{(2)}$ ) | 8-Pin VSSOP    | 217°C/W |

|                                                    | 14-Pin TSSOP   | 135°C/W |

(1) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is intended to be functional, but specific performance is not ensured. For ensured specifications and the test conditions, see the Electrical Characteristics Tables.

(2) The maximum power dissipation is a function of  $T_{J(MAX)}$ ,  $\theta_{JA}$ , and  $T_A$ . The maximum allowable power dissipation at any ambient temperature is  $P_D = (T_{J(MAX)} - T_A)/\theta_{JA}$ . All numbers apply for packages soldered directly onto a PC board.

## 3.3V Electrical Characteristics<sup>(1)</sup>

Unless otherwise specified, all limits are specified for at  $T_A = 25^{\circ}$ C,  $V^+ = 3.3$ V,  $V^- = 0$ V,  $V_{CM} = V^+/2$ , and  $R_L = 10 \text{ k}\Omega$  to  $V^+/2$ . **Boldface** limits apply at the temperature extremes.

| Symbol            | Parameter                                                   | Conditions        | Min<br>(2) | Тур<br>(3) | Max<br>(2)            | Units |

|-------------------|-------------------------------------------------------------|-------------------|------------|------------|-----------------------|-------|

| V <sub>OS</sub>   | Input Offset Voltage <sup>(4)</sup>                         |                   |            | ±0.25      | ±1.00<br><b>±1.23</b> | mV    |

| TCV <sub>OS</sub> | Input Offset Voltage Temperature<br>Drift <sup>(4)(5)</sup> | LMV831,<br>LMV832 |            | ±0.5       | ±1.5                  | µV/°C |

|                   |                                                             | LMV834            |            | ±0.5       | ±1.7                  |       |

- (1) Electrical Table values apply only for factory testing conditions at the temperature indicated. Factory testing conditions result in very limited self-heating of the device such that  $T_J = T_A$ . No specification of parametric performance is indicated in the electrical tables under conditions of internal self-heating where  $T_J > T_A$ .

- (2) Limits are 100% production tested at 25°C. Limits over the operating temperature range are specified through correlations using statistical quality control (SQC) method.

- (3) Typical values represent the most likely parametric norm as determined at the time of characterization. Actual typical values may vary over time and will also depend on the application and configuration. The typical values are not tested and are not ensured on shipped production material.

- (4) The typical value is calculated by applying absolute value transform to the distribution, then taking the statistical average of the resulting distribution.

- (5) This parameter is specified by design and/or characterization and is not tested in production.

- 2 Submit Documentation Feedback

#### www.ti.com

## 3.3V Electrical Characteristics<sup>(1)</sup> (continued)

Unless otherwise specified, all limits are specified for at  $T_A = 25^{\circ}C$ ,  $V^+ = 3.3V$ ,  $V^- = 0V$ ,  $V_{CM} = V^+/2$ , and  $R_L = 10 \text{ k}\Omega$  to  $V^+/2$ . **Boldface** limits apply at the temperature extremes.

| Symbol           | Parameter                                       | Conditions                                                                                           |                      | Min<br>(2)        | Тур<br>(3) | Max<br>(2)          | Units                  |  |

|------------------|-------------------------------------------------|------------------------------------------------------------------------------------------------------|----------------------|-------------------|------------|---------------------|------------------------|--|

| I <sub>B</sub>   | Input Bias Current <sup>(5)</sup>               |                                                                                                      |                      |                   | 0.1        | 10<br><b>500</b>    | pА                     |  |

| l <sub>os</sub>  | Input Offset Current                            |                                                                                                      |                      |                   | 1          |                     | pА                     |  |

| CMRR             | Common-Mode Rejection Ratio <sup>(4)</sup>      | $0.2 V \le V_{CM} \le V^+ - 1.2 V$                                                                   |                      | 76<br><b>75</b>   | 91         |                     | dB                     |  |

| PSRR             | Power Supply Rejection Ratio <sup>(4)</sup>     | $2.7V \le V^+ \le 5.5V$ ,<br>$V_{OUT} = 1V$                                                          | 76<br><b>75</b>      | 93                |            | dB                  |                        |  |

| EMIRR            | EMI Rejection Ratio, IN+ and IN- <sup>(6)</sup> | V <sub>RF_PEAK</sub> =100 mV <sub>P</sub> (-20<br>f = 400 MHz                                        | ) dB <sub>P</sub> ), |                   | 80         |                     |                        |  |

|                  |                                                 | V <sub>RF_PEAK</sub> =100 mV <sub>P</sub> (−20<br>f = 900 MHz                                        | ) dB <sub>P</sub> ), |                   | 90         |                     |                        |  |

|                  |                                                 | V <sub>RF_PEAK</sub> =100 mV <sub>P</sub> (−20<br>f = 1800 MHz                                       | ) dB <sub>P</sub> ), |                   | 110        |                     | – dB                   |  |

|                  |                                                 | V <sub>RF_PEAK</sub> =100 mV <sub>P</sub> (-20<br>f = 2400 MHz                                       | ) dB <sub>P</sub> ), |                   | 120        |                     |                        |  |

| CMVR             | Input Common-Mode Voltage Range                 | CMRR ≥ 65 dB                                                                                         |                      | -0.1              |            | 2.1                 | V                      |  |

| A <sub>VOL</sub> | Large Signal Voltage Gain <sup>(7)</sup>        | $ \begin{array}{l} R_{L} = 2 \; k\Omega, \\ V_{OUT} = 0.15 V \; \text{to} \; 1.65 V, \end{array} $   | LMV831,<br>LMV832    | 102<br><b>102</b> | 121        |                     |                        |  |

|                  |                                                 | V <sub>OUT</sub> = 3.15V to 1.65V                                                                    | LMV834               | 102<br><b>102</b> | 121        |                     | dB                     |  |

|                  |                                                 | $\label{eq:RL} \begin{split} R_L &= 10 \; k\Omega, \\ V_{OUT} &= 0.1 V \; to \; 1.65 V, \end{split}$ | LMV831,<br>LMV832    | 104<br><b>104</b> | 126        |                     |                        |  |

|                  |                                                 | V <sub>OUT</sub> = 3.2V to 1.65V                                                                     | LMV834               | 104<br><b>103</b> | 123        |                     |                        |  |

| V <sub>OUT</sub> | Output Voltage Swing High                       | $R_L = 2 k\Omega$ to V <sup>+</sup> /2                                                               | LMV831,<br>LMV832    |                   | 29         | 36<br><b>43</b>     |                        |  |

|                  |                                                 |                                                                                                      | LMV834               |                   | 31         | 38<br><b>44</b>     | mV from<br>either rail |  |

|                  |                                                 | $R_L = 10 \text{ k}\Omega \text{ to V}^+/2$                                                          | LMV831,<br>LMV832    |                   | 6          | 8<br><b>9</b>       |                        |  |

|                  |                                                 |                                                                                                      | LMV834               |                   | 7          | 9<br>10             |                        |  |

|                  | Output Voltage Swing Low                        | $R = 2 k\Omega$ to V <sup>+</sup> /2                                                                 |                      |                   | 25         | 34<br><b>43</b>     |                        |  |

|                  |                                                 | $R_L = 10 \text{ k}\Omega$ to V <sup>+</sup> /2                                                      |                      |                   | 5          | 8<br>10             |                        |  |

| I <sub>OUT</sub> | Output Short Circuit Current                    | Sourcing, $V_{OUT} = V_{CM}$ ,<br>$V_{IN} = 100 \text{ mV}$                                          | LMV831,<br>LMV832    | 27<br><b>22</b>   | 28         |                     |                        |  |

|                  |                                                 |                                                                                                      | LMV834               | 24<br><b>19</b>   | 28         |                     | mA                     |  |

|                  |                                                 | Sinking, $V_{OUT} = V_{CM}$ ,<br>$V_{IN} = -100 \text{ mV}$                                          |                      | 27<br><b>21</b>   | 32         |                     |                        |  |

| I <sub>S</sub>   | Supply Current                                  |                                                                                                      | LMV831               |                   | 0.24       | 0.27<br><b>0.30</b> |                        |  |

|                  |                                                 |                                                                                                      | LMV832               |                   | 0.46       | 0.51<br><b>0.58</b> | mA                     |  |

|                  |                                                 |                                                                                                      | LMV834               |                   | 0.90       | 1.00<br><b>1.16</b> |                        |  |

| SR               | Slew Rate <sup>(8)</sup>                        | A <sub>V</sub> = +1, V <sub>OUT</sub> = 1 V <sub>PP</sub> ,<br>10% to 90%                            |                      |                   | 2          |                     | V/µs                   |  |

(6) The EMI Rejection Ratio is defined as EMIRR = 20log ( $V_{RF_{PEAK}}/\Delta V_{OS}$ ).

(7) The specified limits represent the lower of the measured values for each output range condition.

(8) Number specified is the slower of positive and negative slew rates.

#### SNOSAZ6B-AUGUST 2008-REVISED MARCH 2013

## 3.3V Electrical Characteristics<sup>(1)</sup> (continued)

Unless otherwise specified, all limits are specified for at  $T_A = 25^{\circ}C$ ,  $V^+ = 3.3V$ ,  $V^- = 0V$ ,  $V_{CM} = V^+/2$ , and  $R_L = 10 \text{ k}\Omega$  to  $V^+/2$ . **Boldface** limits apply at the temperature extremes.

| Symbol           | Parameter                            | Conditions                                  | Min<br>(2) | Тур<br>(3) | Max<br>(2) | Units  |

|------------------|--------------------------------------|---------------------------------------------|------------|------------|------------|--------|

| GBW              | Gain Bandwidth Product               |                                             |            | 3.3        |            | MHz    |

| Φ <sub>m</sub>   | Phase Margin                         |                                             |            | 65         |            | deg    |

| e <sub>n</sub>   | Input Referred Voltage Noise Density | f = 1 kHz                                   |            | 12         |            | nV/√Hz |

|                  |                                      | f = 10 kHz                                  |            | 10         |            | NV/VHZ |

| i <sub>n</sub>   | Input Referred Current Noise Density | f = 1 kHz                                   |            | 0.005      |            | pA/√Hz |

| R <sub>OUT</sub> | Closed Loop Output Impedance         | f = 2 MHz                                   |            | 500        |            | Ω      |

| C <sub>IN</sub>  | Common-mode Input Capacitance        |                                             |            | 15         |            | - 5    |

|                  | Differential-mode Input Capacitance  |                                             |            | 20         |            | pF     |

| THD+N            | Total Harmonic Distortion + Noise    | f = 1 kHz, A <sub>V</sub> = 1, BW ≥ 500 kHz |            | 0.02       |            | %      |

### 5V Electrical Characteristics<sup>(1)</sup>

Unless otherwise specified, all limits are specified for at  $T_A = 25^{\circ}C$ ,  $V^+ = 5V$ ,  $V^- = 0V$ ,  $V_{CM} = V^+/2$ , and  $R_L = 10 \text{ k}\Omega$  to  $V^+/2$ . **Boldface** limits apply at the temperature extremes.

| Symbol            | Parameter                                                | Conditions                                                     |                    |                 | Тур<br>(3)       | Max<br>(2)            | Units |

|-------------------|----------------------------------------------------------|----------------------------------------------------------------|--------------------|-----------------|------------------|-----------------------|-------|

| V <sub>OS</sub>   | Input Offset Voltage <sup>(4)</sup>                      | It Offset Voltage <sup>(4)</sup>                               |                    |                 | ±0.25            | ±1.00<br><b>±1.23</b> | mV    |

| TCV <sub>OS</sub> | Input Offset Voltage Temperature Drift <sup>(4)(5)</sup> |                                                                | LMV831,<br>LMV832  |                 | ±0.5             | ±1.5                  | µV/°C |

|                   |                                                          |                                                                | LMV834             |                 | ±0.5             | ±1.7                  |       |

| IB                | Input Bias Current <sup>(5)</sup>                        |                                                                |                    | 0.1             | 10<br><b>500</b> | pА                    |       |

| l <sub>os</sub>   | Input Offset Current                                     |                                                                |                    |                 | 1                |                       | pА    |

| CMRR              | Common-Mode Rejection Ratio <sup>(4)</sup>               | $0V \le V_{CM} \le V^+ - 1.2V$                                 |                    | 77<br><b>77</b> | 93               |                       | dB    |

| PSRR              | Power Supply Rejection Ratio <sup>(4)</sup>              | $2.7V \le V^+ \le 5.5V,$<br>$V_{OUT} = 1V$                     |                    | 76<br><b>75</b> | 93               |                       | dB    |

| EMIRR             | EMI Rejection Ratio, IN+ and IN- <sup>(6)</sup>          | V <sub>RF_PEAK</sub> =100 mV <sub>P</sub> (-20<br>f = 400 MHz  | dB <sub>P</sub> ), |                 | 80               |                       |       |

|                   |                                                          | V <sub>RF_PEAK</sub> =100 mV <sub>P</sub> (-20<br>f = 900 MHz  | dB <sub>P</sub> ), |                 | 90               |                       | - dB  |

|                   |                                                          | V <sub>RF_PEAK</sub> =100 mV <sub>P</sub> (−20<br>f = 1800 MHz | dB <sub>P</sub> ), |                 | 110              |                       | uв    |

|                   |                                                          | V <sub>RF_PEAK</sub> =100 mV <sub>P</sub> (-20<br>f = 2400 MHz |                    | 120             |                  |                       |       |

| CMVR              | Input Common-Mode Voltage Range                          | CMRR ≥ 65 dB                                                   |                    | -0.1            |                  | 3.8                   | V     |

- (1) Electrical Table values apply only for factory testing conditions at the temperature indicated. Factory testing conditions result in very limited self-heating of the device such that  $T_J = T_A$ . No specification of parametric performance is indicated in the electrical tables under conditions of internal self-heating where  $T_J > T_A$ .

- (2) Limits are 100% production tested at 25°C. Limits over the operating temperature range are specified through correlations using statistical quality control (SQC) method.

- (3) Typical values represent the most likely parametric norm as determined at the time of characterization. Actual typical values may vary over time and will also depend on the application and configuration. The typical values are not tested and are not ensured on shipped production material.

- (4) The typical value is calculated by applying absolute value transform to the distribution, then taking the statistical average of the resulting distribution.

- (5) This parameter is specified by design and/or characterization and is not tested in production.

- (6) The EMI Rejection Ratio is defined as EMIRR = 20log ( $V_{RF_PEAK}/\Delta V_{OS}$ ).

- 4 Submit Documentation Feedback

#### www.ti.com

## 5V Electrical Characteristics<sup>(1)</sup> (continued)

Unless otherwise specified, all limits are specified for at  $T_A = 25^{\circ}C$ ,  $V^+ = 5V$ ,  $V^- = 0V$ ,  $V_{CM} = V^+/2$ , and  $R_L = 10 \text{ k}\Omega$  to  $V^+/2$ . **Boldface** limits apply at the temperature extremes.

| Symbol                             | Parameter                                                    | Conditions                                                                                        | 5                 | Min<br>(2)        | <b>Тур</b><br>(3) | Max<br>(2)          | Units              |

|------------------------------------|--------------------------------------------------------------|---------------------------------------------------------------------------------------------------|-------------------|-------------------|-------------------|---------------------|--------------------|

| A <sub>VOL</sub>                   | Large Signal Voltage Gain <sup>(7)</sup>                     | $ \begin{array}{l} R_{L} = 2 \; k\Omega, \\ V_{OUT} = 0.15 V \; \text{to} \; 2.5 V, \end{array} $ | LMV831,<br>LMV832 | 107<br><b>106</b> | 127               |                     |                    |

|                                    |                                                              | V <sub>OUT</sub> = 4.85V to 2.5V                                                                  | LMV834            | 104<br><b>104</b> | 127               |                     |                    |

|                                    |                                                              |                                                                                                   | LMV831,<br>LMV832 | 107<br><b>107</b> | 130               |                     | – dB               |

|                                    |                                                              | $V_{OUT} = 4.9V \text{ to } 2.5V$                                                                 | LMV834            | 105<br><b>104</b> | 127               |                     |                    |

| V <sub>OUT</sub>                   | Output Voltage Swing High                                    | $R_L = 2 k\Omega$ to V <sup>+</sup> /2                                                            | LMV831,<br>LMV832 |                   | 32                | 42<br><b>49</b>     |                    |

|                                    |                                                              |                                                                                                   | LMV834            |                   | 35                | 45<br><b>52</b>     |                    |

|                                    |                                                              | $R_L = 10 \text{ k}\Omega \text{ to } V^+/2$                                                      | LMV831,<br>LMV832 |                   | 6                 | 9<br><b>10</b>      | mV from            |

|                                    |                                                              |                                                                                                   | LMV834            |                   | 7                 | 10<br><b>11</b>     | either rail        |

|                                    | Output Voltage Swing Low $R_L = 2 k\Omega \text{ to } V^+/2$ |                                                                                                   |                   |                   | 27                | 43<br><b>52</b>     | 1                  |

|                                    |                                                              | $R_L = 10 \text{ k}\Omega \text{ to V}^+/2$                                                       |                   |                   | 6                 | 10<br><b>12</b>     |                    |

| I <sub>OUT</sub>                   | Output Short Circuit Current                                 | Sourcing $V_{OUT} = V_{CM}$<br>$V_{IN} = 100 \text{ mV}$                                          | LMV831,<br>LMV832 | 59<br><b>49</b>   | 66                |                     |                    |

|                                    |                                                              |                                                                                                   | LMV834            | 57<br>45          | 63                |                     |                    |

|                                    |                                                              | Sinking $V_{OUT} = V_{CM}$<br>$V_{IN} = -100 \text{ mV}$                                          | LMV831,<br>LMV832 | 50<br><b>41</b>   | 64                |                     | – mA               |

|                                    |                                                              |                                                                                                   | LMV834            | 53<br>41          | 63                |                     |                    |

| I <sub>S</sub>                     | Supply Current                                               |                                                                                                   | LMV831            |                   | 0.25              | 0.27<br><b>0.31</b> |                    |

|                                    |                                                              |                                                                                                   | LMV832            |                   | 0.47              | 0.52<br><b>0.60</b> | mA                 |

|                                    |                                                              |                                                                                                   | LMV834            |                   | 0.92              | 1.02<br><b>1.18</b> |                    |

| SR                                 | Slew Rate <sup>(8)</sup>                                     | A <sub>V</sub> = +1, V <sub>OUT</sub> = 2V <sub>PP</sub> ,<br>10% to 90%                          |                   |                   | 2                 |                     | V/µs               |

| GBW                                | Gain Bandwidth Product                                       |                                                                                                   |                   |                   | 3.3               |                     | MHz                |

| Φ <sub>m</sub>                     | Phase Margin                                                 |                                                                                                   |                   |                   | 65                |                     | deg                |

| e <sub>n</sub>                     | Input Referred Voltage Noise                                 | f = 1 kHz<br>f = 10 kHz                                                                           |                   |                   | 12<br>10          |                     | nV/√Hz             |

| i                                  | Input Referred Current Noise                                 | f = 1  kHz                                                                                        |                   |                   | 0.005             |                     | pA/√ <del>Hz</del> |

| i <sub>n</sub><br>R <sub>OUT</sub> | Closed Loop Output Impedance                                 | f = 2 MHz                                                                                         |                   |                   | 500               |                     | Ω                  |

| C <sub>IN</sub>                    | Common-mode Input Capacitance                                |                                                                                                   |                   |                   | 14                |                     |                    |

|                                    | Differential-mode Input Capacitance                          |                                                                                                   |                   |                   | 20                |                     | pF                 |

| THD+N                              | Total Harmonic Distortion + Noise                            | f = 1 kHz, A <sub>V</sub> = 1, BW 2                                                               | ≥ 500 kHz         |                   | 0.02              |                     | %                  |

(7) The specified limits represent the lower of the measured values for each output range condition.

(8) Number specified is the slower of positive and negative slew rates.

## LMV831, LMV832, LMV834

www.ti.com

SNOSAZ6B-AUGUST 2008-REVISED MARCH 2013

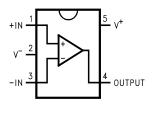

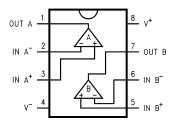

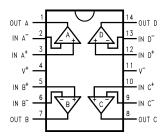

## **Connection Diagram**

Figure 2. 5-Pin SC70 Top View

Figure 3. 8-Pin VSSOP Top View

Figure 4. 14-Pin TSSOP Top View

6

## LMV831, LMV832, LMV834

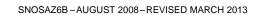

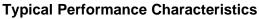

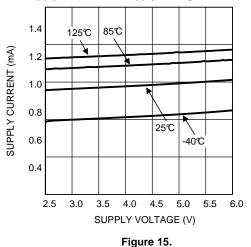

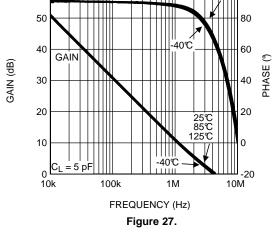

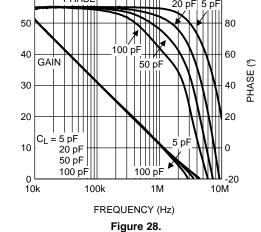

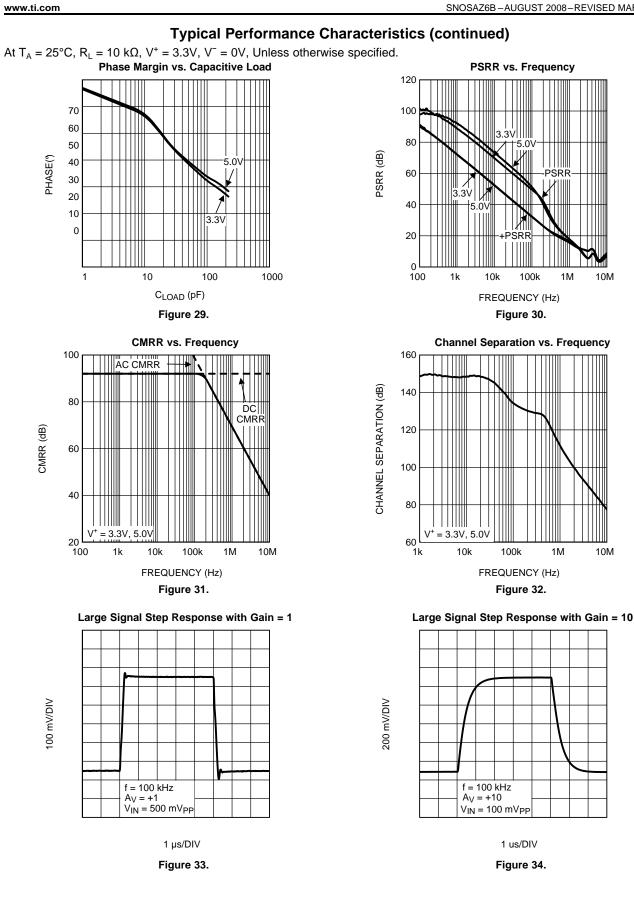

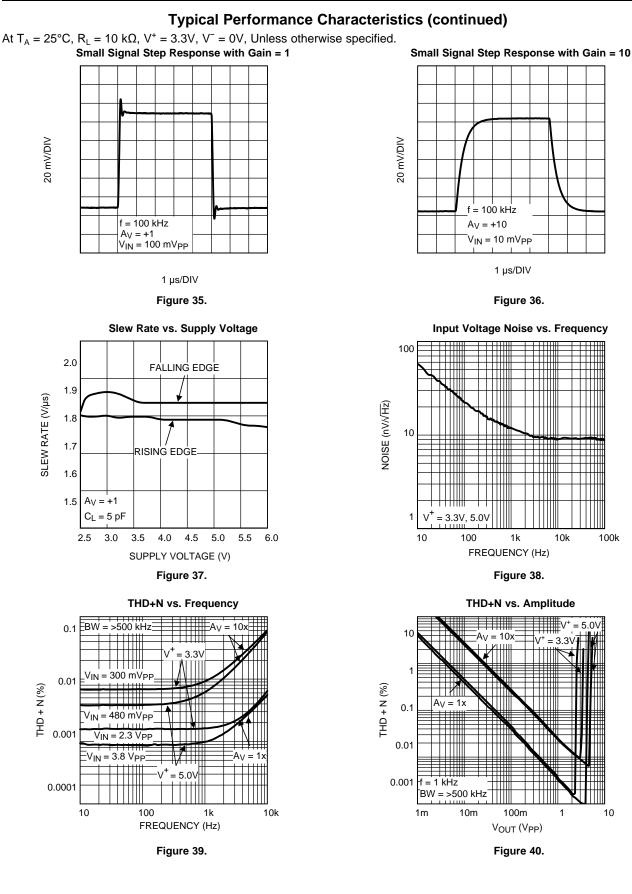

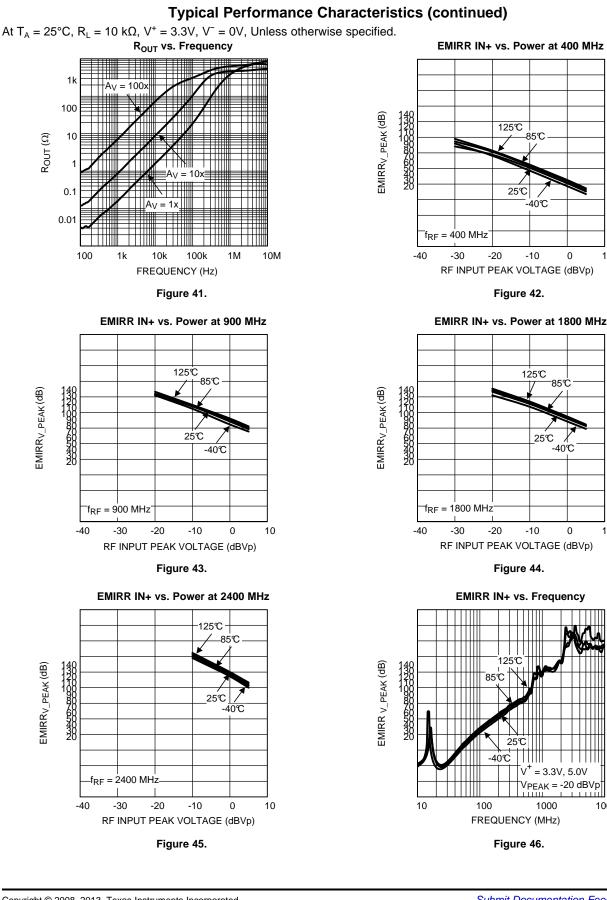

At  $T_A = 25^{\circ}C$ ,  $R_L = 10 \text{ k}\Omega$ ,  $V^+ = 3.3V$ ,  $V^- = 0V$ , Unless otherwise specified.

Copyright © 2008–2013, Texas Instruments Incorporated

Submit Documentation Feedback 7

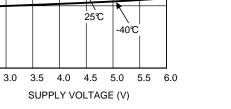

Figure 13.

Supply Current vs. Supply Voltage Quad LMV834

Supply Current vs. Temperature Single LMV831

SUPPLY VOLTAGE (V)

Figure 14.

4.0 4.5 -40℃

5.0

5.5

6.0

0.3

2.5

3.0 3.5

STRUMENTS

EXAS

6

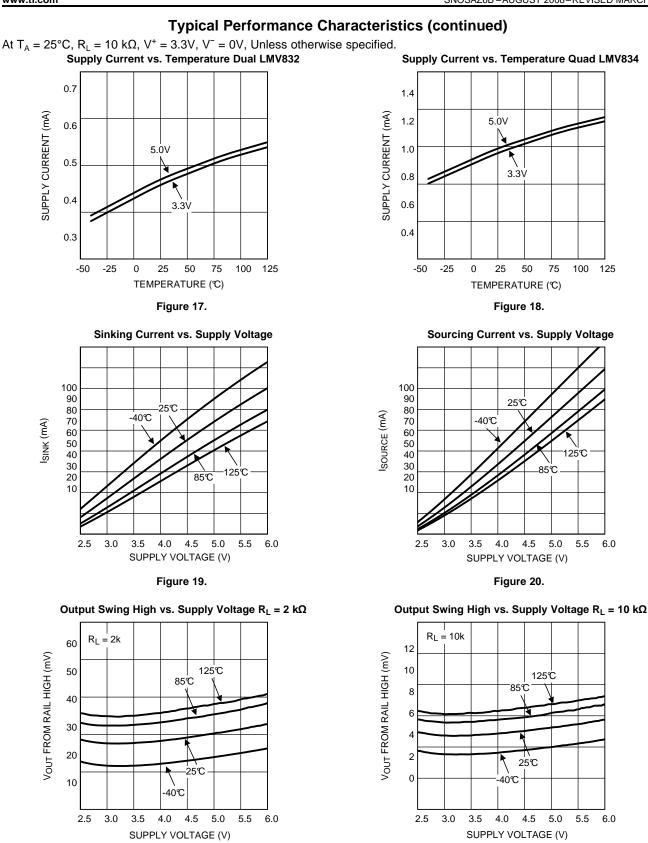

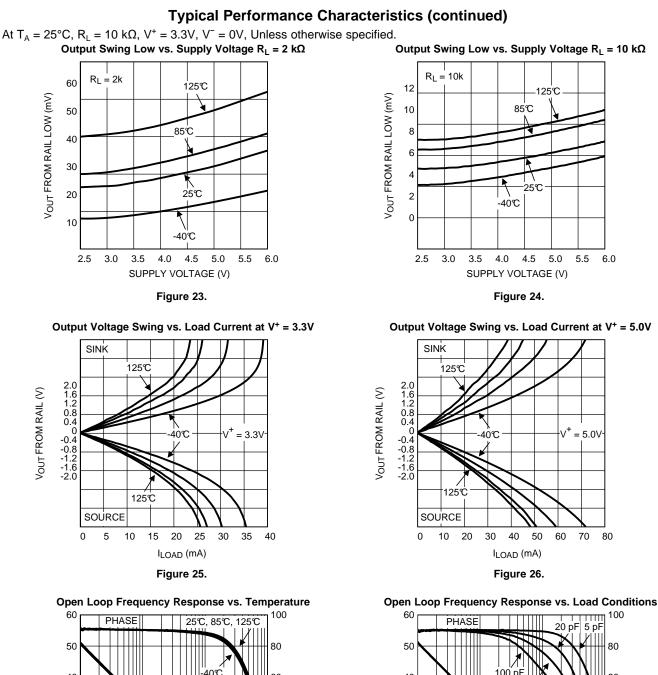

## **Typical Performance Characteristics (continued)**

8

0.1

2.5

Figure 22.

Copyright © 2008–2013, Texas Instruments Incorporated

### www.ti.com

## XAS STRUMENTS

Figure 21.

GAIN (dB)

www.ti.com

#### www

**EXAS**

ISTRUMENTS

www.ti.com

Copyright © 2008–2013, Texas Instruments Incorporated

10

10

10

#### SNOSAZ6B-AUGUST 2008-REVISED MARCH 2013

**EXAS**

www.ti.com

**NSTRUMENTS**

10000

www.ti.com

## **APPLICATION INFORMATION**

### INTRODUCTION

The LMV831, LMV832 and LMV834 are operational amplifiers with excellent specifications, such as low offset, low noise and a rail-to-rail output. These specifications make the LMV831, LMV832 and LMV834 great choices for medical and instrumentation applications such as diagnosis equipment. The low supply current is perfectly suited for battery powered equipment. The small packages, SC70 package for the LMV831, the TSSOP package for the dual LMV832 and the TSSOP package for the quad LMV834, make these parts a perfect choice for portable electronics. Additionally, the EMI hardening makes the LMV831, LMV832 or LMV834 a must for almost all op amp applications. Most applications are exposed to Radio Frequency (RF) signals such as the signals transmitted by mobile phones or wireless computer peripherals. The LMV831, LMV832 and LMV834 will effectively reduce disturbances caused by RF signals to a level that will be hardly noticeable. This again reduces the need for additional filtering and shielding. Using this EMI resistant series of op amps will thus reduce the number of components and space needed for applications that are affected by EMI, and will help applications, not yet identified as possible EMI sensitive, to be more robust for EMI.

### INPUT CHARACTERISTICS

The input common mode voltage range of the LMV831, LMV832 and LMV834 includes ground, and can even sense well below ground. The CMRR level does not degrade for input levels up to 1.2V below the supply voltage. For a supply voltage of 5V, the maximum voltage that should be applied to the input for best CMRR performance is thus 3.8V.

When not configured as unity gain, this input limitation will usually not degrade the effective signal range. The output is rail-to-rail and therefore will introduce no limitations to the signal range.

The typical offset is only 0.25 mV, and the TCV<sub>OS</sub> is 0.5  $\mu$ V/°C, specifications close to precision op amps.

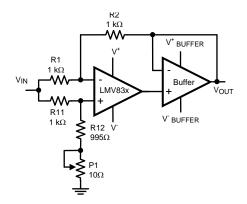

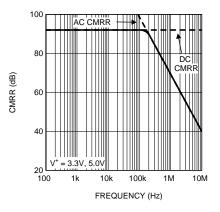

### **CMRR MEASUREMENT**

The CMRR measurement results may need some clarification. This is because different setups are used to measure the AC CMRR and the DC CMRR.

The DC CMRR is derived from  $\Delta V_{OS}$  versus  $\Delta V_{CM}$ . This value is stated in the tables, and is tested during production testing. The AC CMRR is measured with the test circuit shown in Figure 47.

Figure 47. AC CMRR Measurement Setup

The configuration is largely the usually applied balanced configuration. With potentiometer P1, the balance can be tuned to compensate for the DC offset in the DUT. The main difference is the addition of the buffer. This buffer prevents the open-loop output impedance of the DUT from affecting the balance of the feedback network. Now the closed-loop output impedance of the buffer is a part of the balance. As the closed-loop output impedance is much lower, and by careful selection of the buffer also has a larger bandwidth, the total effect is that the CMRR of the DUT can be measured much more accurately. The differences are apparent in the larger measured bandwidth of the AC CMRR.

SNOSAZ6B-AUGUST 2008-REVISED MARCH 2013

One artifact from this test circuit is that the low frequency CMRR results appear higher than expected. This is because in the AC CMRR test circuit the potentiometer is used to compensate for the DC mismatches. So, mainly AC mismatch is all that remains. Therefore, the obtained DC CMRR from this AC CMRR test circuit tends to be higher than the actual DC CMRR based on DC measurements.

The CMRR curve in Figure 48 shows a combination of the AC CMRR and the DC CMRR.

Figure 48. CMRR Curve

### **OUTPUT CHARACTERISTICS**

As already mentioned the output is rail-to-rail. When loading the output with a 10 k $\Omega$  resistor the maximum swing of the output is typically 6 mV from the positive and negative rail.

The output of the LMV831/LMV832/LMV834 can drive currents up to 30 mA at 3.3V and even up to 65 mA at 5V

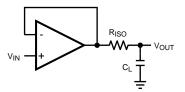

The LMV831/LMV832/LMV834 can be connected as non-inverting unity-gain amplifiers. This configuration is the most sensitive to capacitive loading. The combination of a capacitive load placed at the output of an amplifier along with the amplifier's output impedance creates a phase lag, which reduces the phase margin of the amplifier. If the phase margin is significantly reduced, the response will be under damped which causes peaking in the transfer and, when there is too much peaking, the op amp might start oscillating. The LMV831/LMV832/LMV834 can directly drive capacitive loads up to 200 pF without any stability issues. In order to drive heavier capacitive loads, an isolation resistor,  $R_{\rm ISO}$ , should be used, as shown in Figure 49. By using this isolation resistor, the capacitive load is isolated from the amplifier's output, and hence, the pole caused by  $C_{\rm L}$  is no longer in the feedback loop. The larger the value of  $R_{\rm ISO}$ , the more stable the amplifier will be. If the value of  $R_{\rm ISO}$  result in reduced output swing and reduced output current drive.

Figure 49. Isolating Capacitive Load

A resistor value of around  $150\Omega$  would be sufficient. As an example some values are given in the following table, for 5V.

| C <sub>LOAD</sub> | R <sub>ISO</sub> |

|-------------------|------------------|

| 300 pF            | 165Ω             |

| 400 pF            | 175Ω             |

| 500 pF            | 185Ω             |

### EMIRR

With the increase of RF transmitting devices in the world, the electromagnetic interference (EMI) between those devices and other equipment becomes a bigger challenge. The LMV831, LMV832 and LMV834 are EMI hardened op amps which are specifically designed to overcome electromagnetic interference. Along with EMI hardened op amps, the EMIRR parameter is introduced to unambiguously specify the EMI performance of an op amp. This section presents an overview of EMIRR. A detailed description on this specification for EMI hardened op amps can be found in Application Note AN-1698(SNOA497).

The dimensions of an op amp IC are relatively small compared to the wavelength of the disturbing RF signals. As a result the op amp itself will hardly receive any disturbances. The RF signals interfering with the op amp are dominantly received by the PCB and wiring connected to the op amp. As a result the RF signals on the pins of the op amp can be represented by voltages and currents. This representation significantly simplifies the unambiguous measurement and specification of the EMI performance of an op amp.

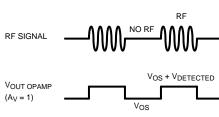

RF signals interfere with op amps via the non-linearity of the op amp circuitry. This non-linearity results in the detection of the so called out-of-band signals. The obtained effect is that the amplitude modulation of the out-of-band signal is downconverted into the base band. This base band can easily overlap with the band of the op amp circuit. As an example Figure 50 depicts a typical output signal of a unity-gain connected op amp in the presence of an interfering RF signal. Clearly the output voltage varies in the rhythm of the on-off keying of the RF carrier.

Figure 50. Offset voltage variation due to an interfering RF signal

## EMIRR DEFINITION

To identify EMI hardened op amps, a parameter is needed that quantitatively describes the EMI performance of op amps. A quantitative measure enables the comparison and the ranking of op amps on their EMI robustness. Therefore the EMI Rejection Ratio (EMIRR) is introduced. This parameter describes the resulting input-referred offset voltage shift of an op amp as a result of an applied RF carrier (interference) with a certain frequency and level. The definition of EMIRR is given by:

$$\mathsf{EMIRR}_{\mathsf{V}_{\mathsf{RF}}\mathsf{PEAK}} = 20 \log \left( \frac{\mathsf{V}_{\mathsf{RF}}\mathsf{PEAK}}{\Delta \mathsf{V}_{\mathsf{OS}}} \right)$$

In which

- V<sub>RF\_PEAK</sub> is the amplitude of the applied un-modulated RF signal (V)

- $\Delta V_{OS}$  is the resulting input-referred offset voltage shift (V)

The offset voltage depends quadratically on the applied RF level, and therefore, the RF level at which the EMIRR is determined should be specified. The standard level for the RF signal is 100 mV<sub>P</sub>. Application Note AN-1698(SNOA497) addresses the conversion of an EMIRR measured for an other signal level than 100 mV<sub>P</sub>. The interpretation of the EMIRR parameter is straightforward. When two op amps have an EMIRR which differ by 20 dB, the resulting error signals when used in identical configurations, differ by 20 dB as well. So, the higher the EMIRR, the more robust the op amp.

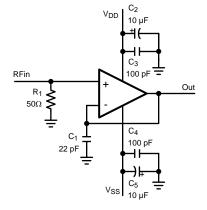

### Coupling an RF Signal to the IN+ Pin

Each of the op amp pins can be tested separately on EMIRR. In this section the measurements on the IN+ pin (which, based on symmetry considerations, also apply to the IN- pin) are discussed. In Application Note AN-1698(SNOA497) the other pins of the op amp are treated as well. For testing the IN+ pin the op amp is connected in the unity gain configuration. Applying the RF signal is straightforward as it can be connected directly to the IN+ pin. As a result the RF signal path has a minimum of components that might affect the RF

#### SNOSAZ6B-AUGUST 2008-REVISED MARCH 2013

signal level at the pin. The circuit diagram is shown in Figure 51. The PCB trace from  $RF_{IN}$  to the IN+ pin should be a 50 $\Omega$  stripline in order to match the RF impedance of the cabling and the RF generator. On the PCB a 50 $\Omega$ termination is used. This 50 $\Omega$  resistor is also used to set the bias level of the IN+ pin to ground level. For determining the EMIRR, two measurements are needed: one is measuring the DC output level when the RF signal is off; and the other is measuring the DC output level when the RF signal is switched on. The difference of the two DC levels is the output voltage shift as a result of the RF signal. As the op amp is in the unity gain configuration, the input referred offset voltage shift corresponds one-to-one to the measured output voltage shift.

Figure 51. Circuit for coupling the RF signal to IN+

#### Cell Phone Call

The effect of electromagnetic interference is demonstrated in a setup where a cell phone interferes with a pressure sensor application. The application is shown in Figure 53.

This application needs two op amps and therefore a dual op amp is used. The op amp configured as a buffer and connected at the negative output of the pressure sensor prevents the loading of the bridge by resistor R2. The buffer also prevents the resistors of the sensor from affecting the gain of the following gain stage. The op amps are placed in a single supply configuration.

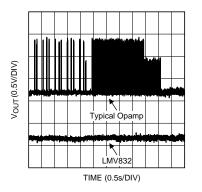

The experiment is performed on two different dual op amps: a typical standard op amp and the LMV832, EMI hardened dual op amp. A cell phone is placed on a fixed position a couple of centimeters from the op amps in the sensor circuit.

When the cell phone is called, the PCB and wiring connected to the op amps receive the RF signal. Subsequently, the op amps detect the RF voltages and currents that end up at their pins. The resulting effect on the output of the second op amp is shown in Figure 52.

#### SNOSAZ6B-AUGUST 2008-REVISED MARCH 2013

The difference between the two types of dual op amps is clearly visible. The typical standard dual op amp has an output shift (disturbed signal) larger than 1V as a result of the RF signal transmitted by the cell phone. The LMV832, EMI hardened op amp does not show any significant disturbances. This means that the RF signal will not disturb the signal entering the ADC when using the LMV832.

Figure 53. Pressure Sensor Application

## DECOUPLING AND LAYOUT

Care must be given when creating a board layout for the op amp. For decoupling the supply lines it is suggested that 10 nF capacitors be placed as close as possible to the op amp. For single supply, place a capacitor between V<sup>+</sup> and V<sup>-</sup>. For dual supplies, place one capacitor between V<sup>+</sup> and the board ground, and a second capacitor between ground and V<sup>-</sup>. Even with the LMV831/LMV832/LMV834 inherent hardening against EMI, it is still recommended to keep the input traces short and as far as possible from RF sources. Then the RF signals entering the chip are as low as possible, and the remaining EMI can be, almost, completely eliminated in the chip by the EMI reducing features of the LMV831/LMV832/LMV834.

## PRESSURE SENSOR APPLICATION

The LMV831/LMV832/LMV834 can be used for pressure sensor applications. Because of their low power the LMV831/LMV832/LMV834 are ideal for portable applications, such as blood pressure measurement devices, or portable barometers. This example describes a universal pressure sensor that can be used as a starting point for different types of sensors and applications.

### **Pressure Sensor Characteristics**

The pressure sensor used in this example functions as a Wheatstone bridge. The value of the resistors in the bridge change when pressure is applied to the sensor. This change of the resistor values will result in a differential output voltage, depending on the sensitivity of the sensor and the applied pressure. The difference between the output at full scale pressure and the output at zero pressure is defined as the span of the pressure sensor. A typical value for the span is 100 mV. A typical value for the resistors in the bridge is 5 k $\Omega$ . Loading of the resistor bridge could result in incorrect output voltages of the sensor. Therefore the selection of the circuit configuration, which connects to the sensor, should take into account a minimum loading of the sensor.

### Pressure Sensor Example

The configuration shown in Figure 53 is simple, and is very useful for the read out of pressure sensors. With two op amps in this application, the dual LMV832 fits very well. The op amp configured as a buffer and connected at the negative output of the pressure sensor prevents the loading of the bridge by resistor R2. The buffer also prevents the resistors of the sensor from affecting the gain of the following gain stage. Given the differential output voltage  $V_S$  of the pressure sensor, the output signal of this op amp configuration,  $V_{OUT}$ , equals:

$$V_{OUT} = \frac{V_{DD}}{2} - \frac{V_{S}}{2} \left( 1 + 2x \frac{R1}{R2} \right)$$

(2)

To align the pressure range with the full range of an ADC, the power supply voltage and the span of the pressure sensor are needed. For this example a power supply of 5V is used and the span of the sensor is 100 mV. When a 100 $\Omega$  resistor is used for R2, and a 2.4 k $\Omega$  resistor is used for R1, the maximum voltage at the output is 4.95V and the minimum voltage is 0.05V. This signal is covering almost the full input range of the ADC. Further processing can take place in the microprocessor following the ADC.

Copyright © 2008–2013, Texas Instruments Incorporated

## **REVISION HISTORY**

| Cł | nanges from Revision A (March 2013) to Revision B P | age  |

|----|-----------------------------------------------------|------|

| •  | Changed layout of National Data Sheet to TI format  | . 18 |

Texas

NSTRUMENTS

#### Dago

19

Submit Documentation Feedback

## PACKAGING INFORMATION

| Orderable Device | Status<br>(1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan<br>(2) | Lead finish/<br>Ball material | MSL Peak Temp      | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|---------------|--------------|--------------------|------|----------------|-----------------|-------------------------------|--------------------|--------------|-------------------------|---------|

|                  | (1)           |              | 2.4                |      | ,              | (2)             | (6)                           | (3)                |              | (4/3)                   |         |

| LMV831MG/NOPB    | ACTIVE        | SC70         | DCK                | 5    | 1000           | RoHS & Green    | SN                            | Level-1-260C-UNLIM | -40 to 125   | AFA                     | Samples |

| LMV831MGE/NOPB   | ACTIVE        | SC70         | DCK                | 5    | 250            | RoHS & Green    | SN                            | Level-1-260C-UNLIM | -40 to 125   | AFA                     | Samples |

| LMV831MGX/NOPB   | ACTIVE        | SC70         | DCK                | 5    | 3000           | RoHS & Green    | SN                            | Level-1-260C-UNLIM | -40 to 125   | AFA                     | Samples |

| LMV832MM/NOPB    | ACTIVE        | VSSOP        | DGK                | 8    | 1000           | RoHS & Green    | SN                            | Level-1-260C-UNLIM | -40 to 125   | AU5A                    | Samples |

| LMV832MME/NOPB   | ACTIVE        | VSSOP        | DGK                | 8    | 250            | RoHS & Green    | SN                            | Level-1-260C-UNLIM | -40 to 125   | AU5A                    | Samples |

| LMV832MMX/NOPB   | ACTIVE        | VSSOP        | DGK                | 8    | 3500           | RoHS & Green    | SN                            | Level-1-260C-UNLIM | -40 to 125   | AU5A                    | Samples |

| LMV834MT/NOPB    | ACTIVE        | TSSOP        | PW                 | 14   | 94             | RoHS & Green    | SN                            | Level-1-260C-UNLIM | -40 to 125   | LMV834<br>MT            | Samples |

| LMV834MTX/NOPB   | ACTIVE        | TSSOP        | PW                 | 14   | 2500           | RoHS & Green    | SN                            | Level-1-260C-UNLIM | -40 to 125   | LMV834<br>MT            | Samples |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

**PREVIEW:** Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

<sup>(3)</sup> MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

<sup>(5)</sup> Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

10-Dec-2020

(6) Lead finish/Ball material - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:**The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

## PACKAGE MATERIALS INFORMATION

Texas Instruments

www.ti.com

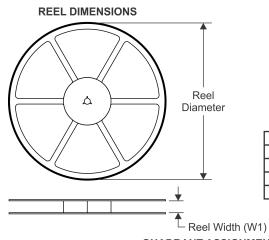

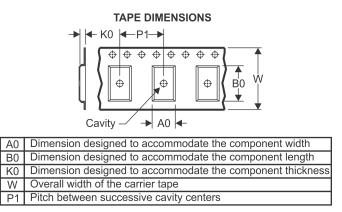

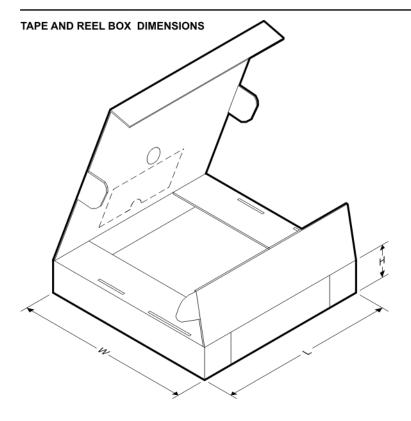

## TAPE AND REEL INFORMATION

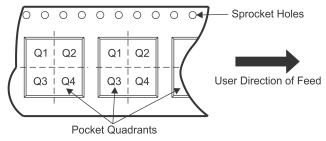

## QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| *All dimensions are nominal |                 |                    |    |      |                          |                          |            |            |            |            |           |                  |

|-----------------------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| Device                      | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

| LMV831MG/NOPB               | SC70            | DCK                | 5  | 1000 | 178.0                    | 8.4                      | 2.25       | 2.45       | 1.2        | 4.0        | 8.0       | Q3               |

| LMV831MGE/NOPB              | SC70            | DCK                | 5  | 250  | 178.0                    | 8.4                      | 2.25       | 2.45       | 1.2        | 4.0        | 8.0       | Q3               |

| LMV831MGX/NOPB              | SC70            | DCK                | 5  | 3000 | 178.0                    | 8.4                      | 2.25       | 2.45       | 1.2        | 4.0        | 8.0       | Q3               |

| LMV832MM/NOPB               | VSSOP           | DGK                | 8  | 1000 | 178.0                    | 12.4                     | 5.3        | 3.4        | 1.4        | 8.0        | 12.0      | Q1               |

| LMV832MME/NOPB              | VSSOP           | DGK                | 8  | 250  | 178.0                    | 12.4                     | 5.3        | 3.4        | 1.4        | 8.0        | 12.0      | Q1               |

| LMV832MMX/NOPB              | VSSOP           | DGK                | 8  | 3500 | 330.0                    | 12.4                     | 5.3        | 3.4        | 1.4        | 8.0        | 12.0      | Q1               |

| LMV834MTX/NOPB              | TSSOP           | PW                 | 14 | 2500 | 330.0                    | 12.4                     | 6.95       | 5.6        | 1.6        | 8.0        | 12.0      | Q1               |

## PACKAGE MATERIALS INFORMATION

5-Jan-2022

\*All dimensions are nominal

| Device         | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|----------------|--------------|-----------------|------|------|-------------|------------|-------------|

| LMV831MG/NOPB  | SC70         | DCK             | 5    | 1000 | 208.0       | 191.0      | 35.0        |

| LMV831MGE/NOPB | SC70         | DCK             | 5    | 250  | 208.0       | 191.0      | 35.0        |

| LMV831MGX/NOPB | SC70         | DCK             | 5    | 3000 | 208.0       | 191.0      | 35.0        |

| LMV832MM/NOPB  | VSSOP        | DGK             | 8    | 1000 | 208.0       | 191.0      | 35.0        |

| LMV832MME/NOPB | VSSOP        | DGK             | 8    | 250  | 208.0       | 191.0      | 35.0        |

| LMV832MMX/NOPB | VSSOP        | DGK             | 8    | 3500 | 367.0       | 367.0      | 35.0        |

| LMV834MTX/NOPB | TSSOP        | PW              | 14   | 2500 | 367.0       | 367.0      | 35.0        |

5-Jan-2022

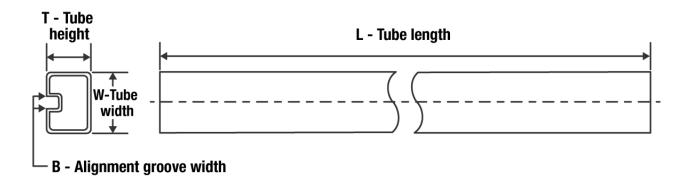

## TUBE

#### \*All dimensions are nominal

| Device        | Package Name | Package Type | Pins | SPQ | L (mm) | W (mm) | Τ (μm) | B (mm) |

|---------------|--------------|--------------|------|-----|--------|--------|--------|--------|

| LMV834MT/NOPB | PW           | TSSOP        | 14   | 94  | 495    | 8      | 2514.6 | 4.06   |

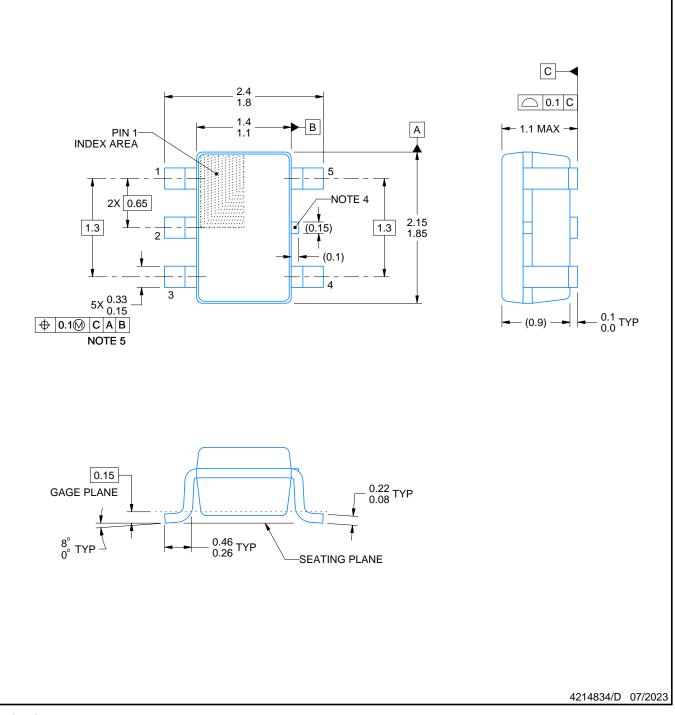

# **DCK0005A**

## **PACKAGE OUTLINE**

## SOT - 1.1 max height

SMALL OUTLINE TRANSISTOR

NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

This drawing is subject to change without notice.

Reference JEDEC MO-203.

- 4. Support pin may differ or may not be present.5. Lead width does not comply with JEDEC.

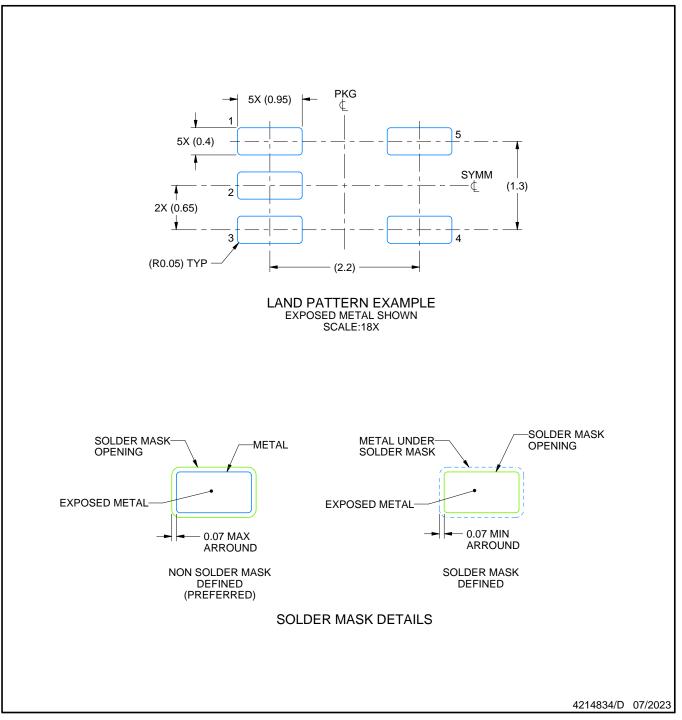

## **DCK0005A**

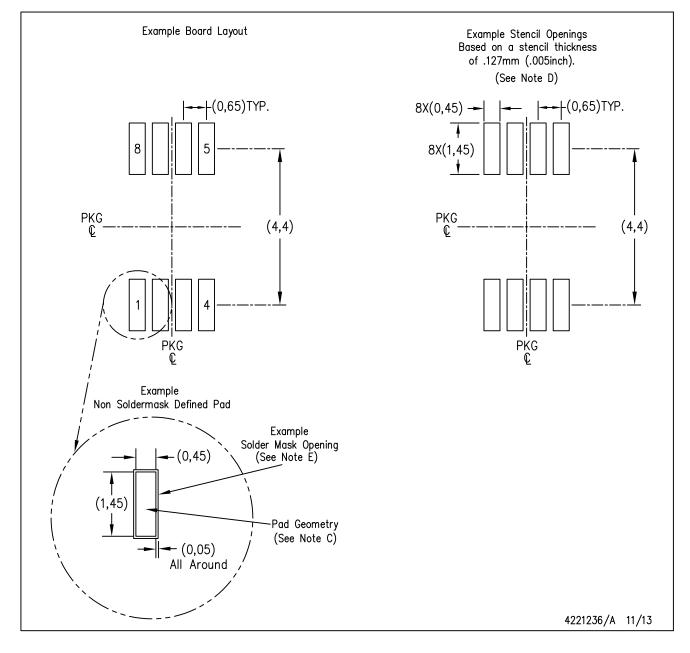

## **EXAMPLE BOARD LAYOUT**

## SOT - 1.1 max height

SMALL OUTLINE TRANSISTOR

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

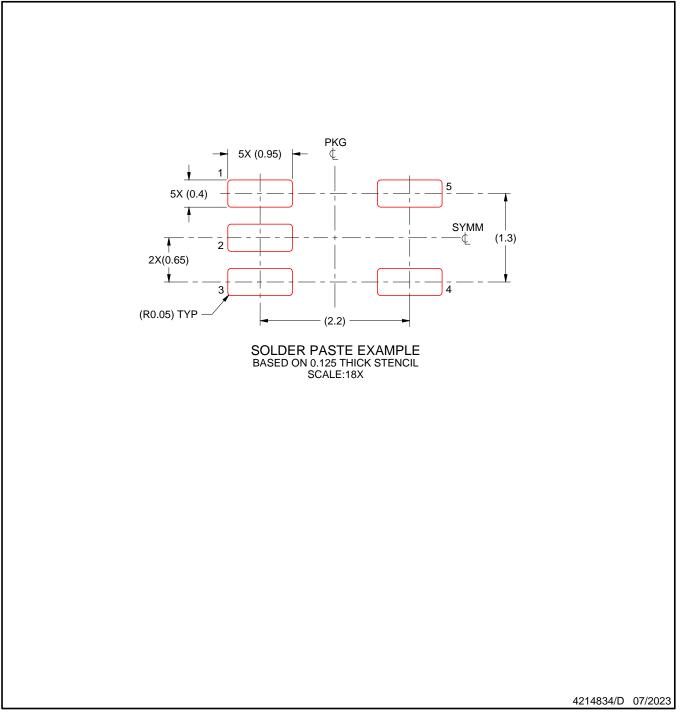

## DCK0005A

# **EXAMPLE STENCIL DESIGN**

## SOT - 1.1 max height

SMALL OUTLINE TRANSISTOR

NOTES: (continued)

8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

9. Board assembly site may have different recommendations for stencil design.

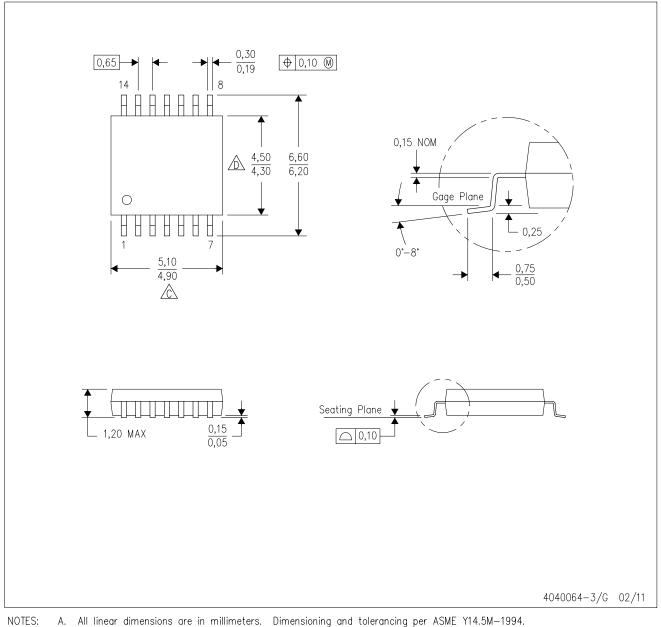

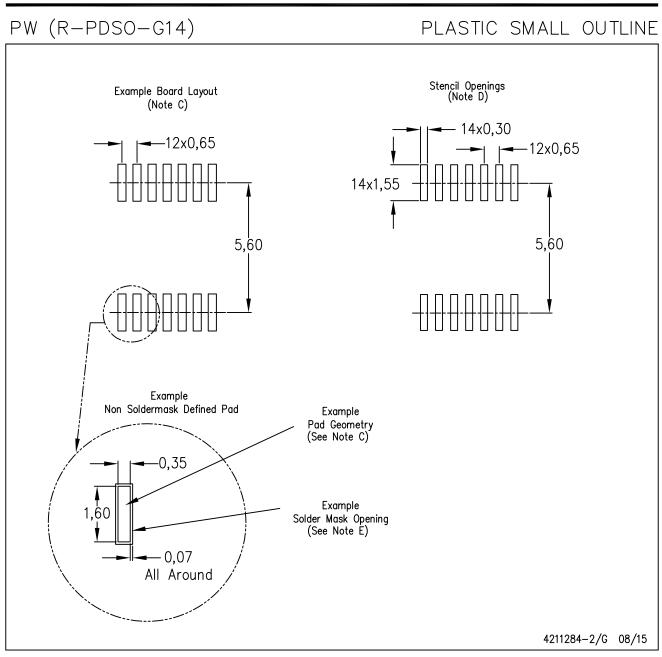

PW (R-PDSO-G14)

PLASTIC SMALL OUTLINE

A. An integration of the information o

Body length does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0,15 each side.

Body width does not include interlead flash. Interlead flash shall not exceed 0,25 each side.

E. Falls within JEDEC MO-153

NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Publication IPC-7351 is recommended for alternate designs.

- D. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Refer to IPC-7525 for other stencil recommendations.

- E. Customers should contact their board fabrication site for solder mask tolerances between and around signal pads.

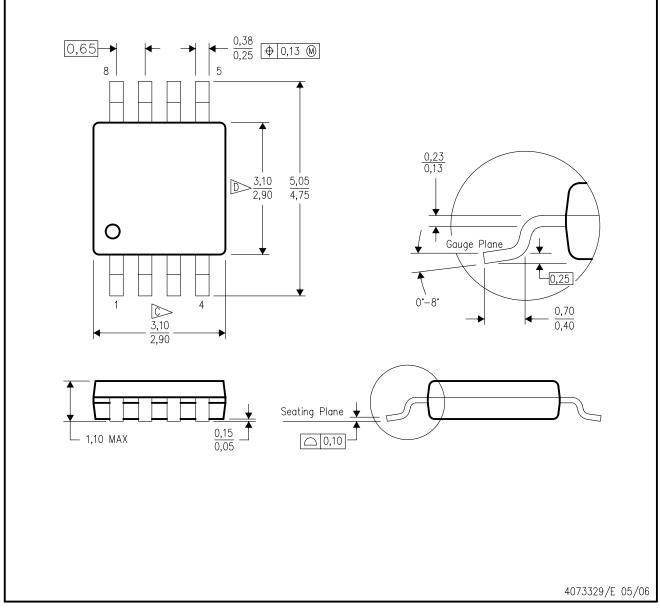

DGK (S-PDSO-G8)

PLASTIC SMALL-OUTLINE PACKAGE

NOTES: A. All linear dimensions are in millimeters.

B. This drawing is subject to change without notice.

Body length does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.15 per end.

- D Body width does not include interlead flash. Interlead flash shall not exceed 0.50 per side.

- E. Falls within JEDEC MO-187 variation AA, except interlead flash.

## DGK (S-PDSO-G8)

## PLASTIC SMALL OUTLINE PACKAGE

NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Publication IPC-7351 is recommended for alternate designs.

- D. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Refer to IPC-7525 for other stencil recommendations.

- E. Customers should contact their board fabrication site for solder mask tolerances between and around signal pads.

## IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2024, Texas Instruments Incorporated