LMH6518

SNOSB21D-MAY 2008-REVISED SEPTEMBER 2016

# LMH6518 900 MHz, Digitally Controlled, Variable Gain Amplifier

#### 1 Features

Gain Range: 40 dBGain Step Size: 2 dB

Combined Gain Resolution With Gsps ADCs: 8.5 mdB

Minimum Gain: -1.16 dB

Maximum Gain: 38.8 dB

-3 dB BW: 900 MHz

• Rise and Fall Time: <500 ps

• Recovery Time: <5 ns

· Propagation Delay Variation: 100 ps

HD2 at 100 MHz: -50 dBc

HD3 at 100 MHz: -53 dBc

Input-Referred Noise (Maximum Gain): 0.98 nV/√Hz

Overvoltage Clamps for Fast Recovery

Power Consumption: Auxiliary Turned Off 1.1 W to 0.75 W

## 2 Applications

- Oscilloscope Programmable Gain Amplifiers

- Differential ADC Drivers

- High-Frequency Single-Ended Input to Differential Conversion

- Precision Gain Control Applications

- · Medical Applications

- RF/IF Applications

## 3 Description

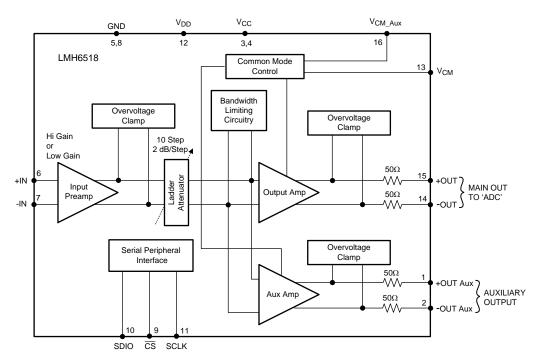

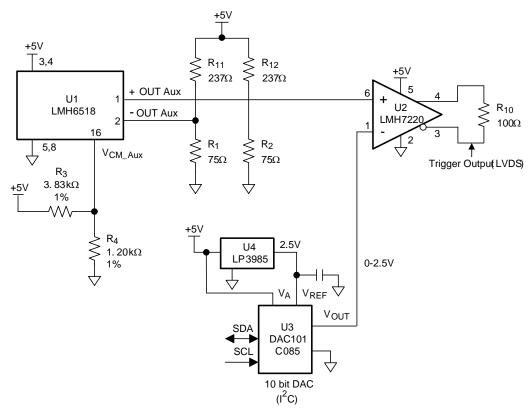

The LMH6518 device is a digitally controlled variable gain amplifier whose total gain is varied from  $-1.16~\mathrm{dB}$  to 38.8 dB for a 40 dB range in 2-dB steps. The -3-dB bandwidth is 900 MHz at all gains. Gain accuracy at each setting is typically 0.1 dB. When used in conjunction with TI's Gsample/second (Gsps) ADC with adjustable full-scale (FS) range, the LMH6518 gain adjustment accommodates full scale input signals from 6.8 mV<sub>PP</sub> to 920 mV<sub>PP</sub> to get 700 mV<sub>PP</sub> nominal at the ADC input. The auxiliary output (+OUT AUX and –OUT AUX) follows the main output and is intended for use in oscilloscope trigger function circuitry but may have other uses in other applications.

The LMH6518 gain is programmed through a SPI-1 compatible serial bus. A signal path combined gain resolution of 8.5 mdB is achieved when the device's gain and the Gsps ADC's FS input are both manipulated. Inputs and outputs are DC-coupled. The outputs are differential with individual common mode (CM) voltage control (for main and auxiliary outputs), and have a selectable bandwidth limiting circuitry (common to both main and auxiliary) of 20, 100, 200, 350, 650, 750 MHz or full bandwidth.

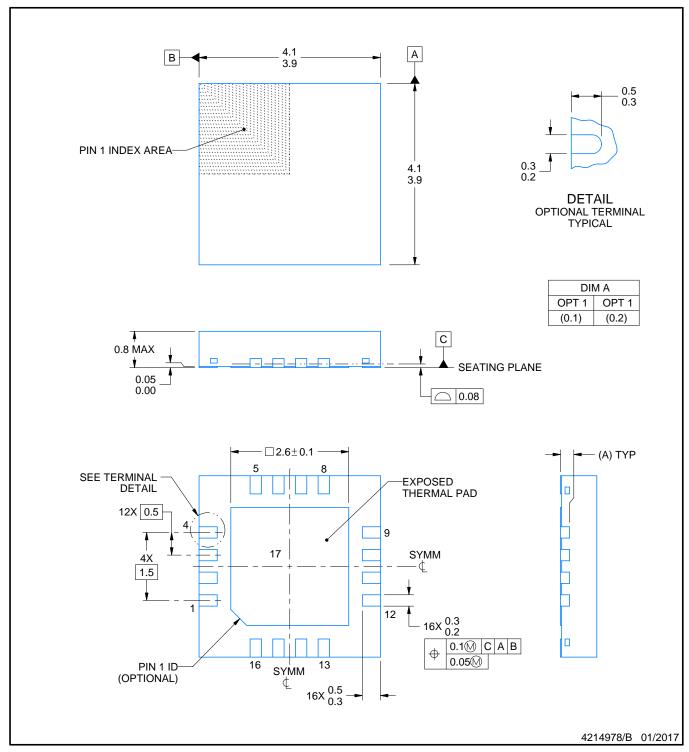

#### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE   | BODY SIZE (NOM)   |  |  |

|-------------|-----------|-------------------|--|--|

| LMH6518     | WQFN (16) | 4.00 mm × 4.00 mm |  |  |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

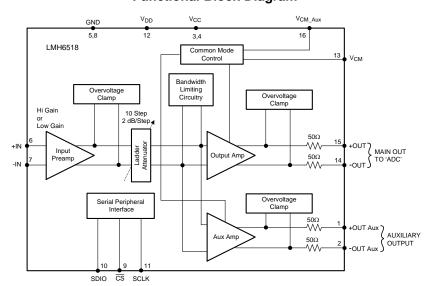

#### **Functional Block Diagram**

Copyright © 2016, Texas Instruments Incorporated

## **Table of Contents**

| 1 | Fea  | tures 1                          |    | 7.5 Programming                                      | . 20 |

|---|------|----------------------------------|----|------------------------------------------------------|------|

| 2 | App  | lications 1                      | 8  | Application and Implementation                       | . 24 |

| 3 |      | cription 1                       |    | 8.1 Application Information                          | . 24 |

| 4 |      | ision History 2                  |    | 8.2 Typical Application                              | . 24 |

| 5 |      | Configuration and Functions 3    | 9  | Power Supply Recommendations                         | . 37 |

| 6 |      | cifications5                     | 10 | Layout                                               | . 37 |

| ٠ | 6.1  | Absolute Maximum Ratings5        |    | 10.1 Layout Guidelines                               | . 37 |

|   | 6.2  | ESD Ratings                      |    | 10.2 Layout Example                                  | . 38 |

|   | 6.3  | Recommended Operating Conditions | 11 | Device and Documentation Support                     | . 39 |

|   | 6.4  | Thermal Information              |    | 11.1 Device Support                                  | . 39 |

|   | 6.5  | Electrical Characteristics6      |    | 11.2 Documentation Support                           | . 39 |

|   | 6.6  | Timing Requirements9             |    | 11.3 Receiving Notification of Documentation Updates | s 40 |

|   | 6.7  | Typical Characteristics          |    | 11.4 Community Resources                             | . 40 |

| 7 | Deta | ailed Description19              |    | 11.5 Trademarks                                      | . 40 |

|   | 7.1  | Overview                         |    | 11.6 Electrostatic Discharge Caution                 | . 40 |

|   | 7.2  | Functional Block Diagram         |    | 11.7 Glossary                                        | . 40 |

|   | 7.3  | Feature Description              | 12 | Mechanical, Packaging, and Orderable                 |      |

|   | 7.4  | Device Functional Modes20        |    | Information                                          | . 40 |

|   |      |                                  |    |                                                      |      |

# 4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| Cł       | nanges from Revision C (July 2013) to Revision D                                                                                                                                                                                                                                    | Page |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| •        | Added ESD Ratings table, Feature Description section, Device Functional Modes, Application and Implementation section, Power Supply Recommendations section, Layout section, Device and Documentation Support section, and Mechanical, Packaging, and Orderable Information section |      |

| •        | Added Thermal Information table                                                                                                                                                                                                                                                     | 5    |

| •        | Changed Y-axis unit on Output vs Input Typical Characteristics graphs From: (V) To: (mV)                                                                                                                                                                                            | 17   |

| <u>•</u> | Changed Y-axis unit on V <sub>OUT</sub> vs V <sub>IN</sub> Application Curves graph From: (V) To: (mV)                                                                                                                                                                              | 34   |

| Cł       | nanges from Revision A (March 2013) to Revision B                                                                                                                                                                                                                                   | Page |

| •        | Changed layout of National Semiconductor Data Sheet to TI format                                                                                                                                                                                                                    | 1    |

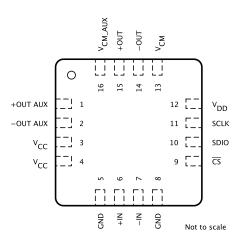

# 5 Pin Configuration and Functions

RGH Package 16-Pin WQFN Top View

#### **Pin Functions**

|     | PIN      | TYPE <sup>(1)</sup>             | DESCRIPTION               |

|-----|----------|---------------------------------|---------------------------|

| NO. | NAME     | TYPE <sup>(1)</sup> DESCRIPTION |                           |

| 1   | +OUT AUX | 0                               | Auxiliary positive output |

| 2   | -OUT AUX | 0                               | Auxiliary negative output |

Product Folder Links: LMH6518

(1) G = Ground, I = Input, O = Output, P = Power

# Pin Functions (continued)

|      | PIN                 | T)(D=(1)            | DECODIONION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------|---------------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO.  | NAME                | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 3, 4 | V <sub>cc</sub>     | Р                   | Analog power supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 5, 8 | GND                 | G                   | Ground, electrically connected to the WQFN heat sink                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 6    | +IN                 | I                   | Positive input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 7    | -IN                 | I                   | Negative input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

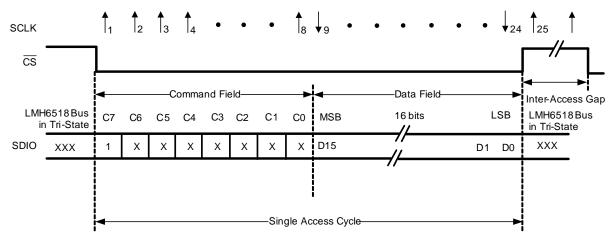

| 9    | <del>CS</del>       | I                   | Serial chip select (SPI interface, active low): While this signal is asserted SCLK is used to accept serial data present on SDIO and to source serial data on SDIO. When this signal is de-asserted, SDIO is ignored and SDIO is in TRI-STATE mode.                                                                                                                                                                                                                                                                                           |

| 10   | SDIO                | I/O                 | Serial data-in or data-out (SPI interface): Serial data are shifted into the device (8 bit command and 16 bit data) on this pin while $\overline{CS}$ signal is asserted during Write operation. Serial data are shifted out of the device on this pin during a read operation while $\overline{CS}$ signal is asserted. At other times, and after one complete Access Cycle (24 bits, see Figure 54 and Figure 55), this input is ignored. This output is in TRI-STATE mode when $\overline{CS}$ is de-asserted. This pin is bi-directional. |

| 11   | SCLK                | I                   | Serial clock (SPI interface): Serial data <u>are</u> shifted into and out of the device synchronous with this clock signal. SCLK transitions with $\overline{\text{CS}}$ de-asserted are ignored. SCLK must be stopped when not required to minimize digital crosstalk.                                                                                                                                                                                                                                                                       |

| 12   | $V_{DD}$            | Р                   | Digital power supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 13   | $V_{CM}$            | I                   | Input from ADC to control main output CM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 14   | -OUT                | 0                   | Main negative output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 15   | +OUT                | 0                   | Main positive output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 16   | V <sub>CM_AUX</sub> | I                   | Input to control auxiliary output CM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

Submit Documentation Feedback

Copyright © 2008–2016, Texas Instruments Incorporated

## 6 Specifications

## 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                                                                                                            |                                 | MIN | MAX | UNIT |

|------------------------------------------------------------------------------------------------------------|---------------------------------|-----|-----|------|

| Complement                                                                                                 | V <sub>CC</sub> (5 V nominal)   |     | 5.5 | \/   |

| Supply voltage                                                                                             | V <sub>DD</sub> (3.3 V nominal) |     | 3.6 | V    |

| Supply voltage  VDD (3.3 V nor  Differential input  Input common mode voltage  VCM and VCM_Aux  SPI inputs |                                 |     | ±1  | V    |

| Input common mode voltage                                                                                  |                                 | 1   | 4   | V    |

| V <sub>CM</sub> and V <sub>CM_Aux</sub>                                                                    |                                 |     | 2   | V    |

| SPI inputs                                                                                                 |                                 |     | 3.6 | V    |

| SPI inputs                                                                                                 | Infrared or convention (20 s)   |     | 235 | 00   |

| Soldering temperature                                                                                      | Wave (10 s)                     |     | 260 | °C   |

| Junction temperature, T <sub>J</sub>                                                                       |                                 |     | 150 | °C   |

| Storage temperature, T <sub>stg</sub>                                                                      |                                 | -65 | 150 | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### 6.2 ESD Ratings

|             | -                       |                                                                                | VALUE | UNIT |

|-------------|-------------------------|--------------------------------------------------------------------------------|-------|------|

|             |                         | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1)                         | ±2000 |      |

| $V_{(ESD)}$ | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±1000 | V    |

|             |                         | Machine model (MM)                                                             | ±200  |      |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

#### 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|          |                        | MIN NO | M MAX | UNIT |

|----------|------------------------|--------|-------|------|

| $V_{CC}$ | Analog supply voltage  | 5 ±5   | %     | V    |

| $V_{DD}$ | Digital supply voltage | 3.3 ±5 | %     | V    |

| $T_A$    | Temperature range      | -40    | 85    | °C   |

#### 6.4 Thermal Information

|                      |                                              | LMH6518    |      |

|----------------------|----------------------------------------------|------------|------|

|                      | THERMAL METRIC <sup>(1)</sup>                | RGH (WQFN) | UNIT |

|                      |                                              | 16 PINS    |      |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 40         | °C/W |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 31.7       | °C/W |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 11.5       | °C/W |

| ΨЈТ                  | Junction-to-top characterization parameter   | 0.3        | °C/W |

| ΨЈВ                  | Junction-to-board characterization parameter | 11.5       | °C/W |

| $R_{\theta JC(bot)}$ | Junction-to-case (bottom) thermal resistance | 3.4        | °C/W |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

#### 6.5 Electrical Characteristics

Unless otherwise noted, all limits are ensured for  $T_A = 25^{\circ}C$ , input CM = 2.5 V,  $V_{CM} = 1.2$  V,  $V_{CM\_Aux} = 1.2$  V, single-ended input drive,  $V_{CC} = 5$  V,  $V_{DD} = 3.3$  V,  $R_L = 100$   $\Omega$  differential (both main and auxiliary outputs),  $V_{OUT} = 0.7$  V<sub>PP</sub> differential (both main and auxiliary outputs), both main and auxiliary output specifications, full bandwidth setting, gain = 18.8 dB (preamp LG, 0 dB ladder attenuation), and full power setting (with auxiliary output turned on) (see Table 8 for abbreviations used). (1)

|                    | PARAMETER                                                 | TEST CONDITIONS                                                 | MIN <sup>(2)</sup> TYP <sup>(3)</sup> | MAX <sup>(2)</sup> | UNIT     |

|--------------------|-----------------------------------------------------------|-----------------------------------------------------------------|---------------------------------------|--------------------|----------|

| DYNAMIC PE         | RFORMANCE                                                 |                                                                 |                                       |                    |          |

| LSBW               | -3-dB bandwidth                                           | All gains                                                       | 900                                   |                    | MHz      |

|                    | Peaking                                                   | All gains                                                       | 1                                     |                    | dB       |

| GF_0.1 dB          | ±0.1-dB gain flatness                                     | All gains                                                       | 150                                   |                    | MHz      |

| GF_1 dB            | ±1-dB gain flatness                                       | All gains                                                       | 400                                   |                    | MHz      |

| TRS                | Rise time                                                 |                                                                 | 460                                   |                    | ps       |

| TRL                | Fall time                                                 |                                                                 | 450                                   |                    |          |

| os                 | Overshoot                                                 | Main output                                                     | 9%                                    |                    |          |

| t <sub>s_1</sub>   | Settling time                                             | Main output, ±0.5%                                              | 10                                    |                    | ns       |

| t <sub>s_2</sub>   | Settling time                                             | Main output, ±0.05%                                             | 14                                    |                    |          |

| t_recover          | Recovery time (4)                                         | All gains                                                       | <5                                    |                    | ns       |

| P <sub>D</sub>     | Propagation delay                                         | V <sub>OUT</sub> = 0.7 V <sub>PP</sub> , all gains              | 1.2                                   |                    | ns       |

| P <sub>D_VAR</sub> | Propagation delay variation                               | Gain varied                                                     | 100                                   |                    | ps       |

|                    | ORTION, AND RF SPECIFICATION                              | ONS                                                             |                                       |                    |          |

| e <sub>n_1</sub>   | Input noise spectral density                              | Max gain, 10 MHz                                                | 0.98                                  |                    | nV/√Hz   |

| e <sub>n_2</sub>   | Input noise spectral density                              | Preamp LG and 0-dB ladder,<br>10 MHz                            | 4.1                                   |                    | nV/√Hz   |

| e <sub>no_1</sub>  | RMS output noise                                          | Max gain, 100 Hz to 400 MHz                                     | 1.7                                   |                    | mV       |

| e <sub>no_2</sub>  | RMS output noise                                          | Preamp LG, 0-dB ladder,<br>100 Hz to 400 MHz                    | 940                                   |                    | μV       |

| NF_1               | Noise figure                                              | Max gain, $R_S = 50 \Omega$ each input, 10 MHz                  | 3.8                                   |                    | dB       |

| NF_2               | Noise figure                                              | Preamp LG, 0-dB ladder,<br>$R_S = 50 \Omega$ each input, 10 MHz | 13.5                                  |                    | dB       |

| HD2_1              | 2 <sup>nd</sup> harmonic distortion <sup>(5)</sup>        | Main output, 100 MHz, all gains                                 | -50                                   |                    | dBc      |

| HD3_1              | 3 <sup>rd</sup> harmonic distortion <sup>(5)</sup>        | Main output, 100 MHz, all gains                                 | -53                                   |                    | dBc      |

| HD2_2              | 2 <sup>nd</sup> harmonic distortion <sup>(5)</sup>        | Auxiliary output, 100 MHz, all gains                            | -48                                   |                    | dBc      |

| HD3_2              | 3 <sup>rd</sup> harmonic distortion <sup>(5)</sup>        | Auxiliary output, 100 MHz, all gains                            | -50                                   |                    | dBc      |

| HD2_3              | 2 <sup>nd</sup> harmonic distortion <sup>(5)</sup>        | Main output, 250 MHz, all gains                                 | -44                                   |                    | dBc      |

| HD3_3              | 3 <sup>rd</sup> harmonic distortion <sup>(5)</sup>        | Main output, 250 MHz, all gains                                 | -50                                   |                    | dBc      |

| HD2/HD3_4          | 2 <sup>nd</sup> / 3 <sup>rd</sup> harmonic distortion (5) | Auxiliary output, 250 MHz, all gains                            | -42                                   |                    | dBc      |

| IMD3               | Intermodulation distortion <sup>(5)</sup>                 | f = 250 MHz, main output                                        | -65                                   |                    | dBc      |

| OIP3_1             | Intermodulation intercept <sup>(5)</sup>                  | Main output, 250 MHz                                            | 26                                    |                    | dBm      |

| D 44D              | 4 dD                                                      | Main output, 250 MHz, 0-dB ladder                               | 1.8                                   |                    | \/       |

| P_1dB_main         | –1-dB compression                                         |                                                                 |                                       |                    | $V_{PP}$ |

<sup>(1)</sup> Electrical Characteristics table values apply only for factory testing conditions at the temperature indicated. Factory testing conditions result in limited self-heating of the device such that T<sub>J</sub> = T<sub>A</sub>. No specification of parametric performance is indicated in the electrical tables under conditions of internal self-heating where T<sub>J</sub> > T<sub>A</sub>.

<sup>(2)</sup> Limits are 100% production tested at 25°C unless otherwise specified. Limits over the operating temperature range are ensured through correlation using Statistical Quality Control (SQC) methods.

<sup>(3)</sup> Typical values represent the most likely parametric norm as determined at the time of characterization. Actual typical values may vary over time and also depends on the application and configuration. The typical values are not tested and are not ensured on shipped production material.

<sup>(4)</sup> Recovery time is the slower of the main and auxiliary outputs. Output swing of 700 mV<sub>PP</sub> shifted up or down by 50% (0.35 V) by introducing an offset. Measured values correspond to the time it takes to return to within ±1% of 0.7 V<sub>PP</sub> (±7 mV).

<sup>(5)</sup> Distortion data taken under single ended input condition.

## **Electrical Characteristics (continued)**

Unless otherwise noted, all limits are ensured for  $T_A$  = 25°C, input CM = 2.5 V,  $V_{CM}$  = 1.2 V,  $V_{CM\_Aux}$  = 1.2 V, single-ended input drive,  $V_{CC}$  = 5 V,  $V_{DD}$  = 3.3 V,  $R_L$  = 100  $\Omega$  differential (both main and auxiliary outputs),  $V_{OUT}$  = 0.7  $V_{PP}$  differential (both main and auxiliary outputs), both main and auxiliary output specifications, full bandwidth setting, gain = 18.8 dB (preamp LG, 0 dB ladder attenuation), and full power setting (with auxiliary output turned on) (see Table 8 for abbreviations used). (1)

|                                     | PARAMETER                                                          | TEST CONDITIONS                                                          | MIN <sup>(2)</sup>     | TYP <sup>(3)</sup> | MAX <sup>(2)</sup> | UNIT                   |

|-------------------------------------|--------------------------------------------------------------------|--------------------------------------------------------------------------|------------------------|--------------------|--------------------|------------------------|

| D. AdD. som                         | 4.40                                                               | Auxiliary output, 250 MHz, 0-dB ladder                                   |                        | 1.65               |                    | .,                     |

| P_1dB_aux                           | –1-dB compression                                                  | Auxiliary output, 250 MHz, 20-dB ladder                                  |                        | 1                  |                    | V <sub>PP</sub>        |

| GAIN PARAME                         | TERS                                                               |                                                                          |                        |                    |                    |                        |

| A <sub>V_DIFF_MAX</sub>             | Maximum gain                                                       |                                                                          | 38.1                   | 38.8               | 39.5               | dB                     |

| A <sub>V_DIFF_MIN</sub>             | Minimum gain                                                       |                                                                          | -1.91                  | -1.16              | -0.4               | dB                     |

|                                     | Gain step size                                                     | All gains including preamp step                                          | 1.8                    | 2                  | 2.2                | dB                     |

| Gain_Step                           | Gain step size with ADC (see Application and Implementation)       | ADC FS adjusted                                                          |                        | 8.5                |                    | mdB                    |

| Gain_Range                          | Gain range                                                         |                                                                          | 39                     | 40                 | 41                 | dB                     |

| TC_A <sub>V_DIFF</sub>              | Gain temp coefficient <sup>(6)</sup>                               | All gains                                                                |                        | -0.8               |                    | mdB/°C                 |

| Gain_A <sub>CC</sub>                | Absolute gain accuracy                                             | Compared to theoretical from max gain in 2-dB steps                      | 0.75                   |                    | 0.75               | dB                     |

| MATCHING                            |                                                                    |                                                                          |                        |                    | · ·                |                        |

| Gain_match                          | Gain matching,<br>main and auxiliary                               | All gains                                                                |                        | ±0.1               | ±0.2               | dB                     |

| BW_match                            | <ul><li>-3-dB bandwidth matching,<br/>main and auxiliary</li></ul> | All gains                                                                |                        | 5%                 |                    |                        |

| RT_match                            | Rise time matching, main and auxiliary                             | All gains                                                                |                        | 5%                 |                    |                        |

| PD_match                            | Propagation delay matching, main and auxiliary                     | All gains                                                                |                        | 100                |                    | ps                     |

| ANALOG I/O                          |                                                                    |                                                                          |                        |                    |                    |                        |

| CMRR_1                              | CM rejection ratio (see Table 8)                                   | Preamp HG, 0-dB ladder,<br>1.9 V < CMVR < 3.1 V                          | 45                     | 86                 |                    | dB                     |

| CMRR_2                              | CM rejection ratio (see Table 8)                                   | Preamp LG, 0-dB ladder,<br>1.9 V < CMVR < 3.1 V                          | 40                     | 55                 |                    | dB                     |

| CMVR_1                              | Input common mode voltage range                                    | Preamp HG, all ladder steps,<br>CMRR ≥ 45 dB                             | 1.9                    |                    | 3.1                | V                      |

| CMVR_2                              | Input common mode voltage range                                    | Preamp LG, all ladder steps,<br>CMRR ≥ 40 dB                             | 1.9                    |                    | 3.1                | V                      |

| $ \Delta V_{O\_CM} \Delta_{I\_CM} $ |                                                                    | All gains, 2 V < CMVR < 3 V                                              | -60                    | -100               |                    | dB                     |

| CMRR_CM                             | CM rejection ratio relative to VCM (see Table 8)                   | Preamp LG, 0 dB                                                          |                        | 101                |                    | dB                     |

| Z <sub>in_diff</sub>                | Differential input impedance                                       | All gains                                                                |                        | 150    1.5         |                    | KΩ    pF               |

|                                     |                                                                    | Preamp HG                                                                |                        | 420    1.7         |                    |                        |

| Z <sub>in_CM</sub>                  | CM input impedance                                                 | Preamp LG                                                                |                        | 900    1.7         |                    | $K\Omega \parallel pF$ |

| FS <sub>OUT1</sub>                  | Full scale voltage swing                                           | Main output, all gains, THD at 100 MHz ≤ –40 dBc  770 <sup>(7)</sup> 800 |                        |                    | ${\rm mV_{PP}}$    |                        |

| FS <sub>OUT2</sub>                  | Full scale voltage swing                                           | Main output, clamped, 0-dB ladder                                        |                        | 1800               | 1960               | $mV_{PP}$              |

| FS <sub>OUT3</sub>                  | Full scale voltage swing                                           | Auxiliary output, all gains THD at 100 MHz ≤ -40 dBc                     | 770 <sup>(7)</sup> 800 |                    | mV <sub>PP</sub>   |                        |

| FS <sub>OUT4</sub>                  | Full scale voltage swing                                           | Auxiliary output, clamped, 0-dB ladder                                   |                        | 1600               | 1760               | $mV_{PP}$              |

| V <sub>OUT_MAX1</sub>               | Voltage at each output pin (clamped)                               | Main output, all gains, V <sub>CM</sub> = 1.2 V                          | 0.5                    |                    | 1.8                | V                      |

<sup>(6)</sup> Drift determined by dividing the change in parameter at temperature extremes by the total temperature change.

<sup>(7)</sup> Specified by design.

## **Electrical Characteristics (continued)**

Unless otherwise noted, all limits are ensured for  $T_A$  = 25°C, input CM = 2.5 V,  $V_{CM}$  = 1.2 V,  $V_{CM\_Aux}$  = 1.2 V, single-ended input drive,  $V_{CC}$  = 5 V,  $V_{DD}$  = 3.3 V,  $R_L$  = 100  $\Omega$  differential (both main and auxiliary outputs),  $V_{OUT}$  = 0.7  $V_{PP}$  differential (both main and auxiliary outputs), both main and auxiliary output specifications, full bandwidth setting, gain = 18.8 dB (preamp LG, 0 dB ladder attenuation), and full power setting (with auxiliary output turned on) (see Table 8 for abbreviations used).<sup>(1)</sup>

|                         | PARAMETER                                             | TEST                                                | CONDITIONS                                                                                                             | MIN <sup>(2)</sup>   | TYP <sup>(3)</sup> | MAX <sup>(2)</sup> | UNIT  |

|-------------------------|-------------------------------------------------------|-----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|----------------------|--------------------|--------------------|-------|

| V <sub>OUT_MAX2</sub>   | Voltage at each output pin (clamped)                  | Auxiliary output,<br>V <sub>CM</sub> = 1.2 V        | , all gains,                                                                                                           | 0.8                  |                    | 2.2                | V     |

| V <sub>OUT_MAX3</sub>   | Voltage at each output pin (clamped)                  | Main output, all                                    | gains, V <sub>CM</sub> = 1.45 V                                                                                        |                      |                    | 2.05               | V     |

| $V_{OUT\_MAX4}$         | Voltage at each output pin (clamped)                  | Auxiliary output,<br>V <sub>CM</sub> = 1.45 V       | , all gains,                                                                                                           |                      |                    | 2.45               | V     |

| Z <sub>OUT_DIFF</sub>   | Differential output impedance                         | All gains                                           |                                                                                                                        | 92                   | 100                | 108                | Ω     |

| V <sub>OOS</sub>        | Output offset voltage                                 | All gains                                           |                                                                                                                        |                      | ±15                | ±40                | mV    |

| V <sub>OOS_shift1</sub> | Output offset voltage shift                           | Preamp LG to p                                      | Preamp LG to preamp HG                                                                                                 |                      | 13.7               |                    | mV    |

| V <sub>OOS_shift2</sub> | Output offset voltage shift                           | All gains, exclud                                   | ding preamp step                                                                                                       |                      | 12.7               |                    | mV    |

| TCV <sub>OOS</sub>      | Output offset voltage drift <sup>(6)</sup>            | Preamp HG, 0-d                                      |                                                                                                                        |                      | -24<br>-7          |                    | μV/°C |

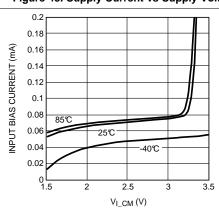

| I <sub>B</sub>          | Input bias current <sup>(8)</sup>                     | $T_A = -40$ °C to 8<br>$T_A = -65$ °C to 1          |                                                                                                                        |                      | 40                 | 100<br>140         | μA    |

| V <sub>OCM</sub>        | Output CM voltage                                     | All gains                                           | $T_A = -40$ °C to 85°C<br>$T_A = -65$ °C to 150°C                                                                      | 0.95                 | 1.2                | 1.45               | V     |

| V <sub>OS_CM</sub>      | Output CM offset                                      | All gains                                           | 1A - 00 0 10 100 0                                                                                                     | 0.00                 | ±15                | ±30                | mV    |

| TC_V <sub>OS_CM</sub>   | CM offset voltage temperature coefficient             | All gains                                           |                                                                                                                        |                      | +55                | 200                | μV/°C |

| BAL_Error_DC            | Output gain balance error                             | DC, $\frac{\Delta V_{O\_CM}}{\Delta V_{OUT}}$       |                                                                                                                        |                      | -78                |                    | dB    |

| BAL_Error_AC            | Output gain balance error                             | 250                                                 | 250 MHz, <sup>VO_CM</sup> / <sub>VOUT</sub>                                                                            |                      | -45                |                    | dB    |

| РВ                      | Phase balance error (see Table 8)                     | 250 MHz                                             |                                                                                                                        |                      | ±0.8               |                    | deg   |

| DODD                    | Differential power supply                             | Preamp HG, 0-0                                      | dB ladder                                                                                                              | -60                  | -87                |                    | -ID   |

| PSRR                    | rejection (see Table 8)                               | Preamp LG, 0-d                                      | IB ladder                                                                                                              | -50                  | -70                |                    | dB    |

| PSRR_CM                 | CM power supply rejection (see Table 8)               | Preamp LG, 0-d                                      | IB ladder                                                                                                              | -55                  | -71                |                    | dB    |

| V <sub>CM_I</sub>       | V <sub>CM</sub> input bias current <sup>(8)</sup>     | All gains                                           | $T_A = -40$ °C to 85°C<br>$T_A = -65$ °C to 150°C                                                                      |                      | ±1                 | ±10<br>±20         | nA    |

| V <sub>CM_AUX_I</sub>   | V <sub>CM_AUX</sub> input bias current <sup>(8)</sup> | All gains                                           | $T_A = -40^{\circ}\text{C} \text{ to } 85^{\circ}\text{C}$ $T_A = -65^{\circ}\text{C} \text{ to } 150^{\circ}\text{C}$ |                      | ±1                 | ±10                | nA    |

| DIGITAL I/O             |                                                       |                                                     | R                                                                                                                      |                      |                    |                    |       |

| V <sub>IH</sub>         | Input logic high                                      | $T_A = -65^{\circ}C \text{ to } 1$                  | 50°C                                                                                                                   | V <sub>DD</sub> -0.6 |                    |                    | V     |

| V <sub>IL</sub>         | Input logic low                                       | $T_A = -65^{\circ}\text{C to } 150^{\circ}\text{C}$ |                                                                                                                        |                      |                    | 0.5                | V     |

| V <sub>OH</sub>         | Output logic high                                     | ,,                                                  |                                                                                                                        |                      | V <sub>DD</sub>    |                    | V     |

| V <sub>OL</sub>         | Output logic low                                      |                                                     |                                                                                                                        |                      | 0                  |                    | V     |

| R <sub>Hi_Z</sub>       | Output resistance                                     | High impedance mode                                 |                                                                                                                        |                      | 5                  |                    | ΜΩ    |

| I_in                    | Input bias current                                    | 5 ,                                                 |                                                                                                                        |                      | <1                 |                    | μA    |

| F <sub>SCLK</sub>       | SCLK rate                                             |                                                     |                                                                                                                        |                      |                    | 10                 | MHz   |

| F <sub>SCLK_DT</sub>    | SCLK duty cyle                                        |                                                     |                                                                                                                        | 45%                  | 50%                | 55%                | ····- |

<sup>(8)</sup> Positive current is current flowing into the device.

## **Electrical Characteristics (continued)**

Unless otherwise noted, all limits are ensured for  $T_A = 25^{\circ}C$ , input CM = 2.5 V,  $V_{CM} = 1.2$  V,  $V_{CM\_Aux} = 1.2$  V, single-ended input drive,  $V_{CC} = 5$  V,  $V_{DD} = 3.3$  V,  $R_L = 100~\Omega$  differential (both main and auxiliary outputs),  $V_{OUT} = 0.7$  V<sub>PP</sub> differential (both main and auxiliary outputs), both main and auxiliary output specifications, full bandwidth setting, gain = 18.8 dB (preamp LG, 0 dB ladder attenuation), and full power setting (with auxiliary output turned on) (see Table 8 for abbreviations used). (1)

|                     | PARAMETER                               | TES                                | T CONDITIONS | MIN <sup>(2)</sup> | TYP <sup>(3)</sup> | MAX <sup>(2)</sup> | UNIT |

|---------------------|-----------------------------------------|------------------------------------|--------------|--------------------|--------------------|--------------------|------|

| POWER R             | EQUIREMENTS                             |                                    |              |                    |                    |                    |      |

|                     | Complex compact V                       | $T_A = -40^{\circ}C \text{ to } 8$ | 35°C         | 195                | 210                | 225                | A    |

| I <sub>S1</sub>     | Supply current, V <sub>CC</sub>         | $T_A = -65^{\circ}C$ to 1          | 150°C        |                    |                    | 230                | mA   |

|                     | Complete company V complete             | $T_A = -40^{\circ}C \text{ to } 8$ | 35°C         |                    | 150                | 165                | A    |

| I <sub>S1_off</sub> | Supply current, V <sub>CC</sub> aux off | $T_A = -65^{\circ}C$ to 1          | 150°C        |                    |                    | 170                | mA   |

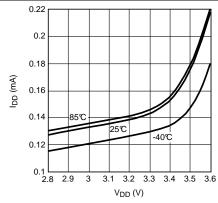

|                     | Cumply ourrent V                        | $T_A = -40^{\circ}C \text{ to } 8$ | 35°C         |                    | 180                | 350                |      |

| I <sub>DD</sub>     | Supply current, V <sub>DD</sub>         | $T_A = -65^{\circ}C \text{ to } 1$ | 150°C        |                    |                    | 400                | μΑ   |

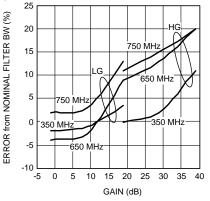

| BANDWID             | TH LIMITING FILTER SPECIFICAT           | IONS                               |              | •                  |                    | •                  |      |

|                     |                                         |                                    | 20 MHz       | 0%                 | 20%                |                    |      |

|                     |                                         |                                    | 100 MHz      | 0%                 | 20%                |                    |      |

|                     |                                         | All going                          | 200 MHz      | 0%                 | 20%                |                    |      |

|                     |                                         | All gains                          | 350 MHz      |                    | ±25%               |                    |      |

|                     | Pass band tolerance,  –3 dB bandwidth   |                                    | 650 MHz      |                    | ±25%               |                    |      |

|                     | -5 db baildwidin                        |                                    | 750 MHz      |                    | ±25%               |                    |      |

|                     |                                         |                                    | 350 MHz      |                    | ±10%               |                    |      |

|                     |                                         | Preamp LG,<br>0-dB ladder          | 650 MHz      |                    | ±10%               |                    |      |

|                     |                                         | 5 52 .addoi                        | 750 MHz      |                    | ±10%               |                    |      |

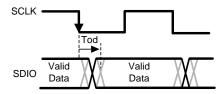

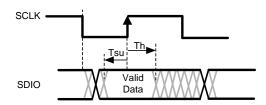

## 6.6 Timing Requirements

|                  |                                                                                                            | MIN | NOM | MAX | UNIT        |

|------------------|------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------------|

| T <sub>S</sub>   | SDIO setup time                                                                                            | 25  |     |     | ns          |

| T <sub>H</sub>   | SDIO hold time                                                                                             | 25  |     |     | ns          |

| T <sub>CES</sub> | CS enable setup time (from CS asserted to rising edge of SCLK)                                             | 25  |     |     | ns          |

| t <sub>CDS</sub> | $\overline{\text{CS}}$ disable setup time (from $\overline{\text{CS}}$ de-asserted to rising edge of SCLK) | 25  |     |     | ns          |

| T <sub>IAG</sub> | Inter-acess gap                                                                                            | 3   |     |     | SCLK cycles |

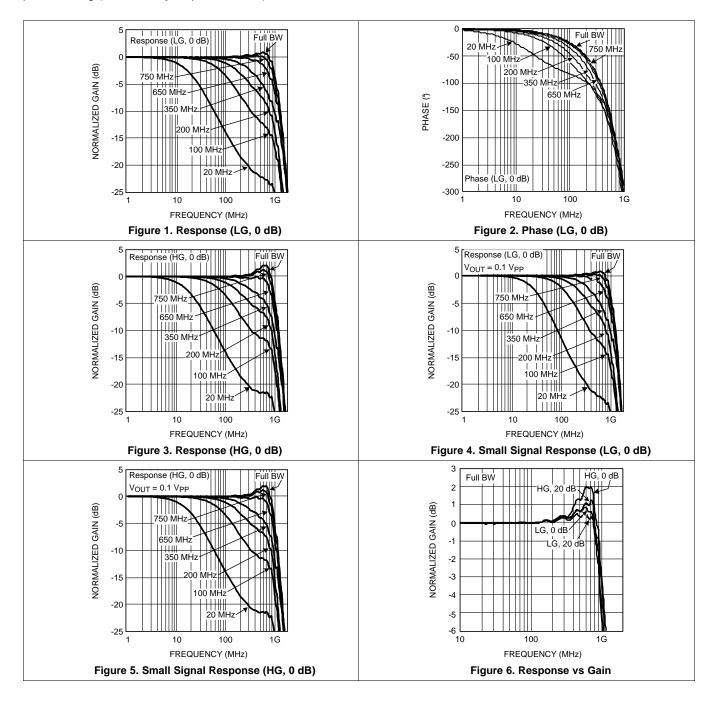

## 6.7 Typical Characteristics

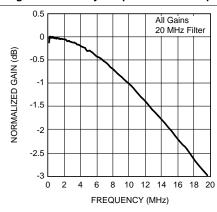

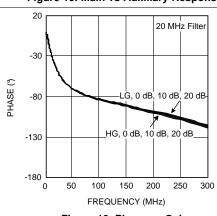

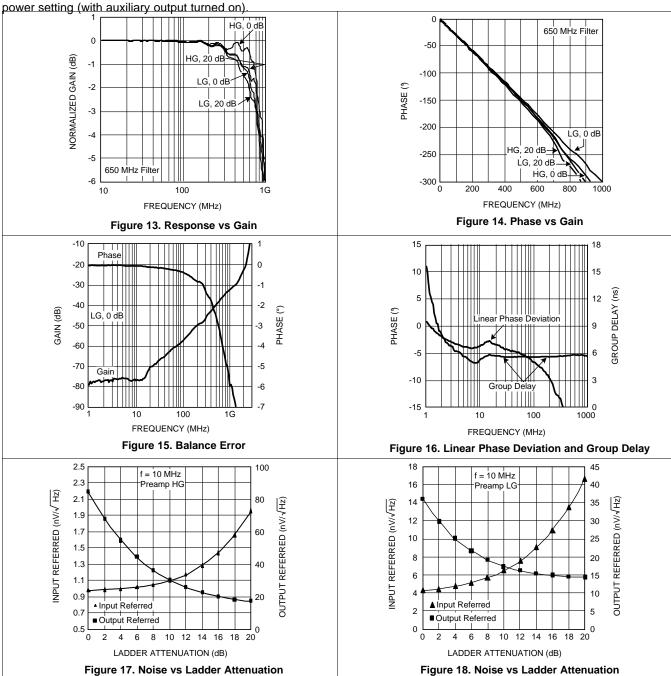

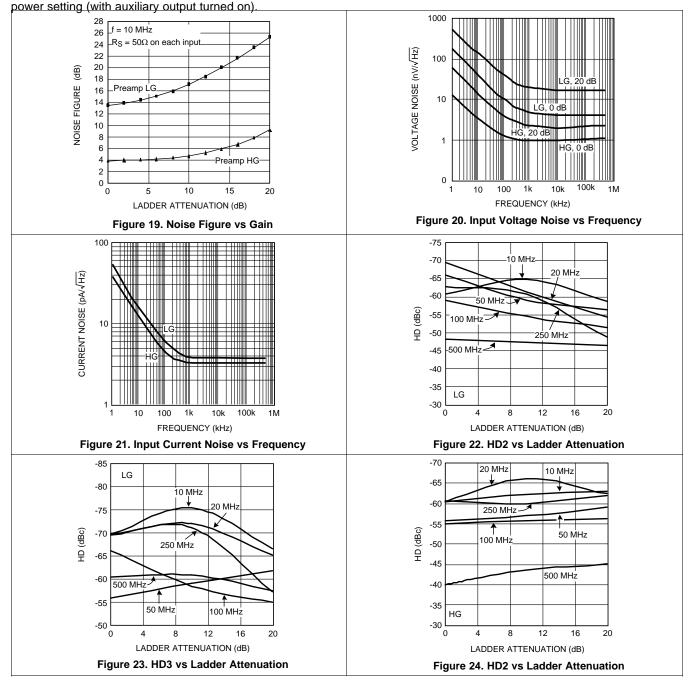

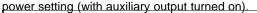

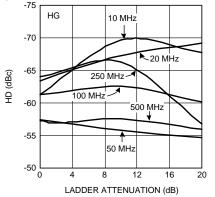

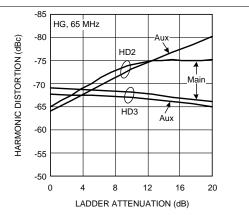

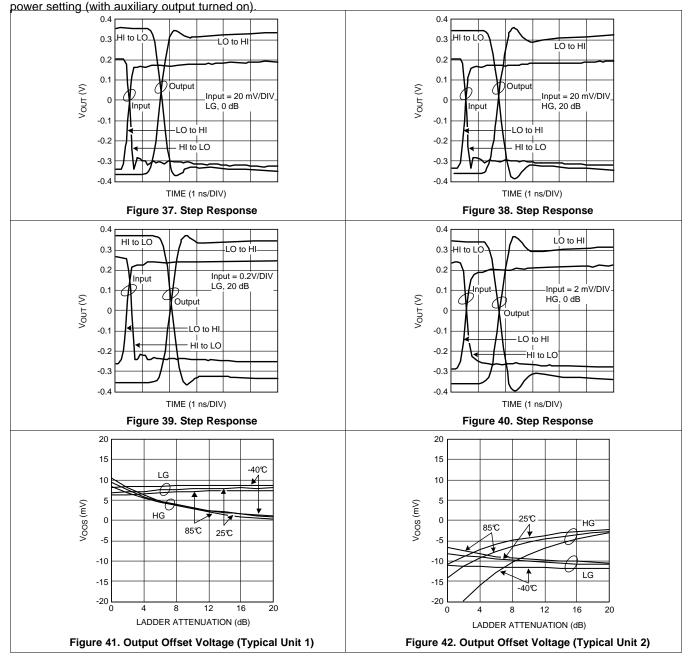

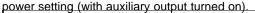

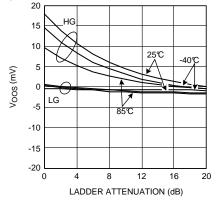

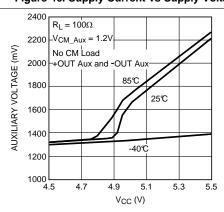

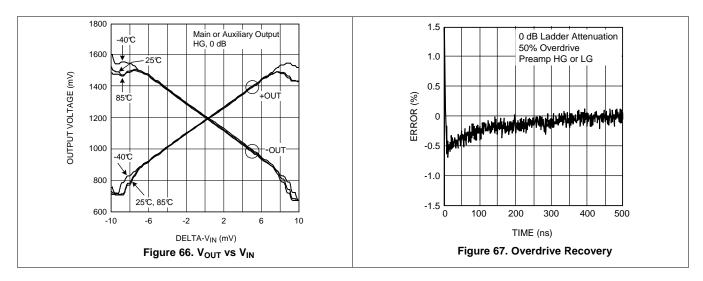

Unless otherwise noted, input CM = 2.5 V,  $V_{CM}$  = 1.2 V,  $V_{CM AUX}$  = 1.2 V, single-ended input drive,  $V_{CC}$  = 5 V,  $V_{DD}$  = 3.3 V,  $R_L$  = 100  $\Omega$  differential (both main and auxiliary outputs),  $V_{OUT}$  = 0.7  $V_{PP}$  differential (both main and auxiliary outputs), main output specification (auxiliary is labeled), full bandwidth setting, gain = 18.8 dB (preamp LG, 0 dB ladder attenuation), and full power setting (with auxiliary output turned on).

Submit Documentation Feedback

Unless otherwise noted, input CM = 2.5 V,  $V_{CM}$  = 1.2 V,  $V_{CM AUX}$  = 1.2 V, single-ended input drive,  $V_{CC}$  = 5 V,  $V_{DD}$  = 3.3 V,

$R_L$  = 100  $\Omega$  differential (both main and auxiliary outputs),  $V_{OUT}$  = 0.7  $V_{PP}$  differential (both main and auxiliary outputs), main output specification (auxiliary is labeled), full bandwidth setting, gain = 18.8 dB (preamp LG, 0 dB ladder attenuation), and full

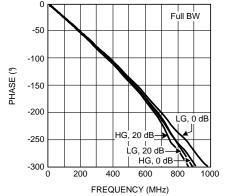

Figure 7. Phase vs Gain

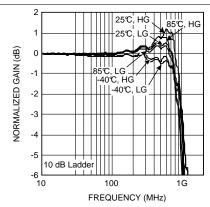

Figure 8. Response Over Temperature

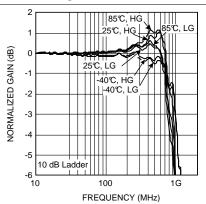

Figure 9. Auxiliary Response Over Temperature

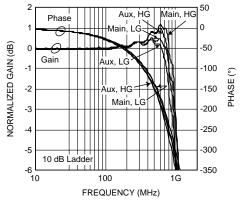

Figure 10. Main vs Auxiliary Response

Figure 11. Response vs Gain

Figure 12. Phase vs Gain

Unless otherwise noted, input CM = 2.5 V,  $V_{CM}$  = 1.2 V,  $V_{CM AUX}$  = 1.2 V, single-ended input drive,  $V_{CC}$  = 5 V,  $V_{DD}$  = 3.3 V,

$R_L$  = 100  $\Omega$  differential (both main and auxiliary outputs),  $V_{OUT}$  = 0.7  $V_{PP}$  differential (both main and auxiliary outputs), main output specification (auxiliary is labeled), full bandwidth setting, gain = 18.8 dB (preamp LG, 0 dB ladder attenuation), and full

Submit Documentation Feedback

Copyright © 2008–2016, Texas Instruments Incorporated

Unless otherwise noted, input CM = 2.5 V,  $V_{CM}$  = 1.2 V,  $V_{CM AUX}$  = 1.2 V, single-ended input drive,  $V_{CC}$  = 5 V,  $V_{DD}$  = 3.3 V,

$R_L = 100~\Omega$  differential (both main and auxiliary outputs),  $V_{OUT} = 0.7~V_{PP}$  differential (both main and auxiliary outputs), main output specification (auxiliary is labeled), full bandwidth setting, gain = 18.8 dB (preamp LG, 0 dB ladder attenuation), and full

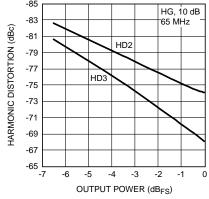

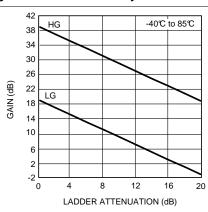

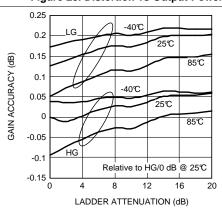

Unless otherwise noted, input CM = 2.5 V,  $V_{CM}$  = 1.2 V,  $V_{CM AUX}$  = 1.2 V, single-ended input drive,  $V_{CC}$  = 5 V,  $V_{DD}$  = 3.3 V,

$R_L$  = 100  $\Omega$  differential (both main and auxiliary outputs),  $V_{OUT}$  = 0.7  $V_{PP}$  differential (both main and auxiliary outputs), main output specification (auxiliary is labeled), full bandwidth setting, gain = 18.8 dB (preamp LG, 0 dB ladder attenuation), and full

Figure 25. HD3 vs Ladder Attenuation

Figure 26. Main and Auxiliary Distortion Comparison

Figure 27. Main and Auxiliary Distortion Comparison

Figure 28. Distortion vs Output Power

Figure 29. Gain vs Ladder Attenuation

Figure 30. Gain Accuracy vs Ladder Attenuation

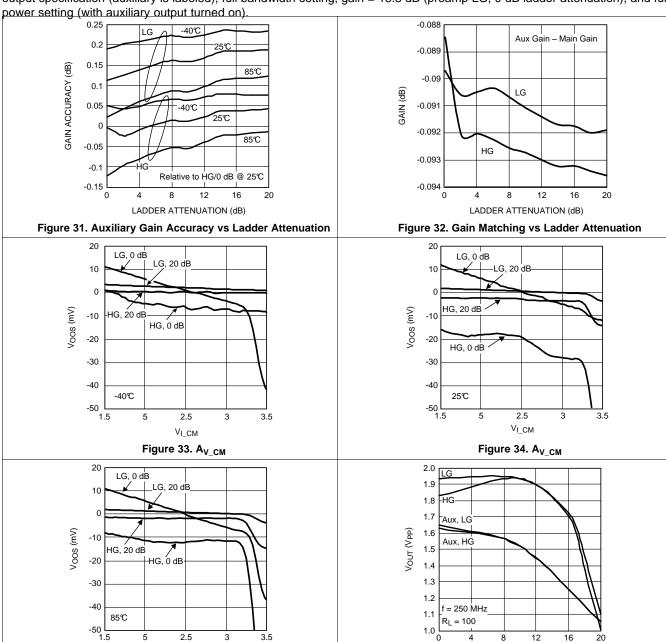

Unless otherwise noted, input CM = 2.5 V,  $V_{CM}$  = 1.2 V,  $V_{CM AUX}$  = 1.2 V, single-ended input drive,  $V_{CC}$  = 5 V,  $V_{DD}$  = 3.3 V,

$R_L$  = 100  $\Omega$  differential (both main and auxiliary outputs),  $V_{OUT}$  = 0.7  $V_{PP}$  differential (both main and auxiliary outputs), main output specification (auxiliary is labeled), full bandwidth setting, gain = 18.8 dB (preamp LG, 0 dB ladder attenuation), and full

Product Folder Links: LMH6518

Submit Documentation Feedback

LADDER ATTENUATION (dB)

Figure 36. –1 dB Compression vs Ladder Attenuation

V<sub>I\_CM</sub>

Figure 35. A<sub>V CM</sub>

Unless otherwise noted, input CM = 2.5 V,  $V_{CM}$  = 1.2 V,  $V_{CM AUX}$  = 1.2 V, single-ended input drive,  $V_{CC}$  = 5 V,  $V_{DD}$  = 3.3 V,

$R_L$  = 100  $\Omega$  differential (both main and auxiliary outputs),  $V_{OUT}$  = 0.7  $V_{PP}$  differential (both main and auxiliary outputs), main output specification (auxiliary is labeled), full bandwidth setting, gain = 18.8 dB (preamp LG, 0 dB ladder attenuation), and full

Submit Documentation Feedback

Copyright © 2008–2016, Texas Instruments Incorporated

Unless otherwise noted, input CM = 2.5 V,  $V_{CM}$  = 1.2 V,  $V_{CM AUX}$  = 1.2 V, single-ended input drive,  $V_{CC}$  = 5 V,  $V_{DD}$  = 3.3 V,

$R_L$  = 100  $\Omega$  differential (both main and auxiliary outputs),  $V_{OUT}$  = 0.7  $V_{PP}$  differential (both main and auxiliary outputs), main output specification (auxiliary is labeled), full bandwidth setting, gain = 18.8 dB (preamp LG, 0 dB ladder attenuation), and full

Figure 43. Output Offset Voltage (Typical Unit 3)

Figure 44. V<sub>OS\_CM</sub> vs V<sub>CM</sub>

Figure 45. Supply Current vs Supply Voltage

Figure 46. Supply Current vs Supply Voltage

Figure 47. Input Bias Current vs Input CM

Figure 48. Auxiliary Output Voltage (Hi-Z Mode)

Unless otherwise noted, input CM = 2.5 V,  $V_{CM}$  = 1.2 V,  $V_{CM AUX}$  = 1.2 V, single-ended input drive,  $V_{CC}$  = 5 V,  $V_{DD}$  = 3.3 V,

$R_L$  = 100  $\Omega$  differential (both main and auxiliary outputs),  $V_{OUT}$  = 0.7  $V_{PP}$  differential (both main and auxiliary outputs), main output specification (auxiliary is labeled), full bandwidth setting, gain = 18.8 dB (preamp LG, 0 dB ladder attenuation), and full

Figure 49. Filter BW vs Gain

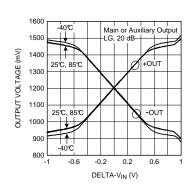

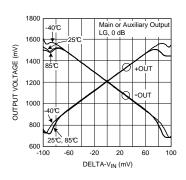

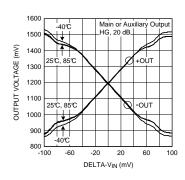

Figure 50. Output vs Input

Figure 51. Output vs Input

Figure 52. Output vs Input

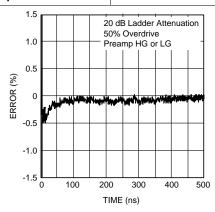

Figure 53. Overdrive Recovery Time (Return to Zero)

Submit Documentation Feedback

Copyright © 2008–2016, Texas Instruments Incorporated

#### 7 Detailed Description

#### 7.1 Overview

The LMH6518 device is a digitally-controlled variable gain amplifier (DVGA) which is designed specifically as an oscilloscope analog front end (AFE). This device samples an analog voltage and conditions it for the analog to digital converter (ADC) input. It is specifically designed to drive TI's giga sample ADCs which have  $100-\Omega$  input impedance and  $800-\text{mV}_{PP}$  full scale input voltage.

#### 7.2 Functional Block Diagram

Copyright © 2016, Texas Instruments Incorporated

#### 7.3 Feature Description

The LMH6518 offers several unique features in addition to being a general purpose digital variable gain amplifier (DVGA).

#### 7.3.1 Input Preamplifier

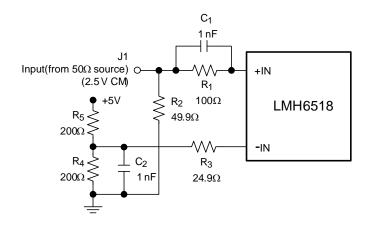

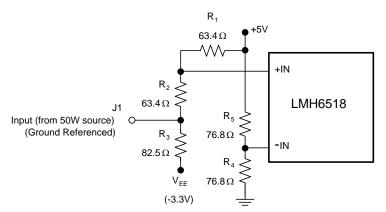

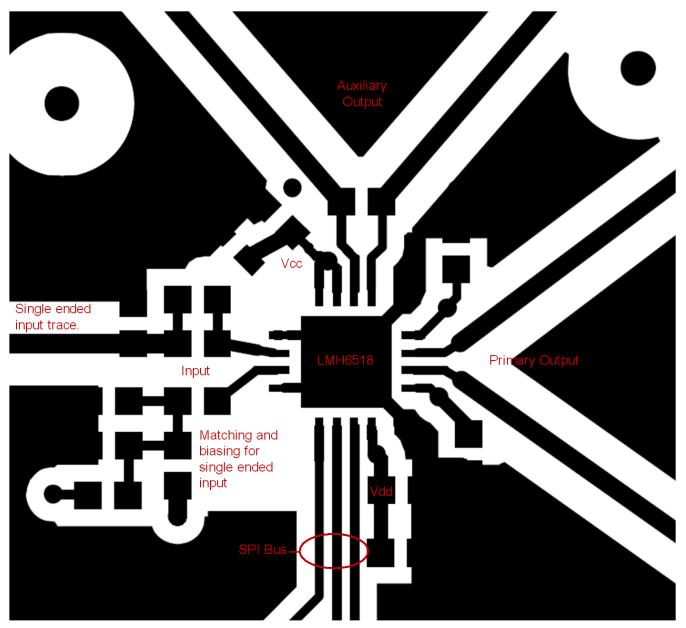

The LMH6518 has a fully differential preamplifier which has a consistent 150-k $\Omega$  impedance across all gain settings. The LMH6518 is also driven with a single-ended signal source. The preamplifier has two gain settings. See *Input and Output Considerations* for details.

#### 7.3.1.1 Primary Output Amplifier

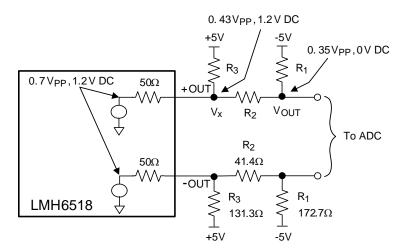

The LMH6518 has two nearly identical amplifiers. The output amplifier was designed as the primary output amplifier. It features an internal  $100-\Omega$  termination for interfacing with  $100-\Omega$  input impedance ADCs. The output amplifier has a common mode voltage control pin which sets the output common mode of the amplifier.

#### 7.3.1.2 Auxiliary Amplifier

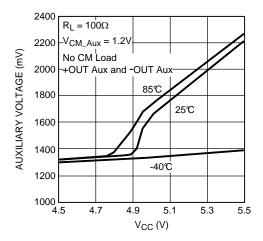

The LMH6518 has a second output amplifier that was designed to provide a trigger signal when used as an oscilloscope AFE. The auxiliary amplifier has all of the features of the output amplifier and provides a duplicate signal for use in trigger circuits. The auxiliary amplifier has a common mode voltage control pin which sets the output common mode of the amplifier.

#### **Feature Description (continued)**

#### 7.3.2 Overvoltage Clamp

THe LMH6518 features two levels of clamps used to protect the amplifier and the ADC from voltage transients. These clamps are placed after the input preamplifier and also after the final output amplifier. The clamp voltages are set using the SPI bus.

#### 7.3.3 Attenuator

The primary gain control feature of the LMH65418 is the digital attenuator. The attenuator controls the overall gain of the amplifier. The attenuator has a range of 0 dB to 20 dB of attenuation.

## 7.3.4 Digital Control Block

The LMH6518 has digitally controlled gain as well as digitally controlled voltage clamps and digitally controlled bandwidth. If it is not used, this block can also disable the auxiliary amplifier. *Logic Functions* has details on the digital control registers and programming.

#### 7.4 Device Functional Modes

## 7.4.1 Primary Amplifier

The main functional mode of the LMH6518 is as an AFE providing gain, voltage clamping, and frequency limiting. In this mode, the gain, bandwidth, and voltage swing are all programmable using the SPI control block.

#### 7.4.2 Auxiliary Output

The secondary functional mode of the LMH6518 is the auxiliary output. This output is nearly identical to the primary amplifier. The only difference is that the auxiliary output has slightly lower distortion performance. The auxiliary output was designed to provide a trigger signal when used as an oscilloscope AFE.

#### 7.5 Programming

#### 7.5.1 Logic Functions

The following LMH6518 functions are controlled using the SPI-1 compatible bus:

- Filters (20, 100, 200, 350, 650, 750 MHz or full bandwidth)

- Power mode (Full power or auxiliary high impedance, Hi-Z)

- Preamp (HG or LG)

- Attenuation ladder (0 dB to 20 dB, 10 states)

- LMH6518 state write or read back

The SPI-1 bus uses 3.3-V logic. *SDIO* is the serial digital input-output which writes to the LMH6518 or reads back from it. *SCLK* is the bus clock with chip select function controlled by CS.

## **Programming (continued)**

Copyright © 2016, Texas Instruments Incorporated

Figure 54. Serial Interface Protocol, Read Operation

Copyright © 2016, Texas Instruments Incorporated

Figure 55. Serial Interface Protocol, Write Operation

Figure 56. Read Timing

## **Programming (continued)**

Figure 57. Write Timing

## Table 1. Data Field

|              |     |     |     |     |                                |    |    | FILTER   |    |    | PREAMP           | LAD | DER A | TTEN  | UATION      |

|--------------|-----|-----|-----|-----|--------------------------------|----|----|----------|----|----|------------------|-----|-------|-------|-------------|

| D15<br>(MSB) | D14 | D13 | D12 | D11 | D10                            | D9 | D8 | D7       | D6 | D5 | D4               | D3  | D2    | D1    | D0<br>(LSB) |

| Х            | 0   | 0   | 0   | 0   | 0 = Full power<br>1 = Aux Hi-Z | 0  | S  | ee Table | 3  | 0  | 0 = LG<br>1 = HG |     | See   | Table | 4           |

#### **NOTE**

Bits D5, D9, and D11 to D14 must be 0. Otherwise, device operation is undefined and specifications are not ensured.

**Table 2. Default Power-On Reset Condition**

|              |     |     |     |     |     |    | <b>FILTER</b> |    |    | PREAMP | LA | DDER . | ATTENU | JATION |             |

|--------------|-----|-----|-----|-----|-----|----|---------------|----|----|--------|----|--------|--------|--------|-------------|

| D15<br>(MSB) | D14 | D13 | D12 | D11 | D10 | D9 | D8            | D7 | D6 | D5     | D4 | D3     | D2     | D1     | D0<br>(LSB) |

| 0            | 0   | 0   | 0   | 0   | 0   | 0  | 0             | 0  | 0  | 0      | 0  | 1      | 0      | 1      | 0           |

**Table 3. Filter Selection Data Field**

|    | FILTER |    | PANDWIDTH (MH-) |

|----|--------|----|-----------------|

| D8 | D7     | D6 | BANDWIDTH (MHz) |

| 0  | 0      | 0  | Full            |

| 0  | 0      | 1  | 20              |

| 0  | 1      | 0  | 100             |

| 0  | 1      | 1  | 200             |

| 1  | 0      | 0  | 350             |

| 1  | 0      | 1  | 650             |

| 1  | 1      | 0  | 750             |

| 1  | 1      | 1  | Unallowed       |

#### **NOTE**

All filters are low-pass, single pole roll-off and operate on both main and auxiliary outputs. These filters are intended as signal path bandwidth and noise limiting.

**Table 4. Ladder Attenuation Data Field**

|    | LADDER AT | TENUATION |    | DANDWIDTH (JD) |

|----|-----------|-----------|----|----------------|

| D3 | D2        | D1        | D0 | BANDWIDTH (dB) |

| 0  | 0         | 0         | 0  | 0              |

| 0  | 0         | 0         | 1  | -2             |

| 0  | 0         | 1         | 0  | -4             |

| 0  | 0         | 1         | 1  | -6             |

| 0  | 1         | 0         | 0  | -8             |

| 0  | 1         | 0         | 1  | -10            |

| 0  | 1         | 1         | 0  | -12            |

| 0  | 1         | 1         | 1  | -14            |

| 1  | 0         | 0         | 0  | -16            |

| 1  | 0         | 0         | 1  | -18            |

| 1  | 0         | 1         | 0  | -20            |

| 1  | 0         | 1         | 1  | Unallowed      |

| 1  | 1         | 0         | 0  | Unallowed      |

| 1  | 1         | 0         | 1  | Unallowed      |

| 1  | 1         | 1         | 0  | Unallowed      |

| 1  | 1         | 1         | 1  | Unallowed      |

## **NOTE**

An *unallowed* SPI-1 state may result in undefined operation where device behavior is not ensured.

## 8 Application and Implementation

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

## 8.1 Application Information

The LMH6518 device is ideal in applications that require a differential signal path and drive a differential, high-bandwidth analog to digital converter. The LMH6581 has 900 MHz of bandwidth and drives signals up to 1.8  $V_{PP}$ .

Typical applications for the LMH6518 include an oscilloscope AFE, gain control in a radio receiver, and a data acquisition system.

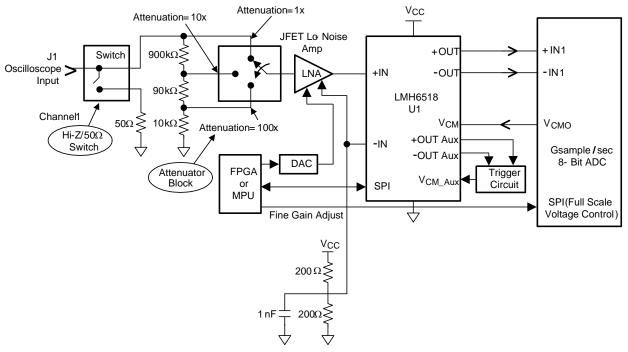

#### 8.2 Typical Application

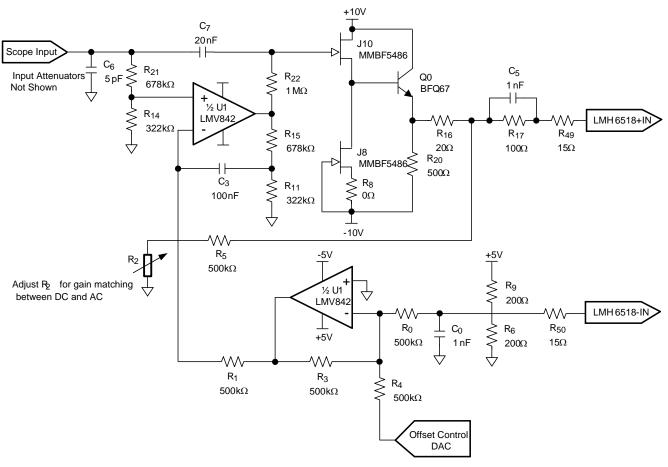

#### 8.2.1 Oscilloscope Front End

Copyright © 2016, Texas Instruments Incorporated

Figure 58. Digital Oscilloscope Front-End

## 8.2.1.1 Design Requirements

An oscilloscope is used to sample signals from millivolts to volts. To make the best use of the limited ADC input range, the oscilloscope input circuitry must have a wide gain range.

In this design example, the LMH6518 is driving an ADC12J2700 and has the following requirements:

- Common mode voltage = 1.225 V

- Full scale voltage = 650 mV<sub>PP</sub> to 800 mV<sub>PP</sub>

- Bandwidth = 900 MHz

- Trigger channel

- Spurious free dynamic range = 50 dB

## **Typical Application (continued)**

#### 8.2.1.2 Detailed Design Procedure

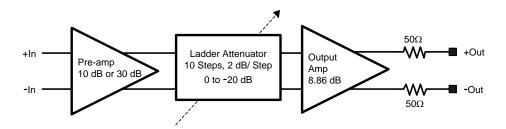

Figure 59 shows a block diagram of the LMH6518's main output signal path.

Figure 59. LMH6518 Signal Path Block Diagram

The auxiliary output (not shown) uses another but similar output amplifier that taps into the ladder attenuator output. In this data sheet, preamp gain of 30 dB is referred to as high gain (HG), and preamp gain of 10 dB as low gain (LG).

The LMH6518 2-dB/step gain resolution and 40-dB adjustment range (from -1.16 dB to 38.8 dB) allows this device to be used with the TI Gsps ADCs which have full scale (FS) adjustment through their extended control mode (ECM) to provide near-continuous variability (8.5-mdB resolution) which covers 42.6 dB FS input range using Equation 1.

$$(20 \times \log \frac{920 \text{ mV}_{PP}}{6.8 \text{ mV}_{PP}} = 42.6 \text{ dB})$$

(1)

TI's Gsps ECM control allows the ADC FS to be set using the ADC SPI bus. The ADC FS voltage range is from 560 mV to 840 mV with 9 bits of FS voltage control.

The ADC ECM gain resolution is calculated with Equation 2.

Gain Resolution = 20 log

$$\frac{0.56 + \left(\frac{0.84 - 0.56}{2 \times 512}\right)}{0.56 - \left(\frac{0.84 - 0.56}{2 \times 512}\right)} = 8.5 \text{ mdB}$$

(2)

However, the *recommended* ADC FS operating range is narrower; it is from 595 mV to 805 mV with 700 mV<sub>PP</sub> as the mid-point. Raising the value of ADC FS voltage is tantamount to reducing the signal path gain to accommodate a larger input and vice versa, thus providing a method of gain fine-adjust. The ADC ECM gain adjustment is  $\neg 1.21$  dB as in Equation 3.

$$(= 20 \times \log \frac{700 \text{ mV}}{805 \text{ mV}}) \text{ to } +1.41 \text{ dB}$$

$$(= 20 \times \log \frac{700 \text{ mV}}{595 \text{ mV}})$$

(3)

Because the ADC FS fine-adjust range of 2.62 dB (= 1.41 dB + 1.21 dB) is larger than the LMH6518's 2-dB/step resolution, there is always at least one LMH6518 gain setting to accommodate any FS signal from 6.8 mV<sub>PP</sub> to 920 mV<sub>PP</sub>, at the LMH6518 input, with 0.62 dB (= 2.62-2) overlap.

## **Typical Application (continued)**

Assuming a nominal 0.7-V<sub>PP</sub> output, the LMH6518's minimum FS input swing is limited by the maximum signal path gain possible and vice versa with Equation 4.

Maximum LMH6518 FS Input

$$\frac{0.7 \text{ V}_{PP}}{10\left(\frac{(38.8 + 1.41) \text{ dB}}{20}\right)} = 6.8 \text{ mV}_{PP}$$

(4)

(or 8 mV<sub>PP</sub> with no ADC fine adjust in Equation 5)

Maximum LMH6518 FS Input

$$\frac{0.7 \text{ V}_{PP}}{10 \left( \frac{(-1.16 - 1.21) \text{ dB}}{20} \right)} = 920 \text{ mV}_{PP}$$

(5)

(or 800 mV<sub>PP</sub> with no ADC FS adjust)

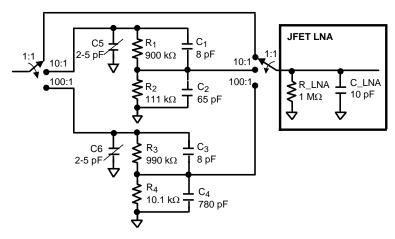

To accommodate a higher FS input, an additional attenuator is required before the LMH6518. This front-end attenuator is shown in the Figure 58 with its details shown in Figure 69. The highest minimum attenuation level is determined by the largest FS input signal (FS<sub>max</sub>) in Equation 6.

Attenuation (dB) = 20 x log

$$\frac{FS_{MAX} (V_{PP})}{800 \text{ mV}_{PP}}$$

(6)

So, to accommodate 80 V<sub>PP</sub>, 40 dB minimum attenuation is required before the LMH6518.

In a typical oscilloscope application, the voltage range encountered is from 1 mV/DIV to 10 V/DIV with 8 vertical divisions visible on the screen. One of the primary concerns in a digital oscilloscope is SNR which translates to display trace width to thickness. Typically, oscilloscope manufacturers require the noise level to be low enough so that the *no-input* visible trace width is less than 1% of FS. Experience shows that this corresponds to a minimum SNR of 52 dB.

The factors that influence SNR are:

- Scope front end noise (Front-end attenuator + scope probe Hi-Z buffer which is discussed later in this data sheet and shown in Figure 58)

- LMH6518

- ADC

LMH6518 related SNR factors are:

- Bandwidth

- Preamp used (Preamp HG or LG)

- Ladder attenuation

- Signal level

SNR increases with the inverse square root of the bandwidth. So, reducing bandwidth from 450 MHz to 200 MHz, for example, improves SNR by 3.5 dB as seen in Equation 7.

$$(20 \times \log \frac{\sqrt{450 \text{ MHz}}}{\sqrt{200 \text{ MHz}}} = 3.5 \text{ dB})$$

(7)

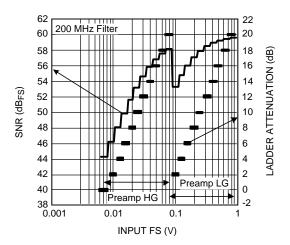

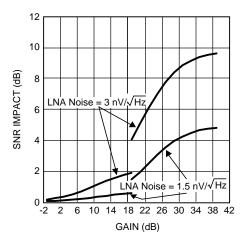

The other factors listed above, preamp and ladder attenuation, depend on the signal level and also impact SNR. The combined effect of these factors is summarized in Figure 60, where SNR is plotted as a function of the LMH6518 FS input voltage (assuming scope bandwidth of 200 MHz) and not including the ADC and the front end noise.

#### Typical Application (continued)

Figure 60. LMH6518 SNR and Ladder Attenuation Used vs Input

As seen in Figure 60, SNR of at least 52 dB is maintained for FS inputs above 24 mV<sub>PP</sub> (3 mV/DIV on a scope) assuming the LMH6518's internal 200 MHz filter is enabled. Most oscilloscope manufacturers relax the SNR specifications to 40 dB for the highest gain (lowest scope voltage setting). From Figure 60, LMH6518's minimum SNR is 43.5 dB, thereby meeting the relaxed SNR specification for the lower range of scope front panel voltages.

In Figure 60, the step-change in SNR near Input FS of 90 mV<sub>PP</sub> is the transition point from preamp LG to preamp HG with a subsequent 3 dB difference due to the preamp HG to 20-dB ladder attenuation's lower output noise compared to preamp LG to 2-dB ladder attenuation's noise. Judicious choice of front-end attenuators ensures that the 52-dB SNR specification is maintained for scope FS inputs ≥24 mV<sub>PP</sub> by confining the LMH6518 gain range to the lower 30.5 dB using Equation 8 from the total range of 40 dB (= 38.8 – (-1.16)) is possible.

$$(= 20 \times \log \frac{0.8 \text{ V}_{PP}}{24 \text{ mV}_{PP}})$$

(8)

For example, to cover the range of 1 mV/DIV to 10 V/DIV (80 dB range), Table 5 lists a configuration which affords good SNR.

Table 5. Oscilloscope Example Including Front-End Attenuators

| ROW | SCOPE FS<br>INPUT (V <sub>PP</sub> ) | S, SCOPE VERTICAL<br>SCALE (V/DIV) | PREAMP | LADDER<br>ATTENUATION<br>RANGE (dB) | A, FRONT-END<br>ATTENUATION<br>(V/V) | MINIMUM SNR (dB)<br>WITH 200 MHz FILTER |

|-----|--------------------------------------|------------------------------------|--------|-------------------------------------|--------------------------------------|-----------------------------------------|