Order

Now

Texas INSTRUMENTS bq24153A, bq24156A bq24158, bq24159

SLUSAB0D-OCTOBER 2010-REVISED APRIL 2016

# bg2415x Fully Integrated Switch-Mode One-Cell Li-Ion Charger With Full USB Compliance and USB-OTG Support

bq24153A, bq24156A, bq24159

## **Features**

- Charge Faster than Linear Chargers

- High-Accuracy Voltage and Current Regulation

- Input Current Regulation Accuracy: ±5% (100) mA and 500 mA)

- Charge Voltage Regulation Accuracy: ±0.5% (25°C), ±1% (0°C to 125°C)

- Charge Current Regulation Accuracy: ±5%

- Input Voltage Based Dynamic Power Management (VIN DPM)

- Bad Adaptor Detection and Rejection

- Safety Limit Register for Maximum Charge Voltage and Current Limiting

- High-Efficiency Mini-USB/AC Battery Charger for • Single-Cell Li-Ion and Li-Polymer Battery Packs

- 20-V Absolute Maximum Input Voltage Rating

- 9-V Maximum Operating Input Voltage-• bq24156A/9

- 6-V Maximum Operating Input Voltagebq24153A/8

- Built-In Input Current Sensing and Limiting

- Integrated Power FETs for Up To 1.55-A Charge Rate

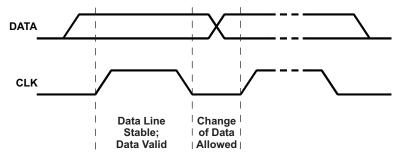

- Programmable Charge Parameters through I<sup>2</sup>C<sup>™</sup> Compatible Interface (up to 3.4 Mbps):

- Input Current Limit

- VIN DPM Threshold

- Fast-Charge/Termination Current

- Charge Regulation Voltage (3.5 V to 4.44 V)

- Low Charge Current Mode Enable/Disable

- Safety Timer with Reset Control \_

- Termination Enable/Disable

- Support up to 1.55 A Charge Current Using 55mΩ Sensing Resistor

- Synchronous Fixed-Frequency PWM Controller Operating at 3 MHz With 0% to 99.5% Duty Cycle

- Automatic High Impedance Mode for Low Power Consumption

- Robust Protection

- Reverse Leakage Protection Prevents Battery Drainage

- Thermal Regulation and Protection

- Input/Output Overvoltage Protection

- Status Output for Charging and Faults

- USB Friendly Boot-Up Sequence

- Automatic Charging •

- Power Up System without Battery bg24158/9

- Boost Mode Operation for USB OTG: (bq24153A/8 only)

- Input Voltage Range (from Battery): 2.5 V to \_ 4.5 V

- Output for V<sub>BUS</sub>: 5.05 V/ 200 mA

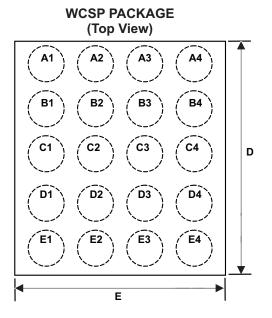

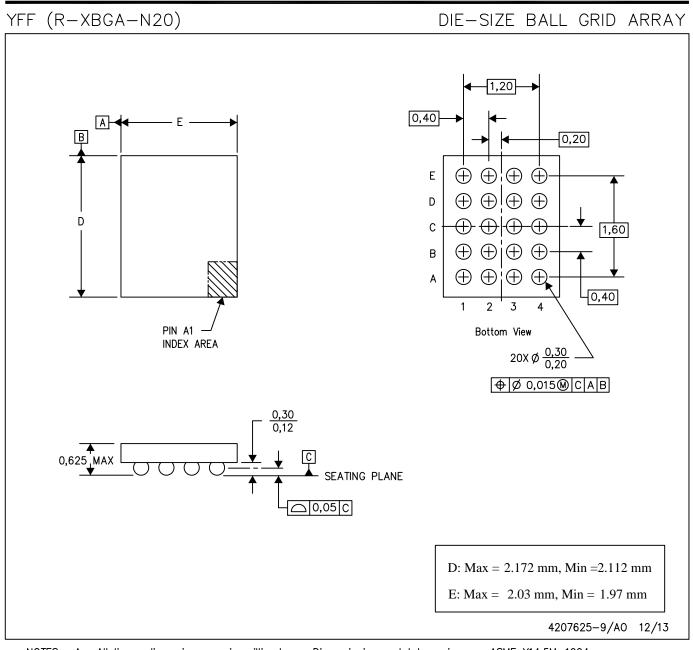

- 2.1 mm x 2 mm 20-Pin WCSP Package

#### 2 Applications

- Mobile and Smart Phones

- **MP3 Players**

- Handheld Devices

## 3 Description

The bg24153A/6A/8/9 is a compact, flexible, highefficiency, **USB-friendly** switch-mode charge management device for single-cell Li-ion and Lipolymer batteries used in a wide range of portable applications. The charge parameters can be programmed through an I<sup>2</sup>C interface. The IC integrates a synchronous PWM controller, power MOSFETs, input current sensing, high-accuracy and and voltage regulation, current charge termination, into a small WCSP package.

## Device Information<sup>(1)</sup>

| PART NUMBER                             | PACKAGE     | BODY SIZE (NOM) |

|-----------------------------------------|-------------|-----------------|

| bq24153A, bq24156A,<br>bq24158, bq24159 | 20-Pin WCSP | 2.1 mm x 2 mm   |

(1) For all available packages, see the orderable addendum at the end of the datasheet.

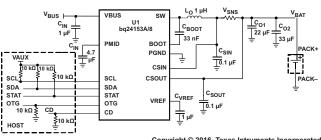

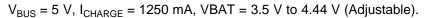

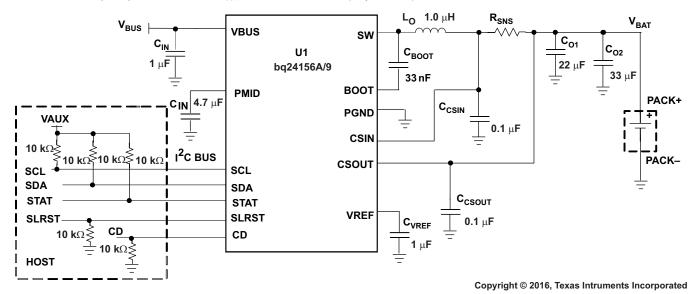

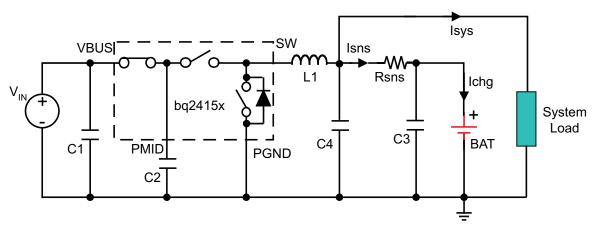

## Typical Application Circuit

Copyright © 2016, Texas Intruments Incorporated

## **Table of Contents**

| 1 | Feat | tures 1                            |

|---|------|------------------------------------|

| 2 | Арр  | lications1                         |

| 3 | Des  | cription1                          |

| 4 |      | ision History2                     |

| 5 | Des  | cription (Continued)4              |

| 6 | Dev  | ice Comparisons 4                  |

| 7 | Pin  | Configuration and Functions5       |

| 8 | Spe  | cifications6                       |

|   | 8.1  | Absolute Maximum Ratings 6         |

|   | 8.2  | ESD Ratings 6                      |

|   | 8.3  | Recommended Operating Conditions 6 |

|   | 8.4  | Thermal Information 6              |

|   | 8.5  | Electrical Characteristics7        |

|   | 8.6  | Timing Requirements 11             |

|   | 8.7  | Typical Characteristics 12         |

| 9 | Deta | ailed Description 14               |

|   | 9.1  | Overview 14                        |

|   | 9.2  | Functional Block Diagram 15        |

|   | 9.3  | Feature Description 17             |

|   | 9.4  | Device Functional Modes 21         |

|   | 9.5  | Programming                        |

|    | 9.6  | Register Maps                       | 30 |

|----|------|-------------------------------------|----|

| 10 | Арр  | lication and Implementation         | 34 |

|    | 10.1 | Application Information             | 34 |

|    | 10.2 | Typical Application                 | 34 |

|    | 10.3 | System Example                      | 39 |

| 11 | Pow  | ver Supply Recommendations          | 40 |

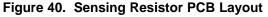

|    | 11.1 | System Load After Sensing Resistor  | 40 |

|    | 11.2 | System Load Before Sensing Resistor | 41 |

| 12 | Lay  | out                                 | 42 |

|    | 12.1 | Layout Guidelines                   | 42 |

|    | 12.2 | Layout Example                      | 43 |

| 13 | Dev  | ice and Documentation Support       | 44 |

|    | 13.1 | Third-Party Products Disclaimer     | 44 |

|    | 13.2 | Related Links                       | 44 |

|    | 13.3 | Community Resources                 | 44 |

|    | 13.4 | Trademarks                          | 44 |

|    | 13.5 | Electrostatic Discharge Caution     |    |

|    | 13.6 | Glossary                            | 44 |

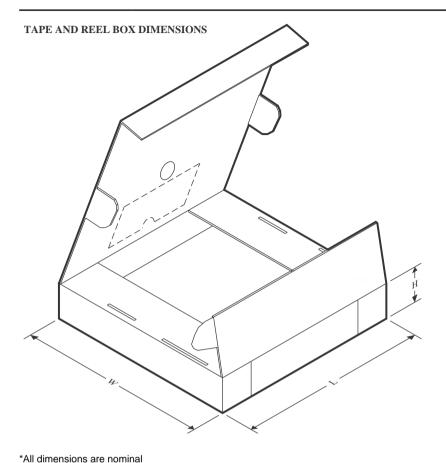

| 14 |      | hanical, Packaging, and Orderable   |    |

|    | Info | rmation                             | -  |

|    | 14.1 | Package Summary                     | 45 |

|    |      |                                     |    |

## 4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

#### Changes from Revision C (July 2013) to Revision D

Page

| • | Added the Device Information table, ESD Ratings table, Detailed Description section, Application and Implementation section, Power Supply Recommendation section, Layout section, Device and Documentation Support section, and the Mechanical, Packaging, and Orderable Information section |

|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| • | Changed Features bullet From: "1.5-A Charge Rate" To: "1.55-A Charge Rate"                                                                                                                                                                                                                   |

| • | Added Features bullet: "Support up to 1.55ASensing Resistor " 1                                                                                                                                                                                                                              |

| • | Added information to the Device Comparisons table                                                                                                                                                                                                                                            |

| • | Changed t <sub>32S</sub> in the <i>Timing Requirements</i> table, PROTECTION section, MAX value From: 32s To 40s 11                                                                                                                                                                          |

| • | Added information to bullet note at Table 9 for clarification                                                                                                                                                                                                                                |

|   |                                                                                                                                                                                                                                                                                              |

| Changes from Revision B (August 2012) to Revision C       Page         • Changed Boot capacitor value from 10 nF to 33 nF in Typical Application Circuit       • Changed BOOT capacitor value from 10 nF to 33 nF in Pin Functions Description         • Changed BOOT capacitor value from 10 nF to 33 nF in Pin Functions Description       • Other Pin Functions Description | ge                                                                                       |     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|-----|

| •                                                                                                                                                                                                                                                                                                                                                                              | Changed Boot capacitor value from 10 nF to 33 nF in Typical Application Circuit          | . 1 |

| •                                                                                                                                                                                                                                                                                                                                                                              | Changed BOOT capacitor value from 10 nF to 33 nF in Pin Functions Description            | . 5 |

| •                                                                                                                                                                                                                                                                                                                                                                              | Changed C <sub>BOOT</sub> capacitor value from 10 nF to 33 nF in Figure 25 and Figure 36 | 34  |

## Changes from Revision A (February 2012) to Revision B

| • | Changed the revision to Rev B, August 2012 1                                                                    |

|---|-----------------------------------------------------------------------------------------------------------------|

| • | Deleted the last sentence in the PIN Functions table: Name CD, in the description column                        |

| • | Changed I <sub>O(CHARGE)</sub> Test Conditions statement from "V <sub>(LOWV)</sub> " to "V <sub>(SHORT)</sub> " |

| • | Deleted from the CD Pin (Charge Disable) section the last sentence: In 15-minute32-second timer                 |

| CI | hanges from Original (October 2010) to Revision A | Pag | e |

|----|---------------------------------------------------|-----|---|

| •  | Added bq24159 throughout this data sheet.         |     | 1 |

| •  | Changed the Device Comparisons table              |     | 4 |

SLUSAB0D-OCTOBER 2010-REVISED APRIL 2016

www.ti.com

## **5** Description (Continued)

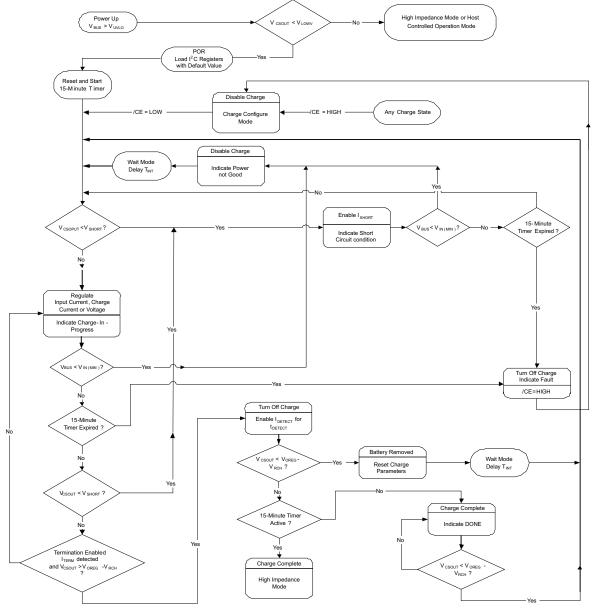

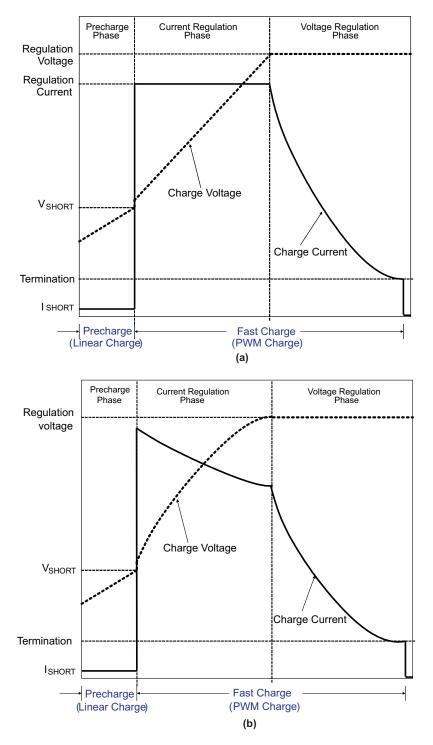

The IC charges the battery in three phases: conditioning, constant current and constant voltage. The input current is automatically limited to the value set by the host. Charge is terminated based on battery voltage and user-selectable minimum current level. A safety timer with reset control provides a safety backup for I<sup>2</sup>C interface. During normal operation, The IC automatically restarts the charge cycle if the battery voltage falls below an internal threshold and automatically enters sleep mode or high impedance mode when the input supply is removed. The charge status can be reported to the host using the I<sup>2</sup>C interface. During the charging process, the IC monitors its junction temperature (T<sub>J</sub>) and reduces the charge current once T<sub>J</sub> increases to about 125°C. To support USB OTG device, bq24153A/8 can provide VBUS (5.05 V) by boosting the battery voltage. The IC is available in 20-pin WCSP package.

## 6 Device Comparisons

| PART NUMBER                                                                                                                  | bq24153A                             | bq24156A   | bq24158                              | bq24159   |

|------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|------------|--------------------------------------|-----------|

| VOVP (V)                                                                                                                     | 6.5                                  | 9.8        | 6.5                                  | 9.8       |

| D4 Pin Definition                                                                                                            | OTG                                  | SLRST      | OTG                                  | SLRST     |

| $I_{CHARGE(MAX)}$ at POR in 15-minute mode with $R_{(SNS)}$ = 68 m $\Omega$ (55 m $\Omega$ ) and OTG=High on bq24153A/8 (mA) | 325 (402)                            | 325 (N/A)  | 325 (402)                            | 325 (N/A) |

| $I_{CHARGE(MAX)}$ in HOST mode with $R_{(SNS)} = 68 \text{ m}\Omega (55 \text{ m}\Omega)$                                    | 1.25 (1.55A)                         | 1.55 (N/A) | 1.25 (1.55A)                         | 1.55(N/A) |

| and Safety Limit Register increased from default (A) (1)                                                                     | 1.55                                 | N/A        | 1.55                                 | N/A       |

| Output regulation voltage at POR (V)                                                                                         | 3.54                                 | 3.54       | 3.54                                 | 3.54      |

| Boost Function                                                                                                               | Yes                                  | No         | Yes                                  | No        |

| Input Current Limit in 15Min Mode                                                                                            | 100mA (OTG=LOW);<br>500mA (OTG=High) | 500mA      | 100mA (OTG=LOW);<br>500mA (OTG=High) | 500mA     |

| Battery Detection at Power Up                                                                                                | Yes                                  | Yes        | No                                   | No        |

| I2C Address                                                                                                                  | 6BH                                  | 6AH        | 6AH                                  | 6AH       |

| PN1 (bit4 of 03H)                                                                                                            | 1                                    | 0          | 1                                    | 0         |

| PN0 (bit3 of 03H)                                                                                                            | 0                                    | 0          | 0                                    | 0         |

| Safety Timer and WD Timer                                                                                                    | Enabled                              | Enabled    | Enabled                              | Enabled   |

(1) See Application Section for more explanation and calculations on using different sense resistors.

4

Copyright © 2010–2016, Texas Instruments Incorporated

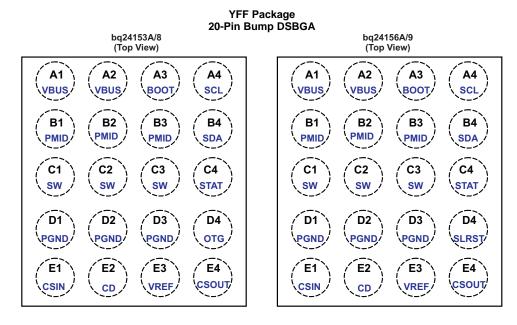

## 7 Pin Configuration and Functions

#### **Pin Functions**

| PIN                        |            | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

|----------------------------|------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME                       | NO.        | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| BOOT                       | A3         | I/O | Bootstrap capacitor connection for the high-side FET gate driver. Connect a 33-nF ceramic capacitor (voltage rating ≥ 10 V) from BOOT pin to SW pin.                                                                                                                                                                                                                                                                                                                   |  |

| CD                         | E2         | I   | Charge disable control pin. CD=0, charge is enabled. CD=1, charge is disabled and VBUS pin is high impedance to GND.                                                                                                                                                                                                                                                                                                                                                   |  |

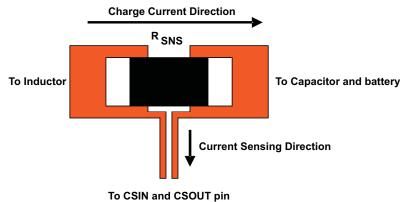

| CSIN                       | E1         | I   | Charge current-sense input. Battery current is sensed across an external sense resistor. A 0.1-µF ceramic capacitor to PGND is required.                                                                                                                                                                                                                                                                                                                               |  |

| CSOUT                      | E4         | I   | Battery voltage and current sense input. Bypass it with a ceramic capacitor (minimum 0.1 $\mu$ F) to PGND if there are long inductive leads to battery.                                                                                                                                                                                                                                                                                                                |  |

| OTG<br>(bq24153A/8 only)   | D4         | I   | oost mode enable control or input current limiting selection pin. When OTG is in active status, bq24153A forced to operate in boost mode. It has higher priority over I <sup>2</sup> C control and can be disabled using the ontrol register. At POR while in 15-min mode, the OTG pin is default to be used as the input current limit election pin. The I <sup>2</sup> C register is ignored at startup. When OTG=High, I <sub>IN_LIMIT</sub> =500mA and when OTG=Lo |  |

| PGND                       | D1, D2, D3 |     | Power ground                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| PMID                       | B1, B2, B3 | I/O | Connection point between reverse blocking FET and high-side switching FET. Bypass it with a minimum of 3.3-µF capacitor from PMID to PGND.                                                                                                                                                                                                                                                                                                                             |  |

| SCL                        | A4         | Ι   | $I^2C$ interface clock. Connect a 10-kΩ pullup resistor to 1.8V rail (V <sub>AUX</sub> = V <sub>CC_HOST</sub> )                                                                                                                                                                                                                                                                                                                                                        |  |

| SDA                        | B4         | I/O | l <sup>2</sup> C interface data. Connect a 10-kΩ pullup resistor to 1.8V rail (V <sub>AUX</sub> = V <sub>CC_HOST</sub> )                                                                                                                                                                                                                                                                                                                                               |  |

| SLRST<br>(bq24156A/9 only) | D4         | I   | Safety limit register reset control. When SLRST=0, bq24156A/9 resets all the safety limits (06H) to default values, regardless of the write actions to safety limits registers (06H). When SLRST=1, bq24156A/9 can program the safety limit register until any write action to other registers locks the programmed safety limits.                                                                                                                                     |  |

| STAT                       | C4         | 0   | Charge status pin. Pull low when charge in progress. Open drain for other conditions. During faults, a 128- $\mu$ s pulse is sent out. STAT pin can be disabled by the EN_STAT bit in control register. STAT can be used to drive a LED or communicate with a host processor.                                                                                                                                                                                          |  |

| SW                         | C1, C2, C3 | 0   | Internal switch to output inductor connection.                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| VBUS                       | A1, A2     | I/O | Charger input voltage. Bypass it with a 1- $\mu$ F ceramic capacitor from VBUS to PGND. It also provides power to the load during boost mode (bq24153A/8 only).                                                                                                                                                                                                                                                                                                        |  |

| VREF                       | E3         | 0   | Internal bias regulator voltage. Connect a 1µF ceramic capacitor from this output to PGND. External load on VREF is not recommended.                                                                                                                                                                                                                                                                                                                                   |  |

TEXAS INSTRUMENTS

www.ti.com

## 8 Specifications

## 8.1 Absolute Maximum Ratings<sup>(1) (2)</sup>

over operating free-air temperature range (unless otherwise noted)

|                                                       |                                                         | bq24153 | bq24153A/6A/8/9  |      |

|-------------------------------------------------------|---------------------------------------------------------|---------|------------------|------|

|                                                       |                                                         | MIN     | MAX              | UNIT |

| Supply voltage (with respect to PGND <sup>(3)</sup> ) | VBUS; $V_{PMID} \ge V_{BUS} - 0.3 V$                    | -2      | 20               | V    |

| Input voltage (with respect to PGND <sup>(3)</sup> )  | SCL, SDA, OTG, SLRST, CSIN, CSOUT, CD                   | -0.3    | 7                | V    |

|                                                       | PMID, STAT                                              | -0.3    | 20               | V    |

| Output voltage (with respect to PGND <sup>(3)</sup> ) | VREF                                                    |         | 7                | V    |

|                                                       | SW, BOOT                                                | -0.7    | 20               | V    |

| Voltage difference between CSIN and CSOL              | IT inputs (V <sub>(CSIN)</sub> – V <sub>(CSOUT)</sub> ) | -7      | 7                | V    |

| Voltage difference between BOOT and SW i              | nputs (V <sub>(BOOT)</sub> – V <sub>(SW)</sub> )        | -0.3    | 7                | V    |

| Voltage difference between VBUS and PMID              | ) inputs (V <sub>(VBUS)</sub> – V <sub>(PMID)</sub> )   | -7      | 0.7              | V    |

| Voltage difference between PMID and SW in             | puts (V <sub>(PMID)</sub> – V <sub>(SW)</sub> )         | -0.7    | 20               | V    |

| Output sink                                           | STAT                                                    |         | 10               | mA   |

| Output Current (average)                              | SW                                                      | 1.5     | 5 <sup>(2)</sup> | А    |

| T <sub>A</sub> Operating free-air temperature range   | · ·                                                     | -30     | 85               | °C   |

| T <sub>J</sub> Junction temperature                   |                                                         | -40     | 125              | °C   |

| T <sub>stg</sub> Storage temperature                  |                                                         | -45     | 150              | °C   |

(1) Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability. All voltage values are with respect to the network ground terminal unless otherwise noted.

(2) Duty cycle for output current should be less than 50% for 10- year life time when output current is above 1.25A.

(3) All voltages are with respect to PGND if not specified. Currents are positive into, negative out of the specified terminal, if not specified. Consult Packaging Section of the data sheet for thermal limitations and considerations of packages.

## 8.2 ESD Ratings

|             |                         |                                                                                                | VALUE | UNIT |

|-------------|-------------------------|------------------------------------------------------------------------------------------------|-------|------|

|             |                         | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins <sup>(1)</sup>                    | ±2000 |      |

| $V_{(ESD)}$ | Electrostatic discharge | Charged device model (CDM), per JEDEC specification JESD22-C101, all $\ensuremath{pins^{(2)}}$ | ±500  | V    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

## 8.3 Recommended Operating Conditions

|                  |                                      | MIN | NOM | MAX              | UNIT |

|------------------|--------------------------------------|-----|-----|------------------|------|

| V <sub>BUS</sub> | Supply voltage, bq24153A/8           | 4   |     | 6 <sup>(1)</sup> | V    |

| V <sub>BUS</sub> | Supply voltage, bq24156A/9           | 4   |     | 9 <sup>(1)</sup> | V    |

| TJ               | Operating junction temperature range | -40 |     | 125              | °C   |

(1) The inherent switching noise voltage spikes should not exceed the absolute maximum rating on either the BOOST or SW pins. A *tight* layout minimizes switching noise.

#### 8.4 Thermal Information

|                      |                                              | bq24153A/6A/8/9 |      |

|----------------------|----------------------------------------------|-----------------|------|

|                      | THERMAL METRIC <sup>(1)</sup>                | YFF (DSBGA)     | UNIT |

|                      |                                              | 20 Pins         |      |

| $R_{\thetaJA}$       | Junction-to-ambient thermal resistance       | 85              | °C/W |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 25              | °C/W |

| $R_{\thetaJB}$       | Junction-to-board thermal resistance         | 55              | °C/W |

| ΨJT                  | Junction-to-top characterization parameter   | 4               | °C/W |

| Ψ <sub>JB</sub>      | Junction-to-board characterization parameter | 50              | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

#### **Thermal Information (continued)**

|                       |                                              | bq24153A/6A/8/9 |      |

|-----------------------|----------------------------------------------|-----------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | YFF (DSBGA)     | UNIT |

|                       |                                              | 20 Pins         |      |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | n/a             | °C/W |

### 8.5 Electrical Characteristics

Circuit of Figure 25, VBUS = 5 V, HZ\_MODE = 0, OPA\_MODE = 0 (CD = 0),  $T_J = -40^{\circ}$ C to 125°C,  $T_J = 25^{\circ}$ C for typical values (unless otherwise noted)

|                                                                 | PARAMETER                                                                                    | TEST CONDITIONS                                                                                                                                                          | MIN   | TYP | MAX  | UNIT |

|-----------------------------------------------------------------|----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----|------|------|

| INPUT CUR                                                       | RENTS                                                                                        |                                                                                                                                                                          |       |     |      |      |

|                                                                 |                                                                                              | VBUS > VBUS(min), PWM switching                                                                                                                                          |       | 10  |      | mA   |

| (VBUS) VBUS supply current control                              |                                                                                              | VBUS > VBUS(min), PWM NOT switching                                                                                                                                      |       |     | 5    |      |

| . ,                                                             |                                                                                              | 0°C < T <sub>J</sub> < 85°C, CD=1 or HZ_MODE=1                                                                                                                           |       | 15  | 23   | μA   |

| I <sub>lgk</sub>                                                | Leakage current from battery to VBUS pin                                                     | $0^{\circ}\text{C} < \text{T}_{\text{J}} < 85^{\circ}\text{C}, \text{ V}_{(\text{CSOUT})} = 4.2 \text{ V}, \text{ High Impedance}$ mode, VBUS = 0 V                      |       |     | 5    | μΑ   |

|                                                                 | Battery discharge current in High Impedance mode, (CSIN, CSOUT, SW pins)                     | $0^{\circ}C$ < $T_{J}$ < $85^{\circ}C,$ $V_{(CSOUT)}$ = 4.2 V, High Impedance mode, V = 0 V, SCL, SDA, OTG = 0 V or 1.8 V                                                |       |     | 23   | μΑ   |

| VOLTAGE                                                         | REGULATION                                                                                   |                                                                                                                                                                          |       |     | ·    |      |

| V <sub>(OREG)</sub>                                             | Output regulation voltage programable range                                                  | Operating in voltage regulation, programmable                                                                                                                            | 3.5   |     | 4.44 | V    |

|                                                                 |                                                                                              | $T_A = 25^{\circ}C$                                                                                                                                                      | -0.5% |     | 0.5% |      |

|                                                                 | Voltage regulation accuracy                                                                  |                                                                                                                                                                          | -1%   |     | 1%   |      |

| CURRENT                                                         | REGULATION (FAST CHARGE)                                                                     | 1                                                                                                                                                                        | 1     |     |      |      |

|                                                                 |                                                                                              | $ \begin{array}{l} bq24153A/8, \ V_{(SHORT)} \leq V_{(CSOUT)} < V_{(OREG)}, \\ VBUS > V_{(SLP)}, \ R_{(SNS)} = 68 \ m\Omega, \ LOW\_CHG=0, \\ Programmable \end{array} $ | 550   |     | 1250 | mA   |

| I <sub>O(CHARGE)</sub> Output charge current programmable range | Output charge current programmable range                                                     | $\begin{array}{l} bq24156A/9, V_{(SHORT)} \leq V_{(CSOUT)} < V_{(OREG)}, \\ VBUS > V_{(SLP)}, R_{(SNS)} = 68 \ m\Omega, \ LOW\_CHG=0, \\ Programmable \end{array}$       | 550   |     | 1550 | mA   |

|                                                                 | Low charge current (default after POR in 15 min mode) for bq24153A/6A/8/9                    | $V_{SHORT} \le V_{CSOUT} < V_{OREG}$ , VBUS $>V_{SLP}$ ,<br>R <sub>SNS</sub> = 68 m $\Omega$ , LOW_CHG=1, OTG=High for<br>bq24153A/8                                     |       | 325 | 350  | mA   |

|                                                                 | Regulation accuracy of the voltage across                                                    | $37.4 \text{ mV} \le V_{(IREG)} \le 44.2 \text{mV}$                                                                                                                      | -3.5% |     | 3.5% |      |

|                                                                 | $R_{(SNS)}$ (for charge current regulation)<br>$V_{(IREG)} = I_{O(CHARGE)} \times R_{(SNS)}$ | 44.2 mV $\leq$ V <sub>(IREG)</sub>                                                                                                                                       | -3%   |     | 3%   |      |

| WEAK BAT                                                        | TERY DETECTION                                                                               |                                                                                                                                                                          |       |     |      |      |

| V <sub>(LOWV)</sub>                                             | Weak battery voltage threshold programmable range <sup>2</sup> <sup>(1)</sup>                | Adjustable using I <sup>2</sup> C control                                                                                                                                | 3.4   |     | 3.7  | V    |

|                                                                 | Weak battery voltage accuracy                                                                |                                                                                                                                                                          | -5%   |     | 5%   |      |

|                                                                 | Hysteresis for V <sub>(LOWV)</sub>                                                           | Battery voltage falling                                                                                                                                                  |       | 100 |      | mV   |

| CD, OTG ar                                                      | nd SLRST PIN LOGIC LEVEL                                                                     |                                                                                                                                                                          | 1     |     |      |      |

| V <sub>IL</sub>                                                 | Input low threshold level                                                                    |                                                                                                                                                                          |       |     | 0.4  | V    |

| V <sub>IH</sub>                                                 | Input high threshold level                                                                   |                                                                                                                                                                          | 1.3   |     |      | V    |

| I <sub>(bias)</sub>                                             | Input bias current                                                                           | Voltage on control pin is 5 V                                                                                                                                            |       |     | 1.0  | μA   |

|                                                                 | ERMINATION DETECTION                                                                         | <u> </u>                                                                                                                                                                 |       |     |      |      |

| I <sub>(TERM)</sub>                                             | Termination charge current programmable range                                                | $\label{eq:V_(CSOUT)} \begin{array}{l} V_{(CREG)} - V_{(RCH)}, \\ VBUS > V_{(SLP)}, R_{(SNS)} = 68 \ m\Omega, \ Programmable \end{array}$                                | 50    |     | 400  | mA   |

|                                                                 | Population accuracy for termination current                                                  | $3.4 \text{ mV} \le V_{\text{(IREG TERM)}} \le 6.8 \text{ mV}$                                                                                                           | -15%  |     | 15%  |      |

|                                                                 | Regulation accuracy for termination current across R <sub>(SNS)</sub>                        | $6.8 \text{ mV} < V_{(IREG TERM)} \le 17 \text{ mV}$                                                                                                                     | -10%  |     | 10%  |      |

| $V_{(IREG_{TERM})} = I_{O(TERM)} \times$                        | $V_{(IREG_{TERM})} = I_{O(TERM)} \times R_{(SNS)}$                                           | $17 \text{ mV} < V_{(IREG_TERM)} \le 27.2 \text{ mV}$                                                                                                                    | -5.5% |     | 5.5% |      |

| BAD ADAP                                                        | TOR DETECTION                                                                                | (·····································                                                                                                                                   | 1     |     |      |      |

| V <sub>IN</sub> (min)                                           | Input voltage lower limit                                                                    | BAD ADAPTOR DETECTION                                                                                                                                                    | 3.6   | 3.8 | 4.0  | V    |

|                                                                 | Hysteresis for V <sub>IN</sub> (min)                                                         | Input voltage rising                                                                                                                                                     | 100   |     | 200  | mV   |

| ISHORT                                                          | Current source to GND                                                                        | During bad adaptor detection                                                                                                                                             | 20    | 30  | 40   | mA   |

(1) While in 15-min mode, if a battery that is charged to a voltage higher than this voltage is inserted, the charger enters Hi-Z mode and awaits I<sup>2</sup>C commands.

## **Electrical Characteristics (continued)**

Circuit of Figure 25, VBUS = 5 V, HZ\_MODE = 0, OPA\_MODE = 0 (CD = 0),  $T_J = -40^{\circ}$ C to 125°C,  $T_J = 25^{\circ}$ C for typical values (unless otherwise noted)

|                     | PARAMETER                                      | TEST CONDITIONS | MIN | TYP MAX | UNIT |  |  |  |

|---------------------|------------------------------------------------|-----------------|-----|---------|------|--|--|--|

| INPUT BAS           | INPUT BASED DYNAMIC POWER MANAGEMENT           |                 |     |         |      |  |  |  |

| V <sub>IN_DPM</sub> | Input Voltage DPM threshold programmable range |                 | 4.2 | 4.76    | V    |  |  |  |

|                     | VIN DPM threshold accuracy                     |                 | -3% | 1%      |      |  |  |  |

#### **Electrical Characteristics (continued)**

Circuit of Figure 25, VBUS = 5 V, HZ\_MODE = 0, OPA\_MODE = 0 (CD = 0),  $T_J = -40^{\circ}$ C to 125°C,  $T_J = 25^{\circ}$ C for typical values (unless otherwise noted)

| PARAMETER               |                                                                                      | TEST CONDITIONS                                              |                                                                    | MIN  | TYP   | MAX  | UNIT |

|-------------------------|--------------------------------------------------------------------------------------|--------------------------------------------------------------|--------------------------------------------------------------------|------|-------|------|------|

| INPUT CUR               | RENT LIMITING                                                                        |                                                              |                                                                    |      |       |      |      |

|                         |                                                                                      |                                                              | $T_{J} = 0^{\circ}C - 125^{\circ}C$                                | 88   | 93    | 98   | mA   |

|                         |                                                                                      | I <sub>IN</sub> = 100 mA                                     | $T_{J} = -40^{\circ}C - 125^{\circ}C$                              | 86   | 93    | 98   |      |

| I <sub>IN_LIMIT</sub>   | Input current limiting threshold                                                     |                                                              | $T_{J} = 0^{\circ}C - 125^{\circ}C$                                | 450  | 475   | 500  | mA   |

|                         |                                                                                      | I <sub>IN</sub> = 500 mA                                     | $T_{J} = -40^{\circ}C - 125^{\circ}C$                              | 440  | 475   | 500  |      |

| VREF BIAS               | REGULATOR                                                                            | ł.                                                           |                                                                    |      |       |      |      |

| V <sub>REF</sub>        | Internal bias regulator voltage                                                      | VBUS >V <sub>IN</sub> (min)<br>I <sub>(VREF)</sub> = 1 mA, 0 | or V <sub>(CSOUT)</sub> > VBUS(min),<br>C <sub>(VREF)</sub> = 1 μF | 2    |       | 6.5  | V    |

|                         | V <sub>REF</sub> output short current limit                                          |                                                              |                                                                    |      | 30    |      | mA   |

| BATTERY F               | RECHARGE THRESHOLD                                                                   |                                                              |                                                                    | -    |       |      |      |

| V <sub>(RCH)</sub>      | Recharge threshold voltage                                                           | Below $V_{(OREG)}$                                           |                                                                    | 100  | 120   | 150  | mV   |

| STAT OUT                | PUTS                                                                                 |                                                              |                                                                    |      |       |      |      |

| Value                   | Low-level output saturation voltage, STAT pin                                        | $I_{O} = 10 \text{ mA}, \text{ sink}$                        | current                                                            |      |       | 0.55 | V    |

| V <sub>OL(STAT)</sub>   | High-level leakage current for STAT                                                  | Voltage on STA                                               | T pin is 5 V                                                       |      |       | 1    | μΑ   |

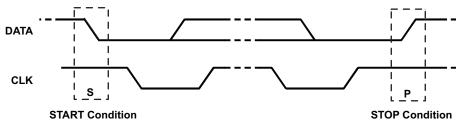

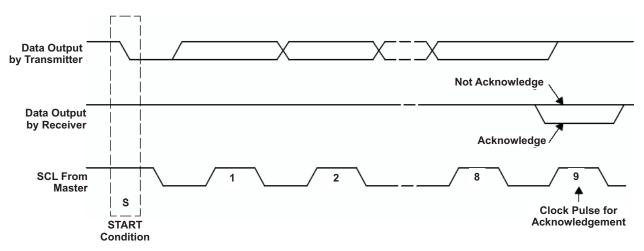

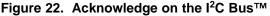

| I <sup>2</sup> C BUS LO | GIC LEVELS AND TIMING CHARACTERISTICS                                                |                                                              |                                                                    |      |       |      |      |

| V <sub>OL</sub>         | Output low threshold level                                                           | $I_{O} = 10 \text{ mA}, \text{ sink}$                        | current                                                            |      |       | 0.4  | V    |

| V <sub>IL</sub>         | Input low threshold level                                                            | V <sub>(pull-up)</sub> = 1.8 V,                              | SDA and SCL                                                        |      |       | 0.4  | V    |

| V <sub>IH</sub>         | Input high threshold level                                                           | V <sub>(pull-up)</sub> = 1.8 V,                              | SDA and SCL                                                        | 1.2  |       |      | V    |

| I(BIAS)                 | Input bias current                                                                   | V <sub>(pull-up)</sub> = 1.8 V,                              | SDA and SCL                                                        |      |       | 1    | μΑ   |

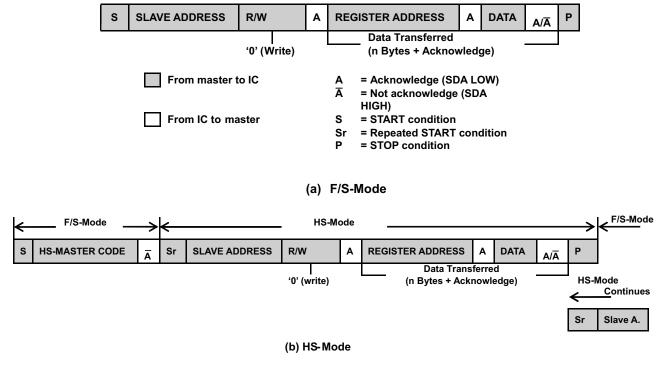

| f <sub>(SCL)</sub>      | SCL clock frequency                                                                  |                                                              |                                                                    |      |       | 3.4  | MHz  |

| BATTERY [               | DETECTION                                                                            |                                                              |                                                                    |      |       |      |      |

| I <sub>(DETECT)</sub>   | Battery detection current before charge done (sink current) $^{(2)}$                 | Begins after terr<br>$V_{(CSOUT)} \le V_{(ORE}$              | nination detected,                                                 |      | -0.5  |      | mA   |

| SLEEP CO                | MPARATOR                                                                             |                                                              |                                                                    |      |       |      |      |

| V <sub>(SLP)</sub>      | Sleep-mode entry threshold,<br>VBUS – V <sub>CSOUT</sub>                             | $2.3 \text{ V} \leq \text{V}_{(\text{CSOUT})}$               | $\leq V_{(OREG)}, V_{BUS}$ falling                                 | 0    | 40    | 100  | mV   |

| V <sub>(SLP_EXIT)</sub> | Sleep-mode exit hysteresis                                                           | $2.3 \text{ V} \leq \text{V}_{(\text{CSOUT})}$               | ≤ V <sub>(OREG)</sub>                                              | 140  | 200   | 260  | mV   |

| UNDERVOL                | TAGE LOCKOUT (UVLO)                                                                  |                                                              |                                                                    |      |       |      |      |

| UVLO                    | IC active threshold voltage                                                          | V <sub>BUS</sub> rising - Exi                                | ts UVLO                                                            | 3.05 | 3.3   | 3.55 | V    |

| UVLO <sub>(HYS)</sub>   | IC active hysteresis                                                                 | V <sub>BUS</sub> falling belo                                | w UVLO - Enters UVLO                                               | 120  | 150   |      | mV   |

| PWM                     |                                                                                      |                                                              |                                                                    |      |       |      |      |

|                         | Voltage from BOOT pin to SW pin                                                      | During charge o                                              | r boost operation                                                  |      |       | 6.5  | V    |

|                         | Internal top reverse blocking MOSFET on-<br>resistance                               | $I_{\rm IN(LIMIT)} = 500 \ {\rm m}$                          | A, Measured from VBUS to PMID                                      |      | 180   | 250  |      |

|                         | Internal top N-channel Switching MOSFET on-<br>resistance                            | Measured from PMID to SW, $V_{BOOT} - V_{SW}$ = 4V           |                                                                    |      | 120   | 250  | mΩ   |

|                         | Internal bottom N-channel MOSFET on-<br>resistance                                   | Measured from SW to PGND                                     |                                                                    |      | 110   | 210  |      |

| f <sub>(OSC)</sub>      | Oscillator frequency                                                                 |                                                              |                                                                    |      | 3.0   |      | MHz  |

|                         | Frequency accuracy                                                                   |                                                              |                                                                    | -10% |       | 10%  |      |

| D <sub>(MAX)</sub>      | Maximum duty cycle                                                                   |                                                              |                                                                    |      | 99.5% |      |      |

| D <sub>(MIN)</sub>      | Minimum duty cycle                                                                   |                                                              |                                                                    | 0    |       |      |      |

|                         | Synchronous mode to non-synchronous mode transition current threshold <sup>(2)</sup> | Low-side MOSF                                                | ET cycle-by-cycle current sensing                                  |      | 100   |      | mA   |

(2) Bottom N-channel FET always turns on for ~30 ns and then turns off if current is too low.

## **Electrical Characteristics (continued)**

Circuit of Figure 25, VBUS = 5 V, HZ\_MODE = 0, OPA\_MODE = 0 (CD = 0),  $T_J = -40^{\circ}$ C to 125°C,  $T_J = 25^{\circ}$ C for typical values (unless otherwise noted)

| PARAMETER               |                                                                    | TEST CONDITIONS                                                                           | MIN  | TYP  | MAX  | UNIT               |

|-------------------------|--------------------------------------------------------------------|-------------------------------------------------------------------------------------------|------|------|------|--------------------|

| CHARGE M                | ODE PROTECTION                                                     | ·                                                                                         |      |      |      |                    |

| V <sub>OVP_IN_USB</sub> | Input VBUS OVP threshold voltage<br>(bq24153A/8)                   | VBUS threshold to turn off converter during charge                                        | 6.3  | 6.5  | 6.7  | V                  |

|                         | V <sub>(OVP_IN_USB)</sub> hysteresis (bq24153A/8)                  | VBUS falling from above V <sub>(OVP_IN_USB)</sub>                                         |      | 170  |      | mV                 |

| V <sub>OVP-IN_DYN</sub> | Input VBUS OVP threshold voltage (bq24156A)                        | Threshold over VBUS to turn off converter during charge                                   | 9.57 | 9.8  | 10   |                    |

|                         | V <sub>(OVP_IN_DYN)</sub> hysteresis (bq24156A/9)                  | VBUS falling from above V <sub>(OVP_IN_DYN)</sub>                                         |      | 140  |      |                    |

| V <sub>OVP</sub>        | Output OVP threshold voltage                                       | $V_{(\text{CSOUT})}$ threshold over $V_{(\text{OREG})}$ to turn off charger during charge | 110  | 117  | 121  | %V <sub>OREG</sub> |

| -                       | V <sub>(OVP)</sub> hysteresis                                      | Lower limit for $V_{(CSOUT)}$ falling from above $V_{(OVP)}$                              |      | 11   |      |                    |

| I <sub>LIMIT</sub>      | Cycle-by-cycle current limit for charge                            | Charge mode operation                                                                     | 1.8  | 2.4  | 3.0  | A                  |

| V                       | Trickle to fast charge threshold                                   | V <sub>(CSOUT)</sub> rising                                                               | 2.0  | 2.1  | 2.2  | V                  |

| V <sub>SHORT</sub>      | V <sub>SHORT</sub> hysteresis                                      | $V_{(CSOUT)}$ falling below $V_{SHORT}$                                                   |      | 100  |      | mV                 |

| I <sub>SHORT</sub>      | Trickle charge charging current                                    | $V_{(CSOUT)} \le V_{SHORT)}$                                                              | 20   | 30   | 40   | mA                 |

| BOOST MOI               | DE OPERATION FOR V <sub>BUS</sub> (OPA_MODE = 1, HZ                | _MODE = 0, bq24153A/8 only)                                                               |      |      |      |                    |

| V <sub>BUS_B</sub>      | Boost output voltage (to VBUS pin)                                 | 2.5V < V <sub>(CSOUT)</sub> < 4.5 V                                                       |      | 5.05 |      | V                  |

|                         | Boost output voltage accuracy                                      | Including line and load regulation                                                        | -3%  |      | 3%   |                    |

| I <sub>BO</sub>         | Maximum output current for boost                                   | $V_{BUS_B}$ = 5.05 V, 2.5 V < $V_{(CSOUT)}$ < 4.5 V                                       | 200  |      |      | mA                 |

| I <sub>BLIMIT</sub>     | Cycle by cycle current limit for boost                             | $V_{BUS_B}$ = 5.05 V, 2.5 V < $V_{(CSOUT)}$ < 4.5 V                                       |      | 1.0  |      | Α                  |

| VBUSOVP                 | Overvoltage protection threshold for boost (VBUS pin)              | Threshold over VBUS to turn off converter during boost                                    | 5.8  | 6.0  | 6.2  | V                  |

|                         | V <sub>BUSOVP</sub> hysteresis                                     | V <sub>BUS</sub> falling from above V <sub>BUSOVP</sub>                                   |      | 162  |      | mV                 |

| V <sub>BATMAX</sub>     | Maximum battery voltage for boost (CSOUT pin)                      | V <sub>(CSOUT)</sub> rising edge during boost                                             | 4.75 | 4.9  | 5.05 | V                  |

| Dittinget               | V <sub>BATMAX</sub> hysteresis                                     | V <sub>(CSOUT)</sub> falling from above V <sub>BATMAX</sub>                               |      | 200  |      | mV                 |

| V                       | Minimum hottom weltage for beest (CCOUT pip)                       | During boosting                                                                           |      | 2.5  |      | V                  |

| V <sub>BATMIN</sub>     | Minimum battery voltage for boost (CSOUT pin)                      | Before boost starts                                                                       |      | 2.9  | 3.05 | V                  |

|                         | Boost output resistance at high-impedance mode (From VBUS to PGND) | CD = 1 or HZ_MODE = 1                                                                     | 217  |      |      | kΩ                 |

| PROTECTIO               | N                                                                  |                                                                                           |      |      |      |                    |

| T <sub>SHTDWN)</sub>    | Thermal trip                                                       |                                                                                           |      | 165  |      |                    |

|                         | Thermal hysteresis                                                 |                                                                                           |      | 10   |      | °C                 |

| T <sub>CF</sub>         | Thermal regulation threshold                                       | Charge current begins to reduce                                                           |      | 120  |      | ]                  |

SLUSAB0D-OCTOBER 2010-REVISED APRIL 2016

www.ti.com

## 8.6 Timing Requirements

|                     |                                                                     |                                                                                                    | MIN      | NOM | MAX | UNIT |

|---------------------|---------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|----------|-----|-----|------|

| WEAK BA             | ATTERY DETECTION                                                    |                                                                                                    |          |     |     |      |

|                     | Deglitch time for weak battery threshold                            | Rising voltage, 2-mV over drive,<br>t <sub>RISE</sub> = 100 ns                                     |          | 30  |     | ms   |

| CHARGE              | TERMINATION DETECTION                                               |                                                                                                    |          |     |     |      |

|                     | Deglitch time for charge termination                                | Both rising and falling, 2-mV<br>overdrive,<br>t <sub>RISE</sub> , t <sub>FALL</sub> = 100 ns      |          | 30  |     | ms   |

| BAD ADA             | APTER DETECTION                                                     |                                                                                                    |          |     |     |      |

|                     | Deglitch time for VBUS rising above $V_{IN}(min)$                   | Rising voltage, 2-mV overdrive,<br>t <sub>RISE</sub> = 100 ns                                      |          | 30  |     | ms   |

| t <sub>INT</sub>    | Detection Interval                                                  | Input power source detection                                                                       |          | 2   |     | S    |

| BATTER              | Y RECHARGE THRESHOLD                                                |                                                                                                    |          |     |     |      |

|                     | Deglitch time                                                       | V <sub>(SCOUT)</sub> decreasing below<br>threshold,<br>t <sub>FALL</sub> = 100 ns, 10-mV overdrive |          | 130 |     | ms   |

| BATTER              | Y DETECTION                                                         |                                                                                                    |          |     |     |      |

| t <sub>DETECT</sub> | Battery detection time                                              |                                                                                                    |          | 262 |     | ms   |

| SLEEP C             | OMPARATOR                                                           |                                                                                                    |          |     |     |      |

|                     | Deglitch time for VBUS rising above $V_{(SLP)}$ + $V_{(SLP\_EXIT)}$ | Rising voltage, 2-mV overdrive,<br>t <sub>RISE</sub> = 100 ns                                      |          | 30  |     | ms   |

| UNDERV              | OLTAGE LOCKOUT (UVLO)                                               |                                                                                                    |          |     |     |      |

|                     | Power up delay                                                      |                                                                                                    |          | 140 |     | ms   |

| PROTEC              | TION                                                                |                                                                                                    |          |     |     |      |

| t <sub>32S</sub>    | 32 second watchdog (WD) timer                                       | 32 Second or HOST mode                                                                             | 15 32 40 |     | 40  | S    |

| t <sub>15M</sub>    | 15 minute safety timer                                              | 15 Minute mode                                                                                     | 12       |     | 15  | m    |

## bq24153A, bq24156A bq24158, bq24159

SLUSAB0D-OCTOBER 2010-REVISED APRIL 2016

www.ti.com

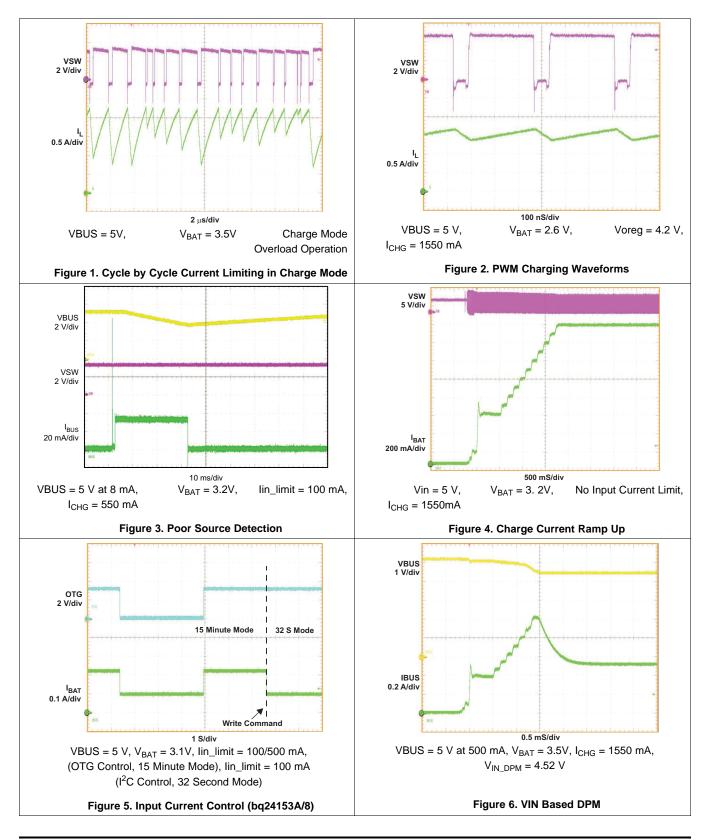

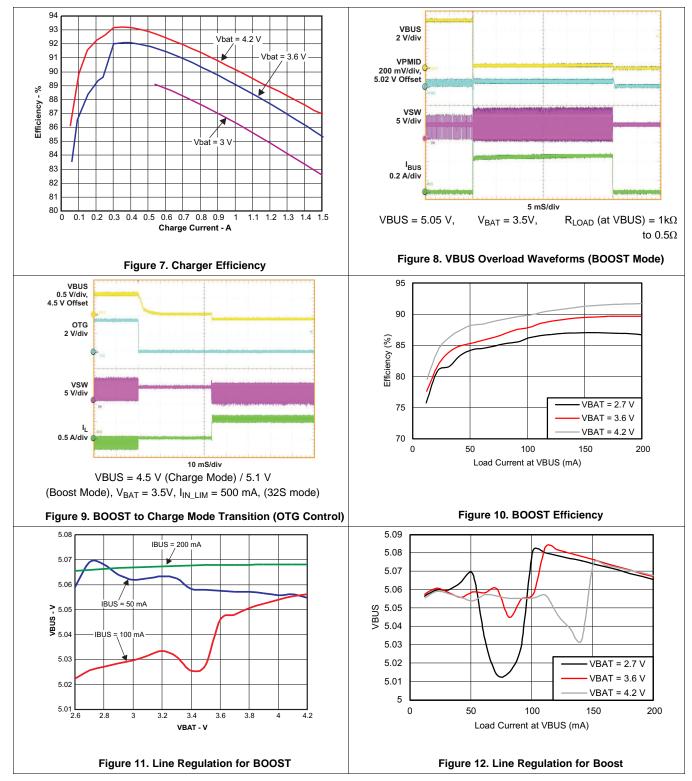

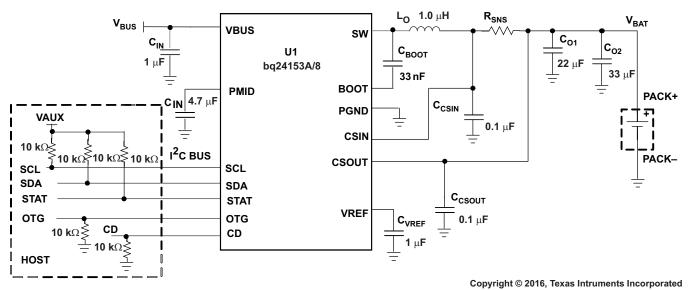

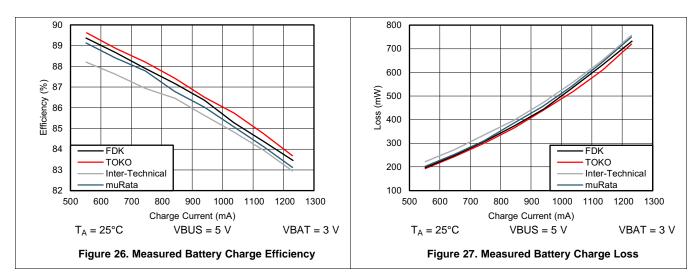

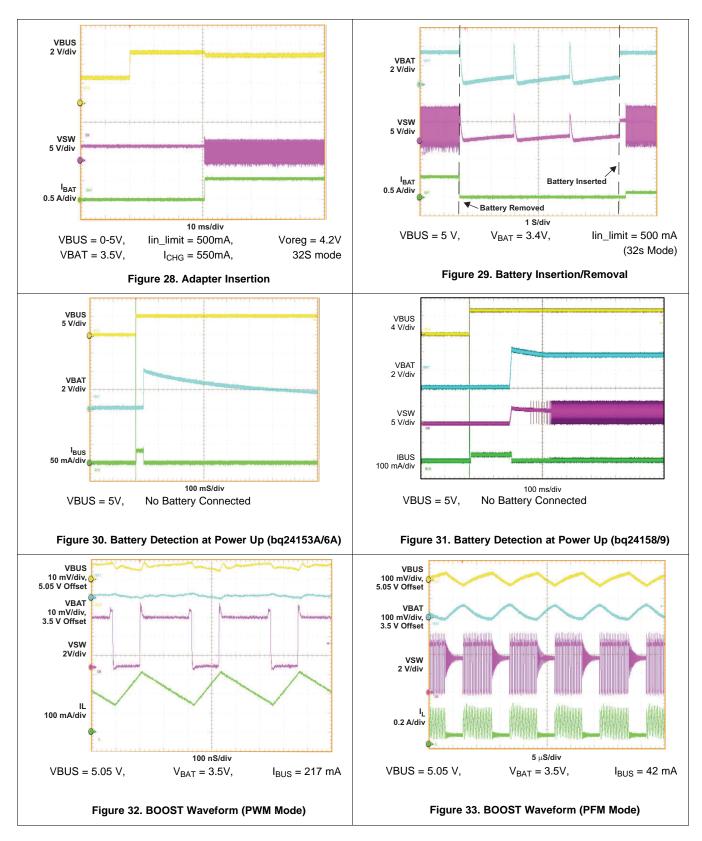

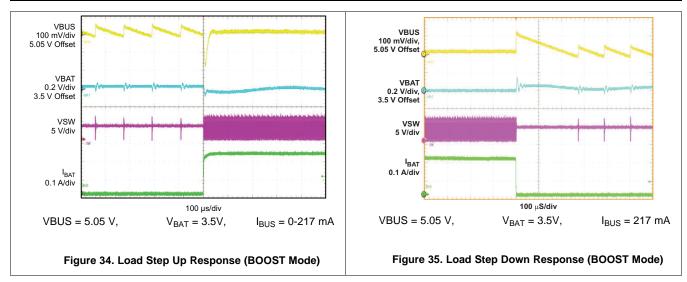

## 8.7 Typical Characteristics

Using circuit shown in Figure 25,  $T_A = 25^{\circ}C$ , unless otherwise specified.

Copyright © 2010–2016, Texas Instruments Incorporated

Product Folder Links: bq24153A bq24156A bq24158 bq24159

#### **Typical Characteristics (continued)**

## 9 Detailed Description

#### 9.1 Overview

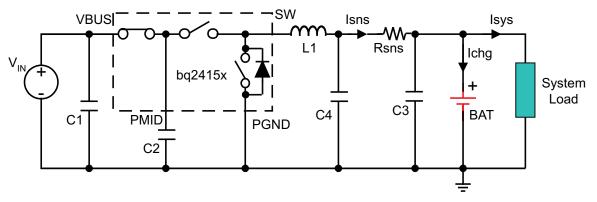

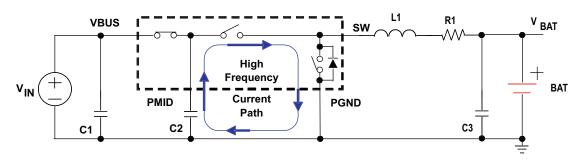

For a current restricted power source, such as a USB host or hub, a high efficiency converter is critical to fully use the input power capacity for quickly charging the battery. Due to the high efficiency for a wide range of input voltages and battery voltages, the switch mode charger is a good choice for high speed charging with less power loss and better thermal management than a linear charger.

The bq24153A/8/9 are highly integrated synchronous switch-mode chargers, featuring integrated FETs and small external components, targeted at extremely space-limited portable applications powered by 1-cell Li-Ion or Lipolymer battery pack. Furthermore, bq24153A/8 also has bi-directional operation to achieve boost function for USB OTG support.

The bq24153A/8 have three operation modes: charge mode, boost mode, and high impedance mode, while the bq24156A/9 only has charge mode and high impedance mode. In charge mode, the IC supports a precision Liion or Li-polymer charging system for single-cell applications. In boost mode, the IC boosts the battery voltage to VBUS for powering attached OTG devices. In high impedance mode, the IC stops charging or boosting and operates in a mode with very low current from VBUS or battery, to effectively reduce the power consumption when the portable device is in standby mode. Through I<sup>2</sup>C communication with a host, referred to as "HOST or 32-second" control/mode, the IC starts a 15 minute saftey timer and enters "15-minute" (default) mode. During 15-minute operation, the charger will still charge the battery but using each register's default values.

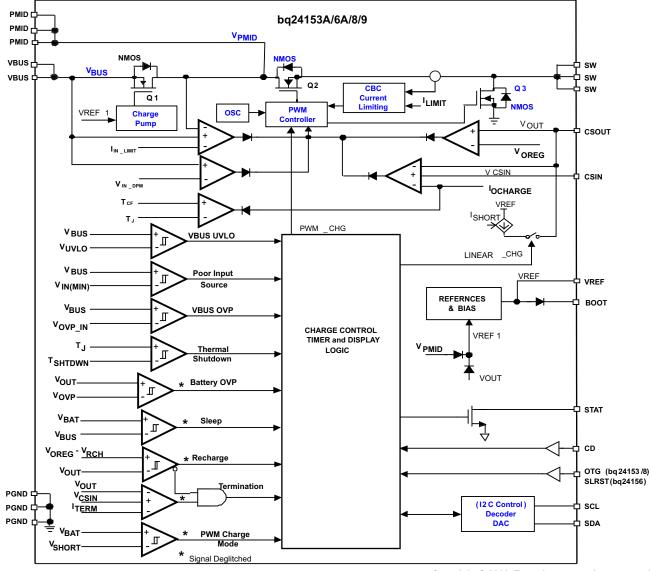

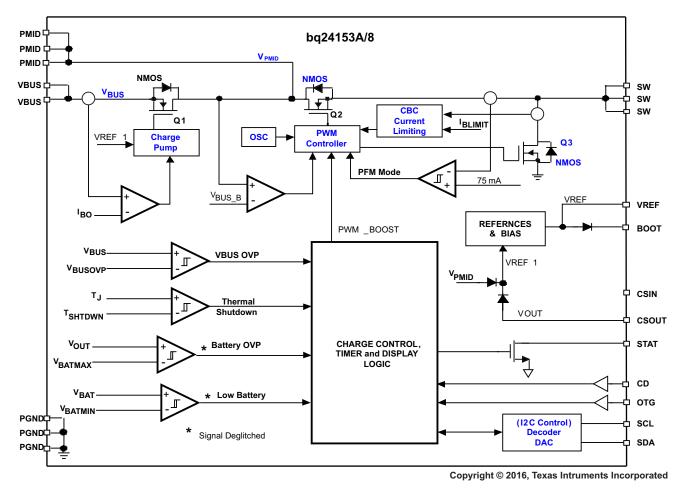

### 9.2 Functional Block Diagram

Copyright © 2016, Texas Intruments Incorporated

Figure 13. Function Block Diagram of bq2415x in Charge Mode

INSTRUMENTS

Texas

## Functional Block Diagram (continued)

Figure 14. Function Block Diagram of bq2415x in Boost Mode

#### 9.3 Feature Description

#### 9.3.1 Input Voltage Protection

#### 9.3.1.1 Input Overvoltage Protection

The IC provides a built-in input overvoltage protection to protect the device and other components against damage if the input voltage (Voltage from VBUS to PGND) goes too high. When an input overvoltage condition is detected, the IC turns off the PWM converter, sets fault status bits, and sends out a fault pulse from the STAT pin. Once  $V_{BUS}$  drops below the input overvoltage exit threshold, the fault is cleared and charge process resumes.

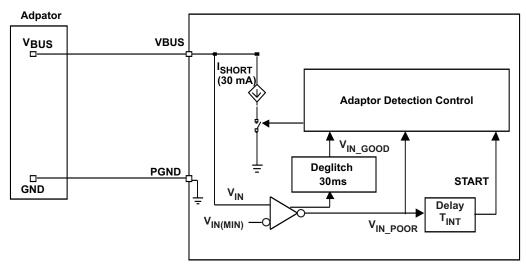

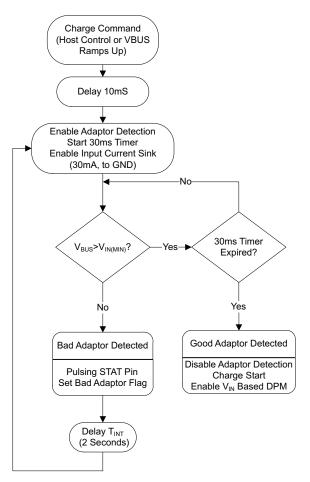

#### 9.3.1.2 Bad Adaptor Detection/Rejection

Although not shown in Figure 26, at power-on-reset (POR) of VBUS, the IC performs the bad adaptor detection by applying a current sink to VBUS. If the VBUS is higher than  $V_{IN(MIN)}$  for 30ms, the adaptor is good and the charge process begins. Otherwise, if the VBUS drops below  $V_{IN(MIN)}$ , a bad adaptor is detected. Then, the IC disables the current sink, sends a send fault pulse in FAULT pin and sets the bad adaptor flag (B2 - B0 = 011 for Register 00H). After a delay of  $T_{INT}$ , the IC repeats the adaptor detection process, as shown in Figure 15 and Figure 16.

Figure 15. Bad Adaptor Detection Circuit

## Feature Description (continued)

Figure 16. Bad Adaptor Detection Scheme Flow Chart

#### 9.3.1.3 Sleep Mode

The IC enters the low-power sleep mode if the VBUS pin voltage falls below the sleep-mode entry threshold,  $V_{CSOUT}+V_{SLP}$ , and VBUS is higher than the bad adaptor detection threshold,  $V_{IN(MIN)}$ . This feature prevents draining the battery during the absence of  $V_{BUS}$ . During sleep mode, both the reverse blocking switch Q1 and PWM are turned off.

#### 9.3.1.4 Input Voltage Based DPM (Special Charger Voltage Threshold)

During the charging process, if the input power source is not able to support the programmed or default charging current, the VBUS voltage will decrease. Once the VBUS drops to  $V_{IN\_DPM}$  (default 4.52V), the charge current begins to taper down to prevent any further drop of VBUS. When the IC enters this mode, the charge current is lower than the set value and the special charger bit is set (B4 in Register 05H). This feature makes the IC compatible with adapters having different current capabilities.

#### 9.3.2 Battery Protection

#### 9.3.2.1 Output Overvoltage Protection

The IC provides a built-in overvoltage protection to protect the device and other components against damage if the battery voltage goes too high, as when the battery is suddenly removed. When an overvoltage condition is detected, the IC turns off the PWM converter, sets fault status bits, and sends out a fault pulse from the STAT pin. Once  $V_{(CSOUT)}$  drops to the battery overvoltage exit threshold, the fault is cleared and charge process resumes.

#### Feature Description (continued)

#### 9.3.2.2 Battery Short Protection

During the normal charging process, if the battery voltage is lower than the short-circuit threshold,  $V_{SHORT}$ , the charger operates in short circuit mode with a lower charge rate of  $I_{SHORT}$ .

#### 9.3.2.3 Battery Detection at Power Up in 15-minute Mode (bq24153A/6A only)

bq24153A/6A also have a unique battery detection scheme during the start up of the charger. At VBUS power up, if the timer is in 15-minute mode, bq24153A/6A will start a 262ms timer when exiting from short circuit mode to PWM charge mode. If the battery voltage is charged above the recharge threshold (V<sub>OREG-VRCH</sub>) when the 262ms timer expired, bq2153A/6A will not consider the battery present; then stop charging, and go to high impedance mode immediately. However, if the battery voltage is still below the recharge threshold when the 262ms timer expires, the charging process will continue as normal battery charging process.

bq24158/9 simply begin regulating the output voltage to their default values (3.54V) at power up while in 15-minute mode.

#### 9.3.2.4 Battery Detection in Host Mode

For applications with removable battery packs, the IC provides a battery absent detection scheme to reliably detect insertion or removal of battery packs.

During the normal charging process with host control, once the voltage at the CSOUT pin is above the battery recharge threshold,  $V_{OREG}$  -  $V_{RCH}$ , and the termination charge current is detected, the IC turns off the PWM charge and enables a discharge current,  $I_{DETECT}$ , for a period of  $t_{DETECT}$ , (262 ms typical) then checks the battery voltage. If the battery voltage is still above the recharge threshold after  $t_{DETECT}$ , the battery is present. On the other hand, if the battery voltage is below the battery recharge threshold, the battery is absent. Under this condition, the charge parameters (such as input current limit) are reset to the default values and charge resumes after a delay of  $T_{INT}$ . This function ensures that the charge parameters are reset whenever the battery is replaced.

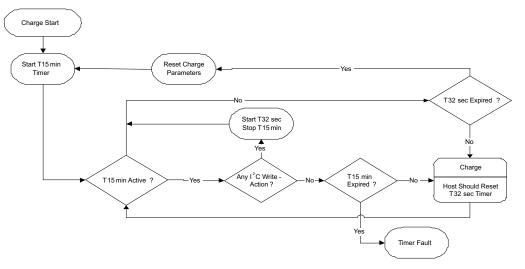

#### 9.3.3 15-Minute Safety Timer and 32-second Watchdog Timer in Charge Mode

Once a good adapter and good battery are attached, the IC starts the 15-minute saftey timer (t15min) that can be disabled by any write-action performed by host through I<sup>2</sup>C interface. Once the 15-minute timer is disabled, a 32-second watchdog timer (t32sec) is automatically started. The 32-second timer can be reset by the host using I2C interface. Writing "1" to reset the TMR\_RST bit in the control register will reset the 32-second timer and TMR\_RST is automatically set to "0" after the 32-second timer is reset. If the 32-second timer expires, the charge is terminated and charge parameters are reset to default values. Then the 15-minute timer starts and the charge resumes in 15-minute mode.

During normal charging process, the IC is usually in 32-second mode with host control and 15-minute mode without host control using  $I^2C$  interface. The above process repeats until the battery is fully charged. If the 15-minute timer expires, the IC turns off the charge, enunciates FAULT on the STATx bits of status register, and sends the 128µs interrupt pulse. This function prevents battery over charge if the host fails to reset the safety timer. The 15-minute charge, with default parameters, allows time for a discharged battery to charge sufficiently to be able to power the host and start communication. The safety timer flow chart is shown in Figure 17. Fault condition is cleared by POR and fault status bits can only be updated after the status bits are read by the host.

## **Feature Description (continued)**

Figure 17. Timer Flow Chart for bq24153A/6A/8/9

#### 9.3.4 USB Friendly Power Up

Prior to POR, if the host continues to write the TMR\_RST bit to 1, to stay in 32-second mode, then at POR, the charger enters normal charge mode (using the desired control bits). If not in 32-second mode at POR, the charge will operate with default bit values, in 15 minute mode, until the host updates the control registers.

If the battery voltage is above the  $V_{LOWV}$  threshold while in 15 minute mode, the charger will be in the high impedance state. The default control bits set the charging current and regulation voltage low as a safety feature to avoid violating USB spec and over-charging any of the Li-Ion chemistries, while the host has lost communication. The input current limiting is described below.